# MachXO2 デバイスの電力管理と 電力見積もり

2012 年 10 月 テクニカルノート TN1198

### はじめに

今日の多くの大容量 FPGA アプリケーションにとって、低消費電力は重要な要件の一つです。MachXO2<sup>™</sup> PLD はパワーコントローラやバンクコントローラ、およびパワーガードなど、多くの省電力機能を備えています。本書では供給電源に関する考慮事項やパワーカリキュレータ・ツールによる消費電力見積もりなど、MachXO2 アーキテクチャをベースにした省電力機能の活用方法について詳しく説明します。

## 電力モード

通常 FPGA 設計者は、コンフィグレーション中やユーザ機能の動作中にサブシステムをオフにすることで、消費電力を最小限にします。一般にデザインの動作モードは以下のように分類されます。

#### 通常動作:

·デバイスがフル動作状態で、全ての回路がアクティブ

・消費電力が最大

#### 低消費電力動作:

·サブシステムを不要時に動的にシャットダウン

・消費電力が平均またはそれ以下

#### 超低消費電力スタンバイ:

·全てのサブシステムをシャットダウン

・消費電力が最少、電池動作時間の延長に最適

柔軟な構造を持つ MachXO2 は、省電力動作モード時に、多くのオンチップ・コンポーネントを動的にオフにできます。表 8-1 はこれらの機能についての説明です。

#### 表 8-1. 低消費電力機能を持つ MachXO2 のコンポーネント

| デバイスコンポーネント                                   | 記 述                                                                                                                                                               |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| バンドギャップ                                       | スタンバイモード時にオフにできる。バンドギャップがオフのとき、PLL やオンチップオシレータのようなアナログ回路、そして参照型及び差動 I/O バッファもオフになる                                                                                |

| パワーオンリセット<br>(POR)                            | スタンバイモード時にオフにできる。この回路は VCC レベルを監視する。 VCC が危険なレベルに低下した場合、この回路により MachXO2 デバイスが再コンフィグレーションされる。 POR 回路がオフになっても、一部の電圧検出回路はアクティブなままである。このオプションの使用は供給電源が信頼できるアプリケーションのみ |

| オンチップオシレータ                                    | 2 つの省電力機能がある。オンチップオシレータは、設計で使用されない場合は静的にオフにできる。スタンバイモード時にもオフにできる                                                                                                  |

| PLL                                           | オンチップオシレータと同様に2つの省電力機能がある。PLLが設計で不要な場合は静的にオフにできる。スタンバイモード時にもオフにできる                                                                                                |

| I/O バンクコントローラ                                 | 参照型及び差動 I/O バッファ(HSTL、SSTL、LVDS などの規格を実装するために使用)は、LVCMOS のようなレシオ型シングルエンド I/O よりも電力を消費する。I/O バンクコントローラによってバンクごとにこれらの I/O を動的にオフできる                                 |

| プライマリ・クロック<br>ネットワーク・ダイナ<br>ミック・クロックイネー<br>ブル | 省電力のために、プライマリ・クロックネットワークを動的にディセーブルできる                                                                                                                             |

| パワーガード                                        | パワーガードは入力バッファに実装されている機能で、これは入力バッファが不要時にオフできる。この機能はクロックとデータパスの両方で使用できる。この機能の効果を最大限に得られるのは、スタンバイモード時に汎用配線リソースを使って供給されるクロック入力をオフにする目的で使用した場合となる                      |

© 2011 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

(日本語版は日本語による理解のため一助として提供しています。その作成にあたっては可能な限り正確を期しておりますが、原文英語版との不一致や不適切な訳文がある場合を含み、英語版が正(有効)です。特に電気的特性・仕様値係わる事項については最新版の英語版を必ず参照するようにお願い致します。)

## パワーコントローラ

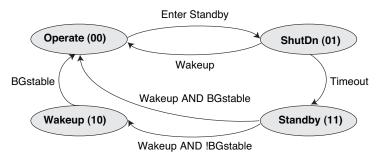

MachXO2 PLD には、スタンバイモードへの出入りをスムーズにするためのパワーコントローラが内蔵されています。パワーコントローラの2つの主要な信号(STOPとSTDBY)の遷移を図8-1に示します。

## 図 8-1. パワーコントローラの状態図 (STDBY, STOP))

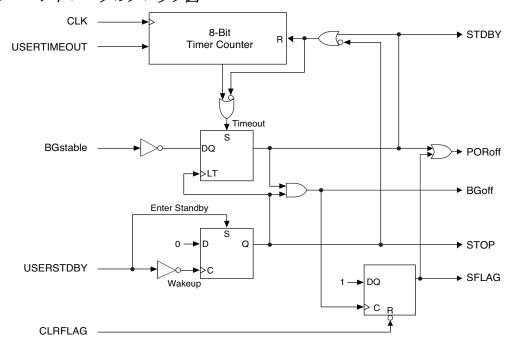

図 8-2 はパワーコントローラの詳細なブロック図です。表 8-2 にはポートの説明を示します。タイムアウト信号は、入力クロックソースを 28 (または 256) で分周するオプションの 8 ビット・タイマカウンタから生成されます。これにより STOP 信号と STDBY 信号の間に遅延が発生します。

#### 図8-2. パワーコントローラのブロック図

## 表 8-2. パワーコントローラの信号

| ポート名                | I/O                  | オプション<br>指定有無 | 記 述                                                                                                                                                                                                                                                            |  |

|---------------------|----------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLK                 | 入力                   | 有             | タイマ遅延ブロックへのクロックソース                                                                                                                                                                                                                                             |  |

| USERTIMEOUT         | 入力                   | 有             | タイマカウンタ・ブロック用のアクティブ High イネーブル信号                                                                                                                                                                                                                               |  |

| USERSTDBY           | 入力、ま<br>たはハー<br>ドワイヤ | 有             | この信号の立ち上がりエッジにより、スタンバイに入るシャットダウン・シーケンスが開始され、立ち下がりエッジによりスタンバイからのウェイクアップ・シーケンスが開始される。USERSTDBY 信号は、ユーザロジックまたはコンフィグレーション・ロジックからのハードワイヤから供給される。CFGSTDBY 信号と CFGWAKE 信号は、コンフィグレーション用 I2C 及び SPIらの standby/wake コマンドのシミュレーションに対応するために使用する。これらのポートは EFB の対応するポートに接続する |  |

| CLRFLAG             | 入力                   | 有             | スタンバイフラグ用の非同期アクティブ High リセット。デバイスがウェイクアップした後、ユーザロジックはこの信号に High パルスを供給し、SFLAG をクリアする必要がある                                                                                                                                                                      |  |

| STOP                | 出力                   | 有             | STDBY 信号の前ぶれとなるアクティブ High 信号。STOP から STDBY までの遅延は、8 ビット・タイマカウンタ・ブロックによって決まる。STOP 信号を使ってクロックや信号をオフにすることにより、ロジックのスタンバイを準備する                                                                                                                                      |  |

| STDBY               | 出力                   | 無             | 一般配線を介してユーザロジックや I/O パッド、オシレータ、及び PLL に与えるアクティブ High 信号。ロジックをスタンバイ状態にするために使用する                                                                                                                                                                                 |  |

| SFLAG               | 出力                   | 有             | デバイスがスタンバイ状態であることをユーザロジックに通知するために、このフラグ信号が High になる                                                                                                                                                                                                            |  |

| PORoff <sup>1</sup> | ハードワ<br>イヤ           | 有             | 電圧検出回路 (POR) へのシャットオフ信号。電圧検出回路は $V_{CC}$ が降下したかどうかを判断するために使用される。降下した場合はデバイスが再コンフィグレーションされる                                                                                                                                                                     |  |

| BGoff <sup>i</sup>  | ハードワ<br>イヤ           | 有             | さらなる省電力を実現するために、MachXO2 ZE 及び HE バージョンに用意されているバンドギャップ回路へのシャットオフ信号。バンドギャップ回路がオフになると、POR 回路とアナログ回路(PLL、オシレータ、参照型 LVCMOS I/O、SSTL I/O、HTSTL I/O、及び差動 I/O)がオフになる                                                                                                   |  |

| BGstable            | ハードワ<br>イヤ           | 無             | バンドギャップ回路からの信号。これはバンドギャップ回路が安定になってから解放される                                                                                                                                                                                                                      |  |

<sup>1.</sup> POR が遮断されても一部の電圧検出回路はアクティブなままである。このオプションは、供給電源が信頼できる用途でのみ使用すること。VCC はデータシートの推奨動作範囲内でなければならない。範囲外の場合はデバイスの機能が保証されない

(和訳版注:英語オリジナルでは"オプション指定有無"で空欄の信号があるが、次改訂版では本表のように更新予定)

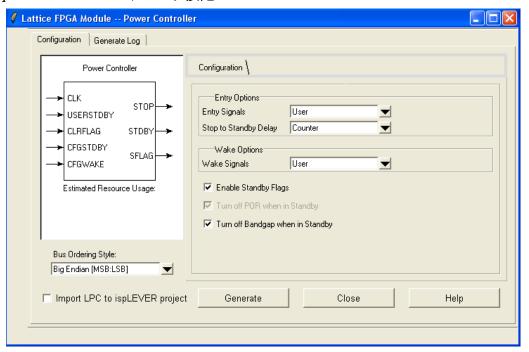

パワーコントローラの構成は図 8-3 に示される IPexpress™ を用いて行います。

### 図8-3. IPexpress のパワーコントローラ設定

表 8-3. IPexpress のパワーコントローラ設定の記述

| エントリ                                             | タイプ           | 値                     | デフォルト値 | コメント                                                                                     |

|--------------------------------------------------|---------------|-----------------------|--------|------------------------------------------------------------------------------------------|

| Entry Signals                                    | プルダウン<br>ボックス | User, Configuration   | User   | コンフィグレーションには JTAG 及び I <sup>2</sup> C を含む                                                |

| Stop to Standby<br>Delay                         | プルダウン<br>ボックス | User, Counter, Bypass | Bypass | ユーザがタイマカウンタへの USERTIMEOUT 信号<br>をイネーブルする。Bypass が選択されている場合、<br>STOP 信号と STDBY 信号の間に遅延はない |

| ウェイクアップ                                          | •             |                       |        |                                                                                          |

| Wake Signals                                     | プルダウン<br>ボックス | User, Configuration   | User   |                                                                                          |

| スタンバイ                                            |               |                       |        |                                                                                          |

| Enable Standby<br>Flags                          | チェック<br>ボックス  | TRUE, FALSE           | TRUE   |                                                                                          |

| Turn off Bandgap<br>when in Standby <sup>1</sup> | チェック<br>ボックス  | TRUE, FALSE           | FALSE  | オフのとき POR 回路及びアナログ回路(PLL、オシレータ、参照型 LVCMOS I/O、SSTL I/O、HTSTL I/O、差動 I/O) がオフになる          |

| Turn off POR when in Standby <sup>1</sup>        | チェック<br>ボックス  | TRUE, FALSE           | FALSE  | 電圧検出回路は、VCCが降下したかどうかを判断するために使用される。降下した場合デバイスが再コンフィグレーションされる                              |

<sup>1.</sup> POR が遮断されても一部の電圧検出回路はアクティブなままである。このオプションは、供給電源が信頼できる用途でのみ使用すること。VCC はデータシートの推奨動作範囲内でなければならない。範囲外の場合はデバイスの機能が保証されない

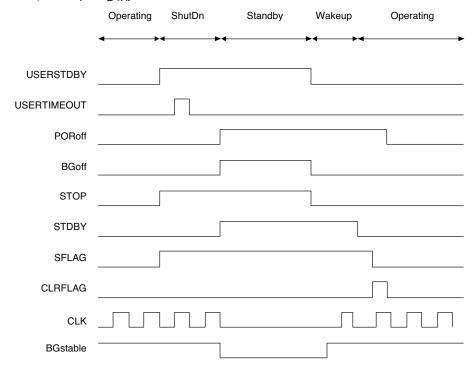

図 8-4 はパワーコントローラが、スタンバイ状態に入る時と抜ける時のシーケンスを示しています。

#### 図8-4. パワーコントローラの波形

パワーコントローラを使用して設計をする場合は以下の点に注意してください。

- ・スタンバイ時にパワーコントローラの USRSTDBY 信号がオフになった場合、ロックアップ状態になることを防ぐためにソフトウェアはエラーを生成する

- ・電圧検出回路がオフになっても、電圧検出回路内の一部の回路はアクティブなままとなる。電圧検出回路 をオフにするのは、供給電源が信頼できる場合のみ。VCC はデータシートの推奨動作範囲内でなければ ならない。そうでない場合は機能が保証されない

- ・バンドギャップ回路がオフのとき電圧検出回路及びアナログ回路(PLL、オシレータ、参照型 LVCMOS I/O、SSTL I/O、HTSTL I/O、 差動 I/O) はオフになる

#### バンクコントローラ

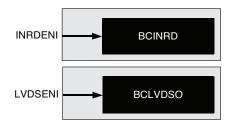

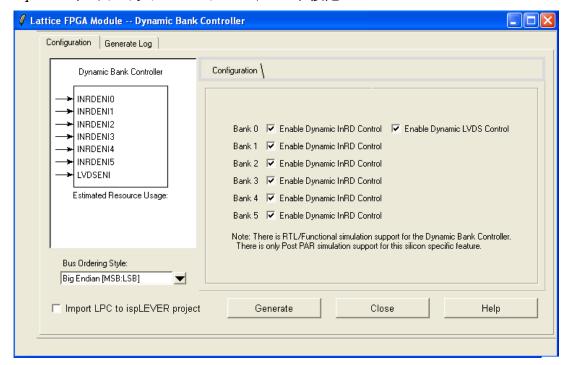

参照型、差動型、及び LVDS I/O タイプは他の I/O タイプよりも消費電力が高いため、常にアクティブにしておく必要はありません。アクティブ High のバンクコントローラは、バンクごとにこれらの I/O を動的にオフできます。参照型及び差動入力をオフにするためには、ダイナミック InRD (Dynamic Input Referenced and Differential I/Os:参照型及び差動 I/O) を使用します。LVDS 出力ドライバをオフにするにはダイナミック LVDS 制御 (Dynamic LVDS Control) を使用します。バンクコントローラは図 8-5 に示されるプリミティブ (ダイナミック InRD は BCINRD、ダイナミック LVDS は BCLVDSO) や、図 8-6 に示される IPexpress を使ってインスタンス化できます。

図 8-5. INRDB, LVDSOB プリミティブ

8-5 tn1198JP\_01.3

## 図8-6. IPexpress のダイナミック・バンクコントローラ設定

バンクコントローラを用いて設計する場合、以下の点に注意してください。

- ・バンクコントローラの制御信号がバンクコントローラによってイネーブルされたバンクの参照型または差動 I/O から供給される場合、ロックアップ状態になることを防ぐためにソフトウェアはエラーを生成する

- バンドギャップの電源をオフにするとバンクコントローラは無効になる

## パワーガード

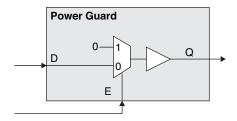

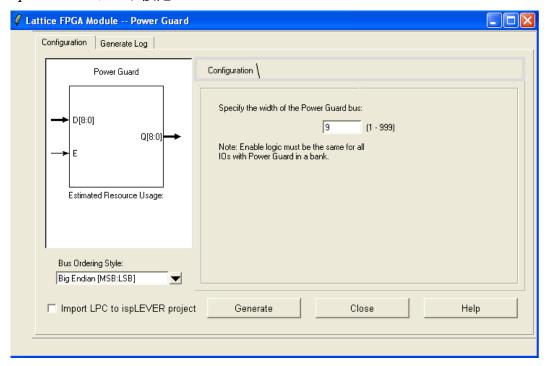

PG (Power Guard:パワーガード)機能は入力ピンで信号をゲーティングすることにより、配線の動的な電力消費を最小にします。特にクロックのような大ファンアウト・ネットや高負荷ネットでこのような電力損失を防ぐために、入力は "パワーガード"できます。パワーガードはアクティブ High の制御信号を使用して、信号がネットに載ることを防ぎます。図 8-7 に示すパワーガード・プリミティブコンポーネントを、クロックまたはデータパスに含めることができます。多ビット幅のバスの場合、図 8-8 に示すように IPexpress を使用します。

## 図8-7. パワーガード・プリミティブ

## 図8-8. IPexpress パワーガード設定

パワーガードを用いて設計する場合、以下の点に注意してください。

・パワーガードの制御信号が、パワーガード・コンポーネントの出力から供給される場合、ロックアップ状態になることを防ぐためにソフトウェアはエラーを生成する

## 低消費電力設計の実装

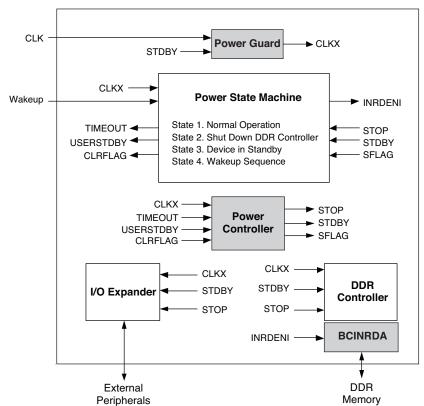

図 8-9 は MachXO2 の省電力アーキテクチャ・コンポーネントを使ったサンプルデザインの実装を示しています。

この設計には以下の4種類の電力レベル/ステートがあります。

- 1. 通常動作

- 2. 通常動作で、DDR メモリコントローラがオフ

- 3. スタンバイの準備

- 4. スタンバイ

このサンプルデザインは以下のようになっています。

- · 白いブロックは通常の FPGA ロジックを示す

- ・グレーのブロックは省電力に関連する MachXO2 コンポーネントを示す

- ・クロック CLK はデザイン内の高ファンアウト・ネットのため、パワーガード・コンポーネントを通過する。STDBY 信号を使用してクロック信号が配線に流れることを防ぎ、これによりダイナミック電力を低減する

- ・バンクコントローラ (BCINRDA) を使用して、INRDENI 信号にによって DDR インターフェイスの参照型 SSTL I/O をオフにし、これによりスタティック及びダイナミック電力を低減します。

- ・パワー・ステートマシンが設計の様々な状態を制御する。以下の項目はそれぞれのステートで何が起こる かを示す:

- 通常動作の DDR コントローラと I/O エキスパンダが外部メモリ及び周辺デバイスと通信する

- DDR メモリは使用されず、INRDENI 信号が High にアサートされる。参照型 SSTL I/O がディセーブルされ、それによりスタティック及びダイナミック電力を低減する。

- デバイスが低消費電力スタンバイ・シーケンスを開始する

- USERSDBY が High にアサートされ、パワーコントローラがそれを使いて STOP を High にアサート する

- DDR コントローラ及び I/O エキスパンダ・ロジックがスタンバイの準備をする

- パワーコントローラのタイマカウンタから生成される CLKX/256 遅延後に、STDBY 信号が High に アサートされる

- SFLAG が High にアサートされる。パワーガードは CLK 信号が高ファンアウト配線に流れるのを防ぐ

- バンクコントローラが参照型 SSTL I/O をオフにする。DDR コントローラ及び I/O エキスパンダロジックがスタンバイ状態になり、最も低い消費電力ステートになる

- 低消費電力スタンバイ・ステートでは、デバイスは通常動作を再開する前にアサートされる Wakeup 信号を待つ

#### 図8-9. 低消費電力デザインの実装

## 電源シーケンス制御と活線挿抜

MachXO2 デバイスは、パワーアップ及びパワーダウン時の振る舞いを確実に予測できるように設計されています。パワーアップ及びパワーダウン・シーケンスの間、I/O は確実に動作するために十分な電圧( $V_{CCMIN}$ )に電源が達するまでトライステートに留まります。さらに、I/O ピンへのリークは、MachXO2 ファミリデータシートに規定されている制限値以下に制御されるため、システムのその他の部分との容易な統合が可能になります。

## 推奨パワーアップ・シーケンス

MachXO2 ファミリのパワーアップ・シーケンスの詳細については、MachXO2 ファミリ・データイーとの "DC とスイッチング特性" セクションを参照してください。

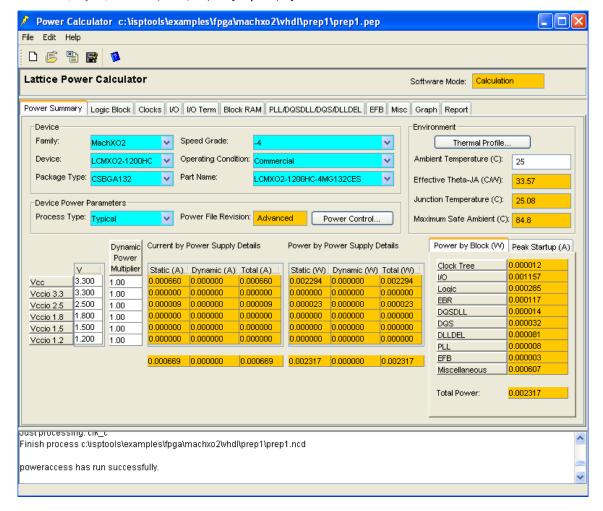

## パワーカリキュレータ

パワーカリキュレータはユーザがデバイスの消費電力を見積もることを可能にする強力なツールです。この ツールには "what-if" 解析のための見積もり(Estimation)モードがあります。またデザインの電力を正確に 見積もるために、NCD デザインファイル(ネットリスト)をインポートすること(計算モード)もできま す。バックグランド・エンジンがいずれのモードでも迅速かつ正確に計算を実行します。

パワーカリキュレータ・ツールを見積もりモードで実行している場合、設計者が様々なコンポーネントの推定使用値を入力することで、ツールは電力見積もり値を計算します。特に "what-if" 解析やデバイス選択を行う場合、このモードから開始するのが良いでしょう。

計算モードはより精度の高いアプローチで、設計者は配置配線後のネットリスト・デザインファイル(NCDファイル)をインポートすることにより、実際のデバイス使用率を取り込みます。

ユーザはトレースレポート (Trace Report, TWR) ファイルをインポートすることもでき、これによりクロック周波数が自動的に取り込まれます。ただしトレースレポートには、設計制約ファイルで制約されているクロックネットの周波数しか含まれていないことに留意してください。

パワーカリキュレータでは、ダイナミック電力計算に使用する AF (活性化率、Activity Factor)のデフォルト値として 10% が設定されています。このデフォルト値は、プロジェクト全体で一括して、または個々のクロックネットごとに変更できます。AF については本書の後ろで詳しく説明します。

#### パワーカリキュレータの想定ハードウェア

デバイスの消費電力は、大きく分けてスタティック (DC) 成分とダイナミック (AC) 成分に分割できます。これらの成分にはチップのジャンクション温度 (TJ) に応じて以下のような依存関係があります。

- ・ スタティック電力はトランジスタ動作に関連する、以下の 2 種類がある

- 温度に強く依存するリーク電流

- 温度に関係なくほぼ一定な DC バイアス

- ・ダイナミック電力は、トランジスタ信号のトグル動作によって生じる

- ダイナミックは温度に関係なくほぼ一定

デバイスの各コンポーネント(LUT、レジスタ、EBR、I/O など)は、スタティック及びダイナミック電力に対するそれぞれの係数を持っています。次のセクションで記述するとおり、パワーカリキュレータ・ツールで行う選択によっては、これらの係数に影響を及ぼします。

#### パワーカリキュレータと電力計算式

パワーカリキュレータ・ツールの起動及び使用については **Help > ispLEVER Help** (Diamond では **Help > Power Calculator Help**) を参照してください。

手順を進めると図8-10に示されるウィンドウが表示されます。

#### 図8-10. パワーカリキュレータのメインウィンドウ

パワーカリキュレータで使用可能なオプションがデバイスの消費電力にどのように影響するかについて理解する必要があります。例えば周囲温度が変わると以下の数式に従ってジャンクション温度に影響が生じます。

$$T_J = T_A + \theta_{JA\_EFFECTIVE} * P$$

(1)

ここで、 $T_J$  および  $T_A$  はそれぞれジャンクション温度と周囲温度、P は電力、 $\theta_{JA\_EFFECTIVE}$  はチップとその周囲環境間の実効熱抵抗です。

ジャンクション温度は周囲温度に直接比例します。 $T_A$ が上昇すると  $T_J$ も上昇し、その結果スタティックリーク成分が増加します。

プロセスタイプの選択もスタティックリークに影響します。特にスタティックリーク係数が変化します。 DC バイアス成分は範囲内で一定です。

ダイナミック電力の場合トグルレートを上げると電力のダイナミック成分が増加します。

## 標準 (Typ.) プロセスおよびワースト (WC) プロセスの消費電力と ICC

DC 電力に影響を及ぼすもう 1 つの要因はプロセスバラつきです。これによりブランク時(quiescent)電力にもバラつきが生じます。

パワーカリキュレータはこれらの要素を考慮しており、設計者が TYP プロセスか WC プロセスかのいずれかを指定できます。

#### ジャンクション温度

ジャンクション温度は動作中のチップ温度であり、デバイス電力に影響を与える最も重要な要素の一つです。ジャンクション温度、電圧、及びデバイスパッケージの組み合わせが固定の場合、ブランク時電力は同一です。

周囲温度は数式 [1] のとおりジャンクション温度に影響します。高温環境で動作中のデバイスではジャンクション温度が高くなるため、リーク電流が比較的多くなります。パワーカリキュレータは、この周囲温度とジャンクション温度間の依存性をモデル化しています。ユーザが周囲温度を入力すると、アルゴリズムでその温度が使用され、環境  $(T_A$ 、気流など)に応じたシステム(その設計を使って動作しているデバイス)の熱平衡を見つける反復プロセスにより、ジャンクション温度と電力が計算されます。

#### 最大安全周囲温度

最大安全周囲温度(Maximum Safe Ambient Temperature)は、パワーカリキュレータのサマリ(Summary)タブに表示される数値のうちで最も重要なものの一つです。これはコマーシャル・グレードまたは産業グレード・デバイスのジャンクション温度制限を超えることなく設計が動作可能な最大の周囲温度です。

パワーカリキュレータはこの温度を正確に予測するアルゴリズムを使用しています。電圧、プロセス、周波数、AF%(またはデバイスの電力損失に影響する可能性のある要素)などのオプションをユーザが変更すると、アルゴリズムが自動的に調節を行います。

### 動作温度範囲

システムを設計する際、システム環境内でデバイスが規定温度で動作することを確認する必要があります。システムの設計前に検討することが特に重要です。パワーカリキュレータを使用すれば、デバイスの熱力学を予測し、ダイナミック電力を見積もることができます。ボード設計前にデバイスの動作温度を見積もることができるため、設計者は電力量や気流をより最適に計画できます。

電力合計、周囲温度、熱抵抗、及び気流の全てがデバイス熱力学の一因となりますが、デバイス動作にとって最も重要なのはジャンクション温度(MachXO2 ファミリ・データシートで規定)です。許容ジャンクション温度範囲は、コマーシャルグレード・デバイスは  $0 \sim 85^\circ$  C、産業用グレード・デバイスは  $-40 \sim 105^\circ$  C です。チップのジャンクション温度がこれらの温度範囲内でない場合、デバイスの機能の性能及び信頼性が保証されません。

## DPM (Dynamic Power Multiplier:ダイナミック電力乗数)

ユーザ定義の動作周波数が、ジャンクション温度制限を守れるかという問題をより複雑にします。これを解決するためにダイナミック電力乗数 DPM を使いることで、システム及びボード設計者に対してマージンを与えることができます。

DPM のデフォルト値 "1.0" は、ダイナミック電力がそのままであるということを表します。例えば 20% のダイナミック電力を加えたい場合、DPM として 1.2 (1.0 + 20%) を設定でき、意図する電源系統に対してこの設定を適用できます。これによって該当する電源のダイナミック電力が 20% 増加し、(必要に応じて) いくらかのマージンが与えられます。

#### 電力バジェット

パワーカリキュレータは特定の条件下におけるデザインの電力損失を計算し、またジャンクション温度(TJ)も予測します。ジャンクション温度が MachXO2 ファミリデータシートで規定されている制限内でない場合、そのジャンクション温度でのデバイスの動作可能性を再評価する必要があります。

コマーシャル・グレードのデバイスは、ジャンクション温度が 85°C を超えると速度が低下する可能性があり、産業用グレード・デバイスは、ジャンクション温度が 100°C を超えると速度が低下します。保証された動作速度を得るには、チップ温度をこれらの制限値より低く保つ必要があります。

高温でデバイスが動作するということは、スタティック Icc も高くなるということです。特定の温度における合計 Icc (スタティック Icc とダイナミック Icc の両方) とスタティック Icc の差が、使用可能なダイナミック Icc 量となります。デバイスがこの値よりも大きいダイナミック Icc で動作する場合、合計 Icc も大きくなります。そうなるとチップ温度が規定の動作条件を超えてしまいます。

電力、周囲温度、熱抵抗、及び気流の4つの要素を変化させ、また制御することで、デバイスのジャンクション温度を低減することもできます。パワーカリキュレータは、システム設計者がFPGA電力量を正確に推定することを可能にする強力なツールです。これにより、すなわちシステム全体の信頼性を向上させます。

#### ダイナミック電力の低減

パワーコントローラ、バンクコントローラ、及びパワーガードがデザインに実装されている場合、パワーカリキュレータは、コンポーネントを単純にイネーブルまたはディセーブルすることにより、電力を動的に見積もります。

#### 図8-11. ダイナミック電力のオプション

| tandby Option   | Dynamic Bank Option                              |  |

|-----------------|--------------------------------------------------|--|

| Disable Bandgap | Bank0 ☑ Disable InRD ☐ Disable LVDSO ☐ Enable PG |  |

| Disable POR     | Bank1 Disable InRD Enable PG                     |  |

| Disable OSC     | Bank2 Disable InRD Enable PG                     |  |

| Disable PLL     | Bank3 Disable InRD Enable PG                     |  |

|                 |                                                  |  |

|                 |                                                  |  |

|                 |                                                  |  |

|                 |                                                  |  |

|                 |                                                  |  |

#### 活性化率の計算

活性化率 AF% は、信号がアクティブになるかまたは出力がトグルする回数(または時間)に対するパーセンテージとして定義されます。クロックドメインに関連するリソースの大部分は、動作しているクロック周波数のある割合でトグルします。パワーカリキュレータ・ツールの AF% コラムの下に、この値をパーセンテージで入力する必要があります。

I/O に関する項目としては I/O トグルレート(TR)があります。AF% は PFU、配線、及びメモリリード / ライトポートなどに適用されます。I/O の活性化率である TR はユーザが供給する信号によって決まるか(入力の場合)、またはデザインの出力に応じて決まります(出力の場合)。したがってこのレートまたは I/O トグル周波数は、I/O の活性化率を示す目安になります。

出力の TR は MHz 単位で表され、以下の数式で定義されます。

トグルレート TR (MHz) =

$$1/2 * f * AF\%$$

(2)

ユーザは他のリソースのような周波数と AF% を指定する代わりに、I/O の TR [MHz] 値を指定する必要があります。AF 値は配線リソースや出力、または PFU ごとに計算できますが、その算出には時間がかかります。 デバイスの使用率がおよそ 30 ~ 70% のデザインの場合、AF% の一般的な推奨値は 15 ~ 25% です。これは平

均値ですが、AF の正確な値はクロック周波数やデザインに対するスティミュラス、及び最終出力などに依存します。

#### 熱抵抗と気流

一般的に、パッケージ化されたデバイスの伝熱性能は、熱抵抗( $\theta$ )を使って示されます。半導体デバイスの場合、熱抵抗はチップ表面で消費される電力(熱)1 ワットに対して、定常状態におけるチップジャンクション温度の上昇度合いを示し、単位は °C/Wです。

最も一般的な例はジャンクション対周囲間(Junction-to-Ambient)の熱抵抗  $\theta$  JA [° C/W] と、ジャンクション対ケース間(Junction-to-Case)の熱抵抗  $\theta$  JC [° C/W] です。もう 1 つの要素はジャンクション対ボード間(Junction-to-Board)の熱抵抗  $\theta$  JB [° C/W] です。

(周囲やケース、またはボードなどの)基準となる温度と電力、及び対応する T 値がわかれば、以下の式でジャンクション温度を計算できます。

$$T_{I} = T_{A} + \theta_{IA} * P \tag{3}$$

$$T_J = T_C + \theta_{JC} * P \tag{4}$$

$$T_{I} = T_{B} + \theta_{IB} * P \tag{5}$$

$T_J$ 、 $T_A$ 、 $T_C$ 、及び  $T_B$  は、それぞれジャンクション、周囲、ケース(またはパッケージ)、及びボードの温度 [°C] です。P[W] はデバイスの総電力損失です。

$\theta_{JA}$  は自然空冷及び強制対流空冷システムで一般的に用いられます。  $\theta_{JC}$  は PCB またはヒートシンクに直接取り付けられた、伝導率が高いケースを持つパッケージの場合に役立ちます。  $\theta_{JB}$  はパッケージに接するボードの温度がわかっている場合に適用します。

パワーカリキュレータは、周囲温度を用いて、対象デバイスの  $\theta_{JA}$  に基づいてジャンクション温度を計算します。またジャンクション温度のより正確な値を得るために、気流値 (LFM) を指定することもできます。

気流の効果を上げるには、デバイス上部またはヒートシンク表面を流れる空気の量を最大限にすることが重要です。ファンを追加したり、既存のファンの出力を増加したりすることで、デバイス周囲の気流を増加できます。それが不可能な場合は、気流がデバイスに向かって流れるように調整する方法に効果のある場合があります。即ち薄い板金や機械的に気流を導く物体を加えることにより、対象デバイスの方向に空気を導くということです。しばしば簡単なバッフルを加えることで、ファンを追加する必要がなくなります。さらに、気流が通過するデバイスの順序も熱損失量に影響を与える可能性があります。

#### 消費電力の削減

今日の設計者にとって最も重要な課題の一つは、システム消費電力の削減です。特に現代の(電池駆動の) 携帯機器及び電子機器では、消費電力を少しでも削減できれば動作時間を延ばせます。システム全体の消費 電力を大幅に削減するために使用される設計技法が幾つかありますが、これには以下のような方法が含まれ ます。

- ・パワーコントローラ、バンクコントローラ、パワーガードなど、MachXO2の省電力機能を利用する

- ・データシートに規定されている制限内で動作電圧を下げる

- ・ 規定されたパッケージ温度制限内で動作させる

- ・ IPexpress の PLL パワーオプションを利用する

- · 入力のみの I/O バンクが省電力になっていることを確認する

- ・最適なクロック周波数を用いて消費電力を削減する。ダイナミック電力は動作周波数に正比例するため、 消費電力を削減する目的で設計者はデザイン内のクロックで低い速度にできないかを判断する必要があり ます。

- ・デバイス内におけるデザインの配置領域を縮小する。密集して配置されるデザインほど少ない配線リソースしか使用しませんので、その結果消費電力も少なくなります。

- · できる限り I/O の電圧振幅を抑える

- ・入力ロジックレベルがフローティング状態のままでなく、プルアップまたはプルダウンされていることを 確認する

- ・ボード上の他の部品の I/O プルアップ・ダウンとコンフリクトしないことを確認する

- ・できる限り最適な符号化を使用する。例えば16ビットの2進カウンタのAFは平均12%しかありませんが、7ビットの2進カウンタのAFは平均28%です。それに対して、7ビットのLFSRカウンタは50%のAFでトグルするため、消費電力がより大きくなります。またグレイコードカウンタは各クロックエッジで1ビットだけ変化するので、10%未満のAFとなり、消費電力が最少になります。

- ・ 以下の方法で動作温度を最も低くなるようにする

- セラミックパッケージなど、熱をよりよく放射できるパッケージを使用する

- ヒートシンク及び熱プレーンを PCB のデバイス周りに置く

- 機械的な気流ガイドやファン (システムファンやデバイスに取り付けられたファン)など、気流を改善する技法を用いる

- ・ 待機時の最少電力を達成するための方策

- すべてのクロックと組み合わせロジックが不動作の状態にする

- すべての入力をロジック High にする。困難な場合はトグルする入力をパワーガードでマスクする

- すべての出力をトライステートにし、バンクコントローラで参照型出力と LVDS 出力をオフにする

- 内部オシレータを STDBY ポートによってオフにする

- PLL を STDBY ポートによってオフにする

- バンドギャップと POR をバンクコントローラを用いてオフにする

#### パワーカリキュレータの考え方

パワーカリキュレータの考え方を以下に示します。

- ・室温 25°C を基準とした定数を用いる等式を使用する。デフォルト温度の 25°C は変更できる

- ・電力見積もりに基づいてデバイスのジャンクション温度  $(T_J)$  を計算する際に、周囲温度  $(T_A)$  を指定可能  $T_I$  はユーザ入力の  $T_A$  および、室温での電力から算出される

- · I/O の消費電力は 5pF の出力負荷に基づいており、設計者はこの容量性負荷の値を変更できる

- ・電源系統( $V_{CC}$ 、 $V_{CCIO}$ )ごとに電力消費と電流を見積もることができる

- ・消費電力の計算にはデフォルトで VCC の公称値が使用される。使用可能な値のリストから、これより低い VCC 値または高い VCC 値を選ぶことができる

- ・動作システムをより正確に見積もるために、 $\theta_{JA}$ を手動で変更したり、ヒートシンク・オプションと共に気流値(LFM、リニアフィート毎分)を入力できる

- ・I/O タイプのデフォルト値は LVCMOS25 で 8mA

- ・AF 値はレジスタ出力などのトグルレートとして定義される。例えばフリップフロップの入力がクロック 周期毎に変化すると仮定した場合、100MHz で動作するフリップフロップの AF =100% は 50MHz になる。 ロジックのデフォルト AF は 10%

# テクニカルサポート

ホットライン:1-800-LATTICE(北米)

+1-503-268-8001(北米以外)

電子メール:techsupport@latticesemi.com インターネット:www.latticesemi.com

## 改訂履歴

| リリース     | バージョン | 新ページ | 変更内容                                                             |

|----------|-------|------|------------------------------------------------------------------|

| 2010年11月 | 01.0  | _    | 初版                                                               |

| 2011年4月  | 01.1  | 14   | 待機時の電力に関する記述を追加                                                  |

| 2011年6月  | 01.1b | 4    | 表 8-3 バンドギャップと POR に関する説明の " デザインプランナの グローバル Tab でオフにできる " 記述を削除 |

| 2012年10月 | 01.3  | 4    | 表 8-3、上二行の値とデフォルトを修正                                             |

|          |       |      |                                                                  |