# Lattice **CORE**

# **DDR2 SDRAM Controller IP Core User's Guide**

# **Table of Contents**

| Chapter 1. Introduction                                   | 5 |

|-----------------------------------------------------------|---|

| Quick Facts                                               | 5 |

| Features                                                  | 5 |

| Chapter 2. Functional Description                         | 7 |

| Command Decode Logic                                      |   |

| Configuration Interface                                   |   |

| sysCLOCK PLL                                              |   |

| Data Path Logic                                           |   |

| Initialization State Machine                              |   |

| Command Application Logic                                 |   |

| DDR2 PHY                                                  |   |

| Signal Descriptions                                       |   |

| Using the Local User Interface                            |   |

| Initialization and Auto-Refresh Control                   |   |

| Command and Address                                       |   |

| Data Write                                                |   |

| Data Read                                                 |   |

| Read/Write with Auto Precharge                            |   |

| Local-to-Memory Address Mapping                           |   |

| Mode Register Programming                                 |   |

| Memory Interface                                          |   |

| Chapter 3. Parameter Settings                             |   |

| DDR2 GUI                                                  |   |

| Controller Settings Tab                                   |   |

| I/O Gearing Selection                                     |   |

| Parameter Settings                                        |   |

| Auto Refresh Control                                      |   |

| Controller Features                                       |   |

| Location Settings                                         |   |

| Memory Settings Tab                                       |   |

| DRAM Configurations                                       |   |

| Initial Mode Register Settings                            |   |

| DIMM Configurations                                       |   |

| Timing Parameters Setting                                 |   |

| Synthesis & Simulation Tools Option Tab                   |   |

| Info Tab                                                  |   |

| Chapter 4. IP Core Generation.                            |   |

| Licensing the IP Core                                     |   |

| Getting Started                                           |   |

| IPexpress-Created Files and Top Level Directory Structure |   |

| Generated Files                                           |   |

| DDR2 SDRAM Controller Core Structure                      |   |

| Top-level Wrapper                                         |   |

| Encrypted Netlist                                         |   |

| I/O Modules                                               |   |

| Clock Generator                                           |   |

| Parameter File                                            |   |

| Core Header File                                          |   |

| Preference Files                                          |   |

|                                                           |   |

© 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Evaluation Project Files             | 31 |

|--------------------------------------|----|

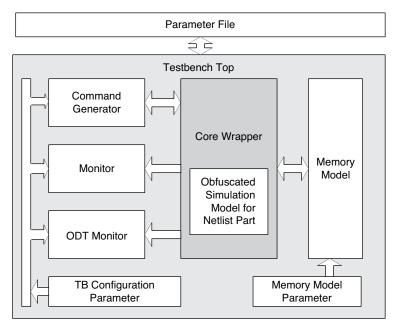

| Simulation Files for Core Evaluation | 31 |

| Test Bench Top                       |    |

| Obfuscated Core Simulation Model     |    |

| Command Generator                    |    |

| Monitor                              |    |

| TB Configuration Parameter           |    |

| Memory Model                         |    |

| Memory Model Parameter               |    |

| Evaluation Script File               |    |

| Hardware Evaluation                  |    |

| Updating/Regenerating the IP Core    |    |

| Chapter 5. Application Support       |    |

| Core Implementation                  |    |

| Understanding Preferences            |    |

| Preference Localization              |    |

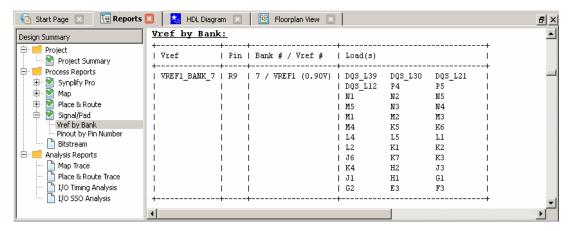

| VREF Assignments                     |    |

| DLL Allocation                       |    |

| I/O Types for DDR2                   |    |

| Skew Treatment                       |    |

| DQS Postamble Handling               |    |

| Data Valid Generation                |    |

| Dummy Logic                          |    |

| Read Data Auto-Alignment Logic       |    |

| PCB Routing Delay Compensation       |    |

| Setting read_pulse_tap               |    |

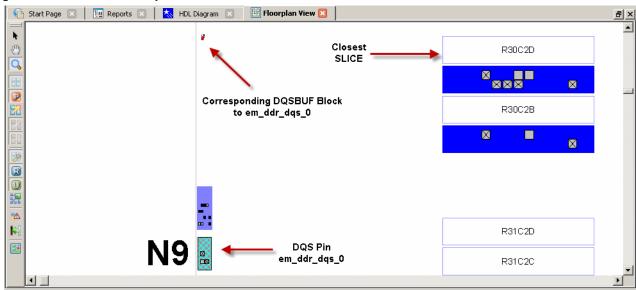

| DQS_PIO_READ Locate Constraints      |    |

| Obtaining Location Values            |    |

| Troubleshooting                      |    |

| Chapter 6. Core Verification         |    |

| Chapter 7. Support Resources         |    |

| •                                    |    |

| Lattice Technical Support            |    |

| Online Forums                        |    |

| Telephone Support Hotline            |    |

| E-mail Support                       |    |

| Local Support                        |    |

| Internet                             |    |

| References                           |    |

| LatticeECP3                          |    |

| LatticeECP2/M                        |    |

| LatticeECP, LatticeXP                |    |

| LatticeXP2                           |    |

| LatticeSC/M                          |    |

| Revision History                     |    |

| Appendix A. Resource Utilization     |    |

| LatticeECP3 FPGAs                    |    |

| Ordering Part Number                 |    |

| LatticeECP2M/S FPGAs                 |    |

| Ordering Part Number                 |    |

| LatticeECP2/S FPGAs                  |    |

| Ordering Part Number                 |    |

| LatticeXP2 Devices                   |    |

| Ordering Part Number                 | 46 |

| LatticeSC/M FPGAs    | ⊿ | 16 |

|----------------------|---|----|

| Ordering Part Number | 4 | ۱F |

# Introduction

The Double Data Rate 2 (DDR2) Synchronous Dynamic Random Access Memory (SDRAM) Controller is a general-purpose memory controller that interfaces with industry standard DDR2 memory devices/modules and provides a generic command interface to user applications. This IP core reduces the efforts required to integrate the DDR2 memory controller with the remainder of the application and minimizes the need to deal with the DDR2 memory interface. This core utilizes dedicated DDR input and output registers in the Lattice FPGA devices to meet the requirements for high-speed double data rate transfers. The timing parameters for a memory device or module can be set through the signals that are input to the core as a part of the configuration interface. This capability enables effortless switching among different memory devices by updating the timing parameters to suit the application without generating a new core configuration.

Note: This user's guide is intended for use with DDR2 SDRAM Controller version 8.0 and later. For all previous versions, please refer to IPUG35, DDR & DDR2 SDRAM Controller IP Cores User's Guide.

#### **Quick Facts**

Table 1-1 gives quick facts about the DDR2 SDRAM Controller IP core.

Table 1-1. DDR2 SDRAM Controller IP Core Quick Facts

|              |                            | DDR2 IP Configuration |                               |                      |                       |                        |                       |                          |  |

|--------------|----------------------------|-----------------------|-------------------------------|----------------------|-----------------------|------------------------|-----------------------|--------------------------|--|

|              | -                          | x32 1cs               | x64 1cs                       | x72 1cs              | x32 1cs               | x64 1cs                | x32 1cs               | x64 1cs                  |  |

| Core         | FPGA Families<br>Supported |                       | LatticeECP                    | Lattice SC/M         |                       |                        |                       |                          |  |

| Requirements | Minimum Device<br>Needed   | LFE2-6E-<br>5F256C    | LFE2M20E-<br>5F256C           | LFXP2-5E-<br>5TN144C | LFE3-70E-<br>6FN484C  | LFE3-17EA-<br>6FN484C  | LFSC3GA15E-<br>5F256C | LFSCM3GA15E<br>P1-5F256C |  |

|              | Target device              | LFE2-50E-<br>6F672C   | LFE2M35E-<br>6F672C           | LFXP2-17E-<br>6F484C | LFE3-95E-<br>7FN1156C | LFE3-95EA-<br>7FN1156C | LFSC3GA25E-<br>6F900C | LFSCM3GA25E<br>P1-6F900C |  |

| Resource     | Data Path Width            | 32                    | 64                            | 72                   | 32                    | 64                     | 32                    | 64                       |  |

| Utilization  | LUTs                       | 1450                  | 1750                          | 1800                 | 1400                  | 1700                   | 1500                  | 1700                     |  |

|              | sysMEM EBRs                | 0                     | 0                             | 0                    | 0                     | 0                      | 0                     | 0                        |  |

|              | Registers                  | 1550                  | 2100                          | 2250                 | 1600                  | 2200                   | 1550                  | 1950                     |  |

|              | Lattice<br>Implementation  |                       |                               | L                    | attice Diamond® 2     | .0                     |                       |                          |  |

| Design Tool  | 0 11 .                     |                       |                               | Synopsys Sy          | nplify Pro for Lattic | ce F2012.03L           |                       |                          |  |

| Support      | Synthesis                  |                       | Mentor Graphics Precision RTL |                      |                       |                        |                       |                          |  |

|              | Simulation                 |                       |                               | Aldec Ac             | tive-HDL 9.1 Lattic   | e Edition              |                       |                          |  |

|              | Simulation -               |                       |                               | Mentor C             | Graphics ModelSim     | SE 6.6D                |                       |                          |  |

#### **Features**

- Interfaces to industry standard DDR2 SDRAM devices and modules

- High-performance DDR2 800/667/533/400 operation for LatticeECP3 (1:4 gearing); DDR2 533/400/333/266/200/133 operation for LatticeECP3 (1:2 gearing), LatticeECP2/M, LatticeECP2/MS and Lattice-SC/M devices; and DDR2 400/333/266/200/133 operation for LatticeXP2 devices.

**Note:** Actual DDR2 memory specifications may not support the core's slower speed DDR2 operation (200/133). For the LatticeSC/M devices, see also TN1099, LatticeSC/M DDR/DDR2 SDRAM Memory Interface User's Guide.

- Programmable burst length of 8

- Programmable CAS latency of 3, 4, 5 or 6 cycles

- Intelligent bank management to optimize performance by minimizing ACTIVE commands

- Supports all JEDEC standard DDR2 commands

- Two-stage command pipeline to improve throughput

- · Supports both registered and unbuffered DIMM

- Command burst function with dynamic burst size control

- Supports all common memory configurations

- SDRAM data path widths of 8, 16, 24, 32, 40, 48, 56, 64 and 72 bits

- Variable address widths for different memory devices

- Up to four chip selects for multiple SO/DIMM support

- Programmable memory timing parameters

- Byte-level writing through data mask signals

# **Functional Description**

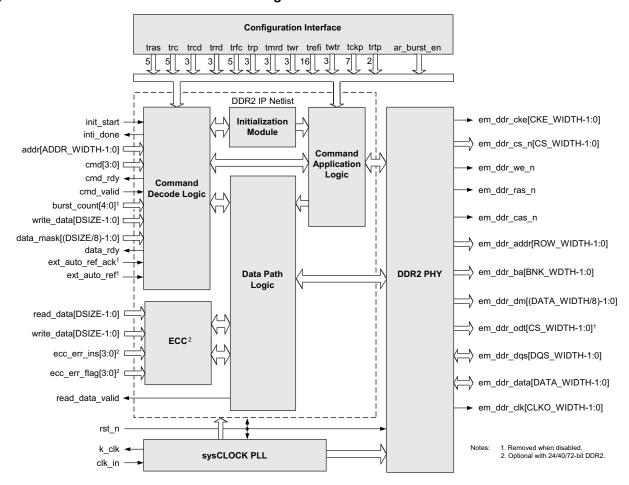

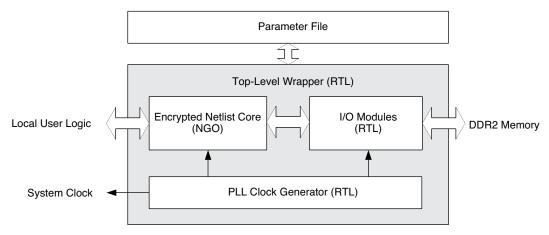

The DDR2 memory controller consists of two major parts, the encrypted netlist and I/O modules. The encrypted netlist comprises several internal blocks, as shown in Figure 2-1. The device architecture-dependent I/O modules are provided in RTL form. This section briefly describes the operation of each of these blocks.

Figure 2-1. DDR2 SDRAM Controller Block Diagram

#### **Command Decode Logic**

The Command Decode Logic (CDL) block accepts the user commands from the local interface. The accepted command is decoded to determine how the core will act to access the memory. When an accepted command is decoded as a write command, the CDL block asks the user logic to provide the write data. Once it receives the write data from the user logic, the CDL block delivers a write command to the Command Application Logic (CAL) block and the data is sent to the Data Path Logic (DPL) block. Similarly, when the accepted command is a read command, the CDL block sends a read command to the DPL block to generate a read command on the memory interface. The data read from memory is presented to the local user interface.

The CDL block also provides the command burst function that automatically repeats a user command up to the number of times specified via a user input. Intelligent bank management logic tracks the open/close status of every bank and stores the row address of every open bank. This information is used to reduce the number of PRE-CHARGE and ACTIVE commands issued to the memory. The controller also utilizes two pipelines to improve throughput. One command in the queue is decoded while another is presented at the memory interface.

### **Configuration Interface**

The Configuration Interface (CI) block provides the DDR2 memory controller with the core reconfiguration capability for the memory timing parameters and other core configuration inputs. The configuration interface for the memory timing parameters can be enabled or disabled via a user parameter. When enabled, the DDR2 SDRAM Controller IP core can be reconfigured with an updated set of the memory timing parameters in the parameter file without generating a new IP core. When disabled, the reconfiguration logic is permanently removed from the core. It is generally expected that the IP core performance will be improved due to a lower utilization.

### sysCLOCK PLL

The sysCLOCK<sup>™</sup> PLL block generates the clocks used in all blocks in the DDR2 SDRAM Controller IP core and provides the system clock to the user logic. If an external clock generator is to be used, it is possible to remove this block from the IP core structure.

### **Data Path Logic**

The DPL block interfaces with the DDR2 I/O modules and is responsible for generation of the read data and read data valid signal in the read operation mode. This block implements the logic to ensure that the data read from the memory is transferred to the local user interface in a deterministic and coherent manner. The write data does not go through the DPL block; it is directly transferred to the Command Application Logic (CAL) block for the write operation mode. The implementation of the DPL block is also device dependent.

#### **Initialization State Machine**

The Initialization State Machine (ISM) block performs the DDR2 memory initialization sequence defined by JEDEC. Although the memory initialization must be done after the power-up, it is the user's responsibility to provide a user input to the block to start the memory initialization sequence. The ISM block provides an output that indicates the completion of the sequence to the local user interface.

### **Command Application Logic**

The CAL block accepts the decoded commands from the Command Decode Logic on two separate queues. These commands are translated to the memory commands in a way that meets the timing requirements of the memory device. The CI block provides the memory timing parameters to the CAL block so that the timing requirements are satisfied during the command translations. Commands in the two stage queues are pipelined to maximize the throughput on the memory interface. The CDL and the CAL blocks work in parallel to fill and empty the queues respectively.

### **DDR2 PHY**

The DDR2 PHY are directly connected to the memory interface providing all required DDR ports for memory access. They convert the single data rate (SDR) data to DDR data for write operations and perform the DDR to SDR conversion for read operations. The PHY utilize the dedicated FPGA DDR I/O logic and are designed to reliably drive and capture the data on the memory interface.

# **Signal Descriptions**

Table 2-1 describes the user interface and memory interface signals at the top level.

Table 2-1. DDR2 SDRAM Controller Top-Level I/O List

| Port Name                 | Active State I/O Desc |        | Description                                                                                                                                                                                                             |  |  |

|---------------------------|-----------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Local User Interface      | I                     | I.     |                                                                                                                                                                                                                         |  |  |

| clk_in                    | N/A                   | Input  | Reference clock. It is connected to the PLL input.                                                                                                                                                                      |  |  |

| sclk                      | N/A                   | Input  | System clock. It is connected to the PLL output (1:2 gearing) or CLK-DIVD output (1:4 gearing).                                                                                                                         |  |  |

| eclk_2x                   | N/A                   | Input  | Edge clock for DDR2 PHY use. It is connected to the ECLKSYNCB output. This port is only for LatticeECP3 devices (1:4 gearing).                                                                                          |  |  |

| k_clk                     | N/A                   | Input  | System clock. It is connected to the PLL output.                                                                                                                                                                        |  |  |

| k1_clk                    | N/A                   | Input  | System clock, 270-degree phase shift from k_clk. It is connected to the PLL output. This port is only for LatticeECP3 devices (1:2 gearing).                                                                            |  |  |

| k4_clk                    | N/A                   | Input  | System clock, 90-degree phase shift from k_clk. It is connected to the PLL output. This port is only for LatticeSC/SCM devices.                                                                                         |  |  |

| rst_n                     | Low                   | Input  | Asynchronous reset. It resets the entire core when asserted.                                                                                                                                                            |  |  |

| init_start                | High                  | Input  | Initialization start. It should be asserted at least 200µs after the power-on reset to initiate the memory initialization.                                                                                              |  |  |

| cmd[3:0]                  | N/A                   | Input  | User command input to the memory controller.                                                                                                                                                                            |  |  |

| cmd_valid                 | High                  | Input  | Command and address valid input. When asserted, the addr, cmd and burst_count inputs are validated.                                                                                                                     |  |  |

| addr[ADDR_WIDTH -1:0]     | N/A                   | Input  | User address input to the memory controller.                                                                                                                                                                            |  |  |

| burst_count[4:0]          | N/A                   | Input  | Command burst count input. It indicates the number of repeats of a given read or write command. The command burst feature is enabled when BRST_CNT_EN is defined. If not defined, burst_count is removed from the core. |  |  |

| write_data[DSIZE -1:0]    | N/A                   | Input  | Write data input from user logic to the memory controller.                                                                                                                                                              |  |  |

| data_mask[(DSIZE/8) -1:0] | High                  | Input  | Data mask input for write_data. Each bit masks the corresponding byte on the write_data bus, in order.                                                                                                                  |  |  |

| ext_auto_ref              | High                  | Input  | User auto-refresh control input. This port is enabled when EXT_AUTO_REF is defined.                                                                                                                                     |  |  |

| k_clk_out                 | N/A                   | Output | System clock output.                                                                                                                                                                                                    |  |  |

| init_done                 | High                  | Output | Initialization done output. It is asserted for one clock cycle when the core completes the memory initialization routine.                                                                                               |  |  |

| ext_auto_ref_ack          | High                  | Output | User auto-refresh control acknowledge output. This port is enabled when EXT_AUTO_REF is defined.                                                                                                                        |  |  |

| cmd_rdy                   | High                  | Output | Command ready output. When asserted, it indicates the core is ready to accept the next command and address.                                                                                                             |  |  |

| data_rdy                  | High                  | Output | Data ready output. When asserted, it indicates the core is ready to receive the write data.                                                                                                                             |  |  |

| read_data[DSIZE -1:0]     | N/A                   | Output | Read data output from the memory to the user logic.                                                                                                                                                                     |  |  |

| read_data_valid           | High                  | Output | Read data valid output. When asserted, it indicates the data on the read_data bus is valid.                                                                                                                             |  |  |

| read_pulse_tap            | N/A                   | Input  | This signal is used for PCB routing delay compensation, to guarante that the falling edge of "dqs_pio_read" signal is placed in the prean ble of the incoming DQS signal.                                               |  |  |

| uddcntl_n                 | N/A                   | Output | Update control. It is connected to the DQSDLL input. This port is only for LatticeECP3, LatticeECP2/S, LatticeECP2M/MS and LatticeXP2 devices.                                                                          |  |  |

Table 2-1. DDR2 SDRAM Controller Top-Level I/O List (Continued)

| Port Name                      | Active<br>State | I/O    | Description                                                                                                                                |

|--------------------------------|-----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------|

| dqsdel                         | High            | Input  | DQS delay. It is connected to the DQSDLL output. This port is only for LatticeECP3, LatticeECP2/S, LatticeECP2M/MS and LatticeXP2 devices. |

| DDR2 SDRAM Memory Interface    |                 |        |                                                                                                                                            |

| em_ddr_clk[CLKO_WIDTH -1:0]    | N/A             | Output | DDR2 memory clock generated by the memory controller.                                                                                      |

| em_ddr_cke[CKE_WIDTH -1:0]     | High            | Output | DDR2 memory clock enable generated by the memory controller.                                                                               |

| em_ddr_addr[ROW_WIDTH -1:0]    | N/A             | Output | DDR2 memory address. It has the multiplexed row and column address for the memory.                                                         |

| em_ddr_ba[BNK_WDTH -1:0]       | N/A             | Output | DDR2 memory bank address.                                                                                                                  |

| em_ddr_data[DATA_WIDTH -1:0]   | N/A             | In/Out | DDR2 memory bi-directional data bus.                                                                                                       |

| em_ddr_dm[(DATA_WIDTH/8) -1:0] | High            | Output | DDR2 memory write data mask. It is used to mask the byte lanes for byte level write control.                                               |

| em_ddr_dqs[(DQS_WIDTH -1:0]    | N/A             | In/Out | DDR2 memory bi-directional data strobe. This strobe signal is associated with either 4 or 8 data pads.                                     |

| em_ddr_cs_n[CS_WIDTH -1:0]     | Low             | Output | DDR2 memory chip select.                                                                                                                   |

| em_ddr_cas_n                   | Low             | Output | DDR2 memory column address strobe.                                                                                                         |

| em_ddr_ras_n                   | Low             | Output | DDR2 memory row address strobe.                                                                                                            |

| em_ddr_we_n                    | Low             | Output | DDR2 memory write enable.                                                                                                                  |

| em_ddr_odt[CS_WIDTH -1:0]      | High            | Output | DDR2 memory on-die termination control.                                                                                                    |

## **Using the Local User Interface**

The local user interface of the DDR2 SDRAM Controller IP core consists of four independent functional groups:

- Initialization and Auto-Refresh Control

- · Command and Address

- Data Write

- Data Read

Each functional group and its associated local interface signals are listed in Table 2-2.

Table 2-2. Local User Interface Functional Groups

| Functional Group                        | Signals                                               |  |  |

|-----------------------------------------|-------------------------------------------------------|--|--|

| Initialization and Auto-Refresh Control | init_start, init_done, ext_auto_ref, ext_auto_ref_ack |  |  |

| Command and Address                     | addr, cmd, cmd_rdy, cmd_valid                         |  |  |

| Data Write                              | data_rdy, write_data, data_mask                       |  |  |

| Data Read                               | read_data, read_data_valid                            |  |  |

#### Initialization and Auto-Refresh Control

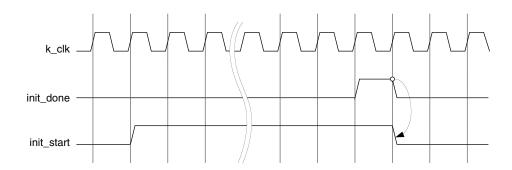

The DDR2 memory devices must be initialized before the memory controller can access them. The memory controller starts the memory initialization sequence when the init\_start signal is asserted by the user interface. The user must wait at least 200 µs after the power-up cycle is completed and the system clock is stabilized, and then generate the initialization start input to the core. Once asserted, the init\_start signal needs to be held high until the initialization process is completed. The init\_done signal is asserted high for one clock cycle when the core has completed the initialization sequence and is now ready to access the memory. The init\_start signal must be deasserted as soon as init done is asserted. The memory initialization is required only once after the system reset.

Note that the core will operate with the default memory configuration initialized in this process if the user does not program the MR and/or EMR registers. Figure 2-2 shows the timing diagram of the initialization control signals.

Figure 2-2. Timing of Memory Initialization Control

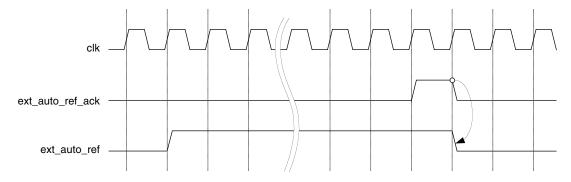

The DDR2 SDRAM Controller IP core provides the user auto-refresh control feature. This feature can be enabled by the External Auto Refresh Port option. It is a useful function for applications that need to have a complete control on the DDR2 interface in order to avoid unwanted intervention caused by the memory refresh operations. Once enabled, ext\_auto\_ref is asserted by a user to force the core to generate a set of Refresh commands in a burst. The number of Refresh commands in a burst is defined by the Auto Refresh Burst Count option. The ext\_auto\_ref\_ack signal is asserted high for one clock cycle to indicate that the core has generated the Refresh commands. The ext\_auto\_ref signal can be deasserted once the acknowledge signal is detected as shown in Figure 2-3.

Figure 2-3. Timing of External Auto Refresh Control

### **Command and Address**

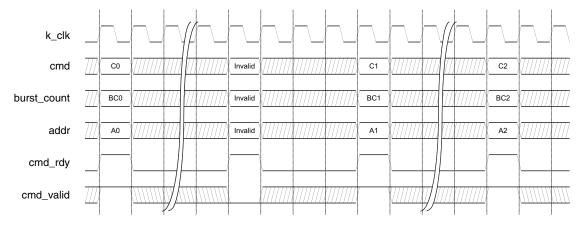

Once the memory initialization is done, the core waits for user commands that will access the memory. The user logic needs to provide the command and address to the core along with the control signals. The commands and addresses are delivered to the core using the procedure described below:

- 1. DDR2 SDRAM Controller IP core tells the user logic that it is ready to receive a command by asserting the cmd\_rdy signal for one clock cycle.

- 2. If the core finds the cmd\_valid signal asserted by the user logic while it is asserting cmd\_rdy, it takes the cmd input as a valid user command. The core also accepts the addr input as a valid start address or mode register programming data depending on the command type. If cmd\_valid is not asserted, the cmd and addr inputs become invalid and the core ignores them.

- 3. The cmd, addr and cmd\_valid inputs become "don't care" while cmd\_rdy is deasserted.

4. The cmd\_rdy signal is asserted again to take the next command.

Note: The first read command issued on the local user interface is a dummy transaction used to initialize the receive physical layer logic. Data will not be returned from the memory until the second read request.

When the core is in the command burst operation, it extensively occupies the data bus. While the core is operating in the command burst mode, it can keep maximum throughput by internally repeating the command. The command burst can be enabled by checking the "Command Burst Enable" box in the Controller Settings tab of the IPexpress GUI.

When command burst is enabled, the memory controller can repeat the given READ or WRITE command up to 32 times. The burst\_count[4:0] input port is used to set the number of repeats of the given command, it indicates the number of memory BL (DDR2 memory burst length), for example, if DQ width is 8bit, burst\_count is 2, BL is 4, then the data length for each write or read command from user should be DQ width \* burst\_count \* BL = 8\*2\*4=64 bit= 8 byte.

The core allows the command burst function to access the memory addresses within the current page. When the core reaches the boundary of the current page while accessing the memory in the command burst mode, the next address that the core will access will be the beginning of the same page, causing it to overwrite the contents of the location or read unexpected data. Therefore, the user must track the accessible address range in the current page while the command burst operation is performed. If an application requires a fixed command burst size, use of 2-, 4-, 8-, 16- or 32-burst. It is recommended to ensure that the command burst accesses do not cross the page boundary. Note that the value '00000' stands for '32'.

When command burst is disabled, the burst\_count port is removed from the core, and the core will always consider the burst\_count as "1" internally.

The burst\_count input is sampled the same way as cmd. The timing of the Command and Address group is shown in Figure 2-4. The timing for burst count in Figure 2-4 shows only the sampling time of the bus. When burst\_count is sampled with a value other than "00001", the core will prevent cmd\_rdy from being asserted when two queues in CDL are both occupied, if any queue in CDL is empty, the cmd\_rdy will be asserted, whatever the command burst is completed or not.

Each command on the cmd bus must be a valid command. Lattice defines the valid memory commands as shown in Table 2-3. All other values are reserved and considered invalid.

Table 2-3. Defined User Commands

| Command                   | Mnemonic | cmd[3:0] |

|---------------------------|----------|----------|

| Read                      | READ     | 0001     |

| Write                     | WRITE    | 0010     |

| Read with Auto Precharge  | READA    | 0011     |

| Write with Auto Precharge | WRITEA   | 0100     |

| Powerdown                 | PDOWN    | 0101     |

| Load Mode Register        | LOAD_MR  | 0110     |

| Self Refresh              | SELF_REF | 0111     |

#### **Data Write**

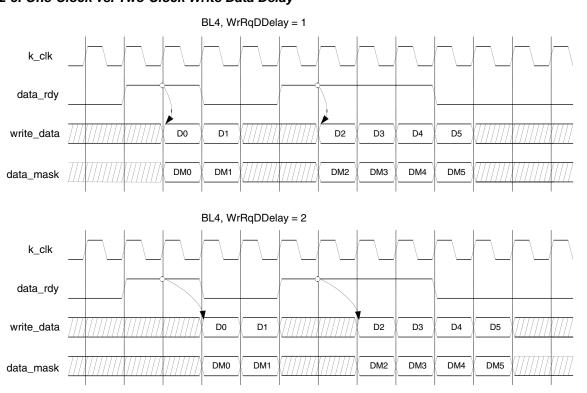

After the WRITE command is accepted, the DDR2 SDRAM Controller IP core asserts the data\_rdy signal when it is ready to receive the write data from the user logic to be written into the memory. Since the duration from the time a write command is accepted to the time the data\_rdy signal is asserted is not fixed, the user logic needs to monitor the data\_rdy signal to detect when it is asserted. Once data\_rdy is asserted, the core expects valid data on the write\_data bus one or two clock cycles after the data\_rdy signal is asserted. The write data delay is programmable by the user parameter, WrRqDDelay, providing flexible back-end application support. For example, setting WrRqDDelay = 2 ensures that the core takes the write data out in proper time when the local user interface of the core is connected to a synchronous FIFO module inside the user logic. All devices support WrRqDDelay 1/2. Figure 2-5 shows two examples of the local user interface data write timing. Both cases are in the BL4 mode. The upper diagram shows the case of one clock cycle delay of write data, while the lower one displays a two clock-cycle delay case. The memory controller considers D0, DM0 through D5, DM5 valid write data.

Figure 2-5. One-Clock vs. Two-Clock Write Data Delay

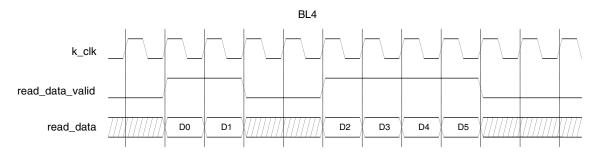

#### **Data Read**

When the READ command is accepted, the DDR2 SDRAM Controller IP core accesses the memory to read the addressed data and brings it back to the local user interface. Once the read data is available on the local user interface, the DDR2 SDRAM Controller IP core asserts the read\_data\_valid signal to tell the user logic that the valid read data is on the read\_data bus. The read data timing on the local user interface is shown in Figure 2-6.

Figure 2-6. Read Data Timing on Local User Interface

### Read/Write with Auto Precharge

The DDR2 SDRAM Controller IP core automatically closes (precharges) and opens rows according to the user memory address accesses. Therefore, the READA and WRITEA commands are not used for most applications. The commands are provided to comply to the JEDEC DDR2 specification.

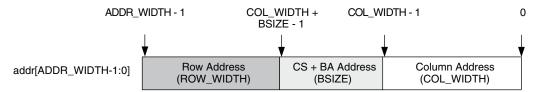

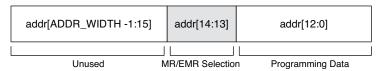

### **Local-to-Memory Address Mapping**

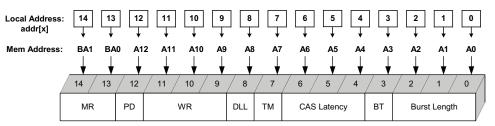

Mapping local addresses to memory addresses is an important part of a system design when a memory controller function is implemented. Users must know how the local address lines from the memory controller connect to those address lines from the memory because proper local-to-memory address mapping is crucial to meet the system requirements in applications such as a video frame buffer controller. Even for other applications, careful address mapping is generally necessary to optimize the system performance. On the memory side, the address (A), bank address (BA) and chip select (CS) inputs are used for addressing a memory device. Users can obtain this information from the memory device data sheet. Figure 2-7 shows the local-to-memory address mapping of the DDR2 SDRAM Controller IP core.

Figure 2-7. Local-to-Memory Address Mapping for Memory Access

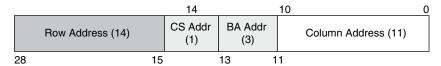

ADDR\_WIDTH is calculated by the sum of COL\_WIDTH, ROW\_WIDTH and BSIZE. BSIZE is determined by the sum of the bank address size and chip select address size. For 4- or 8-Bank DDR2 devices, the bank address size is 2 or 3, respectively. When the number of chip select is 1, 2 or 4, the chip select address size becomes 0, 1, or 2, respectively. An example of the address mapping is shown in Table 2-4 and Figure 2-8.

Table 2-4. An Example of Address Mapping

| User Selection Name           | User Value | Parameter Name | Parameter Value | Actual Line Size | Local Address Map |

|-------------------------------|------------|----------------|-----------------|------------------|-------------------|

| Row Size                      | 14         | ROW_WIDTH      | 14              | 14               | addr[28:15]       |

| Column Size                   | 11         | COL_WIDTH      | 11              | 11               | addr[10:0]        |

| Bank Size                     | 8          | BNK_WDTH       | 3               | 3                | addr[13:11]       |

| Chip Select Width             | 2          | CS_WIDTH       | 2               | 1                | addr[14]          |

| Total Local Address Line Size |            | ADDR_WIDTH     | 29              | 29               | addr[28:0]        |

Figure 2-8. Mapped Address for the Example

### **Mode Register Programming**

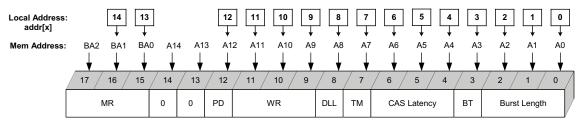

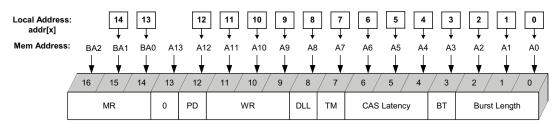

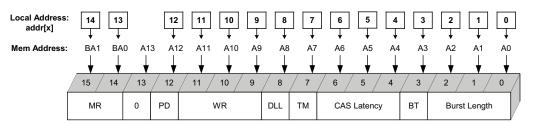

The DDR2 SDRAM memory devices are programmed using the mode register (MR) and extended mode registers (EMR). The bank address bus (em\_ddr\_ba) is used for choosing one of the MR or EMR registers, while the programming data is delivered through the address bus (em\_ddr\_addr). The memory data bus cannot be used for the MR/EMR programming.

The DDR2 SDRAM Controller IP core uses the local address bus, addr, to program these registers. It uses different address mapping from the address mapping for memory accesses. The core accepts a user command, LOAD\_MR, to initiate the programming of MR/EMR registers. When LOAD\_MR is applied on the cmd bus, the user logic must provide the information for a target mode register and the programming data on the addr bus. When the target mode register is programmed, the DDR2 SDRAM Controller IP core is also configured to support the new memory setting. Figure 2-9 shows how the local address lines are allocated for the programming of memory registers.

Figure 2-9. Local-to-Memory Address Mapping for MR/EMR Programming

The register programming data is provided through the lower side of the addr bus starting from the bit 0 for LSB. The programming data requires 13 bits of the local address lines. Two more bits are needed to choose a target register as listed in Table 2-5. All other upper address lines are unused during the command patch cycle for the LOAD\_MR command.

Table 2-5. Mode Register Selection Using Bank Address

|               | Local Address      |  |  |  |

|---------------|--------------------|--|--|--|

| Mode Register | DDR2 (addr[14:13]) |  |  |  |

| MR            | 00                 |  |  |  |

| EMR           | 01                 |  |  |  |

| EMR2          | 10                 |  |  |  |

| EMR3          | 11                 |  |  |  |

Figure 2-10 shows the use of local address for typical DDR2 memory configurations. Starting from DDR2 version 6.7, some of the registers such as Burst Type, Burst Length, CAS Latency and others can be configured directly from the IPexpress GUI for custom initialization.

The initialization default values for all mode registers are listed in Table 2-6.

Table 2-6. Initialization Default Values for DDR2 Mode Registers

| Туре                                       | Registers                     | Value  | Description           | Local address        |

|--------------------------------------------|-------------------------------|--------|-----------------------|----------------------|

|                                            | Burst Length <sup>1</sup>     | 3'b010 | BL = 4                | addr[2:0]            |

|                                            | Burst Type <sup>1</sup>       | 1'b0   | Sequential            | addr[3]              |

|                                            | Cas Latency <sup>1</sup>      | 3'b100 | CL = 4 Cycles         | addr[6:4]            |

| DDR2 MR (BA[1:0] = 00 or                   | Test Mode                     | 1'b0   | Normal                | addr[7]              |

| BA[2:0]=000)                               | DLL Reset                     | 1'b1   | DLL Reset = Yes       | addr[8]              |

|                                            | WR Recovery <sup>1</sup>      | 3'b010 | 3 Cycles              | addr[11:9]           |

|                                            | Power Down Exit <sup>1</sup>  | 1'b0   | Fast                  | addr[12]             |

|                                            | All Others                    | 0      |                       | addr[ROW_WIDTH-1:13] |

|                                            | DLL                           | 1'b0   | DLL Enable            | addr[0]              |

|                                            | Drive Strength                | 1'b0   | Normal                | addr[1]              |

|                                            | RTT0 <sup>1</sup>             | 1'b0   | Disabled with RTT1=0  | addr[2]              |

|                                            | Additive Latency <sup>1</sup> | 3'b011 | 3 Cycles              | addr[5:3]            |

| DDR2 EMR (BA[1:0] = 01 or                  | RTT1 <sup>1</sup>             | 1'b0   | Disabled with RTT0=0  | addr[6]              |

| BA[2:0]=001)                               | OCD                           | 3'b000 | OCD Not Applicable    | addr[9:7]            |

|                                            | DQS Mode                      | 1'b1   | Differential Disabled | addr[10]             |

|                                            | RDQS                          | 1'b0   | Disable               | addr[11]             |

|                                            | Outputs                       | 1'b0   | Enable                | addr[12]             |

|                                            | All Others                    |        |                       | addr[ROW_WIDTH-1:13] |

| DDR2 EMR2 (BA[1:0] = 10 or<br>BA[2:0]=010) | All                           | 0      |                       | addr[ROW_WIDTH-1:0]  |

| DDR2 EMR3 (BA[1:0] = 11 or<br>BA[2:0]=011) | All                           | 0      |                       | addr[ROW_WIDTH-1:0]  |

<sup>1.</sup> This register can be initialized with a custom value through the IPexpress GUI.

Figure 2-10. Local Address Mapping for MR Programming (Typical DDR2 Memory Configurations)

Row Size = 15, Bank Size = 8 (2Gb)

Row Size = 14, Bank Size = 8 (1Gb)

Row Size = 14, Bank Size = 4 (512Mb)

Row Size = 13, Bank Size = 4 (256Mb)

# **Memory Interface**

Table 2-7 lists the connections of the DDR2 interface between the DDR2 SDRAM Controller IP core and memory.

Table 2-7. DDR2 Interface Signal Connections to DDR2 Memory

|                         | Memory                 |              | VREF <sup>2</sup> |                           | I/O Type   |                                      |

|-------------------------|------------------------|--------------|-------------------|---------------------------|------------|--------------------------------------|

| Core Port Name          | Port Name <sup>1</sup> | Width        | DDR               | DDR2                      | DDR        | DDR2                                 |

| em_ddr_clk <sup>3</sup> | CK, CK#                | CLKO_WIDTH   | _                 | _                         | SSTL25D_II | SSTL18D_II                           |

| em_ddr_cke              | CKE                    | CKE_WIDTH    | _                 | _                         | SSTL25_II  | SSTL18_II                            |

| em_ddr_odt              | ODT                    | CS_WIDTH     | _                 | _                         | N/A        | SSTL18_II                            |

| em_ddr_cs_n             | CS#                    | CS_WIDTH     | _                 | _                         | SSTL25_II  | SSTL18_II                            |

| em_ddr_ras_n            | RAS#                   | 1            | _                 | _                         | SSTL25_II  | SSTL18_II                            |

| em_ddr_cas_n            | CAS#                   | 1            | _                 | _                         | SSTL25_II  | SSTL18_II                            |

| em_ddr_we_n             | WE#                    | 1            | _                 | _                         | SSTL25_II  | SSTL18_II                            |

| em_ddr_addr             | Α                      | ROW_WIDTH    | _                 | _                         | SSTL25_II  | SSTL18_II                            |

| em_ddr_ba               | BA                     | BNK_WDTH     | _                 | _                         | SSTL25_II  | SSTL18_II                            |

| em_ddr_data/em_ddr_dq   | DQ                     | DATA_WIDTH   | 1.25V             | 0.9V                      | SSTL25_II  | SSTL18_II                            |

| em_ddr_dm               | DM                     | DATA_WIDTH/8 | _                 | _                         | SSTL25_II  | SSTL18_II                            |

| em_ddr_dqs              | DQS                    | DQS_WIDTH    | 1.25V             | 0.9V or none <sup>4</sup> | SSTL25_II  | SSTL18_II or SSTL18D_II <sup>5</sup> |

<sup>1.</sup> The listed DDR2 memory port names are from the Micron DDR2 memory data sheet.

<sup>2.</sup> In the banks with multiple VREFs, only VREF1 is used for DDR2 memory applications. VREF = VCCIO/2.

<sup>3.</sup> The DDR2 SDRAM Controller IP core defines only the positive-end signal for the memory clock. The negative-end pad is allocated by the implementation software when a differential I/O type is assigned.

<sup>4.</sup> If DQS uses a differential pair, VREF is not required. However, VREF1 is still used for the DQS preamble detection.

<sup>5.</sup> Either single-ended or differential type of DQS can be selected.

# **Parameter Settings**

The IPexpress<sup>™</sup> tool is used to create IP and architectural modules in the Diamond software. Refer to "IP Core Generation" on page 26 for a description on how to generate the IP.

Table 3-1 provides the list of user configurable parameters for the DDR2 SDRAM Controller IP core. The parameter settings are specified using the DDR2 SDRAM Controller IP core Configuration GUI in IPexpress. The numerous PCI Express parameter options are partitioned across multiple GUI tabs as shown in this chapter.

Table 3-1. DDR2 SDRAM Controller Parameters

| Parameter                               | Range/Options                     | Default Value |

|-----------------------------------------|-----------------------------------|---------------|

| Controller Settings                     | ·                                 | <u> </u>      |

| I/O Gearing Selection                   | 1:2, 1:4                          | 1:2           |

| MEM Data Size                           | 8, 16, 24, 32, 40, 48, 56, 64, 72 | 16            |

| Data Input Delay                        | 1, 2                              | 2             |

| Auto Refresh Burst                      | 1, 2, 3, 4, 5, 6, 7, 8            | 8             |

| Fixed Memory Timing                     | Enable, Disable                   | Enable        |

| Command Burst Enable                    | Enable, Disable                   | Enable        |

| Margin Control                          | Enable, Disable                   | Disable       |

| Error Correction Code modules           | Enable, Disable                   | Disable       |

| Add SMI Port Interface for PLL and DLL1 | Enable, Disable                   | Disable       |

| Memory Settings                         | ·                                 | •             |

| Vendor                                  | Micron, Custom                    | Micron        |

| MEM Size                                | 256Mb, 512Mb, 1Gb, 2Gb, 4Gb       | 256Mb         |

| Organization                            | x4, x8, x16                       | x8            |

| Row Size                                | 13, 14, 15, 16                    | 13            |

| Column Size                             | 9, 10, 11, 12                     | 10            |

| Bank Size                               | 4, 8                              | 4             |

| SPD Grade                               | -5E, -37E, -3E, -25E              | -5E           |

| MEM Clock Frequency                     | 100 MHz - 400 MHz                 | 200 MHz       |

| CAS Latency                             | 2, 3, 4, 5, 6                     | 4             |

| Additive Latency                        | 0, 1, 2, 3, 4                     | 3             |

| Differential DQS                        | Enable, Disable                   | Enable        |

| RTT_NOM (Ohm)                           | Disable, 75ohm, 150ohm, 50ohm     | Disable       |

| Drive Strength                          | Full, Reduced                     | Reduced       |

| Burst Length                            | 4, 8                              | 8             |

| Write Recovery                          | 2, 3, 4, 5, 6                     | 3             |

| Burst Type                              | Sequential, Interleaved           | Sequential    |

| DLL Control for PD                      | Fast Exit, Slow Exit              | Fast Exit     |

| Module                                  | Unbuffered, Registered            | Unbuffered    |

| Туре                                    | Single Rank, Dual Rank            | Single Rank   |

| 2T Mode                                 | Enable, Disable                   | Disable       |

| Clock Width                             | 1, 2                              | 1             |

| CKE Width                               | 1, 2                              | 1             |

| TRAS                                    | 1 - 31                            | 8             |

| TRC                                     | 1 - 31                            | 11            |

Table 3-1. DDR2 SDRAM Controller Parameters

| Parameter                                                                   | Range/Options   | Default Value |

|-----------------------------------------------------------------------------|-----------------|---------------|

| TRP                                                                         | 1 - 7           | 3             |

| TRCD                                                                        | 1 - 7           | 3             |

| TRRD                                                                        | 1 - 7           | 2             |

| TMRD                                                                        | 1 - 7           | 2             |

| TRTP                                                                        | 1 - 3           | 2             |

| TWTR                                                                        | 1 - 7           | 2             |

| TRFC                                                                        | 1 - 127         | 15            |

| TREFI                                                                       | 1 - 65535       | 1563          |

| Synthesis & Simulation Tools Option                                         |                 |               |

| "Support Synplify, Support Precision, Support ModelSim, Support Active-HDL" | Enable, Disable | Enable        |

### **DDR2 GUI**

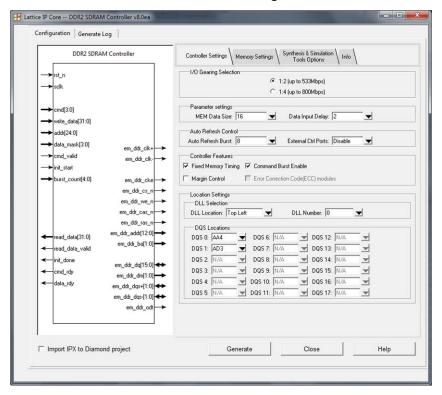

### **Controller Settings Tab**

The Controller Settings Tab includes all DDR2 Memory Controller parameters.

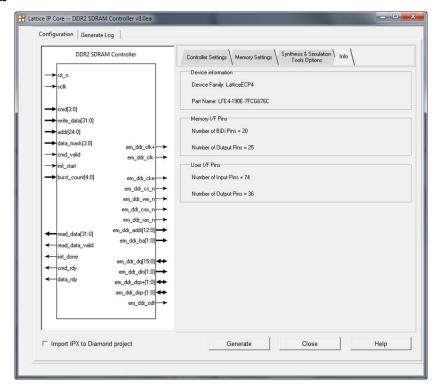

Figure 3-1. DDR2 SDRAM Controller IP Core Controller Settings

### I/O Gearing Selection

For 1:2 mode, the PHY clock frequency equals that of the core logic.

For 1:4 mode, the PHY clock frequency is twice that of the core logic.

### **Parameter Settings**

**MEM Data Size**

This option means the memory data bus width to which the DDR2 SDRAM Controller IP core is connected. If a memory module that has a wider data bus than required is to be used, only the required data width has to be selected.

#### **Data Input Delay**

This option is selected according to the user local back-end application's requirement. The user logic can send the write data to the core with either one-clock cycle or two-clock cycle delay or three-clock cycle delay.

#### **Auto Refresh Control**

#### **Auto Refresh Burst**

This option indicates the number of Refresh commands that the DDR2 SDRAM Controller IP core generates at once. DDR2 memories have at least an 8-deep Refresh command queue following the JEDEC specification and the IP core supports up to eight Refresh commands in one burst. It is recommended that the maximum number be used if the DDR2 interface throughput is a major concern of the system. If it is set to 8, for example, the core will send a set of eight consecutive Refresh commands to the memory at once when it reaches the time period of the eight refresh intervals (t<sub>REFI</sub> x 8). Bursting refresh cycles increases the DDR bus throughput because it helps keep core intervention to a minimum.

#### **External Ctrl Ports**

This option provides users with the capability of controlling the memory refresh command generation. If this option is disabled, the core takes control of the Refresh command generation according to the memory timing parameter, t<sub>REFI</sub>. Once enabled, the core adds the external auto refresh control ports to the local user interface with which users can take full control of the Refresh command generation.

#### **Controller Features**

#### **Fixed Memory Timing**

This option disables the memory timing reconfiguration feature for a generated core. When disabled, the IP core only supports the timing parameter set applied at the time of the core generation. This option may provide somewhat improved performance with lower resource utilization by removing the reconfiguration logic from the core. This option should not be selected if it is necessary to support different memory timing parameters without regenerating the core. This option is checked by default.

#### **Command Burst Enable**

This option enables the core's command burst feature. With this option enabled, the core automatically repeats a memory-read or memory-write command the number of times specified by the burst\_count bus. If unchecked, the command burst function is disabled and the burst\_count bus is removed from the core. Disabling this option may provide somewhat improved performance with lower utilization by removing the burst\_count bus logic from the core. The default of this option is "Enabled." For more detail about this feature, see "Command and Address" on page 11.

#### **Error Correction Code (ECC) Modules**

Optional ECC block when MEM Data Size is 24/40/72.

#### **Location Settings**

#### **DQS Location**

The DQS Location part enables users to select the DQS pin locations of each device (for LatticeECP3, LatticeECP2/S LatticeECP2M/S and LatticeXP2 devices). The user can find and choose all available DQS Pins in the drop-down list.

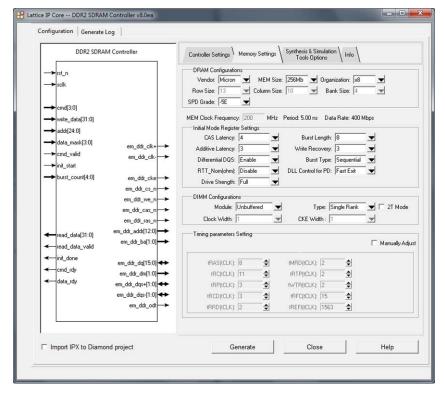

## **Memory Settings Tab**

The Memory Settings tab allows the user to specify the DDR2 controller configuration for the target memory device. Figure 3-2 shows the contents of the Memory Settings tab.

Figure 3-2. DDR2 SDRAM Controller IP Core Memory Settings

### **DRAM Configurations**

### Vendor

Micron DDR2 memory is set as the default. The user can select "Custom" for other memory vendors.

#### **MEM Size**

Memory Size, calculated by the Memory Row/Column/Bank Size and Organization.

#### Organization

This option is used to select the device organization of the RDIMM or UDIMM memory. Device configurations x4, x8, and x16 are supported.

#### **Row Size**

This option indicates the row address size for the memory ranging from 13 to 16, which is found in the memory data sheet.

#### Column Size

This option indicates the column address size for the memory ranging from 9 to 11, which is found in the memory data sheet.

#### **Bank Size**

This option indicates the bank address size for the memory. Either 4 or 8 is selected, depending on the size and type of the memory to be used with the core.

#### **SPD Grade**

This option indicates the speed grade for the memory. For 1:2 gearing mode, -37E and -5E are available. For 1:4 gearing mode, -25E, -3E, -3TE and -5E are available.

#### **MEM Clock Frequency**

Displays the memory operating frequency.

#### **Period**

Displays the memory operating period.

#### **Data Rate**

Displays the memory operating data rate.

### **Initial Mode Register Settings**

This option allows the user to program the mode registers during the core initialization process. Not all mode register bits are initialized from this option. Only the mode register configuration bits that are used for normal DDR operations are programmed using this setting. See Table 3-1 for the list of the covered mode register settings. The user does not need to program the mode registers after the core initialization is finished if the mode register is properly configured.

### **DIMM Configurations**

#### Module

This option allows the user to select an unbuffered or registered type of DIMM.

#### Period

This option allows the user to select the number of ranks (single/dual) available in the DIMM(s).

#### 2T Mode

This option is available only when two DIMMs are installed.

When it is selected (2T), the memory controller can drive the address/command signals one clock cycle earlier to get a bigger setup/hold time margin.

When it is unselected (1T), each DIMM should have its own address/command bus to avoid excessive loading.

#### **Clock Width**

This option sets the number of clocks with which the memory controller drives the memory. The IPexpress tool can generate either one or two memory clocks. Once a DDR2 memory controller core is generated, more memory clocks can be manually instantiated for those applications that need more than two memory clocks.

#### CKE Width

The number of memory clock enable signals is configured using this option. More clock enable signals can also be instantiated by the user.

### **Timing Parameters Setting**

If the user did not select a Micron memory listed in the Memory Vendor drop-down in the DRAM Configurations of Memory Settings Tab in the IPexpress GUI, the DDR2 Memory Controller IP core allows the user to customize the memory timing parameters by selecting "Custom" in the Vendor drop-down. The "Manually Adjust" box in the Timing tab must be checked to adjust these timing parameters. The numbers in the parameter boxes are decimal values indicating the number of clock cycles ( $t_{CLK}$ ). Since the timing numbers available in the memory vendors' data sheets are usually actual-time based, conversions from time numbers to clock numbers should be properly made. The conversion is easily made by dividing the time number by the clock period. When a timing parameter is found to be a minimum value in the data sheet, the calculated number, if not a whole integer, should be the next whole integer to be safe. If it is a maximum value, then only the whole part is taken, and the decimal part is discarded.

Note: There is a timing parameter that is not shown in the Timing tab. The TCKP parameter is not a memory timing parameter but a memory controller core parameter. It provides the wait cycles during the DDR2 memory initialization. The DDR2 specification requires a minimum of 400 ns wait before the PRE-CHARGE ALL command is executed. This parameter is found in the core parameter file with the default number `d107, which ensures 400ns of wait up to 266 MHz speed. Although the wait time can be increased or decreased by adjusting the TCKP parameter, it may not be necessary to modify this parameter in most applications.

Table 3-2. Memory Timing Parameters for the DDR2 SDRAM Controller

| Signal Name                                      | Description                                          |  |

|--------------------------------------------------|------------------------------------------------------|--|

| tras[4:0]                                        | ACTIVE to PRECHARGE command delay in clock cycles    |  |

| trc[4:0]                                         | ACTIVE to ACTIVE/AUTO REFRESH delay in clock cycles  |  |

| trcd[2:0]                                        | ACTIVE to READ/WRITE delay in clock cycles           |  |

| trrd[2:0]                                        | ACTIVE bank A to ACTIVE bank B delay in clock cycles |  |

| trfc[5:0] REFRESH command period in clock cycles |                                                      |  |

| trp[2:0]                                         | rp[2:0] PRECHARGE command period in clock cycles     |  |

| tmrd[2:0]                                        | LOAD MODE REGISTER command period in clock cycles    |  |

| trefi[15:0]                                      | Refresh Interval in clock cycles                     |  |

| trtp[1:0]                                        | READ to PRECHARGE delay                              |  |

| twtr[2:0]                                        | WRITE to READ delay                                  |  |

| tckp[6:0] <sup>1</sup>                           | Wait before PRECHARGE ALL during initialization      |  |

<sup>1.</sup> Not available in the IPexpress GUI.

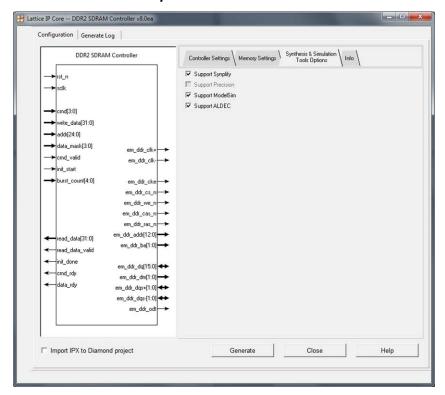

## **Synthesis & Simulation Tools Option Tab**

The DDR2 SDRAM Controller IP core supports multiple synthesis and simulation tool flows. This tab allows users to deselect the unwanted flow supports. Figure 3-3 shows the contents of the Synthesis & Simulation Tools Option tab.

Figure 3-3. Synthesis & Simulation Tools Option Tab

### Info Tab

The number of pins required on the DDR bus and the local user interface are reported in the Info tab. Figure 3-4 shows the contents of the Info tab.

Figure 3-4. Info Tab

### Memory I/F Pins

The numbers displayed indicate the total required number of DDR bus I/O pads.

#### **User I/F Pins**

The numbers displayed indicate the total required number of local user interface signals. Although these signals usually do not use I/O pads in user applications, this information can indicate whether or not the evaluation project will insert the dummy logic. Note that all local user interface signals also use I/O pads in the core evaluation project.

# **IP Core Generation**

This chapter provides information on licensing the DDR2 SDRAM Controller IP core, generating the core using the IPexpress tool, running functional simulation, and including the core in a top-level design. The DDR2 SDRAM Controller IP core can be used in LatticeECP3, LatticeECP2/M, LatticeXP2 and LatticeSC/M device families.

### Licensing the IP Core

An IP license is required to enable full, unrestricted use of the IP core in a complete, top-level design. An IP license that specifies the IP core (DDR2) and device family (LatticeECP3, LatticeECP2/M, LatticeXP2 or LatticeSC/M) is required to enable full use of the DDR2 SDRAM Controller IP core in LatticeECP3, LatticeECP2/M, LatticeXP2 or LatticeSC/M devices. Instructions on how to obtain licenses for Lattice IP cores are given at:

http://www.latticesemi.com/products/intellectualproperty/aboutip/isplevercoreonlinepurchas.cfm

Users may download and generate the DDR2 SDRAM Controller IP core and fully evaluate the core through functional simulation and implementation (synthesis, map, place and route) without an IP license. The IP core also supports Lattice's IP hardware evaluation capability, which makes it possible to create versions of the IP core that operate in hardware for a limited time (approximately four hours) without requiring an IP license. See "Hardware Evaluation" on page 32 for further details. However, a license is required to enable timing simulation, to open the design in the Diamond EPIC tool, and to generate bitstreams that do not include the hardware evaluation timeout limitation.

### **Getting Started**

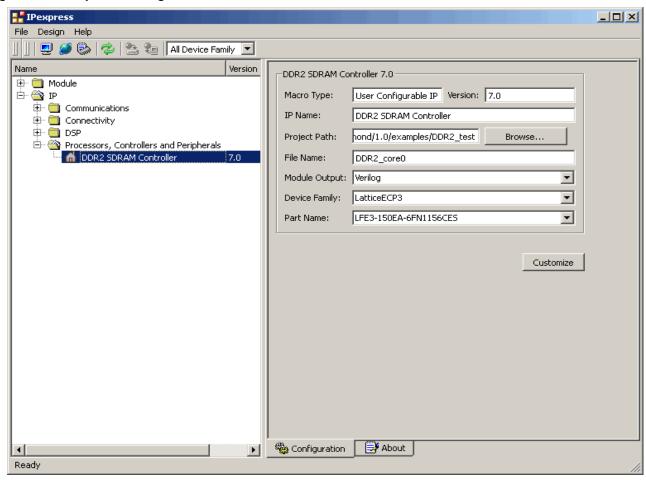

The DDR2 SDRAM Controller IP core is available for download from the Lattice's IP Server using the IPexpress tool. The IP files are automatically installed using ispUPDATE technology in any customer-specified directory. After the IP core has been installed, the IP core will be available in the IPexpress GUI dialog box shown in Figure 4-1.

The IPexpress tool GUI dialog box for the DDR2 SDRAM Controller IP core is shown in Figure 4-1. To generate a specific IP core configuration the user specifies:

- Project Path Path to the directory where the generated IP files will be loaded.

- File Name "username" designation given to the generated IP core and corresponding folders and files.

- Module Output Verilog or VHDL.

- **Device Family** Device family to which IP is to be targeted. Only families that support the particular IP core are listed.

- Part Name Specific targeted part within the selected device family.

Figure 4-1. IPexpress Dialog Box

Note that if the IPexpress tool is called from within an existing project, Project Path, Design Entry, Device Family and Part Name default to the specified project parameters. Refer to the IPexpress tool online help for further information.

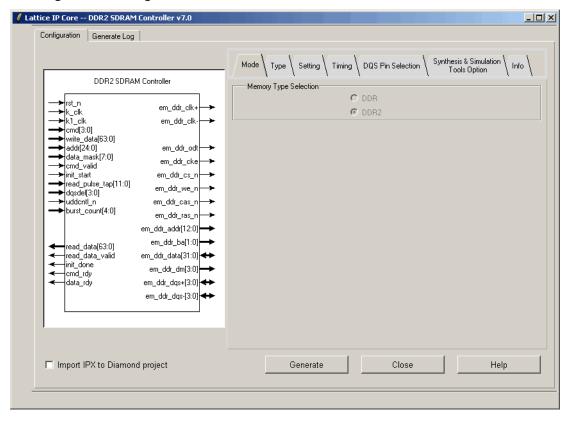

To create a custom configuration, the user clicks the **Customize** button in the IPexpress tool dialog box to display the DDR2 SDRAM Controller IP core Configuration GUI, as shown in Figure 4-2. From this dialog box, the user can select the IP parameter options specific to their application. Refer to "Parameter Settings" on page 19 for more information on the DDR2 parameter settings.

Figure 4-2. Configuration Dialog Box

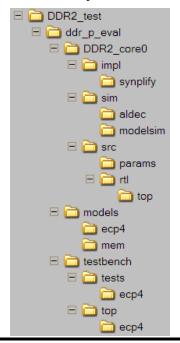

## **IPexpress-Created Files and Top Level Directory Structure**

When the user clicks the **Generate** button in the IP Configuration dialog box, the IP core and supporting files are generated in the specified "Project Path" directory. The directory structure of the generated files is shown in Figure 4-3.

Figure 4-3. DDR2 SDRAM Controller IP Core Directory Structure

### **Generated Files**

This section describes the structure of the DDR2 SDRAM Controller IP core that is generated by IPexpress as per user configuration. It also explains how the generated files are used in the structure. Understanding the core structure is an important step of a system design using the core. The summary of the files of the core for simulation are listed in Table 4-1.

Table 4-1. Files for Simulation and Implementation

| File                                  | Location                                       | Modules                                                                          | S <sup>1</sup> | P <sup>2</sup> | $\mathbb{R}^3$ |

|---------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------|----------------|----------------|----------------|

| Top-level wrapper                     | .\ddr_p_eval\[core_name]\src\rtl\top\[device]\ | ddr_sdram_mem_top                                                                | Χ              |                |                |

| Top-level wrapper                     | .\ddr_p_eval\[core_name]\impl                  | ddr_sdram_mem_top                                                                |                | Χ              |                |

| Encrypted netlist                     | .\                                             | [core_name].ngo                                                                  |                | Χ              |                |

| Core header <sup>4</sup>              | .\                                             | [core_name]_bb.v                                                                 |                | Х              |                |

| Instantiation template                | .\                                             | [core_name]_inst.v                                                               |                |                | Х              |

| I/O modules                           | .\ddr_p_eval\models\[device]\                  | ddr_sdram_mem_io_top and its submodules                                          |                |                | Х              |

| Clock generator                       | .\ddr_p_eval\models\[device]\                  | pmi_pll_fp (LatticeECP2/M,<br>LatticeECP3, LatticeXP2)<br>ddr_pll90(LatticeSC/M) | х              | х              |                |

| Parameter file                        | .\ddr_p_eval\[core_name]\src\params\           | ddr_sdram_mem_params                                                             | Χ              | Х              |                |

| Preference files <sup>5</sup>         | .\ddr_p_eval\[core_name]\impl\[synthesis]\     | [core_name]_eval.lpf<br>post_route_trace.prf                                     |                | Х              |                |

| Evaluation project (GUI) <sup>5</sup> | .\ddr_p_eval\[core_name]\impl\[synthesis]\     | [core_name]_eval.syn                                                             |                | Х              |                |

| Testbench top                         | .\ddr_p_eval\testbench\top\[device]\           | test_mem_ctrl                                                                    | Χ              |                |                |

| Obfuscated core simulation model      | .\                                             | [core_name]                                                                      | Х              |                |                |

| Stimulus generator                    | .\ddr_p_eval\testbench\tests\[device]\         | cmd_gen, test_case                                                               | Χ              |                |                |

| Monitor                               | .\ddr_p_eval\testbench\top\[device]\           | monitor, odt_watchdog                                                            | Χ              |                |                |

| TB configuration parameter            | .\ddr_p_eval\testbench\tests\[device]\         | tb_config_params                                                                 | Χ              |                |                |

| Memory model                          | .\ddr_p_eval\models\mem\                       | ddr2,(plus with DIMM modules)                                                    | Χ              |                |                |

| Memory model parameter                | .\ddr_p_eval\models\mem\                       | ddr2_parameters.vh                                                               | Х              |                |                |

| Evaluation script <sup>5</sup>        | .\ddr_p_eval\[core_name]\sim\(modelsim aldec)\ | [core_name]_eval.do                                                              | Χ              |                |                |

| Simulation script <sup>5</sup>        | .\ddr_p_eval\[core_name]\sim\(modelsim aldec)\ | [core_name]_eval_gatesim_prec ision.do [core_name]_eval_gatesim_synp lify.do     | Х              |                |                |

<sup>1.</sup> S = Simulation.

#### DDR2 SDRAM Controller Core Structure

The DDR2 SDRAM Controller IP core consists of the following five major functional blocks:

- Top-level wrapper (RTL)

- Encrypted memory controller block (NGO)

- I/O module block (RTL)

- Clock generator (RTL)

- Parameter file

<sup>2.</sup> P = Synthesis/Place and Route.

<sup>3.</sup> R = Not used in Simulation/Synthesis/Place and Route, only for reference.

<sup>4.</sup> Not required for the VHDL flow.

<sup>5.</sup> Files are generated according to the Synthesis & Simulation Tools Option tab selection. See "Synthesis & Simulation Tools Option Tab" on page 24.

All of these blocks are required to implement the core on the target FPGA device. Figure 4-4 shows the interconnection among those blocks.

Figure 4-4. Structure of the DDR2 SDRAM Controller IP Core

### **Top-level Wrapper**

The encrypted netlist core, I/O modules, and the clock generator blocks are instantiated in the top-level wrapper. When a system design is made with the DDR2 SDRAM Controller IP core, this wrapper must be instantiated. The wrapper is fully parameterized by the generated parameter file.

### **Encrypted Netlist**

The encrypted netlist contains the memory controller function that interfaces with the local user logic and the I/O modules that communicate with the DDR2 memory. The encrypted netlist must be located in the implementation project directory. IPexpress may generate another netlist for a PMI function when the core is generated. If this is the case, the PMI netlist must also be present along with the core netlist. The name of the PMI netlist is determined by IPexpress with the "pmi xx..xx.ngo" form.

#### I/O Modules

The I/O module block provides device dependant DDR2 I/O functions. This block consist of one I/O module top file and several sub-modules that handle the DDR data (DQ), data mask (DM) and data strobe (DQS) signals. Note that the I/O modules are integrated into an NGO block when the core is generated for the VHDL flow. The simulation will continue to use the Verilog RTL modules to model the I/O Modules block behavior.

#### **Clock Generator**

The DDR2 SDRAM Controller IP core is designed to provide the system clock from the inside of the core. The clock output (k\_clk) from the clock generator is used to drive the whole core logic as well as the external user logic. If a system that uses the DDR2 SDRAM Controller IP core is required to have a clock generator that is external to the core, the incorporated clock generator block can be removed from the core. The connections between the top-level wrapper and the clock generator are fully RTL based, and therefore, it is possible to modify the structure and connection of the core for the clock distribution following the system's need.

#### Parameter File