# LatticeXP2 ファミリ・データシート

DS1009J Version 01.8b, August 2012

© 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

DISCLAIMER: Translation of Lattice materials into languages other than English is intended as a convenience for our non-English reading customers. Although we attempt to provide accurate translations of our materials into languages other than English, Lattice does not warrant the accuracy or completeness of information that has been translated from English. Any use of a translation is at the risk of the user and Lattice expressly disclaims any warranty with respect to the information provided in translation. Customers are encouraged to review the English language version of the materials for accurate and complete information.

(日本語版は日本語での理解のため一助として用意しています。その作成にあたっては可能な限り正確を期しておりますが、原文英語版との不一致や不適切な訳文がある場合を含み、英語版が正(有効)です。特に電気的特性・仕様値については最新版の英語版を必ず参照するようにお願い致します。)

# LatticeXP2ファミリデータシート イントロダクション

# 機能

- □ flexiFLASH<sup>™</sup> アーキテクチャ

- インスタントオン

- コンフィグレーション回数は制限なし

- シングルチップ

- FlashBAK<sup>TM</sup> テクノロジ

- Serial TAGメモリ

- デザインのセキュリティ

- □ ライブアップデート・テクノロジ

- TransFR<sup>TM</sup> テクノロジ

- 128ビットAESで安全なアップデート

- 外部SPIフラッシュでのデュアルブート

- □ sysDSP<sup>™</sup>ブロック

- ・3~8ブロックで高性能の乗算・積和演算 (18x18演算で12~32)

- ・ブロック当たり1個の36×36乗算器、4個の18× 自由度の高いデバイス・コンフィグレーション 18乗算器、または8個の9×9乗算器に構成可能

- □ 組み込みブロックメモリと分散メモリ

- ・ 最大885kbのsysMEM<sup>™</sup> EBR

- 最大83Kbitの分散RAM

- □ sysCLOCK<sup>™</sup> (アナログ)PLL

- デバイスあたり最大4個のPLL

- クロックのてい倍、分周と位相シフト

- □ 自由度の高いI/Oバッファ sysIO™

- LVCMOS 33/25/18/15/12、LVTTL

- SSTL 33/25/18 クラスI, II

- HSTL15 クラスI, HSTL18 クラスI, II

- LVDS, Bus-LVDS, MLVDS, LVPECL, RSDS

- □ 作り込まれたソースシンクロナスI/O

- 200MHzまでのDDR/DDR2インターフェイス

- ディスプレイ用途の7:1 LVDSインターフェイ

- XGMII

- □ デバイス規模とパッケージオプション

- 5k~40k LUT、I/Oは86~540

- · csBGA, TQFP, PQFP, ftBGA, fpBGA

- パッケージ・マイグレーション

- - SPI (マスタ、スレーブ) ブートフラッシュ・ インターフェイス

- デュアルブート・イメージをサポート

- ソフトエラー検出(SED)ハードマクロ

- □ システムレベル・サポート

- IEEE1149.1 / 1532 準拠

- 初期化と汎用用途のオンチップ・オシレータ

- 1.2V供給電源

## 表 1-1 LatticeXP2ファミリ・セレクションガイド

| デバイス                        | XP2-5 | XP2-8 | XP2-17 | XP2-30 | XP2-40 |

|-----------------------------|-------|-------|--------|--------|--------|

| LUT サイズ (K)                 | 5     | 8     | 17     | 29     | 40     |

| 分散 RAM (Kbits)              | 10    | 18    | 35     | 56     | 83     |

| EBR SRAM (Kbits)            | 166   | 221   | 276    | 387    | 885    |

| EBR SRAMブロック数               | 9     | 12    | 15     | 21     | 48     |

| sysDSP ブロック                 | 3     | 4     | 5      | 7      | 8      |

| 18x18 乗算器                   | 12    | 16    | 20     | 28     | 32     |

| Vcc 供給電圧                    | 1.2   | 1.2   | 1.2    | 1.2    | 1.2    |

| GPLL 数                      | 2     | 2     | 4      | 4      | 4      |

| 最大I/O数                      | 172   | 201   | 358    | 472    | 540    |

| パッケージと <b>I/O</b> 数         |       |       |        |        |        |

| 132-pin csBGA (8 x 8 mm)    | 86    | 86    |        |        |        |

| 144-pin TQFP (20 x 20 mm)   | 100   | 100   |        |        |        |

| 208-ball PQFP (28 x 28 mm)  | 146   | 146   | 146    |        |        |

| 256-ball ftBGA (17 x 17 mm) | 172   | 201   | 201    | 201    |        |

| 484-ball fpBGA (23 x 23 mm) |       |       | 358    | 363    | 363    |

| 672-ball fpBGA (27 x 27 mm) |       |       |        | 472    | 540    |

# イントロダクション

LatticeXP2デバイスはルックアップ・テーブル(LUT)ベースのFPGAファブリックに、flexiFLASHと呼んでいるアーキテクチャの不揮発性フラッシュセルを統合しています。

FlexiFLASHアプローチはインスタントオン、回数制限のない再コンフィグレーション、FlashBAK組込みブロックメモリとSerial TAGメモリのオンチップ記憶、およびデザイン・セキュリティを含む恩恵を提供します。また、TransFRによるライブアップデート・テクノロジ、128ビットAES暗号化、およびデュアルブート・テクノロジをサポートします。

LatticeXP2 FPGAファブリックは、着手時から高性能と低コストを念頭において、こうした新技術のために最適化されました。LatticeXP2デバイスはLUTベースのロジック、分散メモリと組み込みメモリ、位相ロックループ(PLL)、組み込みソースシンクロナスI/Oサポート、および機能アップしたsysDSPブロックを含んでいます。

ラティスのLattice Diamond<sup>®</sup>デザインソフトウェアはLatticeXP2ファミリFPGAデバイスにデザインを効率 良く実装することが可能です。広く普及している論理合成ツール用のライブラリをサポートしています。 Diamondはデザインを配置配線するために、論理合成ツール出力をフロアプランニング・ツールからの制約 と共に用います。Diamondツールは、タイミング検証のために、配線からタイミング情報を抽出して、デザインにバック・アノテートします。

ラティスは予め設計された多くのIP(Intellectual Property) Lattice $CORE^{TM}$ モジュールをLatticeXP2ファミリのために提供します。標準化されたブロックとしてこれらのIPを用いることによって、設計者は自らの設計独自な部分に集中することができ、生産性を上げることができます。

# LatticeXP2ファミリデータシート アーキテクチャ

# アーキテクチャ概要

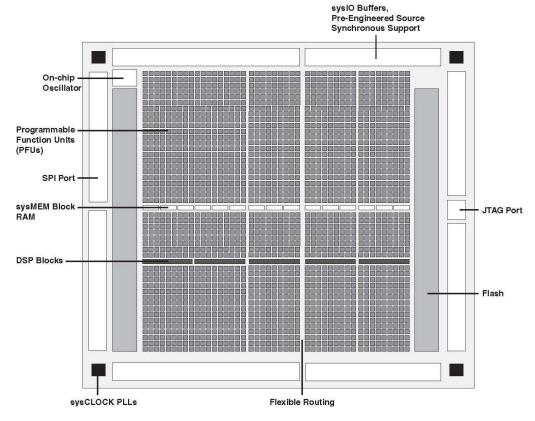

LatticeXP2デバイスはプログラマブルI/Oセル(PIC)によって囲まれた論理ブロックのアレイを含んでいます。図2-1に示す論理ブロックの間にあるのは、 $sysMEM^{TM}$  組み込みブロックRAM(EBR)と $sysDSP^{TM}$  信号処理ブロックの列です。

プログラマブル・ファンクション・ユニット(PFU)アレイの左右辺には不揮発性メモリブロックがあります。コンフィグレーション・モードでは不揮発性メモリはIEEE 1149.1 TAPポート、またはsysCONFIGTM ペリフェラルポートを介してプログラムされます。パワーアップすると、コンフィグレーション・データは不揮発性メモリブロックからコンフィグレーションSRAMに転送されます。このテクノロジにより、高価な外付けコンフィグレーション・メモリは不要になり、デザインは不正なリードバックからも安全になります。このデータ転送は数ミリ秒で完了し、多数のアプリケーションで容易なインターフェイスを可能にする"インスタントオン"機能を提供します。また、LatticeXP2デバイスはsysMEM EBRブロックから不揮発性メモリブロックに、ユーザ要求でデータを移すことができます。

論理ブロックには2種類あり、PFUとRAM/ROMなしのPFU(PFF)です。PFUはロジック、演算、RAM、ROM、およびレジスタ機能のためのビルディング・ブロックを含みます。PFFブロックはロジック、演算、およびROM機能のためのビルディング・ブロックを含んでいます。PFUとPFFブロックは共に、複雑なデザインを迅速にかつ効率的に実装できるように柔軟性が最適化されています。論理ブロックは2次元配列でアレンジされており、1つのタイプのブロックだけが列単位で用いられます。

LatticeXP2デバイスは一列かそれ以上のsysMEM EBRブロックを含んでいます。sysMEM EBRはサイズが 18kbitのメモリ専用ブロックです。各sysMEMブロックはデータ幅や深さを指定可能なRAMやROMに構成できます。加えてLatticeXP2デバイスは2列までのsysDSPブロックを含んでいます。各DSPブロックには乗算器と加算器・アキュミュレータがあり、これらは複雑なデジタル信号処理のビルディングブロックとなります。

各PICブロックはsysIOバッファの2PIO(PIOペア)より成ります。LatticeXP2のsysIOバッファは8バンクにアレンジされており、種々I/O規格の実装を可能にします。デバイスの左右辺にあるPIOペアはLVDSトランシーバ/レシーバ・ペアとして構成することができます。PICはまた、ディスプレイ用途で広く採用されている7:1 LVDSインターフェイスや、DDR/DDR2メモリインターフェイスを含む高速同期インターフェイスを実装する為のサポートロジックが作り込まれています。

これ以外のブロックとしては、PLLとコンフィグレーション機能があります。LatticeXP2アーキテクチャにはデバイスあたり4つの汎用(General)PLL(GPLL)があり、デバイスの各コーナーに配置されています。

コンフィグレーション・ブロックは暗号化されたビットストリームの復号化、トランスペアレント・アップデート、デュアルブートなどの機能をサポートし、バンク2と3の間に配置されています。デバイスのシリアル・コンフィグレーションをサポートするsysCONFIGTMポートはLatticeXP2ファミリの全デバイスが備えており、バンク7のI/Oと多重化されています。JTAGポートはバンク2と3の間にあります。

加えてファミリの全デバイスはオンチップオシレータも備えています。LatticeXP2はコア部供給電圧として 1.2Vを用います。

# 図2-1 LatticeXP2-17の簡略ブロック図(トップレベル)

# PFUブロック

LatticeXP2デバイスのコアは2種類のPFUブロックから成り、これらはPFUとPFFと呼ばれます。PFUはロジック、演算、分散RAM、および分散ROM機能を実行するようにプログラムすることができます。PFFブロックはロジック、演算、およびROM機能を実行するようにプログラムすることができます。特に明記する場合を除いて、データシートの残りでは、PFUとPFFブロックの両方を示すのに用語PFUを用います。

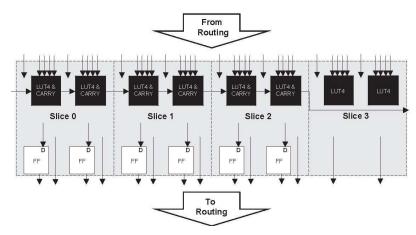

それぞれのPFUブロックは、図2-2で示されるように0~3と番号付けられた4つの相互接続されたスライスから成ります。PFUブロックに出入りするすべての相互接続は配線(領域)から来ています。それぞれのPFUブロックに関連する50本の入力と23本の出力があります。

#### 図2-2 PFUダイヤグラム

#### スライス

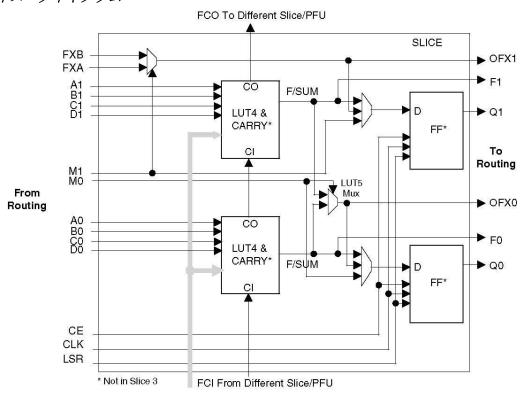

スライス0からスライス2は、2つのレジスタと、これに接続される2つの4入力ルックアップ・テーブル(LUT4) よりなり、スライス3にはレジスタがありません。PFUの場合、スライス0と2は分散メモリに構成でき、PFFでは構成できません。表2-1はPFFとPFU両ブロック内のスライスの動作モードと機能を示します。各PFUにはLUTを組み合わせてLUT5や、LUT6、LUT7またはLUT8などの機能を実行できるようにする関連ロジックを含んでいます。また、セット/リセット機能(同期か非同期としてプログラム)、クロック選択、チップセレクト、そしてRAM/ROM機能を実行するための制御ロジックがあります。図2-3はスライスの内部ロジックの概要を示します。スライス内のレジスタ用クロックは、立ち上がり/立ち下がりエッジ、或いは正または負レベルを有効とするように構成できます。

表2-1 スライスごとのリソースとモード

|       | PFUブロック     |                       | PFFブロック     |               |

|-------|-------------|-----------------------|-------------|---------------|

| スライス  | リソース        | モード                   | リソース        | モード           |

| スライス0 | LUT4とレジスタ各2 | ロジック、リップル、RAM、<br>ROM | LUT4とレジスタ各2 | ロジック、リップル、ROM |

| スライス1 | LUT4とレジスタ各2 | ロジック、リップル、ROM         | LUT4とレジスタ各2 | ロジック、リップル、ROM |

| スライス2 | LUT4とレジスタ各2 | ロジック、リップル、RAM、<br>ROM | LUT4とレジスタ各2 | ロジック、リップル、ROM |

| スライス3 | LUT4が2つ     | ロジック 、ROM             | LUT4が2つ     | ロジック、ROM      |

スライス0/1/2には14の入力信号があり、これは配線からの13本の信号と、キャリチェインからの1本(隣接しているスライスかPFUから)です。また7本の出力があり、これは配線への6本と(隣接しているPFUへの)キャリ・チェーンの1本です。スライス3には配線からの13信号入力と配線への4信号出力があります。表2-2はスライス0から2に関連する信号をリストアップします。

#### 図2-3 スライス・ダイヤグラム

For Slices 0 and 2, memory control signals are generated from Slice 1 as follows:

WCK is CLK

WRE is from LSR

DI[3:2] for Slice 2 and DI[1:0] for Slice 0 data

WAD [A:D] is a 4bit address from slice 1 LUT input

#### 表2-2 スライス信号記述

| 機能 | タイプ     | 信号名            | 記述                                             |

|----|---------|----------------|------------------------------------------------|

| 入力 | データ信号   | A0, B0, C0, D0 | LUT4入力                                         |

| 入力 | データ信号   | A1, B1, C1, D1 | LUT4入力                                         |

| 入力 | 複数用途    | MO             | 複数用途入力                                         |

| 入力 | 複数用途    | M1             | 複数用途入力                                         |

| 入力 | 制御信号    | CE             | クロック・イネーブル                                     |

| 入力 | 制御信号    | LSR            | ローカル・セット/リセット                                  |

| 入力 | 制御信号    | CLK            | システム・クロック                                      |

| 入力 | PFU間信号  | FCI            | 高速キャリ入力1                                       |

| 入力 | スライス間信号 | FXA            | LUT6、LUT7を構成するための中間信号                          |

| 入力 | スライス間信号 | FXB            | LUT6、LUT7を構成するための中間信号                          |

| 出力 | データ信号   | F0, F1         | LUT4出力レジスタ・バイパス信号                              |

| 出力 | データ信号   | Q0, Q1         | レジスタ出力                                         |

| 出力 | データ信号   | OFX0           | LUT5 MUX出力                                     |

| 出力 | データ信号   | OFX1           | LUT6, LUT7, LUT8 <sup>2</sup> MUX 出力、スライスに依存   |

| 出力 | PFU間信号  | FCO            | 各PFUのスライス <b>2</b> からの高速キャリチェイン出力 <sup>1</sup> |

- 1. 接続の詳細については図2-3を参照.

- 2. 2 PFUが必要.

## 動作モード

それぞれのスライスには4動作モードがあり、それらはロジック、リップル、RAM、およびROMです。

#### ロジックモード

このモードで、各スライスにおけるLUTは、4入力の組み合わせルックアップ・テーブルとして構成されます。 LUT4は16の可能な入力組み合わせを持つことができます。このルックアップ・テーブルをプログラムする ことによって、4入力があるどのようなロジック機能も生成することができます。1スライスあたり2個の LUT4があるので、1スライスでLUT5を組み立てることができます。他のスライスを連結することによって、 LUT6や、LUT7、LUT8などのより大きいルックアップ・テーブルを構成することができます。LUT8では4 スライス以上が必要であることに留意してください。

## リップルモード

リップルモードは小さな演算機能の効率的な実装ができます。リップルモードでは、各スライスは以下の機能を実装することができます。

- 2ビット加算

- 2ビット減算

- ・動的な制御での2ビット加算・減算

- 2ビット・アップ/ダウンカウンタ

- 非同期クリア付きアップ/ダウン・カウンタ

- プリロード(同期)付きアップ/ダウン・カウンタ

- リップルモード乗算器ビルディング・ブロック

- 乗算器サポート

- 入力AとBのコンパレータ機能

- AはBより等しいか大きい

- AはBに等しくない

- AはBより等しいか小さい

2本のキャリ信号、FCIとFCO、はこのモードでスライス単位で生成され、スライスを連結することによって 高速演算機能が構成できます。

#### RAMモード

このモードでは、スライス0のLUTブロック2つを用いることで16x4ビットの分散シングルポートRAM(SPR) として、スライス2では16x1ビットのメモリを構成することができます。スライス1はメモリアドレスと制御信号のために使用されます。16×2ビット疑似デュアルポートRAMは、スライス一つををリードライトポートとして用い、もう一つのスライスをリードオンリポートとして使用して生成されます。

ラティスのデザインツールは種々異なるサイズのメモリ作成をサポートします。適切な場合、PFUの機能を示す分散メモリ・プリミティブを用いることで、ソフトウェアはこれらを構成します。表2-3は異なる分散メモリ(RAM)プリミティブを実装するのに必要なスライスの数を示します。LatticeXP2でRAMを用いる詳しい情報に関しては、テクニカルノートTN1137(LatticeXP2 Memory Usage Guide)を参照してください。

#### 表2-3 分散RAMの実装に必要なスライスの数

|       | SPR16x4 | PDPR16x4 |

|-------|---------|----------|

| スライス数 | 3       | 3        |

注: SPR = Single Port RAM, PDPR = Pseudo Dual Port RAM

#### ROMモード

ROMモードはLUTロジックによりますので、スライス0から3が用いられます。プリロードはコンフィグレーションの間、プログラミング・インターフェイスを通して達成されます。

# 配線

単独信号かバス信号として関連する制御信号と共に配線するための多くのリソースがLatticeXP2デバイスに用意されています。配線リソースはスイッチング回路、バッファ、およびメタル・インターコネクト(配線)セグメントから成ります。

PFU相互の接続は(2PFUにまたがる)x1ライン、(3PFUにまたがる)x2ライン、および(7PFUにまたがる)x6ラインで行われます。x1とx2接続は速くて効率の良い接続を横方向と縦方向に提供します。x2とx6リソースはバッファリングされ、PFU間に短い接続と長い接続配線を可能にします。

LatticeXP2ファミリはコンパクトな設計を実現する配線アーキテクチャを持っています。Diamondデザインツールは、論理合成ツールの出力を取り込んで、デザインを配置配線します。デザインを最適化するために対話的な配線エディタが利用できますが、一般に配置配線ツールは完全に自動です。

# sysCLOCK位相同期ループ(PLL)

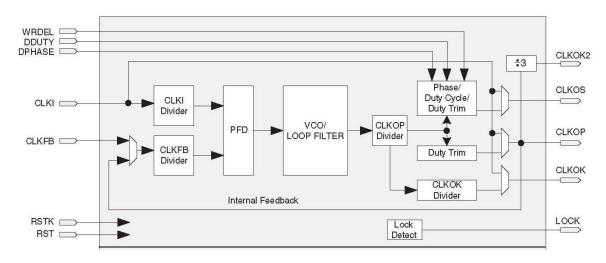

sysCLOCK PLLはクロック周波数を合成する機能を提供します。LatticeXP2ファミリの全デバイスがフル機能をもつGPLL(汎用PLL)を2~4つ搭載しています。GPLLのアーキテクチャを図2-4に示します。

CLKIはPLLの基準周波数入力で外部ピンか配線から加えられます。CLKIは入力クロック分周器ブロックへ与えられます。CLKFBはフィードバック信号で、CLKOPあるいはユーザクロック・ピン/ロジックから与えられます。この信号はフィードバック分周器へ与えられます。フィードバック分周器は、基準周波数をてい倍するために用いられます。

入力信号とフィードバック信号がVCOブロックに入ります。VCOの周波数と位相はこの入力信号とフィードバック信号で決定されます。LOCK信号は、VCOが入力クロック信号にロックした事を示すために生成されます。

VCO出力はポストスケーラ分周器CLKOPに入ります。CLKOP分周器出力はデューティトリム・ブロックで 微調整できます。VCOをCLKOPより高い周波数で動作させることにより、GPLLの動作周波数範囲を広げる

ことが可能です。CLKOP分周器の出力はさらに(第二の)CLKOK分周器を通すことにより、低い周波数のCLKOK出力を得ます。さらに低い周波数のクロックが必要な用途のために、CLKOP信号は3分周回路を通り、CLKOK2として出力されます。CLKOK2はソースシンクロナス・ロジックを用いるアプリケーション用に用意されています。位相/デューティ比/デューティトリム・ブロックは、CLKOS信号を生成するためにCLKOP分周器の位相とデューティ比を調整します。位相/デューティ比設定はコンフィグ時にプログラムするか、またはダイナミックに調整することができます。

GPLLからのCLKOP、CLKOK、CLKOK2、およびCLKOSはクロック分配ネットワークに供給されます。GPLLの詳細に関してはTN1126 (LatticeXP2 sysCLOCK PLL Design and Usage Guide)を参照してください。表2-4はGPLLブロックの信号記述です。

#### **図2-4 GPLL**ブロック図

#### 表2-4 GPLL信号記述

| 信号          | I/O | 記述                                                                |

|-------------|-----|-------------------------------------------------------------------|

| CLKI        | I   | クロック入力。外部ピンもしくは配線から                                               |

| CLKFB       | Ι   | PLLフィードバック入力。CLKOP(PLL内部)、クロックネット(CLKOP)、またはユーザクロック(外部ピンかロジック)から。 |

| RST         |     | "1"でPLLカウンタ、VCO、チャージポンプ、M分周器をリセット                                 |

| RSTK        | I   | "1" でK分周器をリセット                                                    |

| DPHASE[3:0] | I   | DPA位相調整入力                                                         |

| DDDUTY[3:0] | I   | DPAデューティサイクル選択入力                                                  |

| WRDEL       | I   | DPA遅延微調整入力                                                        |

| CLKOS       | 0   | PLL出力クロック。クロックツリーへ(位相シフト、デューティ比可変)                                |

| CLKOP       | 0   | PLL出力クロック。クロックツリーへ(位相シフトなし)                                       |

| CLKOK       | 0   | PLL出力。クロック分周器を介してクロックツリーへ                                         |

| CLKOK2      | 0   | PLL出力クロック。クロックツリーへ(CLKOPを3分周)                                     |

| LOCK        | 0   | "1"でPLLがCLKIにロックを示す                                               |

# クロック分周器

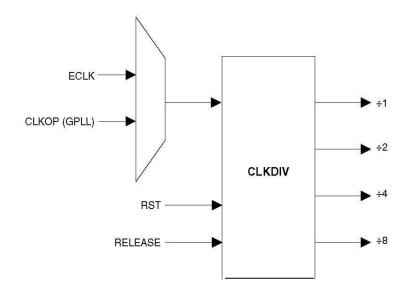

LatticeXP2はデバイスの左右辺に2つのクロック分周器を持っています。これらは高速のエッジクロックから、より低速のシステムクロックを生成することを意図しています。本ブロックは、÷2、÷4または÷8モードで動作し、リセット信号のリリースに基づいて分周クロックと高速クロックを既知の位相関係に維持します。クロック分周器には、GPLLからのCLKOP出力、またはエッジクロック(ECLK)から供給できます。クロック分周器出力はプライマリクロック・ソースとして使用され、クロック分配ネットワークへ供給されます。リセット制御信号(RST)は、入力をリセットし、また全出力をLowにします。RELEASE信号は入力クロックに対して出力をリリースします。クロック分周器の詳細に関しては、テクニカルノートTN1126を参照してください。図2-5はクロック分周器の接続を示します。

#### 図2-5 クロック分周器の接続

# クロック分配ネットワーク

LatticeXP2デバイスには8本のプライマリクロックがクワドラント毎にあり、自由度の高いセカンダリクロック/制御信号がリージョン毎に6~8本あります。高性能エッジクロックがデバイス各辺に2本づつあり、高速インターフェイスをサポートします。クロック入力は外部I/O、sysCLOCK PLL、および配線から選択されます。これらクロック入力はプライマリクロック/セカンダリクロック/エッジクロック各分配システムを介してチップ内部に供給されます。

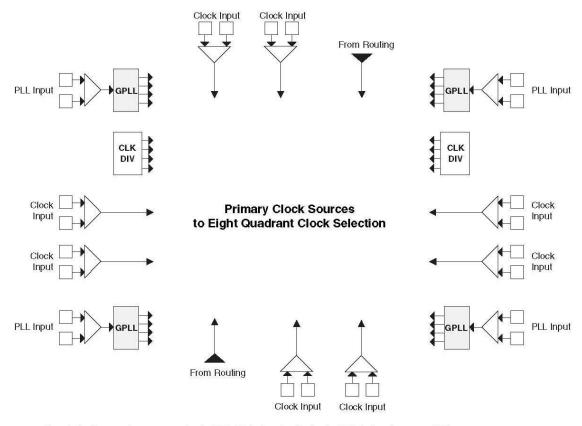

#### プライマリクロックのソース

LatticeXP2デバイスは4つのソースからクロックを得ます。すなわちPLL出力、CLKDIV出力、クロック入力専用ピン、そして配線です。LatticeXP2は2~4個のsysCLOCK PLLを持っており、デバイスの四隅に配置されています。クロック専用入力ピンは8本あり、デバイス各辺に2本づつあります。図2-6はプライマリクロック・ソースを示します。

# 図2-6 LatticeXP2-17のプライマリクロック・ソース

Note: This diagram shows sources for the XP2-17 device. Smaller LatticeXP2 devices have two GPLLs.

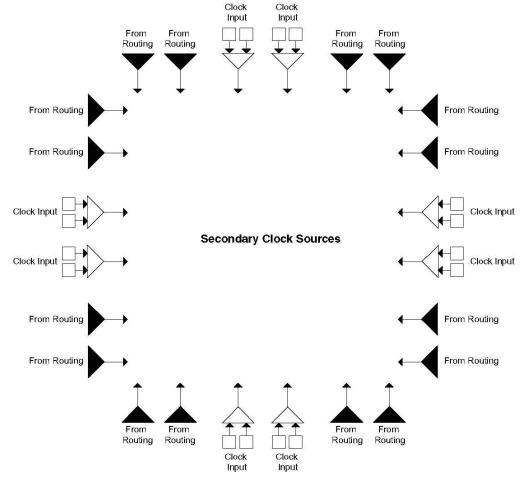

# セカンダリクロック / 制御信号のソース

LatticeXP2はセカンダリクロック (SC0~SC7) を8本のクロック専用入力ピン、および配線より得ます。図 2-7はセカンダリクロック・ソースを示します。

## 図2-7 セカンダリクロック・ソース

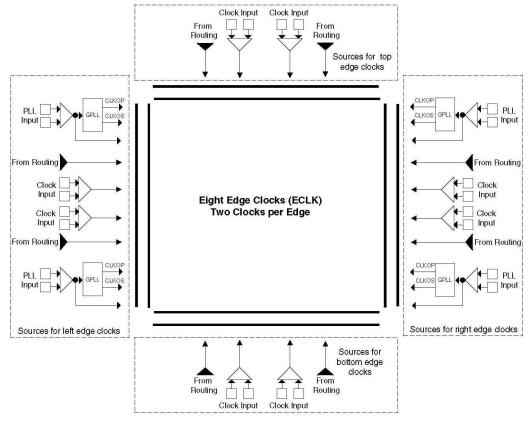

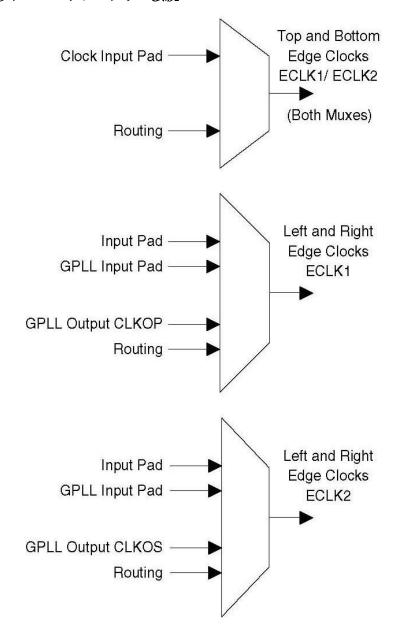

# エッジクロック・ソース

エッジクロック・リソースは同一辺にある種々ソースからドライブすることができます。図2-8で示すように、 隣接するエッジクロックPIO、プライマリクロックPIO、PLL、およびクロック分周器からエッジクロック・ リソースをドライブできます。

#### 図2-8 エッジクロック・ソース

Note: This diagram shows sources for the XP2-17 device. Smaller LatticeXP2 devices have two GPLLs.

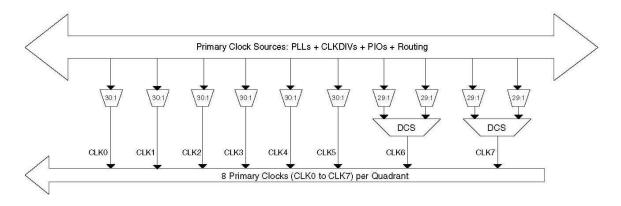

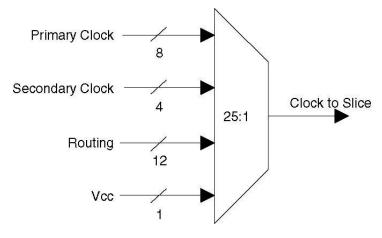

## プライマリクロック配線

LatticeXP2におけるクロック配線構造は、クワドラントごとに8本あるプライマリクロック線(CLK0~CLK7)から成ります。各クワドラントのプライマリクロックはそれぞれデバイスの中央に位置するマルチプレクサから生成されます。全てのソースはこれらマルチプレクサに接続されます。図2-9は各クワドラントのクロック配線を示します。各クワドラントのマルチプレクサは同一で、もし必要な場合はグローバルに(チップ全体に)分配もできます。

## 図2-9 クワドラントあたりのプライマリ・クロック選択

# ダイナミック・クロックセレクト(DCS)

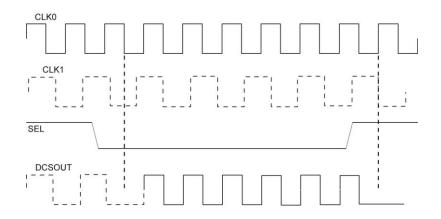

DCSはプライマリクロック配線で使用できる洗練されたマルチプレクサで、グリッチや細ったパルスを出す事なしに2本の独立したクロックソースを切り替えます。これは選択信号がいつトグルするかに係わらず達成できます。クワドラント内に2つのDCSブロックがあり、デバイスに合計8つあります。DCSブロックの入力はデバイス中央のマルチプレクサから得られます。DCS出力はプライマリクロックのCKL6とCLK7に接続されます(図2-9)。

図2-10はデフォルト動作モード時のDCSのタイミング波形を示します。DCSは他の動作モードにも設定できます。より詳しい情報に関しては、テクニカルノートTN1126を参照してください。

#### **図2-10 DCS波形**

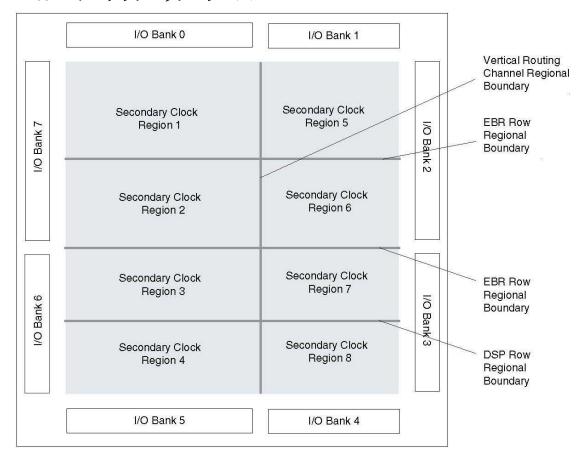

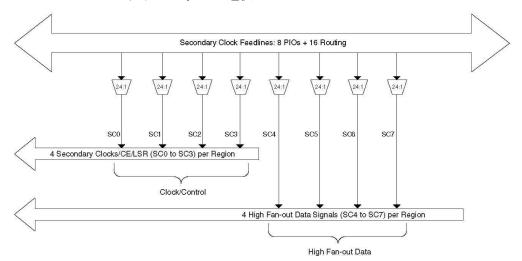

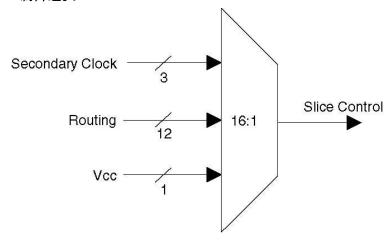

## セカンダリクロック / 制御の配線

LatticeXP2のセカンダリクロックはリージョンベースのリソースで、その利点はプライマリクロックに対して注入遅延(Injection delay)が小さいことと、リージョン内のスキューが比較的小さいことです。その区切りはEBR/DSPブロックの列と、特別な縦の配線チャネルです。この特別の配線チャネルは中央のDSPブロックの左端、或いはDSP列の中央に合わされています。図2-11はLatticeXP2-40の例で、縦に走るこの特別の配線チャネルと8つのリージョンを示します。LatticeXP2-30とそれ以下の規模のデバイスには6つのリージョンがあります。LatticeXP2はリージョンごとに4本のセカンダリクロック・リソース(SCOからSC3)があります。

セカンダリクロックのマルチプレクサはデバイスの中央に位置しています。図2-12がその構造を示します。SCOからSC3は高ファンアウトの制御線に使用され、SC4からSC7はクロック信号に使用されます。

図2-11 XP2-50のセカンダリクロック・リージョン

図2-12 リージョンごとのセカンダリクロックの選択

#### スライスクロックの選択

図2-13はクロック選択を、図2-14はスライス0から2の制御信号の選択を示します。すべてのプライマリクロックとセカンダリクロックの4本はこのクロック選択マルチプレクサに接続されます。配線を使用する他の信号はクロックとしてスライスに入力もできます。スライスの制御信号はセカンダリクロックか、配線から接続される信号により生成されます。

もしこれらクロック・制御選択のマルチプレクサで共に何も選択されない場合はマルチプレクサ出力は1です。スライス3にはレジスタがないので、これらマルチプレクサがありません。

#### 図2-13 スライス0から2のクロック選択

#### 図2-14 スライス0から2の制御選択

# エッジクロックの配線

LatticeXP2デバイスには、高速インターフェイスの実装でPIOと共に使用することを意図する、何本かの高速エッジクロックがあります。エッジ(辺)あたり2本、デバイスとして8本のエッジクロックがあります。図2-15はこれらクロック選択のマルチプレクサを示します。

図2-15 エッジクロック・マルチプレクサの接続

# sysMEMメモリ

LatticeXP2ファミリのデバイスは多くのsysMEM組み込みブロックRAM(EBR)を持っています。EBRは専用の入出力レジスタがある18kビットのRAMから成ります。

# sysMEMメモリブロック

sysMEMブロックはシングルポート、デュアルポートまたは疑似デュアルポート・メモリを実装することができます。表2-5に示されるようにさまざまな深さと幅で各ブロックを用いることができます。PFUでサポートロジックを構成してFIFOとしてsysMEM EBRを実装することも可能です。またEBRはパリティチェック機能の実装を容易にし、さらに18ビット或いは36ビットデータ幅構成ではバイトイネーブル信号もサポートします。

| 表2-5 sysN | <i>IEMブロッ</i> | クのコン | フィグレ | ーション |

|-----------|---------------|------|------|------|

|-----------|---------------|------|------|------|

| メモリ・モード   | 構成                                                                          |

|-----------|-----------------------------------------------------------------------------|

| シングルポート   | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18<br>512 x 36 |

| 真のデュアルポート | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18             |

| 擬似デュアルポート | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18<br>512 x 36 |

#### バスサイズ・マッチング

マルチポートメモリ・モードのすべてがそれぞれの異なるポート幅をサポートします。RAMビットはWord0のLSBからMSBへ、Word1のLSBからMSBへというように配置されます。ワード長とワード数はポートごとに異なりますが、このマッピング体系は各ポートに適用されます。

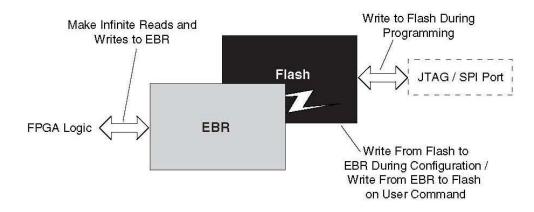

# FlashBAK EBR内データの保存

LatticeXP2のすべてのEBRメモリはフラッシュメモリがシャドーになっています。オプションとして、ラティスLattice Diamondツールを用いることでメモリブロックで初期値を定義することができます。初期値はプログラム時にフラッシュメモリにロードされ、またデバイスのパワーアップ時やデバイスが再コンフィグレーションされるときは常にSRAMへロードされます。この機能はルックアップテーブルやマイクロプロセッサ・コードなど、さまざまな情報の記憶に理想的です。また、EBRメモリの現在の内容をフラッシュメモリに書き出すことも可能です。この機能はエラーコードや較正情報などのデータの格納に有用です。FlashBAKの情報に関してはTN1137 (LatticeXP2 Memory Usage Guide)を参照してください。

# 図2-16 FlashBAKテクノロジ

#### メモリの連結

EBR sysMEMブロックを用いることで、より大きくて、より深いRAMブロックを作成することができます。 通常、ラティス・デザインツールは特定の設計への入力に基づいて透過的に(暗黙に)メモリを連結します。

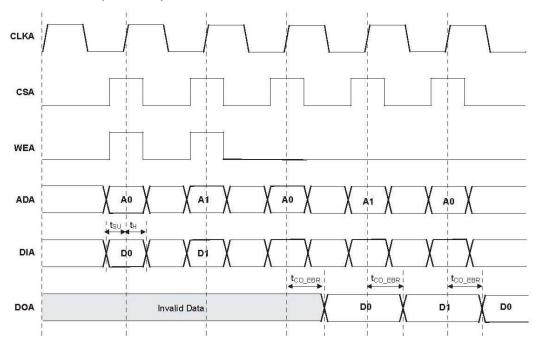

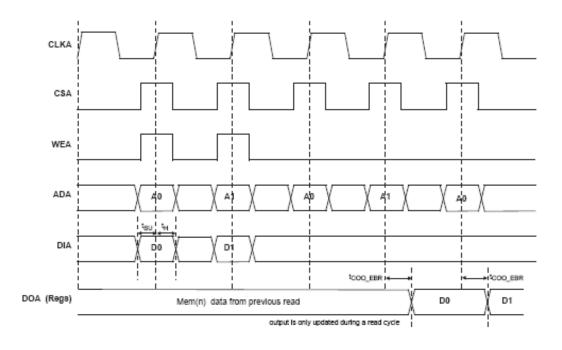

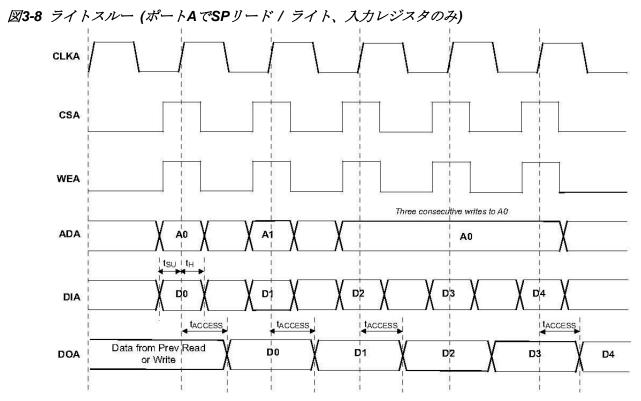

#### シングルポート / デュアルポート / 擬似デュアルポート・モード

全てのsysMEM RAMモードで、ポートへの入力データとアドレスにはメモリアレイの入力にレジスタがあります。メモリの出力データへのレジスタはオプションです。

EBRメモリはシングルポートかデュアルポート動作のための書き込みの振舞いとして2つの形態をサポートします。

- **1. 標準**;出力データはリード・サイクルの間だけ現れます。ライト・サイクルの間、現在のアドレスのデータは出力に現れません。すべてのデータビット幅がサポートされます。

- **2. ライトスルー**; ライト・サイクルの間、入力データのコピーが同じポートの出力に現れます。すべての データビット幅がサポートされます。

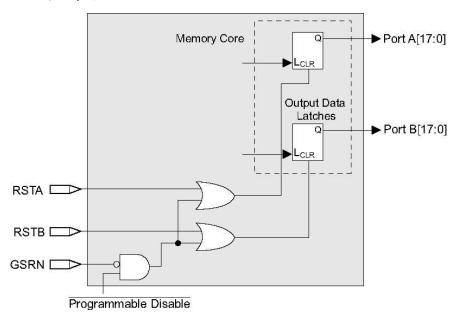

## メモリコア・リセット

EBRのメモリアレイはA出力とB出力ポートのラッチを利用します。これらのラッチを非同期か同期でリセットすることができます。RSTAとRSTBはローカルの信号で、出力ラッチをリセットし、それぞれPort AとPort Bに関連します。Global Reset(GSRN)信号は両ポートをリセットします。両ポートのための出力データラッチと関連するリセットが図2-17で示されます。より詳細についてはテクニカルノートTN1137(LatticeXP2 Memory Usage Guide)を参照してください。

#### 図2-17 メモリコア・リセット

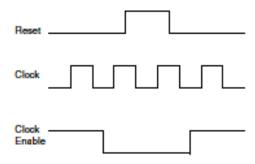

# EBR非同期リセット

図2-18に示すように、クロックイネーブルがリセットのアサート前とネゲート後にクロック1周期(以上) Low (非アクティブ) の場合にのみ、EBRの非同期リセットもしくはGSR(使用されていれば) は与えることができます。EBRへのGSR入力は常に非同期です。

#### 図2-18 EBR非同期リセットのタイミング図(GSRを含む)

もし全てのクロックイネーブルが有効のままの場合、非同期リセットもしくはGSRはリード/ライト・クロック入力が安定状態になった後、最小1/f<sub>MAX</sub>(EBRクロック)の期間、加えられなければなりません。またリセットのリリースタイミングは、次のアクティブなリード/ライト・クロックエッジに対して、同期リセットとしてのセットアップ時間を満たすようにしなければなりません。

EBR初期値がコンフィグレーション時にプリロードされる場合、GSR入力がディセーブルされるか、或いはデバイスのウェイクアップ時にI/Oの解放される前にGSRがリリースされるようにしなければなりません。

これらの要件は全てのEBR RAMとROMに適用されます。

EBRで同期リセットのみが用いられ、またEBRのGSR入力もディセーブルされていればリセットに関する制約はありません。

# sysDSP<sup>™</sup> ブロック

LatticeXP2ファミリはsysDSPブロックを提供し、これにより低コストで高性能のデジタル信号処理(DSP)アプリケーションに理想的に適しています。これらのアプリケーションで用いられる典型的な機能は有限インパルス応答 (FIR)フィルタ、高速フーリエ変換(FFT)機能、相関器、リードソロモン/ターボ/たたみ込み符号器、および復号器などです。これらの複雑な信号処理機能は、加算器と乗算器やアキュムレータと乗算器のように類似のビルディング・ブロックを用います。

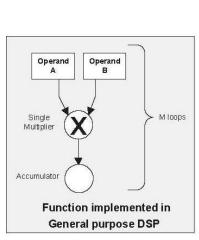

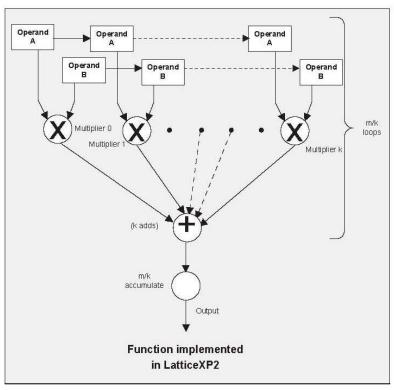

# sysDSPブロック・アプローチと汎用DSPとの比較

従来の汎用DSPチップは固定データ幅のMAC(乗算とアキュミュレート)ユニットを通常1~4個含んでいます。これは限られた並列度と限られたスループットに通じます。それらのスループットは、より高いクロックスピードによって増加されます。他方LatticeXP2には、異なったデータ幅をサポートする多くのDSPブロックがあります。これで、設計者はDSP機能の非常に並列度のある実装ができます。設計者は、適切なレベルの並列度を選ぶことによって、エリアに対するDSP性能を最適化することができます。図2-19はシリアル実装と並列実装を比較します。

## 図2-19 汎用DSPとLatticeXP2アプローチの比較

# sysDSPブロックの機能

LatticeXP2ファミリにおけるsysDSPブロックは、4個の機能要素を9、18と36の3種のデータパス幅でサポートします。ユーザは機能要素をDSPブロック用に選択して、次にオペランドの幅とタイプ(符号あり/なし)を選びます。LatticeXP2ファミリsysDSPブロックにおけるオペランドは、符号ありか符号なしですが、機能要素の中で混在できません。同様に、オペランド幅もブロックの中で混在できません。LatticeXP2ファミリではDSP要素を従属接続できます。

各sysDSPブロックにおけるリソースは以下の4つの要素をサポートするために構成することができます。

• MULT 乗算

MAC 積和(乗算とアキュミュレート(累積))

• MULTADDSUB 乗算、加算/減算

• MULTADDSUBSUM 乗算、加算/減算、アキュミュレート

各ブロックで利用できる要素の数は、x9、x18、およびx36の3つのオプションからの選択に依存します。これらの多くの要素はDSP機能の並列度の高い実装のために連結できます。表2-6はブロックの機能を示します。

表2-6 ブロックにおける最大の要素数

| 乗算器幅 (>)      | x9 | x18 | x36          |

|---------------|----|-----|--------------|

| MULT          | 8  | 4   | 1            |

| MAC           | 2  | 2   | <del>_</del> |

| MULTADDSUB    | 4  | 2   | _            |

| MULTADDSUBSUM | 2  | 1   | _            |

4つの要素ではいくつかのオプションが利用できます。すべての要素の入力レジスタには、直接ロードする

か、または直前のオペランドのシフトレジスタからロードできます。"ダイナミック動作"を選択することで以下の操作が可能になります。

- ・"Signed/Unsigned" オプションでオペランドを各サイクルごとに符号あり・符号なしを切り換える

- ・"Add/Sub" オプションでアキュミュレータを各サイクルごとに加算と減算で切り換える

- オペランドのロード方法をパラレルとシリアルで切り替える

# MULT sysDSP要素

この乗算器要素は加算/アキュムレータ・ノードなしで乗算します。二つのオペランド(AとB)は、乗算され、そして、結果が出力に出てきます。ユーザは入力/出力/パイプライン各レジスタをイネーブルすることができます。図2-20はMULT sysDSP要素を示します。

## 図2-20 MULT sysDSP要素

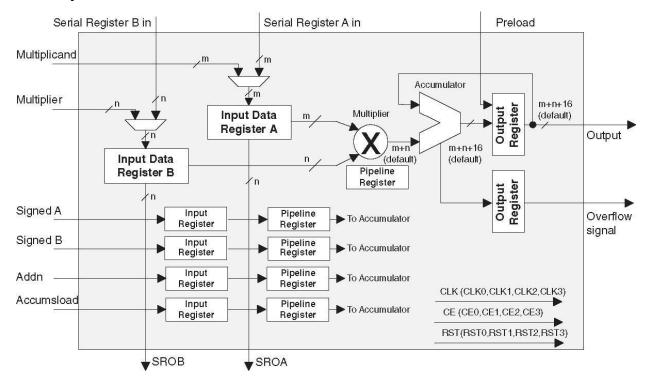

# MAC sysDSP 要素

この場合、二つのオペランド(AとB)は乗算されて、結果はアキュミュレート(累積)された直前の値に加えられます(積和動作)。このアキュミュレート値は出力で利用できます。ユーザは入力とパイプライン・レジスタをイネーブルすることができますが、出力レジスタは常にイネーブルされます。出力レジスタは、アキュミュレートされた値を保持するために用いられます。LatticeXP2のDSPブロックはアキュミュレータを動的に初期化できます。また、レジスタのあるオーバフロー信号も利用できます。本ドキュメントの後ではオーバフロー条件を示します。図2-21はMAC sysDSP要素を示します。

#### 図2-21 MAC sysDSP要素

# MULTADDSUB sysDSP要素

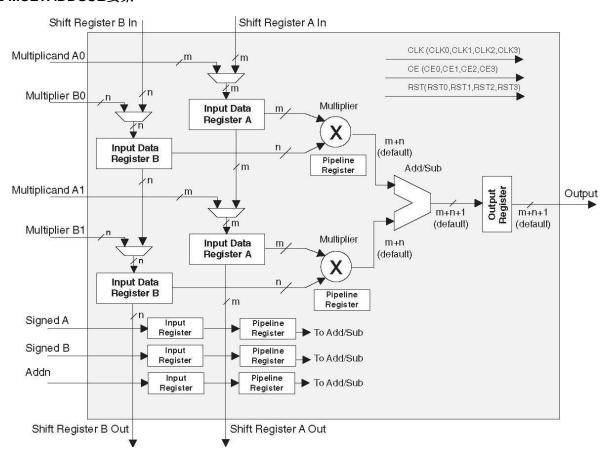

オペランドのA0とB0は乗算されて、その結果は、オペランドA1とA2の乗算の結果に加算されるか、または引き算されます。ユーザは入力/出力/パイプライン各レジスタをイネーブルすることができます。図2-22は MULTADDSUB sysDSP要素を示します。

#### 図2-22 MULTADDSUB要素

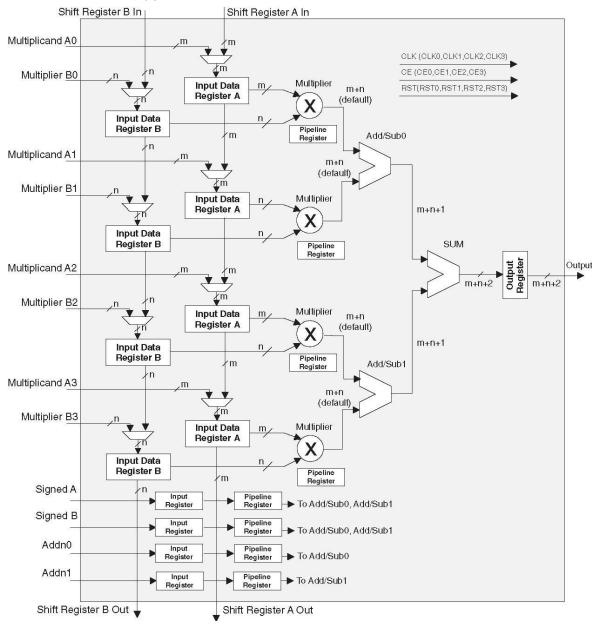

## MULTADDSUBSUM sysDSP要素

オペランドのA0とB0は乗算されて、その結果は、オペランドA1とB1の乗算の結果に加えられるか、または引き算されます。オペランドのA2とB2は乗算されて、その結果は、オペランドのA3とB3の乗算の結果にさらに加えられるか、または引き算されます。加算/減算の結果は共に総和(加算)ブロックで加えられます。ユーザは入力/出力/パイプライン各レジスタをイネーブルすることができます。図 2-23 は MULTADDSUBSUM sysDSP要素を示します。

#### 図2-23 MULTADDSUBSUM要素

## クロック、クロックイネーブル、およびリセット・リソース

配線からのグローバル・クロック、クロックイネーブル(CE)とリセット(RST)信号は全てのDSPブロックで使用できます。4つのクロック・ソース(CLK0、CLK1、CLK2、CLK3)から、1つのクロックがそれぞれの入力レジスタ、パイプライン・レジスタ、および出力レジスタ用に選択されます。同様に、CEとRSTは各4つのソース(CE0、CE1、CE2、CE3とRST0、RST1、RST2、RST3)から入力/パイプライン/出力レジスタでそれぞれ選択されます。

#### 異なる幅での符号あり・符号なし

DSPブロックはx9、x18、およびx36ビット幅以外に、符号あり・符号なしで乗算器の異なる幅をサポートします。符号なしオペランドにおいて、未使用の上位データビットは、有効なx9、x18またはx36オペランドを作成するために拡張されなければなりません。符号あり2の補数オペランドにおいて、x9、x18またはx36幅に達するまで、最上位ビット(MSB)の符号拡張は実行されるべきです。表2-7はこの例を示します。

表2-7 符号拡張に関する例

| 値  | 符号なし | 符号なし<br>9-bit | 符号なし<br><b>18-bit</b> | 符号あり | 2の補数<br>符号あり 9-bit | 2の補数<br>符号あり 18-bit |

|----|------|---------------|-----------------------|------|--------------------|---------------------|

| +5 | 0101 | 00000101      | 000000000000000101    | 0101 | 000000101          | 00000000000000101   |

| -6 | N/A  | N/A           | N/A                   | 1010 | 111111010          | 111111111111111010  |

#### MACからのOVERFLOWフラグ

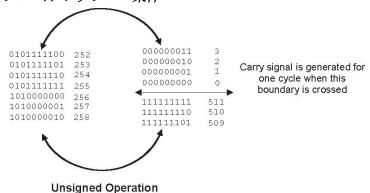

sysDSPブロックは、アキュムレータがオーバフローしたことを示すための出力を提供します。2つの符号なし数が加えられて、結果がそれらより小さい数になった時、アキュムレータ・ロールオーバが起こったと言い、オーバフロー信号が示されます。2つの正数が加算されその和が負であるとき、または2つの負数が加算され和が正数の場合、アキュムレータ・ロールオーバが起こったと言い、そしてオーバフロー信号が示されます。オーバフロー・フラグは1サイクルだけの間存在していますので、オーバフローがいつ起こるかに注意する必要があります。FPGAロジックでこれらのオーバフロー・パルスを数えることによって、より大きいアキュムレータを構成することができます。符号ありおよび符号なしオペランドでのオーバフロー状態は図2-24でリストアップされています。

#### 図2-24 アキュミュレータ・オーバフロー/アンダフロー条件

000000011 0101111100 252 000000010 Overflow signal is generated 0101111101 253 000000001 +1 for one cycle when this 0101111110 254 000000000 0101111111 255 boundary is crossed 111111111 -1 1010000000 256 111111110 1010000001 -3 111111101 1010000010 254 Signed Operation

# **IPexpress**<sup>™</sup>

ユーザは、それぞれのDSPモジュール(または、モジュールのグループ)を構成するオプションを持っている Lattice IPexpressツールか、或いは直接HDLインスタンス化を通してsysDSPブロックにアクセスすることができます。さらにラティスは、グラフィカルなシミュレーション環境であるSimulink®ツール内のインスタンス化をサポートするMathWorks®社とパートナになっています。SimulinkはDiamondと共に動作して、ラティスFPGAでのDSP設計サイクルを劇的に短くします。

#### 最適化されたDSP機能

ラティスは最適化されたDSP IP機能のライブラリを提供します。LatticeXP2用に用意されるIPは、ビット相関器、高速フーリエ変換、有限インパルス応答 (FIR)フィルタ、リードソロモン符号器/復号器、ターボ符号器/復号器、および畳み込み符号器/復号器などです。利用できるDSP IPコアの最新のリスト/ステータスについてはラティスまでお問い合わせください。

# LatticeXP2ファミリで利用できるリソース

表2-8はLatticeXP2ファミリの各メンバーの最大乗算器数を示します。表2-9はそれぞれのLatticeXP2ファミリ・デバイスにおいて利用できる最大EBR RAMブロックを示します。EBRブロックは、分散RAMと共に、高速DSP動作のために変数を局所的に格納するために用いることができます。

表2-8 LatticeXP2ファミリのDSPブロック数

| デバイス   | DSP ブロック | 9x9 乗算器 | 18x18乗算器 | 36x36乗算器 |

|--------|----------|---------|----------|----------|

| XP2-5  | 3        | 24      | 12       | 3        |

| XP2-8  | 4        | 32      | 16       | 4        |

| XP2-17 | 5        | 40      | 20       | 5        |

| XP2-30 | 7        | 56      | 28       | 7        |

| XP2-40 | 8        | 64      | 32       | 8        |

#### 表2-9 LatticeXP2ファミリの組み込みSRAM / TAGメモリ

| デバイス   | EBR SRAM<br>ブロック数 | 総 EBR SRAM<br>(Kbits) | TAG メモリ<br>(Bits) |

|--------|-------------------|-----------------------|-------------------|

| XP2-5  | 9                 | 166                   | 632               |

| XP2-8  | 12                | 221                   | 768               |

| XP2-17 | 15                | 276                   | 2184              |

| XP2-30 | 21                | 387                   | 2640              |

| XP2-40 | 48                | 885                   | 3384              |

# LatticeXP2ファミリDSPの性能

表2-10はLatticeXP2ファミリ各メンバーの最大性能を百万MAC毎秒(MMAC)の単位でリストしています。

表2-10 LatticeECPファミリのDSPブロック性能

| デバイス   | DSP ブロック | DSP性能 (MMAC) |

|--------|----------|--------------|

| XP2-5  | 3        | 3900         |

| XP2-8  | 4        | 5200         |

| XP2-17 | 5        | 6500         |

| XP2-30 | 7        | 9100         |

| XP2-40 | 8        | 10400        |

sysDSPの詳しい情報に関しては、テクニカルノートTN1140(LatticeXP2 sysDSP Usage Guide)を参照してください。

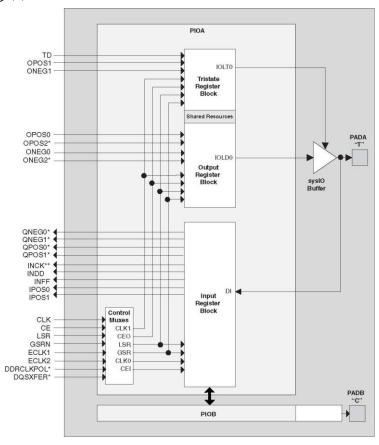

# プログラマブルI/Oセル(PIC)

各PICは図2-25に示されるように2PIOを含んでおり、これはそれぞれのsysIOバッファにそしてパッドに接続されています。PIOブロックは出力データ(DO)とトライステート制御信号(TO)をsysIOバッファに提供し、バッファから入力を受け取ります。表2-11にPIO信号リストがまとめられています。

#### 図2-25 PICダイヤグラム

<sup>\*</sup>Signals are available on left/right/bottom edges only.

\*\* Selected blocks.

図2-25に示されるように差動I/Oペアを提供するために隣接している2 PIOを組み合わせることができます。 パッドは2 PIOを区別するために "T" と "C" と表記されています。デバイスの左・右辺の約50%のPIOペア がLVDSドライバに構成できます。全I/Oペアが入力として動作できます。

# 表2-11 PIO信号リスト

| 名称                                      | タイプ                | 記述                                  |

|-----------------------------------------|--------------------|-------------------------------------|

| CE                                      | コアからの制御            | クロックイネーブル。入出力ブロックのFF用               |

| CLK                                     | コアからの制御            | システムクロック。入出力ブロック用                   |

| ECLK1, ECLK2                            | コアからの制御            | 高速エッジクロック                           |

| LSR                                     | コアからの制御            | ローカル・セット/リセット                       |

| GSRN                                    | 配線からの制御            | グローバル・セット/リセットt (Lowアクティブ).         |

| INCK <sup>2</sup>                       | コアへの入力             | プライマリ・クロック・ネットへの入力、またはPLL基準入力       |

| DQS                                     | PIOへの入力            | DQS信号。ロジック(配線)からPIOへ.               |

| INDD                                    | コアへの入力             | レジスタされないデータ入力                       |

| INFF                                    | コアへの入力             | クロック <b>(CLK0)</b> の立ち上がりでレジスタされる入力 |

| IPOS0, IPOS1                            | コアへの入力             | DDRとしてレジスタされる入力                     |

| QPOS0 <sup>1</sup> , QPOS1 <sup>1</sup> | コアへの入力             | コアのギアボックス(速度変換)パイプライン入力             |

| QNEG0 <sup>1</sup> , QNEG1 <sup>1</sup> | コアへの入力             | コアのギアボックス(速度変換)パイプライン入力             |

| OPOS0, ONEG0, OPOS2, ONEG2              | コアからのデータ出力         | コアからのSDRとDDR動作用出力信号                 |

| OPOS1, ONEG1                            | コアからのトライステ<br>ート制御 | DDR動作用トライステート・レジスタブロックへの出力          |

| DEL[3:0]                                | コアからの制御            | ダイナミック遅延制御入力                        |

| TD                                      | コアからのトライステ<br>ート制御 | SDR動作用.トライステート信号                    |

| DDRCLKPOL                               | クロック極性バスから<br>の制御  | DDR入力ブロックに与えられるクロック (CLK0)の極性を制御    |

| DQSXFER                                 | コアからの制御            | 出力ブロックへの制御信号                        |

- 1, デバイスの左右下辺のバンクのみ。上辺バンクはなし。

- 2, 特定のI/Oのみ

#### PIO

PIOは4ブロックを含んでいます。入力レジスタブロック、出力レジスタブロック、トライステート・レジスタブロック、および制御論理ブロックです。これらのブロックは、必要なクロックと選択ロジックと共に、種々モードで動作するためのレジスタを含んでいます。

#### 入力レジスタブロック

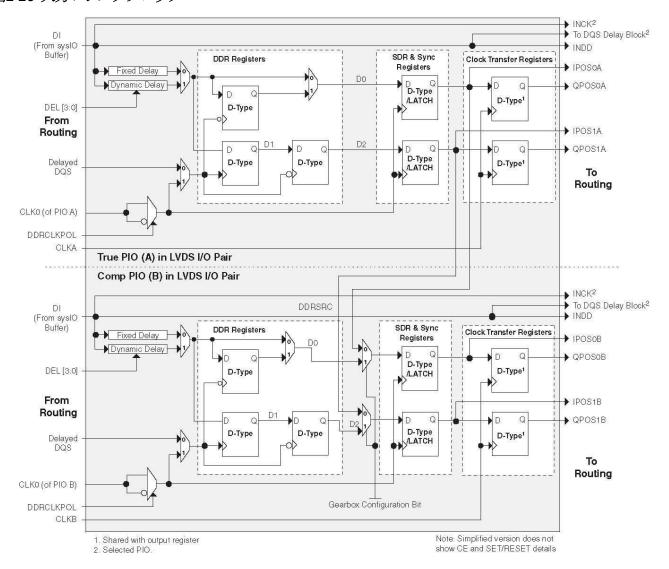

PIOの入力レジスタブロックは遅延素子とレジスタを含んでおり、DDRメモリインターフェイスやソースシンクロナスなどの高速インターフェイス信号がデバイスコアに渡される前に信号を整えるために用いることができます。図2-26は入力レジスタブロックのダイヤグラムです。

入力信号は(信号DIとして)sysIOバッファから入力レジスタブロックに加えられます。必要により、入力信号はレジスタと遅延素子をバイパスして、直接組み合わせ信号(INDD)、クロック(INCK)、或いは選択されたブロックのDQS遅延ブロックへの入力として用いることができます。入力遅延が必要な場合、設計者は固定遅延かダイナミック遅延DEL[3:0]を選択できます。遅延が選択されてグローバルクロックが用いられる場合、入力レジスタのホールド時間要件を緩和します。

入力ブロックは3動作モードを許容します。シングル・データレート(SDR)では、データはSDR同期レジスタ・ブロック内のレジスタの1つによってシステムクロックでサンプルされます。DDRモードでは、2つのレジスタが用いられ、DQS信号の正と負のエッジでデータをサンプルして、2本のデータストリーム、D0およびD2を作ります。これらの2つのデータストリーム(D0とD2)はコアに入る前にシステムクロックと同期化されます。より詳細は本データシートの"DDRメモリサポート"節を参照してください。

コンプリメンタリなPIOを結合し、出力ブロックからのレジスタをいくつか用いることでギアボックス(速度変換)機能が実装できます。これはPIOAに加えられた信号を4本のストリーム、

IPOS0A/IPOS1A/IPOS0B/IPOS1B、に分割します。図2-26はこのギアボックス機能を示します。このトピックについてのより詳細に関しては、TN1138 (LatticeXP2 High Speed I/O Interface)を参照してください。

信号DDRCLKPOLが同機レジスタに使用されるクロックの極性を制御します。これにより、データがDAQドメインからシステムクロックドメインに転送されるときの適切なタイミングを確保します。より詳細の議論については本データシートのDDR章を参照下さい。

# 図2-26 入力レジスタブロック

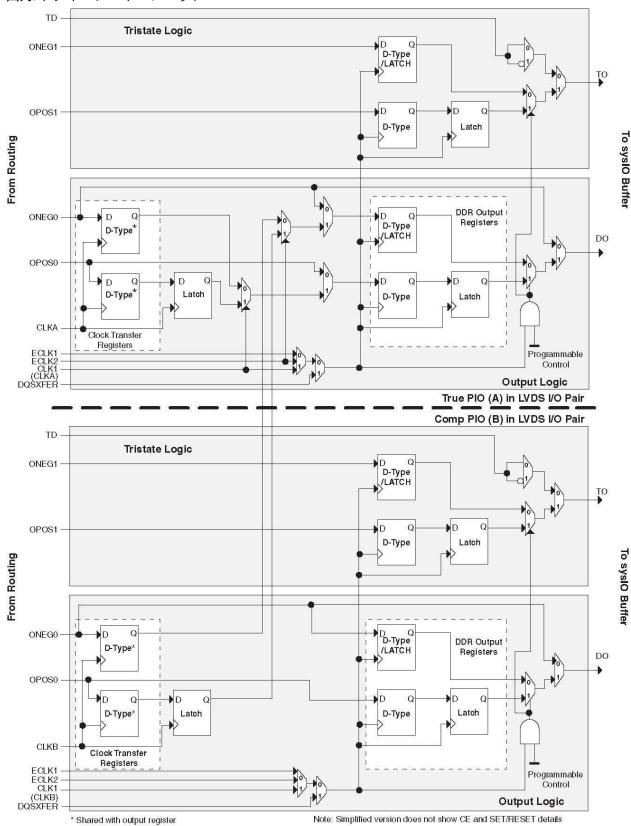

## 出力レジスタブロック

出力レジスタブロックでは、信号がデバイスのコアからsysIOバッファに渡される前にサンプルすることができます。本ブロックでデバイスの左右辺と下辺にあるPIOはSDR動作のためのレジスタを含んでおり、DDR動作のためのラッチと組み合わせられます。図2-27は出力レジスタブロックのダイヤグラムを示します。

SDRモードでは、ONEG0はフリップフロップの1つに与えられ、それが出力につながります。フリップフロップは、D-FFかラッチとして構成できます。DDRモードでは、ONEG0とOPOS0がクロックの正のエッジでレジスタに与えられ、そして次のサイクルでがOPOS0がラッチされます。同じクロックで動作するマルチプレクサが、出力(D0)に信号を与える正しいレジスタを選択します。

図2-27 出力/トライステート・ブロック

コンプリメンタリなPIOを結合し、出力ブロックからのレジスタをいくつか用いることでギアボックス(速度変換)機能が実装できます。これは4本のストリーム、ONEGOA/ONEG1A/ONEG0B/ONEG1B、を取り込みます。図2-27はこの動作について示しています。より詳細に関しては、TN1138を参照してください

#### トライステート・レジスタブロック

トライステート・レジスタブロックでは、信号がデバイスのコアからsyslOバッファに渡される前にサンプルすることができます。このブロックはSDR動作のためのレジスタと、DDR動作のための追加ラッチを含んでいます。図2-27はトライステート・レジスタブロックのダイヤグラムを出力ブロックと共に示します。

SDRモードでは、ONEG1がフリップフロップの1つに与えられ、それが出力につながります。フリップフロップは、D-FFかラッチとして構成できます。DDRモードでは、ONEG1とOPOS1がクロックの正のエッジでレジスタに与えられ、そして次のクロックでOPOS1がラッチされます。同じクロックで動作するマルチプレクサが、出力(D0)に信号を与える正しいレジスタを選択します。

#### 制御ロジックブロック

制御ロジックブロックは、PIOブロック内で使用される制御信号の選択と変更を可能にします。クロックは、汎用の配線から提供されたクロック信号か、エッジクロックの一方(ECLK1/ECLK2)、或いはプログラマブルDQSピンから提供されたDQS信号の1つから選択されて入力レジスタブロックに与えます。クロックを反転するオプションがあります。

#### DDRメモリサポート

PICには高速のソースシンクロナスやDDRメモリインターフェイスの実装を可能にする回路が付加されています。

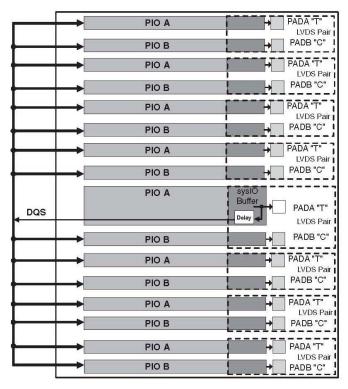

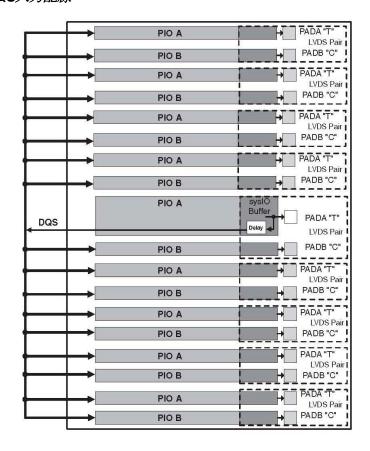

PICにはDDRメモリ・インターフェイスをサポートするためのレジスタ素子があります。左右辺のインターフェイスは16ビットデータをサポートするメモリ用に設計されており、これに対して上下辺では18ビットデータのメモリをサポートします。16本のPIO毎に1つ(左右辺)、或いは18本のPIO毎に1つ(上下辺)DQS信号の生成を容易にする遅延素子を含んでいます。DQS信号は16/18 PIOにまたがるDQSバスに与えられます。図2-28と図2-29は各組に配置されるDQSピンの対応を示します。

正確なDQSピン位置については、本データシートのPinout Information内で "Logic Signal Connection" 表内に "Dual Function" として与えられています (注;オリジナルの英語版データシートを参照。日本語版にはありません)。バスからのDQS信号はメモリからのDDRデータを入力レジスタブロックに取り込むストローブとして用いられます。DDRメモリサポートを使用する場合の記述はTN1138を参照願います。

図2-28 左右辺I/OのDQS入力配線

図2-29 上下辺 I/OのDQS入力配線

#### DLLにより較正されるDQS遅延ブロック

一般に、ソースシンクロナス・インターフェイスは、入力レジスタで正しくデータをキャプチャするために入力クロックが調整されることを必要とします。殆んどのインターフェイスにおいてはPLLがこの調整に用いられますが、DDRメモリではクロック(DQSと呼ばれる)は、フリーランしていませんので、このアプローチを用いることができません。DQS遅延ブロックは必要なクロック・アライメントをDDRメモリ・インターフェイスに提供します。

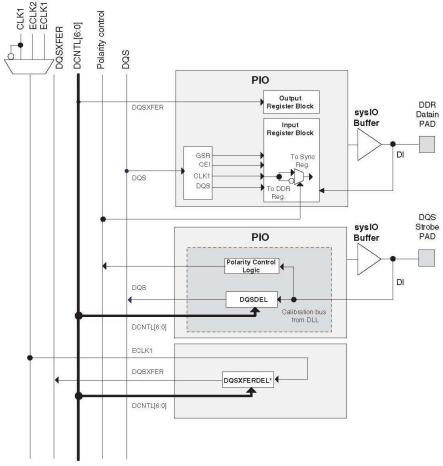

DQS信号(特定のPIOのみ。図2-30参照)はパッドからDQS遅延素子を介して専用のDQS配線リソースに加えれられます。DQS信号はまた、クロック極性制御ロジックにも与えられ、これは入力レジスタ・ブロック内の同期化レジスタへのクロックの極性を制御します。図2-30と図2-31はDQS転送信号がPIOにどのように配線されるかを示します。

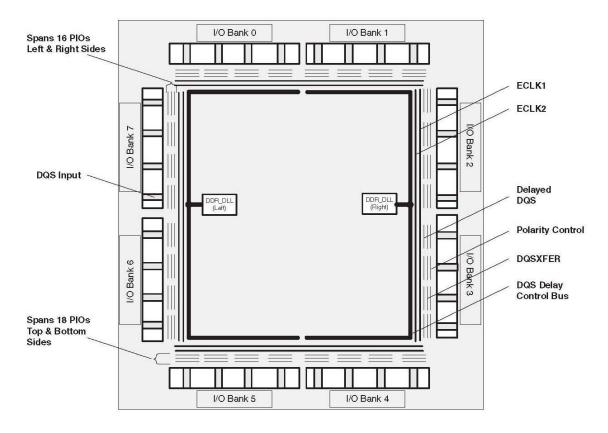

DQS遅延ブロックの温度、電圧、およびプロセス変動は、互いにデバイスの反対側に位置する2個の専用DLL (DDR\_DLL) から与えられる1組の較正信号(6ビットのバス)によって補償されます。各DLLは図2-30に示されるようにデバイスの半分でDQS遅延を補償します。DLLは、システムクロックとフィードバック・ループによって温度、電圧、およびプロセス変動が補償されます。

図2-30 エッジクロック、DLL較正(calibration)バスとDQSローカルバスによる分配

#### 図2-31 DQS ローカル・バス

\*DQSXFERDEL shifts ECLK1 by 90% and is not associated with a particular PIO.

## 極性制御ロジック

典型的なDDRメモリ・インターフェイスの設計では、入力される遅れたDQSストローブと内部のシステムクロック(リードサイクルの間)との位相関係は未知です。LatticeXP2ファミリはこれらドメイン間のデータ転送のための専用回路を含んでいます。ドメイン転送のときにシステムクロックに対するセットアップ/ホールド時間違反を防ぐため、クロック極性セレクタが使用されます。これはデータが入力レジスタブロック内の同期レジスタでサンプルされるエッジを変えますが、正しいクロック極性のためにはそれぞれのリードサイクルの始めでのタイミング評価を必要とします。

DDRメモリの読み出し動作の前に、DQSは(終端抵抗が接続された)トライステート状態にあります。DDRメモリデバイスはプリアンブル・ステートの始めでDQSをLowにドライブします。専用回路がプリアンブル・ステートのあとの最初のDQS遷移を検出し、検出信号は同期レジスタへのクロック極性制御に用いられます。

#### **DQSXFER**

LatticeXP2は、90°シフトされたDQSストローブが必要なDDRメモリのため、出力バッファにDQSXFER信号を提供します。これはDQSDELブロックで生成され、DQSスパンのデータバスで使用できます。

# syslOバッファ

それぞれのI/OはsysIOバッファと呼ばれるフレキシブルなバッファです。これらのバッファは、デバイスの周囲にバンクと呼ばれるグループで配置されています。sysIOバッファは、ユーザはLVCMOS、SSTL、HSTL、LVDS、およびLVPECLを含む、今日のシステムで見られる広範な規格の実装を可能にします。

## sysIOバッファバンク

LatticeXP2デバイスには、8つのsysIOバッファバンクがあり、各辺に2バンクあります。それぞれのバンクが複数のI/O規格をサポートすることができます。各sysIOバンクにはそれ自身のI/O電源電圧( $V_{CCIO}$ )があり、加えて2本の参照電圧 $V_{REF1}$ 、 $V_{REF2}$ のリソースがあることで、それぞれのバンクを互いに完全に独立させることができます。図2-32は8つのバンクとそれらに関連する電源電圧を示します。

LatticeXP2デバイスでは、シングルエンド出力バッファとレシオ入力バッファ(LVTTL、LVCMOS、および PCI)は、 $V_{CCIO}$ を用いて電源が与えられます。また、 $V_{CCIO}$ の如何にかかわらず、LVTTL、LVCMOS33、LVCMOS25、およびLVCMOS12入力には固定スレッショルドを設定することができます。

各バンクは、基準電圧を参照する入力バッファにスレッショルドを設定する $V_{REF}$ 電圧を2つ( $V_{REF1}$ と $V_{REF2}$ )別々にサポートすることができます。LatticeXP2デバイスでは、いくつかの決まったI/Oピンをバンクにおける参照電圧ピンになるように構成することができます。それぞれのI/Oはバンクへの電源電圧と参照電圧に基づいて個別に構成可能です。

TOP

#### 図2-32 LatticeXP2のバンク

VCCIO0 Bank 0 Bank 1 V<sub>CCIO7</sub> V<sub>CCIO2</sub> V<sub>REF1(2)</sub> V<sub>REF1(7)</sub> V<sub>REF2(7)</sub> V<sub>REF2(2)</sub> GND GND LEFT V<sub>CCIO6</sub> V<sub>CCIO3</sub> V<sub>REF1(3)</sub> V<sub>REF1(6)</sub> V<sub>REF2(3)</sub> V<sub>REF2(6)</sub> GND GND Bank 5 Bank 4 VREF1(5) -VREF2(5) -VREF2(4) -VCCI05 GND GND

BOTTOM

LatticeXP2デバイスは2つのタイプのsysIOバッファペアを含んでいます。

1. 上下辺 (バンク**0/1/4/5**) のsysl**O**バッファペア(シングルエンド出力のみ)

デバイスの上下辺バンクにおけるsyslOバッファペアは、2シングルエンド出力ドライバと2組のシングルエンド入力バッファ(レシオ型と参照電圧使用型共に)から成ります。参照電圧ありの入力バッファは差動入力として構成することもできます。

ペアとなる2個のパッドは "True" と "Comp" として記述されます。Trueパッドが差動入力バッファの正側 (信号) を表し、Comp(コンプリメンタリ)パッドが差動入力バッファの反転側 (信号) を表します。上下辺バンクのI/OはプログラマブルPCIクランプがあります。

2. 左右辺 (バンク2/3/6/7) のsyslOバッファペア(50%が差動出力、及び100%のシングルエンド出力) デバイスの左右辺バンクにおけるsyslOバッファペアは、2シングルエンド出力ドライバと2組のシングルエンド入力バッファ(レシオ型と参照電圧使用型共に)、および差動出力ドライバ1つから成ります。参照電圧ありの入力バッファの一方は差動入力として構成することもできます。

ペアとなる2個のパッドは "True" と "Comp" として記述されます。Trueパッドが差動I/Oの正側(信号) を表し、Comp(コンプリメンタリ)パッドが差動のI/Oの反転側(信号) を表します。 左右辺バンクの50%にのみ、真のLVDSの差動出力ドライバがあります。

#### 典型的な電源投入時の1/0の振る舞い

内部パワーオンリセット (POR) 信号は、 $V_{CC} \geq V_{CCAUX}$ が所定のレベルに達すると解除されます。その後FPGA コアロジックが動作を開始します。アプリケーションにとって非常に重要な全I/Oバンクの出力ポートのレベルを適切に制御するために、入力ポートのレベルが有効であるのを確実にすることは、設計者の責任で行う必要があります。パワーアップ時の出力ロジック制御と有効入力レベルの詳細については、テクニカルノートTN1136(LatticeXP2 sysIO Usage Guide)を参照してください。

$V_{CC}$ と $V_{CCAUX}$ はFPGAコアファブリックに、また $V_{CCIO}$ はI/Oバッファに電源を供給します。常に一貫して予測できるI/Oの振舞いを確保しつつも、システム設計を簡易化するためには、FPGAコアファブリックよりも先にI/Oバッファに電源が供給されることを推奨します。即ち、 $V_{CCIO}$ を $V_{CCAUX}$ よりも早く供給するか、或いは同時に供給するべきです。

#### サポートするsysIO規格

LatticeXP2 sysIOバッファは、シングルエンドと差動の規格を共にサポートします。シングルエンド規格はさらにLVCMOS、LVTTL、および他の規格に細分することができます。バッファはLVTTL、LVCMOS1.2V/1.5V/1.8V/2.5V/3.3V規格をサポートします。LVCMOSとLVTTLモードでは、バッファはドライブ強度、バスメンテナンス(弱いプルアップ、弱いプルダウン、またはバスキーパ・ラッチ)、およびオープンドレインとして個別に構成可能なオプションがあります。サポートする他のシングルエンド規格にはSSTLとHSTLを含みます。サポートされる差動の規格にはLVDS、MLVDS、BLVDS、LVPECL、RSDS、差動SSTL、および差動HSTLが含まれます。表2-12と表2-13は、LatticeXP2デバイスでサポートされるI/O規格を、それらの電源電圧と参照電圧と共に示します。sysIOバッファを利用する種々規格のサポートの詳細については、テクニカルノートTN1136を参照してください。

表2-12 サポートする入力規格

| 入力規格                             | V <sub>REF</sub> (公称值) | V <sub>ccio</sub> ¹ (公称值) |

|----------------------------------|------------------------|---------------------------|

| シングルエンド・インターフェイス                 |                        |                           |

| LVTTL                            | _                      | _                         |

| LVCMOS33                         | _                      | _                         |

| LVCMOS25                         |                        | _                         |

| LVCMOS18                         |                        | 1.8                       |

| LVCMOS15                         |                        | 1.5                       |

| LVCMOS12                         | 1                      | _                         |

| PCI33                            |                        | _                         |

| HSTL18 クラス I, II                 | 0.9                    | _                         |

| HSTL15 クラス I                     | 0.75                   | _                         |

| SSTL33 クラス I, II                 | 1.5                    | _                         |

| SSTL25 クラス I, II                 | 1.25                   | _                         |

| SSTL18 クラス I, II                 | 0.9                    | _                         |

| 差動インターフェイス                       |                        |                           |

| 差動 SSTL18 クラス I, II              | _                      | _                         |

| 差動 SSTL25 クラス I, II              | _                      | _                         |

| 差動 SSTL33 クラス I, II              | _                      | _                         |

| 差動 HSTL15 クラス I                  | _                      | _                         |

| 差動 HSTL18 クラス I, II              |                        | _                         |

| LVDS, MLVDS, LVPECL, BLVDS, RSDS |                        | _                         |

<sup>1.</sup> 特に明記しない場合 Vccio は有効な動作範囲内のどの値にも設定可能 (ページ3-1)

表2-13 サポートする出力規格

| 出力規格                 | ドライブ                       | V <sub>ccio</sub> (公称值) |

|----------------------|----------------------------|-------------------------|

| シングルエンド・インターフェイス     |                            |                         |

| LVTTL                | 4mA, 8mA, 12mA, 16mA, 20mA | 3.3                     |

| LVCMOS33             | 4mA, 8mA, 12mA 16mA, 20mA  | 3.3                     |

| LVCMOS25             | 4mA, 8mA, 12mA, 16mA, 20mA | 2.5                     |

| LVCMOS18             | 4mA, 8mA, 12mA, 16mA       | 1.8                     |

| LVCMOS15             | 4mA, 8mA                   | 1.5                     |

| LVCMOS12             | 2mA, 6mA                   | 1.2                     |

| LVCMOS33, オープンドレイン   | 4mA, 8mA, 12mA 16mA, 20mA  | _                       |

| LVCMOS25, オープンドレイン   | 4mA, 8mA, 12mA 16mA, 20mA  | <del></del>             |

| LVCMOS18, オープンドレイン   | 4mA, 8mA, 12mA 16mA        | <del>_</del>            |

| LVCMOS15, オープンドレイン   | 4mA, 8mA                   | <del>_</del>            |

| LVCMOS12, オープンドレイン   | 2mA, 6mA                   | <del>-</del>            |

| PCI33                | N/A                        | 3.3                     |

| HSTL18 クラス I, II     | N/A                        | 1.8                     |

| HSTL15 クラス I         | N/A                        | 1.5                     |

| SSTL33 クラス I, II     | N/A                        | 3.3                     |

| SSTL25 クラス I, II     | N/A                        | 2.5                     |

| SSTL18 クラス I, II     | N/A                        | 1.8                     |

| 差動インターフェイス           |                            |                         |

| 差動 SSTL33, クラス I, II | N/A                        | 3.3                     |

| 差動 SSTL25, クラス I, II | N/A                        | 2.5                     |

| 差動 SSTL18, クラス I, II | N/A                        | 1.8                     |

| 差動 HSTL18, クラス I, II | N/A                        | 1.8                     |

| 差動 HSTL15, クラス I     | N/A                        | 1.5                     |

| LVDS <sup>12</sup>   | N/A                        | 2.5                     |

| MLVDS 1              | N/A                        | 2.5                     |

| BLVDS 1              | N/A                        | 2.5                     |

| LVPECL 1             | N/A                        | 3.3                     |

| RSDS <sup>1</sup>    | N/A                        | 2.5                     |

| LVCMOS33D 1          | 4mA, 8mA, 12mA 16mA, 20mA  | 3.3                     |

- 1. 外部抵抗でエミュレート。TN1138を参照して下さい。

- 2. 左右辺では50%のI/Oで専用差動LVDSドライバがサポートされます。これは外部抵抗が不要です。

## ホット・ソケッティング(活線挿抜)

パワーアップやパワーダウンの間、確実に予測できる振舞いをするようにLatticeXP2デバイスは入念に設計されました。電源投入は順不同にすることができます。パワーアップとパワーダウン・シーケンスの間、電源電圧が信頼できる動作を確実にすることができるくらい高くなるまで、I/Oはトライステートのままです。さらに、I/Oピンへのリークは仕様範囲内に制御されますので、これによりシステムの他部分とのインテグレーションが容易にできます。この機能でLatticeXP2を多くの複数電源やホットスワップのアプリケーションに理想的です。

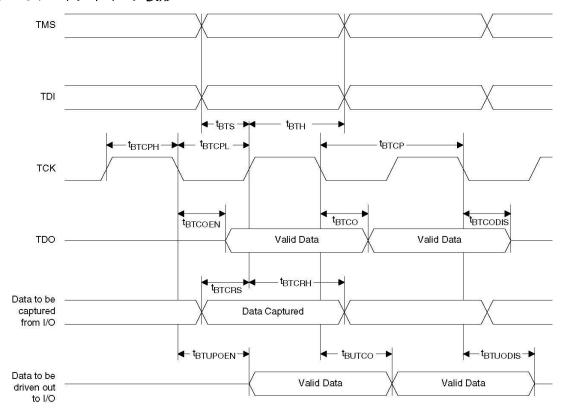

#### IEEEの1149.1準拠のバウンダリスキャン・テスタビリティ

すべてのLatticeXP2デバイスには、IEEE1149.1準拠のテストアクセス・ポート(TAP)を通してアクセスされるバウンダリスキャン・セルがあります。これは、すべての重要なロジックノードにアクセスすることができるシリアル・スキャンパスを通して、デバイスが搭載される回路基板の機能的なテストを可能にします。内部レジスタはリンクされており、テストデータがシフトインされて直接テストノードにロードされるか、または検証のためにテストデータをキャプチャしてシフトアウトすることができます。テストアクセス・ポートはTDI、TDO、TCK、およびTMSの専用I/Oから成ります。テストアクセス・ポートは、それ自身の電源電圧 $V_{CCJ}$ を持っていて、LVCMOS3.3/2.5/1.8/1.5/1.2の規格で動作することができます。詳細はテクニカルノートTN1141(LatticeXP2 sysCONFIG Usage Guide)を参照してください。

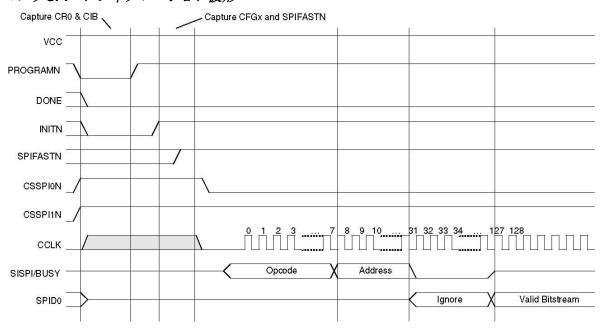

#### flexiFLASHデバイス・コンフィグレーション

LatticeXP2デバイスは、デバイスのプログラミングとコンフィグレーションにおける柔軟性をユーザに提供するために、フラッシュメモリとSRAMを共に集積しています。図2-33はデバイス内でのフラッシュメモリとSRAMコンフィグレーション・セルのアレンジメントの概観を示します。このセクションの残りはこれらの機能の概要を記述します。より詳細な記述に関してはTN1141(LatticeXP2 sysCONFIG Usage Guide)を参照してください。

Massively Parallel Data Transfer **EBR Blocks** Instant-ON Flash for Single-Chip SRAM Solution Configuration Bits FlashBAK for EBR Storage Device Lock for Design Security TAG Decryption Memory and Device Lock SPI and JTAG

図2-33 LatticeXP2デバイスのフラッシュメモリとSRAMコンフィグレーション・セルの概要

パワーアップ時や、ユーザコマンドで、オンチップ・フラッシュメモリからデバイスの動作を制御するSRAM コンフィグレーション・セルにデータが転送されます。膨大な幅のパラレルバスによって、供給電源が有効レベルに達してから数ミリ秒以内に動作することを可能にします。この機能はインスタントオンと呼ばれています。

オンチップ・フラッシュは外付けブートメモリの必要性を排除するシングルチップ・ソリューションを可能にします。デバイスのJTAGかスレーブSPIポートを通してこのフラッシュをプログラムすることができます。また、JTAGとマスターSPIポートを通してSRAMコンフィグレーション・スペースを何度でも再コンフィグレーションすることができます。JTAGポートはIEEE1149.1とIEEE1532に準拠します。

データシートのEBRセクションで説明されるように、FlashBAK機能はデバイス・コンフィグレーションを 消去するとかプログラミングを変えることなく、EBRブロックの内容をフラッシュ格納領域に書き出すこと を可能にします。またシリアルTAGメモリも、較正係数やエラーコードなど少量のデータを格納するために 使用できます。 セキュリティが重要であるアプリケーションにとっては、デバイス外部にビットストリームが露出しないので、SRAMのみのFPGAより本質的に安全です。これはデバイスをロックすることによって、より機能アップされます。デバイスは3つのモードのいづれかにあります。

- 1.アンロック状態

- **2.**キーロックされた状態; プログラミング・インターフェイスを通してキーを提示することが、デバイスのアンロックを可能にします。

- 3.永久にロックされた状態; デバイスは永久にロックされます。

さらにデバイスセキュリティの補足となるように、ワンタイム・プログラマブル(OTP)モードが利用できます。デバイスがこのモードに一度設定されると、デバイスのフラッシュ部分の消去や再プログラムは不可能です。

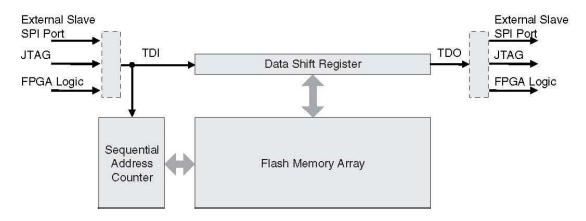

#### Serial TAGメモリ

LatticeXP2デバイスはSerial TAGメモリとして0.6kbitから3.3kbitのフラッシュメモリを提供します。TAGメモリは電子IDコード、バージョンコード、日付スタンプ、資産ID、および較正設定などを含む不揮発格納領域として用いることができるオンチップ・フラッシュです。TAGメモリのブロック図は図2-34で示されます。TAGメモリは外部SPIフラッシュと同様にアクセスされ、JTAG、外部スレーブSPIポート、または直接FPGAロジックから読み出しやプログラムが可能です。TAGメモリを読むためには、スタートアドレスを指定することで、全TAGメモリの内容がファーストイン・ファーストアウト方法でシリアルに出力されます。TAGメモリはデバイス・コンフィグレーションに用いられるフラッシュから独立していて、デバイスのセキュリティ設定にかかわらず、汎用格納機能の用途としていつでもアクセスできます。より詳細に関してはTN1137 (LatticeXP2 Memory Usage Guide)、およびTN1141 (LatticeXP2 sysCONFIG Usage Guide)を参照してください。

#### 図2-34 シリアル・タグメモリブロック図

#### ライブアップデート・テクノロジ

多くのアプリケーションがFPGAのフィールド・アップデートを必要とします。LatticeXP2デバイスは、システム稼働への影響を最小にしながら、安全かつフェールセイフを確保した方法で、そのコンフィグレーションを可能にする3つの機能を提供します

#### 1. 暗号化の対応

LatticeXP2デバイスは、128ビットでAESコード化されたビットストリームを復号化するキーの格納用にオンチップ不揮発メモリを提供するため、デザインを安全にし、著作権侵害を思いとどまらせます。

#### 2. TransFR (Transparent Field Reconfiguration; トランスペアレントなフィールド再構成)

TransFR I/O(TFR)はユニークなラティス・テクノロジで、ユーザがただ一つのispVMコマンドを用いることで、システムの稼働を中断することなくフィールドでそのロジックを更新するものです。TransFR I/Oでは、デバイス・コンフィグレーションの間、I/Oステートをフリーズすることができます。これは、最小のシステム中断・休止時間でデバイスをフィールドで更新することを可能にします。より詳細に関してはTN1143(LatticeXP2 TransFR I/O)を参照してください

#### 3. デュアルブート・イメージの対応

デュアルブート・イメージは、システムFPGAのコンフィギュレーション・データをより信頼できるリモート・アップデートを必要とするアプリケーションのためにサポートされます。システムが基本コンフィグレーションで動作している時に、新しいブートイメージをリモート・ダウンロードして、コンフィグレーション記憶デバイスの別の領域に格納することができます。アップデートの後にいつでも、この新しいコンフィグレーション・ファイルからLatticeXP2をリブートすることができます。新しいブートイメージが、ダウンロード時にエラーが混入したデータとなったり、誤ったバージョン番号であるなどの問題があれば、LatticeXP2デバイスはオリジナルのバックアップ・コンフィグレーションに戻って、再試行することができます。これはシステムの電源をオフして続いてオンすること(サイクリング)なく可能です。より詳細に関してはTN1220 (LatticeXP2 Dual Boot Feature)を参照してください。

デバイス・コンフィグレーションの詳しい情報に関しては、TN1141を参照してください。

#### ソフトエラー検出(SED)サポート

LatticeXP2デバイスにはCRCチェックを実行する専用ロジックがあります。コンフィグレーション中、CRC ブロックでコンフィギュレーション・データ・ビットストリームをチェックすることができます。さらにコンフィグレーションSRAMのソフトエラーをチェックする(SED)ようにLatticeXP2デバイスを設定することができます。このSED機能はユーザ回路が非動作中に実行できます。ユーザモード(通常動作)の間ソフトエラーが起こった場合、既知の問題ないブートイメージを(内部フラッシュか外部SPIメモリから)再ロードするか、または外部にエラー信号を通知することができます。

ソフトエラー検出(SED)サポートの詳しい情報に関しては、テクニカルノートTN1130 (LatticeXP2 Soft Error Detection Usage Guide) を参照してください。

#### オンチップ・オシレータ

全LatticeXP2デバイスが、コンフィグレーション用のマスタクロックCCLKを得るために用いられる内部CMOSオシレータを持っています。オシレータとCCLKは連続して動作し、コンフィグレーションが終了後ユーザロジックで使用できます。表2-14は利用できる周波数を記載します。デザインの過程で異なるCCLK周波数が選択されるとき、以下のシーケンスが行われます。

- 1. デバイスはデフォルト(2.5MHz)CCLK周波数で立ち上がります

- 2. コンフィグレーション時、ユーザは異なるマスタシリアル・クロック周波数を選択します

3. クロックのコンフィグレーション用ビットが入力されるとCCLK周波数が選択された周波数に変化します

内部CMOSオシレータはユーザが使用でき、クロックツリーへの入力ソースとして使用できます。コンフィグレーション用オシレータの詳しい情報に関しては、テクニカルノートTN1141を参照してください。

表2-14 選択可能なコンフィグレーション時のCCLKとユーザモードでのオシレータ周波数

| CCLK・オシレータ (MHz) |

|------------------|

| 2.5 <sup>1</sup> |

| 3.1 <sup>2</sup> |

| 4.3              |

| 5.4              |

| 6.9              |

| 8.1              |

| 9.2              |

| 10               |

| 13               |

| 15               |

| 20               |

| 26               |

| 32               |

| 40               |

| 54               |

| 80 <sup>3</sup>  |

| 163 <sup>3</sup> |

- 1. ソフトウェアがデフォルトにするオシレータ周波数

- 2. ソフトウェアがデフォルトにするCCLK周波数

- 3. CCLKには設定できない周波数

#### ロジック集積度の移行(マイグレーション)

異なるロジック集積度のデバイスでも同じパッケージで同一ピン配置であることを保証するようにLatticeXP2ファミリは設計されています。さらにアーキテクチャは、小さいロジック集積度のデバイスからより大きいロジック集積度のデバイスに設計のマイグレーションを行うときに、高い成功率を確実にします。また多くの場合、高密度デバイスの低い使用効率の設計を、小さいロジック集積度のデバイスにターゲットを移行させることも可能です。しかしながら、最終的なリソース使用効率の正確な詳細は、それぞれのケースで成功の確からしさに影響を与えるでしょう。

## LatticeXP2ファミリデータシート DCおよびスイッチング特性

## 絶対最大定格123

| 供給電源 $V_{CC}$ 0.5 $\sim$                                   | 1.32V |

|------------------------------------------------------------|-------|

| 共給電源 V <sub>CCAUX</sub> 0.5 ~                              | 3.75V |

| 共給電源 V <sub>CCJ</sub> 0.5 ~                                | 3.75V |

| 共給電源 V <sub>CCPLL</sub> <sup>4</sup>                       | 3.75V |

| 出力供給電源 V <sub>CCIO</sub>                                   | 3.75V |

| 人力又はトライステート <b>I/O</b> に加えられる電圧 <sup>5</sup> <b>-0.5</b> ~ | 3.75V |

| R.存温度(周囲)65 ~                                              | 150℃  |

| バイアス下ジャンクション温度(Ti)                                         | 125℃  |

- 1. "絶対最大定格" で記載された以上のストレスはデバイスに永久的な損傷を引き起こすかもしれません。これら条件下で、或いはこれら仕様項目の推奨動作条件セクションで示される以外のいかなる他の条件下でも、デバイスの機能的な動作を暗示するものではありません。

- 2. ラティス "Thermal Management" (熱管理) ドキュメントに従うことが必要です。

- 3. 全ての電圧はGND基準です。

- 4. V<sub>CCPLL</sub> があるのはcsBGA, PQFP, TQFP各パッケージのみ。

- 5. -2V ~(V<sub>IHMAX</sub> + 2)Vまでのオーバシュートとアンダシュートは<20nsの期間は許容されます。

#### 推奨動作条件

| シンボル                                 | パラメータ                      | Min.  | Max.  | 単位           |

|--------------------------------------|----------------------------|-------|-------|--------------|

| $V_{CC}$                             | コア電源電圧                     | 1.14  | 1.26  | V            |

| V <sub>CCAUX</sub> <sup>4</sup>      | 補助(Auxiliary)電源電圧          | 3.135 | 3.465 | V            |

| V <sub>CCPLL</sub> <sup>1</sup>      | PLL電源電圧                    | 3.135 | 3.465 | V            |

| V <sub>CCIO</sub> <sup>2, 3, 4</sup> | I/Oドライバ電源電圧                | 1.14  | 3.465 | V            |

| V <sub>CCJ</sub> <sup>2</sup>        | IEEE1149.1テスト・アクセス・ポート電源電圧 | 1.14  | 3.465 | V            |

| $t_{\text{JCOM}}$                    | ジャンクション温度、コマーシャル動作         | 0     | +85   | ${}^{\sim}$  |

| t <sub>JIND</sub>                    | ジャンクション温度、インダストリアル動作       | -40   | 100   | $^{\circ}$ C |

- 1. V<sub>CCPLL</sub> があるのはcsBGA, PQFP, TQFP各パッケージのみ

- 2.  $V_{CCIO}$  や $V_{CCJ}$  が1.2Vに設定される場合、それらは $V_{CC}$  と同じ電源に接続のこと。また $V_{CCIO}$  や $V_{CCJ}$  が3.3Vに設定される場合、それらは $V_{CCAUX}$  と同じ電源に接続のこと。

- 3. 後述の表で示すI/O規格毎の推奨電圧を参照のこと。

- 4. 予期せぬI/Oの振る舞いを避けるためにVccioはVccaux と同時か先にオフすること。

- 5. fpBGAおよびftBGAパッケージでは、PLLはV<sub>CCAUX</sub> に接続され、その電源としています。

#### オンチップ・フラッシュメモリ仕様

| シンボル    | パラメータ                                                     | Max     | 単位   |

|---------|-----------------------------------------------------------|---------|------|

|         | t <sub>RETENTION</sub> フラッシュメモリのプログラミング・サイクル <sup>1</sup> | 10,000  | サイクル |

| PROGCYC | フラッシュメモリ機能のプログラミング・サイクル                                   | 100,000 | リイクル |

1. 最小データリテンション $t_{RETENTION}$  は20年です。

## ホット・ソケッティング (活線挿抜) 仕様 1234

| シンボル     | パラメータ        | 条件                             | Min. | Тур. | Max  | 単位 |

|----------|--------------|--------------------------------|------|------|------|----|

| $I_{DK}$ | 入力、I/Oのリーク電流 | $0 \le V_{IN} \le V_{IH}(MAX)$ | 1    | 1    | +/-1 | mΑ |

- 1. Vcc、Vccaux 及び Vccio のシーケンスは順不同。ただし、いずれも単調増加・降下レートであることを仮定

- $2.0 \le V_{CC} \le V_{CC}$  (MAX),  $0 \le V_{CCIO} \le V_{CCIO}$  (MAX),  $\sharp \hbar t \downarrow 0 \le V_{CCAUX} \le V_{CCAUX}$  (MAX)

- 3. l<sub>DK</sub> は l<sub>PU</sub> 、l<sub>PW</sub> 、または l<sub>BH</sub> に加算される

- 4. LVCMOSとLVTTLのみ

#### ESD性能

ESD性能を含む信頼性データに関しては、別途提供されているサマリレポート<u>LatticeXP2 Product Falimy</u> Qualification Summaryをご参照ください。

#### DC電気的特性

| シンボル                                           | パラメータ                            | 条件                                                                                   | Min.                  | Тур. | Max.                  | 単位 |

|------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------|-----------------------|------|-----------------------|----|

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1</sup> | <br>  入力、又は <b>I/O</b> のリーク電流    | $0 \le V_{IN} \le V_{CCIO}$                                                          | _                     | 1    | 10                    | uA |

| IIL, IIH                                       | <b>八刀、又は  Oのサーク 电</b> 流<br>      | $V_{CCIO} \leq V_{IN} \leq V_{IH} (MAX)$                                             | _                     | 1    | 150                   | uA |

| $I_{PU}$                                       | I/Oアクティブ・プルアップ電流                 | $0 \le V_{IN} \le 0.7 V_{CCIO}$                                                      | -30                   | 1    | -150                  | uA |

| $I_{PD}$                                       | I/Oアクティブ・プルダウン電流                 | $V_{IL}$ (MAX) $\leq V_{IN} \leq V_{CCIO}$                                           | 30                    | _    | 210                   | uA |

| I <sub>BHLS</sub>                              | バスホールドLow維持電流                    | $V_{IN} = V_{IL} (MAX)$                                                              | 30                    | _    | _                     | uA |

| I <sub>BHHS</sub>                              | バスホールドHigh維持電流                   | V <sub>IN</sub> = 0.7V <sub>CCIO</sub>                                               | -30                   | _    | _                     | uA |

| I <sub>BHLO</sub>                              | バスホールドLowオーバドライブ電<br>流           | $0 \le V_{IN} \le V_{CCIO}$                                                          | -                     | ı    | 210                   | uA |

| I <sub>внно</sub>                              | バスホールド <b>High</b> オーバドライブ電<br>流 | $0 \le V_{IN} \le V_{CCIO}$                                                          | _                     | ı    | -150                  | uA |

| $V_{BHT}$                                      | バスホールド・トリップ・ポイント                 |                                                                                      | V <sub>IL</sub> (MAX) | _    | V <sub>IH</sub> (MIN) | V  |

| C1                                             | I/O容量 <sup>3</sup>               | $V_{CCIO} = 3.3V, 2.5V, 1.8V, 1.5V, 1.2V, V_{CC} = 1.2V, V_{IO} = 0 to V_{IH} (MAX)$ | -                     | 8    | ı                     | pf |

| C2                                             | 専用入力の容量 2                        | $V_{CCIO} = 3.3V, 2.5V, 1.8V, 1.5V, 1.2V, V_{CC} = 1.2V, V_{IO} = 0 to V_{IH} (MAX)$ | _                     | 6    |                       | pf |

<sup>1.</sup> 入力やI/Oのリーク電流は、出力ドライバをトライステートにし、ピンは入力として、またはI/Oとして構成して測定される。 出力ドライバがアクティブな状態では測定されない。バスメンテナンス回路はディセーブルされる。

<sup>2.</sup>  $T_A 25^{\circ}C$ , f = 1.0MHz

## 供給電流(スタンバイ時)<sup>1234</sup>

| シンボル               | パラメータ                 | デバイス   | Typ. <sup>5</sup> | 単位 |

|--------------------|-----------------------|--------|-------------------|----|

|                    |                       | XP2-5  | 14                | mA |

|                    |                       | XP2-8  | 18                | mA |

| I <sub>cc</sub>    | コア電源電流                | XP2-17 | 24                | mA |

|                    |                       | XP2-30 | 35                | mA |

|                    |                       | XP2-40 | 45                | mA |

|                    |                       | XP2-5  | 15                | mA |

|                    |                       | XP2-8  | 15                | mA |

| I <sub>CCAUX</sub> | 補助(Auxiliary)電源電流     | XP2-17 | 15                | mA |

|                    |                       | XP2-30 | 16                | mA |

|                    |                       | XP2-40 | 16                | mA |

| I <sub>CCPLL</sub> | PLL電源電流 (PLLあたり)      |        | 0.1               | mA |

| I <sub>CCIO</sub>  | バンクあたり電源電流            |        | 2                 | mA |

| IccJ               | V <sub>CCJ</sub> 電源電流 |        | 0.25              | mA |

- 1. 供給電流についてのさらなる情報については、TN1139 (Power Estimation and Management for LatticeXP2 Devices)を参照のこと。

- 2. 全出力はトライステート、全入力はLVCMOSに構成されてVccioまたはGNDに固定されていると仮定。

- 3. 周波数 0MHz.

- 4. パターンはブランク。

- 5. Tj=25℃、電源電圧は標準値

- 6. fpBGA, ftBGAパッケージではPLLにはV<sub>CCAUX</sub> から電源を供給。従ってこれらパッケージではI<sub>CCAUX</sub>値はI<sub>CCAUX</sub>と I<sub>CCPLL</sub>との和。csBGA, PQFP, TQFPパッケージではPLLはV<sub>CCAUX</sub> から独立して電源を供給。

## 初期化供給電流 12345

| シンボル               | パラメータ                 | 条件     | Typ.<br>(25℃, Max. Supply) <sup>6</sup> | 単位 |

|--------------------|-----------------------|--------|-----------------------------------------|----|

|                    |                       | XP2-5  | 20                                      | mA |

|                    |                       | XP2-8  | 21                                      | mA |

| I <sub>CC</sub>    | コア電源電流                | XP2-17 | 44                                      | mA |

|                    |                       | XP2-30 | 58                                      | mA |

|                    |                       | XP2-40 | 62                                      | mA |

|                    | 補助(Auxiliary)電源電流     | XP2-5  | 67                                      | mA |

|                    |                       | XP2-8  | 74                                      | mA |

| I <sub>CCAUX</sub> |                       | XP2-17 | 112                                     | mA |

|                    |                       | XP2-30 | 124                                     | mA |

|                    |                       | XP2-40 | 130                                     | mA |

| I <sub>CCPLL</sub> | PLL電源電流(PLLあたり)       |        | 1.8                                     | mA |

| I <sub>CCIO</sub>  | バンクあたり電源電流            |        | 6.4                                     | mA |

| I <sub>CCJ</sub>   | V <sub>CCJ</sub> 電源電流 |        | 1.2                                     | mA |

- 1. 供給電流についてのさらなる情報については、TN1139 (Power Estimation and Management for LatticeXP2 Devices) を参照のこと。

- 2. 全出力はトライステート、全入力はLVCMOSに構成されてVccioまたはGNDに固定されていると仮定。

- 3. 周波数 0MHz。

- 4. 各供給電源のバイパス/デカップリング・コンデンサの充電電流は含まない。

- 5. デバイスサイズに基づいて特定のパターンを採用。PFUを75%、EBRを50%、I/Oを25%使用。

- 6. Tj=25℃、電源電圧は標準値。

- 7. fpBGA, ftBGAパッケージではPLLには $V_{CCAUX}$  から電源を供給。従ってこれらパッケージでは $I_{CCAUX}$ 値は $I_{CCAUX}$ と $I_{CCPLL}$  との和。csBGA, PQFP, TQFPパッケージではPLLは $V_{CCAUX}$  から独立して電源を供給。

## フラッシュメモリ、プログラミング / 消去時電流 12345

| シンボル               | パラメータ                              | 条件     | Typ.<br>(25℃, Max. Supply) <sup>6</sup> | 単位 |

|--------------------|------------------------------------|--------|-----------------------------------------|----|

|                    |                                    | XP2-5  | 17                                      | mA |

|                    |                                    | XP2-8  | 21                                      | mA |

| I <sub>CC</sub>    | コア電源電流                             | XP2-17 | 28                                      | mA |

|                    |                                    | XP2-30 | 36                                      | mA |

|                    |                                    | XP2-40 | 50                                      | mA |

|                    | 補助(Auxiliary)電源電流 <sup>7</sup>     | XP2-5  | 64                                      | mA |

|                    |                                    | XP2-8  | 66                                      | mA |

| I <sub>CCAUX</sub> |                                    | XP2-17 | 83                                      | mA |

|                    |                                    | XP2-30 | 87                                      | mA |

|                    |                                    | XP2-40 | 88                                      | mA |

| I <sub>CCPLL</sub> | PLL電源電流(PLLあたり)                    |        | 0.1                                     | mA |

| I <sub>CCIO</sub>  | バンクあたり電源電流                         |        | 5                                       | mA |

| I <sub>CCJ</sub>   | V <sub>CCJ</sub> 電源電流 <sup>8</sup> |        | 14                                      | mA |

- 1. 供給電流についてのさらなる情報については、TN1139 (Power Estimation and Management for LatticeXP2 Devices) を参照のこと。

- 2. 全出力はトライステート、全入力はLVCMOSに構成されてVccioまたはGNDに固定されていると仮定。

- 3. 周波数 0MHz (FPGA動作のためのダイナミック電流を除く)。

- 4. デバイスサイズに基づいて特定のパターンを採用。PFUを75%、EBRを50%、I/Oを25%使用。

- 5. 各供給電源のバイパス/デカップリング・コンデンサの充電電流は含まない。

- 6. Tj=25℃、電源電圧は標準値。

- 7. fpBGA, ftBGAパッケージではPLLには $V_{CCAUX}$  から電源を供給。従ってこれらパッケージでは $I_{CCAUX}$ 値は $I_{CCAUX}$ と $I_{CCPLL}$  との和。csBGA, PQFP, TQFPパッケージではPLLは $V_{CCAUX}$  から独立して電源を供給。

- 8. JTAGからのプログラミング時。

## sysIO推奨動作条件

| H= H+                                               |       | V <sub>CCIO</sub> |       |       | V <sub>REF</sub> (V) |       |

|-----------------------------------------------------|-------|-------------------|-------|-------|----------------------|-------|

| 規格                                                  | Min.  | Тур.              | Max.  | Min.  | Тур.                 | Max.  |

| LVCMOS33 <sup>2</sup>                               | 3.135 | 3.3               | 3.465 | _     | -                    | -     |

| LVCMOS25 <sup>2</sup>                               | 2.375 | 2.5               | 2.625 | -     | -                    | -     |

| LVCMOS18                                            | 1.71  | 1.8               | 1.89  | -     | -                    | -     |

| LVCMOS15                                            | 1.425 | 1.5               | 1.575 | _     | -                    | _     |

| LVCMOS12 <sup>2</sup>                               | 1.14  | 1.2               | 1.26  | -     | -                    | -     |

| LVTTL33 <sup>2</sup>                                | 3.135 | 3.3               | 3.465 | -     | -                    | -     |

| PCI33                                               | 3.135 | 3.3               | 3.465 | _     | -                    | -     |

| SSTL18_I <sup>2</sup> ,<br>SSTL18_II <sup>2</sup>   | 1.71  | 1.8               | 1.89  | 0.833 | 0.90                 | 0.969 |

| SSTL25_I <sup>2</sup> ,<br>SSTL25 II <sup>2</sup>   | 2.375 | 2.5               | 2.625 | 1.15  | 1.25                 | 1.35  |

| SSTL33_I <sup>2</sup> ,<br>SSTL33_II <sup>2</sup>   | 3.135 | 3.3               | 3.465 | 1.3   | 1.5                  | 1.7   |

| HSTL15_I                                            | 1.425 | 1.5               | 1.575 | 0.68  | 0.75                 | 0.9   |

| HSTL18_I <sup>2</sup> ,<br>HSTL18_II <sup>2</sup>   | 1.71  | 1.8               | 1.89  | 0.816 | 0.9                  | 1.08  |

| LVDS25 <sup>2</sup>                                 | 2.375 | 2.5               | 2.625 | _     | -                    | -     |

| MLVDS25 <sup>1</sup>                                | 2.375 | 2.5               | 2.625 | -     | -                    | -     |

| LVPECL33 1, 2                                       | 3.135 | 3.3               | 3.465 | -     | -                    | -     |

| BLVDS25 1, 2                                        | 2.375 | 2.5               | 2.625 | _     | -                    | _     |

| RSDS 1, 2                                           | 2.375 | 2.5               | 2.625 | -     | -                    | -     |

| SSTL18D_I <sup>2</sup> ,<br>SSTL18D_II <sup>2</sup> | 1.71  | 1.8               | 1.89  | -     | -                    | -     |

| SSTL25D_I <sup>2</sup> ,<br>SSTL25D II <sup>2</sup> | 2.375 | 2.5               | 2.625 | -     | -                    | -     |

| SSTL33D_I <sup>2</sup> ,<br>SSTL33D_II <sup>2</sup> | 3.135 | 3.3               | 3.465 | _     | _                    | _     |

| HSTL15D_I <sup>2</sup>                              | 1.425 | 1.5               | 1.575 | _     | _                    | -     |

| HSTL18D_I <sup>2</sup> ,<br>HSTL18D_II <sup>2</sup> | 1.71  | 1.8               | 1.89  | _     | _                    | _     |

<sup>1</sup> チップに対する入力。出力は外部抵抗を加えて実装する

<sup>2</sup> これら入力規格の場合Vccioの値に依存しない

## シングルエンドsysIO DC電気的特性

#### 推奨動作条件にわたって

| I/O規格       |          | V <sub>IL</sub>          | V <sub>IH</sub>          |          | V <sub>OL</sub> Max. |                          |                     | I <sub>OH</sub> <sup>1</sup> |

|-------------|----------|--------------------------|--------------------------|----------|----------------------|--------------------------|---------------------|------------------------------|

| I/OARIT     | Min. (V) | Max. (V)                 | Min. (V)                 | Max. (V) | (V)                  | (V)                      | (mA)                | (mA)                         |

| LVCMOS33    | -0.3     | 0.8                      | 2.0                      | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 20, 16, 12,<br>8, 4 | -20, -16, -12,<br>-8, -4     |

|             |          |                          |                          |          | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                 | -0.1                         |

| LVTTL33     | -0.3     | 0.8                      | 2.0                      | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 20, 16, 12,<br>8, 4 | -20, -16, -12,<br>-8, -4     |

|             |          |                          |                          |          | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                 | -0.1                         |

| LVCMOS25    | -0.3     | 0.7                      | 1.7                      | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 20, 16, 12,<br>8, 4 | -20, -16, -12,<br>-8, -4     |

|             |          |                          |                          |          | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                 | -0.1                         |

| LVCMOS18    | -0.3     | 0.35V <sub>CCIO</sub>    | 0.65V <sub>CCIO</sub>    | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 16, 12, 8, 4        | -16, -12, -8, -4             |

| LVCIVIOSTO  | -0.3     | 0.33 A CCIO              | 0.02 A CCIO              | 3.0      | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                 | -0.1                         |

| LVCMOS15    | 0.3      | 0.25\/                   | 0.65\/                   | 2.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 8, 4                | -8, -4                       |

| LVCIVIOS15  | -0.3     | 0.35V <sub>CCIO</sub>    | 0.65V <sub>CCIO</sub>    | 3.6      | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                 | -0.1                         |

| LVCMOS12    | 0.3      | 0.251/                   | 0.651/                   | 2.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 6, 2                | -6, -2                       |

| LVCIVIOS 12 | -0.3     | 0.35V <sub>CC</sub>      | 0.65V <sub>CC</sub>      | 3.6      | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                 | -0.1                         |

| PCI33       | -0.3     | 0.3V <sub>CCIO</sub>     | 0.5V <sub>CCIO</sub>     | 3.6      | 0.1V <sub>CCIO</sub> | 0.9V <sub>CCIO</sub>     | 1.5                 | -0.5                         |

| SSTL33_I    | -0.3     | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 3.6      | 0.7                  | V <sub>CCIO</sub> - 1.1  | 8                   | -8                           |

| SSTL33_II   | -0.3     | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 3.6      | 0.5                  | V <sub>CCIO</sub> - 0.9  | 16                  | -16                          |

| SSTL25_I    | -0.3     | V <sub>REF</sub> - 0.18  | V <sub>REF</sub> + 0.18  | 3.6      | 0.54                 | V <sub>CCIO</sub> - 0.62 | 7.6                 | -7.6                         |

| 331L25_I    | -0.3     | V <sub>REF</sub> - 0.10  | V <sub>REF</sub> + 0.10  | 3.0      | 0.54                 | V <sub>CCIO</sub> - 0.02 | 12                  | -12                          |

| CCTI OF II  | 0.0      | \/ 0.40                  | V . 0.40                 | 2.0      | 0.05                 | \/ 0.40                  | 15.2                | -15.2                        |

| SSTL25_II   | -0.3     | V <sub>REF</sub> - 0.18  | V <sub>REF</sub> + 0.18  | 3.6      | 0.35                 | V <sub>CCIO</sub> - 0.43 | 20                  | -20                          |

| SSTL18_I    | -0.3     | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 6.7                 | -6.7                         |

| CCTI 40 II  | 0.3      | \/ 0.105                 | V . 0.125                | 2.6      | 0.20                 | V 0.20                   | 8                   | -8                           |

| SSTL18_II   | -0.3     | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | 3.6      | 0.28                 | V <sub>CCIO</sub> – 0.28 | 11                  | -11                          |

| LICTI 15 I  | 0.2      | V 04                     | V 104                    | 2.6      | 0.4                  | \/ 0.4                   | 4                   | -4                           |

| HSTL15_I    | -0.3     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 8                   | -8                           |

| HCTI 40 L   | 0.0      | V 0.4                    | V . 0.4                  | 2.0      | 0.4                  | \/ O.4                   | 8                   | -8                           |

| HSTL18_I    | -0.3     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 12                  | -12                          |

| HSTL18_II   | -0.3     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 16                  | -16                          |

<sup>1.</sup> ロジック信号接続表で示されるように、I/OによってGND接続の間、あるいはのI/Oバンクの端の最後のGNDと I/Oバンク間を流れる平均DC電流は、n\*8mAを超えないものとします。ここでnはバンクGND接続か、バンクの最後のGNDとバンク端の間のI/O数です。

(The average DC current drawn by I/Os between GND connections, or between the last GND in an I/O bank and the end of an I/O bank, as shown in the logic signal connections table shall not exceed n \* 8mA. Where n is the number of I/Os between bank GND connections or between the last GND in a bank and the end of a bank.)

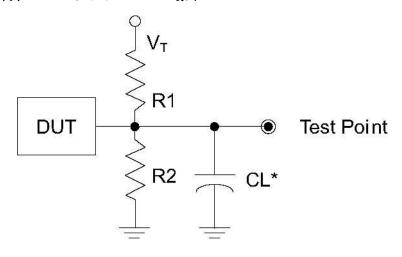

## 差動syslO電気的特性

#### **LVDS**

#### 推奨動作条件にわたって

| シンボル                                | パラメータ記述                                    | テスト条件                                      | Min.   | Тур. | Max.  | 単位 |

|-------------------------------------|--------------------------------------------|--------------------------------------------|--------|------|-------|----|

| V <sub>INP</sub> , V <sub>INM</sub> | 入力電圧                                       |                                            | 0      | _    | 2.4   | V  |

| $V_{CM}$                            | 入力コモンモード電圧                                 | 2入力の和の半分                                   | 0.05   | 1    | 2.35  | V  |

| $V_{THD}$                           | 差動の入力スレッショルド                               | 2入力の差                                      | +/-100 | _    | _     | mV |

| I <sub>IN</sub>                     | 入力電流                                       | パワーオン、またはオフ                                | _      | _    | +/-10 | uA |

| $V_{OH}$                            | V <sub>OP</sub> かV <sub>OM</sub> の出力High電圧 | $R_T = 100 \Omega$                         | 1      | 1.38 | 1.60  | V  |

| V <sub>OL</sub>                     | VopかVomの出力Low電圧                            | $R_T = 100 \Omega$                         | 0.9    | 1.03 | -     | V  |

| $V_{OD}$                            | 出力差動電圧                                     | $(V_{OP} - V_{OM}), R_T = 100 \Omega$      | 250    | 350  | 450   | mV |

| $\Delta V_{OD}$                     | HighとLow間のV <sub>OD</sub> の変化              |                                            | -      | -    | 50    | mV |

| Vos                                 | 出力電圧オフセット                                  | $(V_{OP} + V_{OM})/2$ , $R_T = 100 \Omega$ | 1.125  | 1.20 | 1.375 | V  |

| $\Delta V_{OS}$                     | HとLの間のVos VOSの変化                           |                                            | _      | _    | 50    | mV |

| I <sub>SA</sub>                     | 出力短絡電流                                     | $V_{OD} = 0V$ 、ドライバ出力を $GND$ にショート         | -      | -    | 24    | mA |

| I <sub>SAB</sub>                    | 出力短絡電流                                     | $V_{OD} = 0V$ 、ドライバ出力を相互にショート              | _      | -    | 12    | mA |

## 差動のHSTLとSSTL

差動のHSTLとSSTL出力は1組のコンプリメンタリなシングルエンド出力として実装されます。すべての許容できるシングルエンド出力クラス(クラスI)とクラスII)がこのモードでサポートされます。

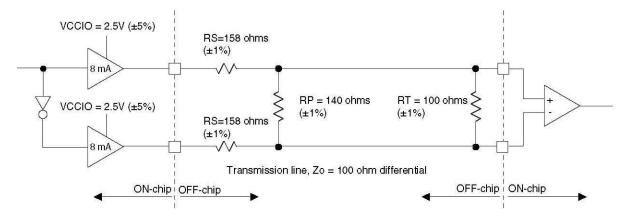

#### LVDS25E

LatticeXP2デバイスの上下辺I/Oバンクは、コンプリメンタリなLVCMOS出力を外部抵抗とともに用いることで、エミュレートLVDSをサポートします。図3-1で示すのはポイント・ツー・ポイント接続時の一つの構成例です。

#### 図3-1 LVDS25E出力終端の例

#### 表3-1 LVDS25EのDC条件

| パラメータ             | 記述              | 標準値   | 単位 |

|-------------------|-----------------|-------|----|

| V <sub>CCIO</sub> | 出力ドライバ電源(+/-5%) | 2.50  | V  |

| Z <sub>OUT</sub>  | ドライバインピーダンス     | 20    | Ω  |

| R <sub>S</sub>    | ドライバ直列抵抗(+/-1%) | 158   | Ω  |

| R <sub>P</sub>    | ドライバ並列抵抗(+/-1%) | 140   | Ω  |

| R <sub>T</sub>    | レシーバ終端抵抗(+/-1%) | 100   | Ω  |

| V <sub>OH</sub>   | 出力High電圧        | 1.43  | V  |

| V <sub>OL</sub>   | 出力Low電圧         | 1.07  | V  |

| V <sub>OD</sub>   | 出力差動電圧          | 0.35  | V  |

| V <sub>CM</sub>   | 出力コモンモード電圧      | 1.25  | V  |

| Z <sub>BACK</sub> | バック・インピーダンス     | 100.5 | Ω  |

| I <sub>DC</sub>   | DC出力電流          | 6.03  | mA |

#### LVCMOS33D

全I/OバンクでLVCMOS33D I/Oタイプを用いたエミュレート差動I/Oをサポートします。本オプションは、外部抵抗と共に用いることで $V_{CCIO}$ が3.3Vバンクに差動出力を配置する自由度をシステム設計者に提供します。デフォルトのドライブ電流は12mAで、オプションとして4mA,8mA,16mA,20mAに指定可能です。LVCMOS33DのDC特性はLVCMOS33に準じます。

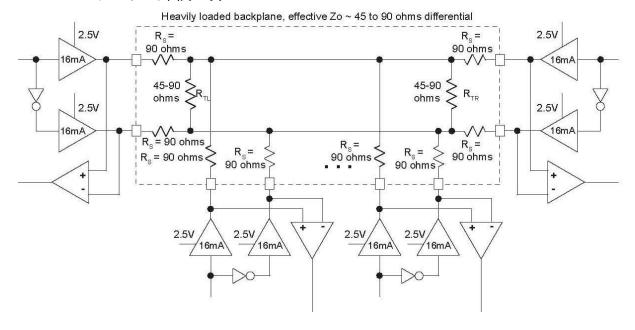

#### **BLVDS**

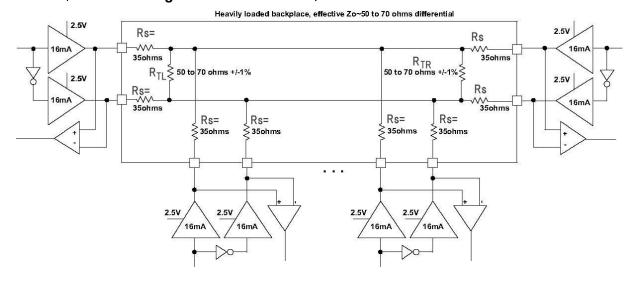

LatticeXP2デバイスは、BLVDS標準をサポートします。この標準は、ドライバ出力間のパラレル外部抵抗と共にコンプリメンタリなLVCMOS出力を用いることでエミュレートされます。BLVDSはマルチドロップで双方向のマルチポイント差動シグナリングが必要な時に用いられることを意図しています。図3-2で示されるスキームは、双方向のマルチポイント差動信号のための1つの可能なソリューションです。

#### 図3-2 BLVDSマルチポイント出力の例

#### 表3-2 BLVDS直流条件1

推奨動作条件にわたって

| パラメータ             | ±1.74             | Тур     | አለ የተ   |    |

|-------------------|-------------------|---------|---------|----|

| ハソメータ             | 記述<br>            | Zo = 45 | Zo = 90 | 単位 |

| V <sub>CCIO</sub> | 出力ドライバ電源(+/-5%)   | 2.50    | 2.50    | V  |

| Z <sub>OUT</sub>  | 出力インピーダンス         | 10.0    | 10.0    | Ω  |

| Rs                | ドライバ直列抵抗(+/-1%)   | 90.0    | 90.0    | Ω  |

| $R_{TL}$          | 左端の終端             | 45.0    | 90.0    | Ω  |

| R <sub>TR</sub>   | 右端の終端             | 45.0    | 90.0    | Ω  |

| V <sub>OH</sub>   | 出力 <b>High</b> 電圧 | 1.38    | 1.48    | V  |

| V <sub>OL</sub>   | 出力Low電圧           | 1.12    | 1.02    | V  |

| V <sub>OD</sub>   | 出力差動電圧            | 0.25    | 0.46    | V  |

| V <sub>CM</sub>   | 出力コモンモード電圧        | 1.25    | 1.25    | V  |

| I <sub>DC</sub>   | DC出力電流            | 11.24   | 10.20   | mA |

<sup>1.</sup> 入力バッファに関しては、LVDS表を参照してください

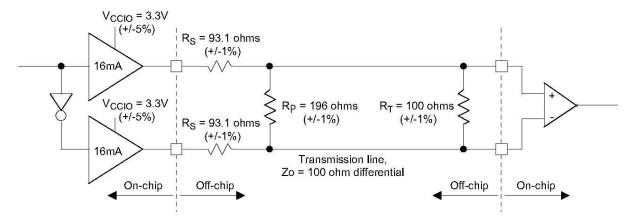

#### **LVPECL**

LatticeXP2デバイスは、差動LVPECL標準をサポートします。この標準は、ドライバ出力間のパラレル外部抵抗と共にコンプリメンタリなLVCMOS出力を用いることでエミュレートされます。LVPECL入力はLVDS 差動入力バッファでサポートされます。図3-3で示されるスキームは、ポイント・ツー・ポイント信号のための1つの可能なソリューションです。

#### 図3-3 差動LVPECL

表3-3 LVPECL直流条件<sup>1</sup>

推奨動作条件にわたって

| パラメータ             | 記述               | Typical | 単位 |

|-------------------|------------------|---------|----|

| V <sub>CCIO</sub> | 出力ドライバ電源(+/-5%)  | 3.30    | V  |

| Z <sub>OUT</sub>  | 出力インピーダンス        | 10      | Ω  |

| Rs                | ドライバ直列抵抗(+/-1%)  | 93      | Ω  |

| R <sub>P</sub>    | ドライバ並列抵抗(+/-1%)  | 196     | Ω  |

| R <sub>T</sub>    | レシーバ終端抵抗(+/-1%)  | 100     | Ω  |

| V <sub>OH</sub>   | 出力High電圧         | 2.05    | V  |

| V <sub>OL</sub>   | 出力 <b>Low</b> 電圧 | 1.25    | V  |

| V <sub>OD</sub>   | 出力差動電圧           | 0.80    | V  |

| V <sub>CM</sub>   | 出力コモンモード電圧       | 1.65    | V  |

| Z <sub>BACK</sub> | バック・インピーダンス      | 100.5   | Ω  |

| I <sub>DC</sub>   | DC出力電流           | 12.11   | mA |

<sup>1.</sup> 入力バッファに関しては、LVDS表を参照してください。

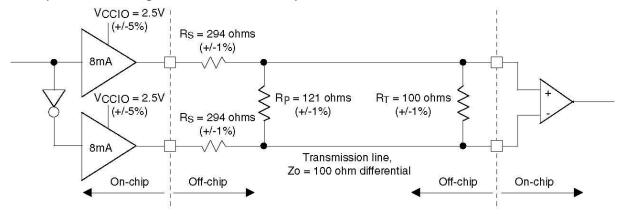

#### **RSDS**

LatticeXP2デバイスは、差動RSDS標準をサポートします。この標準は、ドライバ出力間のパラレル外部抵抗と共にコンプリメンタリなLVCMOS出力を用いることでエミュレートされます。RSDS入力はLVDS差動入力バッファでサポートされます。図3-4に示されたスキームはRSDS標準の実装のための1つの可能なソリューションです。図3-4における抵抗値は1%偏差の業界標準値です。

#### **⊠**3-4 RSDS (Reduced Swing Differential Standard)

#### 表3-4 RSDS DC条件1

| パラメータ             | 記述              | Typical | 単位  |

|-------------------|-----------------|---------|-----|

| V <sub>CCIO</sub> | 出力ドライバ電源(+/-5%) | 2.50    | V   |

| Z <sub>OUT</sub>  | 出力インピーダンス       | 20      | Ω   |

| Rs                | ドライバ直列抵抗(+/-1%) | 294     | Ω   |

| R <sub>P</sub>    | ドライバ並列抵抗(+/-1%) | 121     | ohm |

| $R_T$             | レシーバ終端抵抗(+/-1%) | 100     | ohm |

| $V_{OH}$          | 出力High電圧        | 1.35    | V   |

| V <sub>OL</sub>   | 出力Low電圧         | 1.15    | V   |

| $V_{OD}$          | 出力差動電圧          | 0.20    | V   |

| $V_{CM}$          | 出力コモンモード電圧      | 1.25    | V   |

| Z <sub>BACK</sub> | バック・インピーダンス     | 101.5   | ohm |

| I <sub>DC</sub>   | DC出力電流          | 3.66    | mA  |

<sup>1.</sup> 入力バッファに関しては、LVDS表を参照してください。

#### **MLVDS**

LatticeXP2デバイスは、差動MLVDS標準をサポートします。この標準は、ドライバ出力間のパラレル外部抵抗と共にコンプリメンタリなLVCMOS出力を用いることでエミュレートされます。MLVDS入力は差動LVDS入力バッファでサポートされます。図3-5で示されるスキームは、双方向のマルチポイント差動信号のための1つの可能なソリューションです。図3-5における抵抗値は1%偏差の業界標準値です。

#### **⊠**3-5 MLVDS (Reduced Swing Differential Standard)

#### 表3-5 MLVDS直流条件1

推奨動作条件にわたって

| パラメータ            | 記述                                                          | Тур     | 単位      |                |

|------------------|-------------------------------------------------------------|---------|---------|----------------|

| 1777-9           | 1000<br>1000<br>1000<br>1000<br>1000<br>1000<br>1000<br>100 | Zo = 45 | Zo = 70 | <del>中</del> 化 |

| $V_{CCIO}$       | 出力ドライバ電源(+/-5%)                                             | 2.50    | 2.50    | V              |

| Z <sub>OUT</sub> | 出力インピーダンス                                                   | 10.0    | 10.0    | Ω              |