# LatticeECP3 SERDES/PCS 使用ガイド

2012 年 8 月 テクニカルノート TN1176

## 概要

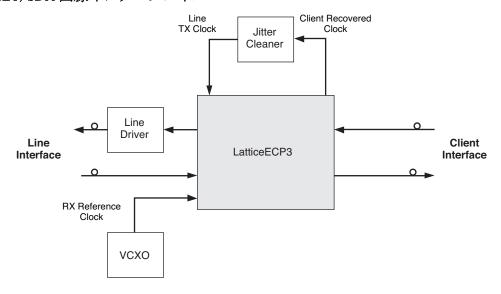

LatticeECP3 ™ FPGA ファミリは、高性能 FPGA ファブリック、高性能 I/O、及び最大 16 チャネルの組み込み SERDES 及び関連する PCS (Physical Coding Sublayer) ロジックを集積しています。多数の業界標準高速データ転送プロトコルに対応するよう、PCS ロジックを構成することができます。

PCS ロジックの各チャネルに専用の送受信 SERDES を含み、最大データレート 3.2Gbps の高速全二重シリアルデータ転送に対応します。PCS ロジックは、GbE、XAUI、SONET/SDH、PCI Express、SRIO、CPRI、OBSAI、SD-SDI、HD-SDI、3G-SDI を含む一連のデータプロトコルに対応するよう、各チャネルを構成することができます。さらに、ユーザの高速データインターフェイス設計に柔軟に対応できるように、多くの構成でプロトコルベースのロジックを完全か部分的にバイパスすることができます。

また PCS はバイパスモードを提供し、SERDES から FPGA ロジックへは 8 ビット、または 10 ビットの直接 インターフェイスがあります。それぞれの SERDES ピンは個別に DC カップリングに設定することでき、シ リアル・デジタルビデオ (SDI) 用途では高速動作と低速動作を、同じ SERDES ピンで対応することが可能です。

# 機能

- ・ 最大 16 チャネルの高速 SERDES

- 汎用(Generic)8b10b、10 ビット SERDES 及び 8 ビット SERDES モードで 150Mbps ~ 3.2Gbps。表 8-1 を参照

- 他のプロトコルでは 230Mbps ~ 3.2Gbps

- 3.2Gbps 動作時にチャネルあたり 110mW の低消費電力

- 小フォームファクタのバックプレーン動作のための受信イコライザと送信プリエンファシス

- PCI Express、ギガビット・イーサネット (1GbE と SGMII)、XAUI、及び他の複数の規格に対応

- ユーザ指定の汎用 (Generic) 8b10b モードに対応

- 低速入力用の OOB (Out-of-Band) 信号インターフェイス (ビデオ用途)

- 複数のクロックレートに対応

- 各 PCS クワッド用に個別の基準クロックが使用でき、単一デバイスで複数のプロトコルレートを容易に扱うことが可能

- · フル機能の組み込み物理コーディング・サブレイヤ(PCS)ロジックで業界標準プロトコルに対応

- デバイス当たり最大16チャネルの全二重データ通信に対応

- 単一チップで複数プロトコルに対応

- 8b10b ベースの広く採用されているパケットプロトコルに対応

- SERDES Only モードは FPGA ロジックと 8 ビット、または 10 ビットで直接インターフェイスが可能

- ・ 複数プロトコルに準拠するクロックトレランス補償 (CTC) ロジック

- 基準クロックと受信データレートの周波数偏差を補償

- 1/2/4 バイト長のユーザ定義スキップパターンの使用が可能

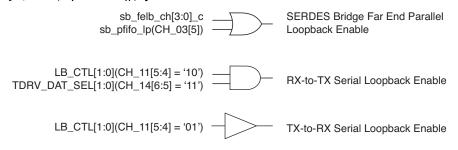

- ・システムデバッグのためのループバックモードを集積

- システムデバッグのために3つのループバックモードを提供

## LatticeECP2M™ SERDES/PCS の新機能

- ・単一の SERDES クワッドで複数のプロトコル規格に対応。表 8-1 に示す対応規格ではフルレートまたは ハーフレートで公称周波数となっている必要があります。構成の柔軟さは、様々なプロトコルや規格の 混在の障害になってはなりません。マルチプロトコル・グルーピングでは、PCI Express、ギガビット・イーサネット、SGMII、及び Serial RapidIO モードに対応します。

- ・XAUI 準拠機能に対応し、SERDES の最大性能を 3.2Gbps まで拡張

- ・SONET/SDH OC-3/STM-1、OC-12/STM-4、OC-48/STM-16 の各レートに対応

- ・SD-SDI、HD-SDI、及び 3G-SDI 用の送受信 DIV11 への対応を追加。マルチレート SDI 対応

# 本テクニカルノートの使い方

Lattice Diamond® 設計ツールは、PCS の全モードに対応しています。ほとんどのモードは、特定の業界の標準データプロトコル用の用途に専用のものとなっています。それ以外のモードは汎用性があり、設計者は独自のカスタム用途設定が可能です。Diamond 設計ツールでは、ユーザが自分のデザイン内でクワッドごとにモードを定義できます。このテクニカルノートでは、ツールが対応する全てのモードに対する、SERDES 及び PCS の動作について説明します。付録 D を参照してください。

本ドキュメントでは、組み込み SERDES 及び関連する PCS ロジックの全機能について詳しく説明します。組み込み SERDES の電気及びタイミング特性は、LatticeECP3 ファミリ・データシートに記載されています。 PCS ロジックの動作は、本ドキュメントの PCS の項で説明します。 SCI バスからアクセス可能な SERDES 及び PCS ロジックに関連する、全てのステータス及びコントロールレジスタの一覧表は付録に示してあります。パッケージのピン配列情報は、LatticeECP3 ファミリ・データシートのピン配列情報の項に記載されています。

# 対応規格

対応する規格を表 8-1 に示します。

表 8-1. SERDES が対応する規格

| 規格                                                                           | データレート<br>(Mbps)                                                | システム基準ク<br>ロック (MHz)                                           | FPGA クロック<br>(MHz)                   | 一般的なリンク幅   | エンコード方式        |

|------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------|------------|----------------|

| PCI Express 1.1                                                              | 2500                                                            | 100                                                            | 250                                  | x1, x2, x4 | 8b10b          |

| 12.18.8                                                                      | 1250                                                            | 125                                                            | 125                                  | x1         | 8b10b          |

| ギガビットイーサネッ<br> ト、SGMII                                                       | 2500                                                            | 125                                                            | 250                                  | x1         | 8b10b          |

| 1 CONIN                                                                      | 3125                                                            | 156.25                                                         | 156.25                               | x1         | 8b10b          |

| XAUI                                                                         | 3125                                                            | 156.25                                                         | 156.25                               | x4         | 8b10b          |

| Serial RapidIO Type I,<br>Serial RapidIO Type II,<br>Serial RapidIO Type III | 1250,<br>2500,<br>3125                                          | 125,<br>125,<br>156.25                                         | 125,<br>250,<br>156.25               | x1, x4     | 8b10b          |

| OBSAI-1,<br>OBSAI-2,<br>OBSAI-3,<br>OBSAI-4                                  | 768,<br>1536,<br>2304,<br>3072                                  | 76.8,<br>76.8, 153.6,<br>115.2,<br>153.6                       | 76.8,<br>153.6,<br>230.4,<br>153.6   | x1         | 8b10b          |

| CPRI-1,<br>CPRI-2,<br>CPRI-3,<br>CPRI-4                                      | 614.4,<br>1228.8,<br>2457.6,<br>3072.0                          | 61.44,<br>61.44, 122.88,<br>122.88,<br>153.6                   | 61.44,<br>122.88,<br>122.88<br>153.6 | x1         | 8b10b          |

| SD-SDI<br>(259M, 344M)                                                       | 143 <sup>1</sup> ,<br>177 <sup>1</sup> ,<br>270,<br>360,<br>540 | 14.3 <sup>1</sup> ,<br>17.7 <sup>1</sup> ,<br>27,<br>36,<br>54 | 143,<br>177,<br>27,<br>36,<br>54     | x1         | NRZI/Scrambled |

8-2 tn1176J\_02.4

| 表 8-1 5 | SERDES | が対応する規格 | (Continued) |

|---------|--------|---------|-------------|

|---------|--------|---------|-------------|

| 規格                                                                                 | データレート<br>(Mbps)         | システム基準ク<br>ロック (MHz)             | FPGA クロック<br>(MHz)              | 一般的なリンク幅       | エンコード方式        |

|------------------------------------------------------------------------------------|--------------------------|----------------------------------|---------------------------------|----------------|----------------|

| HD-SDI<br>(292M)                                                                   | 1483.5,<br>1485          | 74.175, 148.35,<br>74.25, 148.50 | 74.175, 148.35,<br>74.25, 148.5 | x1             | NRZI/Scrambled |

| 3G-SDI<br>(424M)                                                                   | 2967,<br>2970            | 148.35,<br>148.5                 | 148.35,<br>148.5                | x1             | NRZI/Scrambled |

| SONET STS-3 <sup>2</sup><br>SONET STS-12 <sup>2</sup><br>SONET STS-48 <sup>2</sup> | 155.52<br>622.08<br>2488 | 15.552<br>62.208<br>248.8        | 15.552<br>62.208<br>248.8       | x1             | N/A            |

| 10 ビット SERDES                                                                      | 150 - 3125               | 15 - 312.5                       | 15 - 312.5                      | x1, x2, x3, x4 | N/A            |

| 8ビット SERDES                                                                        | 150 - 3125               | 15 - 312.5                       | 15 - 312.5                      | x1, x2, x3, x4 | N/A            |

| 汎用 8b10b                                                                           | 150 - 3125               | 15 - 312.5                       | 15 - 312.5                      | x1, x2, x3, x4 | 8b10b          |

- 1. 低速時は SERDES がバイパスされ、信号が直接 FPGA コアに送られます。

- 2. SONET プロトコルには8ビット SERDES モードで対応しています。詳細については、本ドキュメントの SONET のセクションを参照してください。

# アーキテクチャ概要

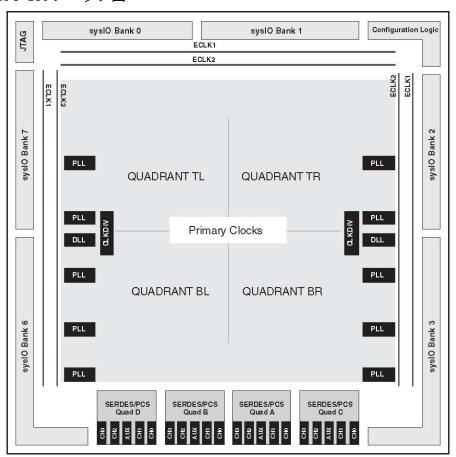

SERDES/PCS ブロックは独立する 4 系統の全二重データチャネル用のロジックを含み、クワッドごとにアレンジされています。図 8-1 は LatticeECP3-150 FPGA の SERDES/PCS クワッドの配置を示しています (他のデバイスではクワッド数は少なくなります)。

図 8-1. LatticeECP3-150 ブロック図

8-3 tn1176J 02.4

表 8-2 は LatticeECP3 ファミリの各デバイスにある SERDES/PCS クワッドの数を示しています。

#### 表 8-2. LatticeECP3 デバイスごとの SERDES/PCS クワッド数

| パッケージ          | ECP3-17 | ECP3-35 | ECP3-70 | ECP3-95 | ECP3-150 |

|----------------|---------|---------|---------|---------|----------|

| 256 ボール ftBGA  | 1       | 1       | _       | _       | _        |

| 328 ボール csBGA  | 2 ch *  | _       | _       | _       | _        |

| 484 ボール ftBGA  | 1       | 1       | 1       | 1       |          |

| 672 ボール ftBGA  | _       | 1       | 2       | 2       | 2        |

| 1156 ボール ftBGA | _       | _       | 3       | 3       | 4        |

<sup>1.</sup> チャネル0と3が使用できます

全てのクワッドは、複数のプロトコルベースのモードの1つにプログラムすることができます。各クワッドはそれ自身の基準クロックを必要とし、外部からパッケージピンを介して、あるいは内部 FPGA ロジックから供給することができます。

各クワッドは、公称周波数を持つ選択プロトコルによってプログラム可能で、チャネルごとにフルレート及びハーフレート・オプションを使用できます。例えば、2.5Gbps の PCI Express x1 とギガビット・イーサネット・チャネルを同一のクワッドで使用し、ギガビット・イーサネット・チャネルでハーフレート・オプションを使用できます。あるクワッドで PCI Express x1 チャネルと PCI Express 以外のチャネルを共有する場合は、そのクワッドの基準クロックがそのクワッド内の全てのプロトコルと互換性を持つ必要があります。例えば、PCI Express スペクトラム分散基準クロックは、多くのギガビット・イーサネット用途と互換性がありません。

各クワッドにはそれぞれの基準クロックがあるため、クワッドが異なれば同一チップでも違う規格に対応することができます。この機能により、LatticeECP3 ファミリは異なる規格間のブリッジ機能の実装に理想的なデバイスとなっています。

PCS クワッドは単に業界標準プロトコル専用なだけではありません。多くのユーザ定義のデータ操作モードのために、各クワッド(そしてクワッド内の各チャネル)をプログラムすることができます。例えば、ワードアライメントとクロックトレランス補償は、ユーザ定義の動作としてプログラムすることができます。

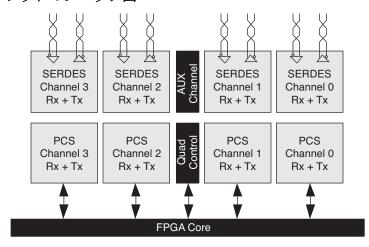

## PCS クワッドとチャネル

デバイスの各クワッドは最大 4 チャネルの全二重データをサポートします。アプリケーションによっては、単一クワッドで1~4 チャネルのいずれも利用することができます。どのクワッドであれ、ユーザがチャネルごとに独立して設定できる多くのオプションがあります。

図 8-1 には 4 つの PCS クワッド、合計 16 の PCS チャネルを含むデバイスの例を示します。

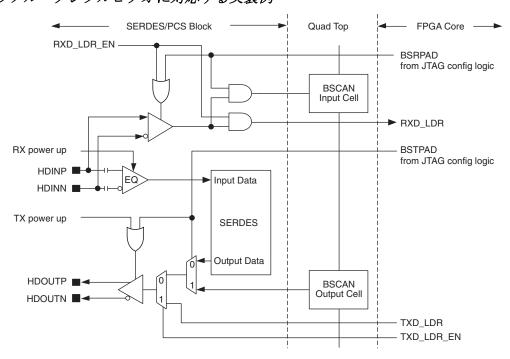

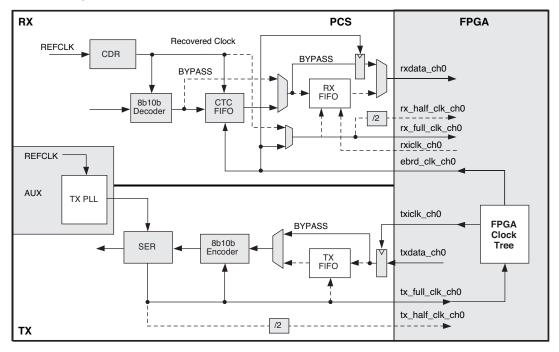

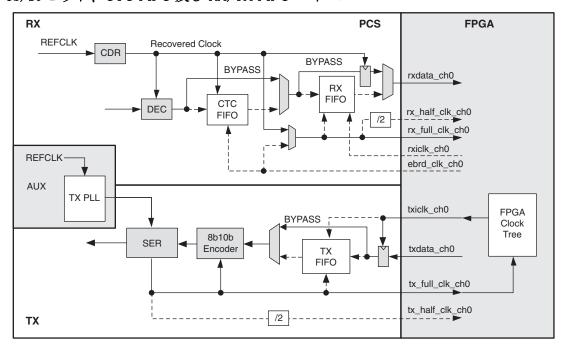

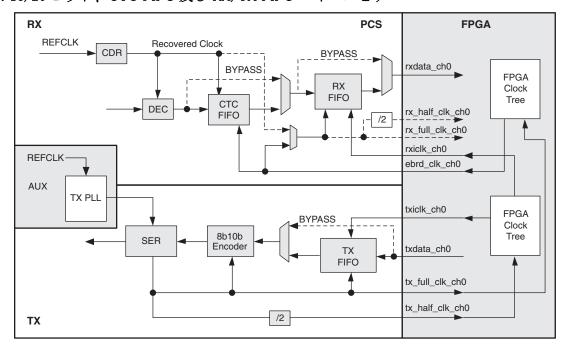

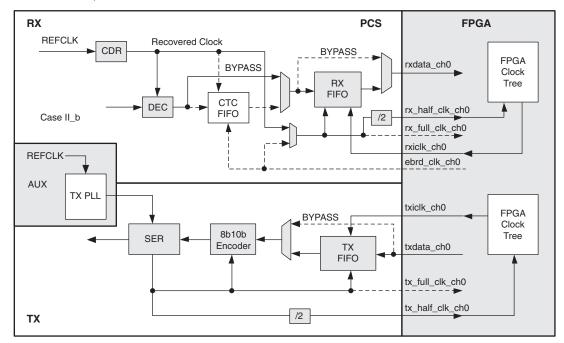

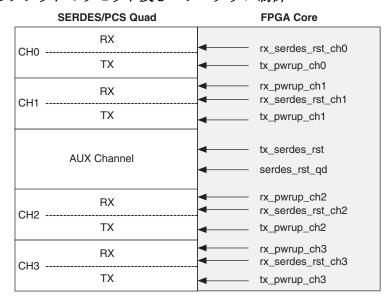

#### チャネル単位の PCS/FPGA インターフェイス・ポート

使用されるモードにかかわらず、全ての PCS クワッドはパッケージピンに共通の外部高速シリアル・インターフェースを持っています。しかしながら、各 PCS モードと FPGA ロジック間の I/O ポートには、それぞれのクワッドで選択されたプロトコルに適切となる独自のリストがあります。本ドキュメントでは各モード用のクワッド入出力信号の詳細を記述します。図 8-2 に SERDES/PCS クワッドの概略を示します。

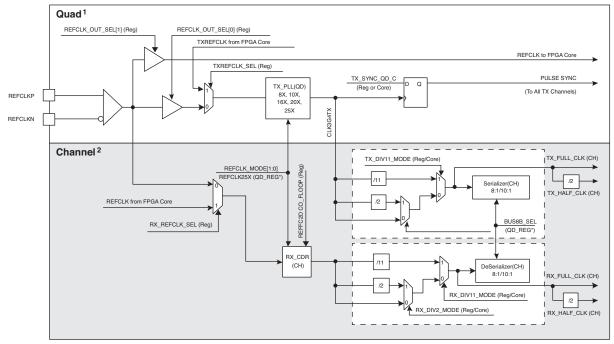

## 図 8-2. SERDES/PCS クワッドのブロック図

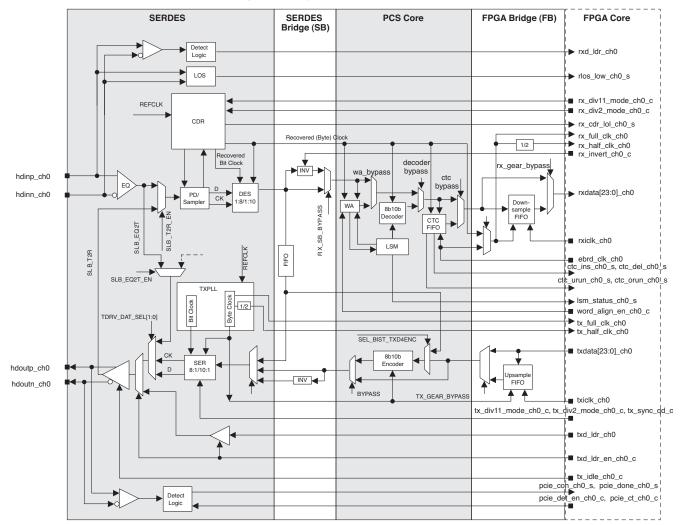

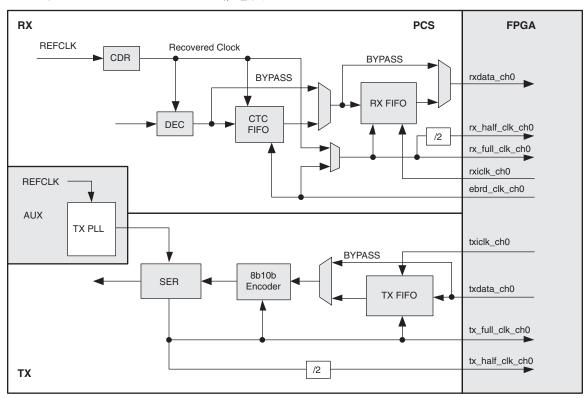

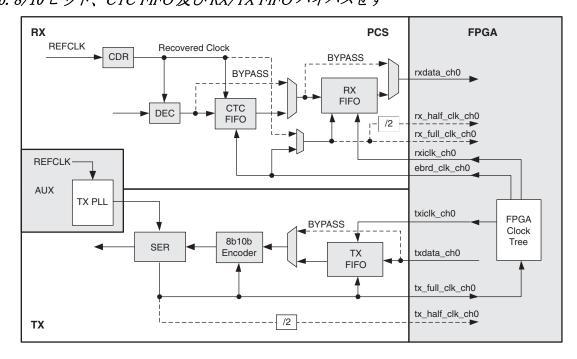

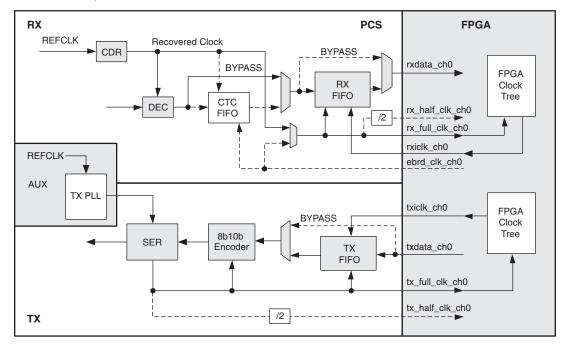

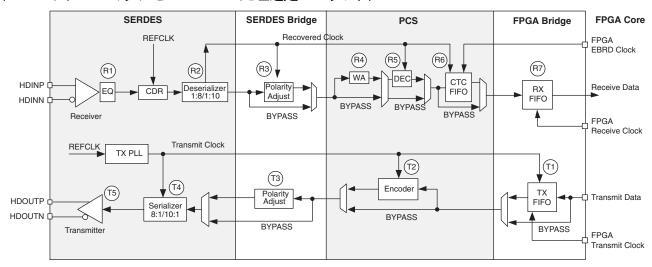

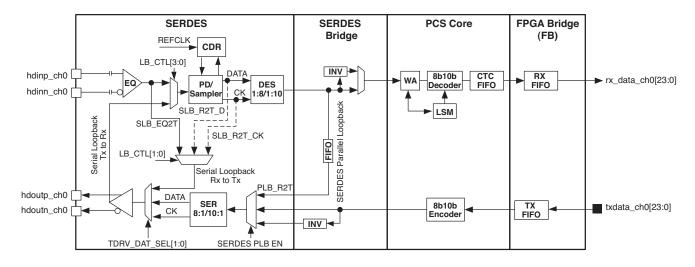

## チャネルの詳細ブロック図

図 8-3 は LatticeECP3 SERDES/PCS 単一チャネルの主要機能の詳細ブロック図を表しています。この図には FPGA でユーザロジックから見える全ての主要ブロック、及び制御とステータス信号の大部分が示されています。また、この図はチャネル SERDES 内の主要なサブブロックである SERDES ブリッジ、PCS コア、及び FPGA ブリッジも示しています。

8-5 tn1176J 02.4

## 図 8-3. LatticeECP3 SERDES/PCS チャネルの詳細ブロック図

## クロックとリセット

PCS クワッドは FPGA ロジック・インターフェイスに対して、(Tx PLL に) ロックした基準クロック及びチャネルごとの受信再生クロックを供給します。各 PCS クワッドはこれらのクロックをプライマリ、及びセカンダリの FPGA クロック配線に提供します。またクワッドの PCS/FPGA インターフェイスには、FPGA ファブリックから全 4 チャネルに供給する送受信クロックポートがあります。

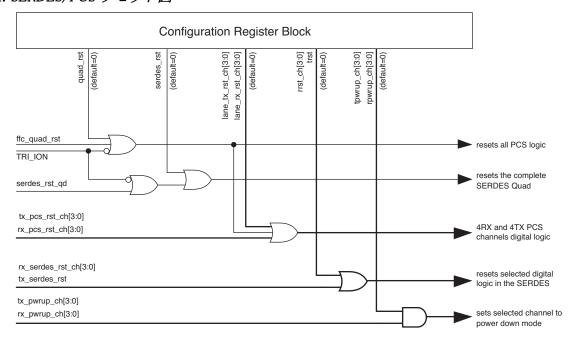

各クワッドには、クワッド内の SERDES と PCS ロジックの両方か、あるいは SERDES のみを強制リセットする信号入力があります。 さらに送受信方向共に、PCS ロジック専用のリセットがチャネルごとにあります。

## 送信データバス

送信データパスの信号は FPGA から PCS ブロック内の FPGA ブリッジまでです。高速伝送規格のために、(制御 / ステータス信号と共に)8 ビット幅の内部 PCS データパス用に 2:1 変換すること(ギアリング)ができます。 PCI Express x1 用インターフェイスの最高速度は 2:1 変換しないモードで 250MHz です。ギアリング 2:1 あり(すなわち、16 ビット幅データパス)で、最大速度は 156.25MHz(XAUI 4x チャネルモード用)です。 SERDES と PCS は、160MHz(2:1 ギアリングあり)のインターフェイス速度に対応する 3.2Gbps データレートまでサポートします。

8-6 tn1176J 02.4

# 受信データバス

受信パスの信号は、PCS ブロック内の FPGA ブリッジから FPGA までです。データパスは、8 ビット幅の内部 PCS データパス用に 2:1 ギアリングできます。FPGA インターフェイスのデータバス幅は 16 ビットです。ソフトウェア・レジスタビットで 2:1 ギアリングを禁止することが可能で、その場合バス幅は半分(8 ビット幅)にされます。データが 2:1 ギアリングされるとき、下位ビット(rxdata[9:0])は最初に受信されたワードに対応し、上位ビット(rxdata[19:10])は 2 番目に受信されたワードに対応します。データが 2:1 ギアリングなしの場合、下位ビット(rxdata[9:0])が有効なビットであり、上位ビットは使用されるべきではありません。表 8-3 に各プロトコルモードにおけるデータバスの用途を示します。

表 8-3. モード別のデータバスの用途

| データバスの<br>PCS セル名 <sup>4</sup> | G8B10B        | CPRI                  | OBSAI                 | PCI Express      | SRIO          | Gigabit Ethernet              | XAUI       | 8-Bit<br>SERDES | 10-Bit<br>SERDES | SDI  |

|--------------------------------|---------------|-----------------------|-----------------------|------------------|---------------|-------------------------------|------------|-----------------|------------------|------|

| FF_TX_D_0_0                    |               |                       |                       |                  | txdata_ch0    | [0]                           |            |                 |                  |      |

| FF_TX_D_0_1                    |               |                       |                       |                  | txdata_ch0    | [1]                           |            |                 |                  |      |

| FF_TX_D_0_2                    |               | txdata_ch0[2]         |                       |                  |               |                               |            |                 |                  |      |

| FF_TX_D_0_3                    |               |                       |                       |                  | txdata_ch0    | [3]                           |            |                 |                  |      |

| FF_TX_D_0_4                    |               |                       |                       |                  | txdata_ch0    | [4]                           |            |                 |                  |      |

| FF_TX_D_0_5                    |               |                       |                       |                  | txdata_ch0    | [5]                           |            |                 |                  |      |

| FF_TX_D_0_6                    |               |                       |                       |                  | txdata_ch0    | [6]                           |            |                 |                  |      |

| FF_TX_D_0_7                    |               |                       |                       |                  | txdata_ch0    | [7]                           |            |                 |                  |      |

| FF_TX_D_0_8                    |               |                       |                       | tx_k_ch0[0]      |               |                               | txc_ch0[0] | GND             | txdata_ch0       | [8]  |

| FF_TX_D_0_9                    | tx_fo         | orce_disp             | o_ch0[0] <sup>1</sup> |                  |               | GND                           |            |                 | txdata_ch0       | [9]  |

| FF_TX_D_0_10                   | tx_           | disp_sel_             | ch0[0] <sup>1</sup>   |                  | GND           | xmit_ch0[0] <sup>2</sup>      |            | GNE             | )                |      |

| FF_TX_D_0_11                   | GND           |                       |                       | pci_ei_en_ch0[0] | GND           | tx_disp_correct_ch0[0]        |            | GNE             | )                |      |

| FF_TX_D_0_12                   |               |                       |                       | t                | xdata_ch0[8]  |                               |            |                 | txdata_ch0[      | [10] |

| FF_TX_D_0_13                   |               |                       |                       | t                | xdata_ch0[9]  |                               |            |                 | txdata_ch0[      | [11] |

| FF_TX_D_0_14                   |               |                       |                       | t                | (data_ch0[10] |                               |            |                 | txdata_ch0[      | [12] |

| FF_TX_D_0_15                   |               |                       |                       | t                | data_ch0[11]  |                               |            |                 | txdata_ch0[      | [13] |

| FF_TX_D_0_16                   |               |                       |                       | t                | data_ch0[12]  |                               |            |                 | txdata_ch0[      | [14] |

| FF_TX_D_0_17                   |               |                       |                       | t                | data_ch0[13]  |                               |            |                 | txdata_ch0[      | [15] |

| FF_TX_D_0_18                   |               |                       |                       | t                | data_ch0[14]  |                               |            |                 | txdata_ch0[      | [16] |

| FF_TX_D_0_19                   |               |                       |                       | t                | data_ch0[15]  |                               |            |                 | txdata_ch0[      | [17] |

| FF_TX_D_0_20                   |               |                       |                       | tx_k_ch0[1]      |               |                               | txc_ch0[1] | GND             | txdata_ch0[      | [18] |

| FF_TX_D_0_21                   | tx_fo         | orce_dis <sub> </sub> | o_ch0[1] <sup>1</sup> |                  |               | GND                           |            |                 | txdata_ch0[      | [19] |

| FF_TX_D_0_22                   | tx_           | disp_sel_             | ch0[1] <sup>1</sup>   |                  | GND           | xmit_ch0[1] <sup>2</sup>      |            | GNE             | )                |      |

| FF_TX_D_0_23                   | GND           |                       |                       | pci_ei_en_ch0[1] | GND           | tx_disp_correct_ch0[1]        |            | GNE             | )                |      |

| FF_RX_D_0_0                    |               |                       |                       |                  | rxdata_ch0    | [0]                           |            |                 |                  |      |

| FF_RX_D_0_1                    |               |                       |                       |                  | rxdata_ch0    | [1]                           |            |                 |                  |      |

| FF_RX_D_0_2                    |               |                       |                       |                  | rxdata_ch0    | [2]                           |            |                 |                  |      |

| FF_RX_D_0_3                    |               |                       |                       |                  | rxdata_ch0    | [3]                           |            |                 |                  |      |

| FF_RX_D_0_4                    |               |                       |                       |                  | rxdata_ch0    | [4]                           |            |                 |                  |      |

| FF_RX_D_0_5                    |               |                       |                       |                  | rxdata_ch0    | [5]                           |            |                 |                  |      |

| FF_RX_D_0_6                    |               |                       |                       |                  | rxdata_ch0    | [6]                           |            |                 |                  |      |

| FF_RX_D_0_7                    |               |                       |                       |                  | rxdata_ch0    | [7]                           |            |                 |                  |      |

| FF_RX_D_0_8                    |               |                       |                       | rx_k_ch0[0]      |               |                               | rxc_ch0[0] | NC              | rxdata_ch0       | [8]  |

| FF_RX_D_0_9                    | rx_disp_err_c | h0[0]                 |                       | rxstatus0_ch0[0] |               | rx_disp_err_ch0[0]            |            | NC              | rxdata_ch0       | [9]  |

| FF_RX_D_0_10                   | rx_cv_err_ch  | 0[0] <sup>3</sup>     |                       | rxstatus0_ch0[1] |               | rx_cv_err_ch0[0] <sup>3</sup> |            |                 | NC               |      |

| FF_RX_D_0_11                   | NC            |                       |                       | rxstatus0_ch0[2] |               |                               | NC         |                 |                  |      |

| FF_RX_D_0_12                   |               |                       |                       | r                | xdata_ch0[8]  |                               |            |                 | rxdata_ch0[      | [10] |

| FF_RX_D_0_13                   |               |                       |                       | r                | xdata_ch0[9]  |                               |            |                 | rxdata_ch0[      | [11] |

| FF_RX_D_0_14                   |               |                       |                       | n                | (data_ch0[10] |                               |            |                 | rxdata_ch0[      | [12] |

| FF_RX_D_0_15                   |               |                       |                       | n                | data_ch0[11]  |                               |            |                 | rxdata_ch0[      | [13] |

| FF_RX_D_0_16                   |               |                       |                       | n                | data_ch0[12]  |                               |            |                 | rxdata_ch0[      | [14] |

8-7 tn1176J 02.4

#### 表 8-3. モード別のデータバスの用途 (Continued)

| データバスの<br>PCS セル名 <sup>4</sup> | G8B10B         | CPRI              | OBSAI | PCI Express      | SRIO                             | Gigabit Ethernet   | XAUI       | 8-Bit<br>SERDES | 10-Bit<br>SERDES | SDI |

|--------------------------------|----------------|-------------------|-------|------------------|----------------------------------|--------------------|------------|-----------------|------------------|-----|

| FF_RX_D_0_17                   |                | rxdata_ch0[13]    |       |                  |                                  |                    |            |                 |                  |     |

| FF_RX_D_0_18                   |                | rxdata_ch0[14]    |       |                  |                                  |                    |            |                 |                  | 6]  |

| FF_RX_D_0_19                   |                | rxdata_ch0[15]    |       |                  |                                  |                    |            |                 |                  | 7]  |

| FF_RX_D_0_20                   |                |                   |       | rx_k_ch0[1]      |                                  |                    | rxc_ch0[1] | NC              | rxdata_ch0[1     | 8]  |

| FF_RX_D_0_21                   | rx_disp_err_cl | h0[1]             |       | rxstatus1_ch0[0] |                                  | rx_disp_err_ch0[1] |            | NC              | rxdata_ch0[1     | 9]  |

| FF_RX_D_0_22                   | rx_cv_err_ch(  | D[1] <sup>3</sup> |       | rxstatus1_ch0[1] | rx_cv_err_ch0[1] <sup>3</sup> NC |                    |            |                 |                  |     |

| FF_RX_D_0_23                   | NC             |                   |       | rxstatus1_ch0[2] |                                  | N                  | IC         |                 |                  |     |

- 1. force\_disp 信号はデータワード [7:0] に対して  $tx_disp_sel$  信号で選択されたカラムのビットにディスパリティを強制します。 disp\_sel が 1 の場合、10 ビットコードは '現在の RD+'(正のディスパリティ)カラムから選択されます。  $tx_disp_sel$  が 0 の場合、10 ビットコードは '現在の RD-'(負のディスパリティ)カラムから選択されます

- 2. ラティスのギガビット・イーサネット PCS IP コアは、信号 xmit を生成する自動ネゴシエーション・ステートマシンを内蔵します。これはハードロジック内で、ギガビット・イーサネット・アイドルステートマシンと相互にインターフェイスする為に用いられます。

- 3. コード違反があるとき、PCS 8b10b パケットデコーダはその出力を 0xEE と K アサートに置き替えます(K=1 かつ d=EE は 8b10b 符号スペースに定義がありません)。

- 4. FF\_TX\_D\_0\_0: FPGA ファブリック送信データバスのチャネル 0 ビット 0。

#### モードごとの制御 / ステータス信号記述

表 8-4 にモードごとの制御 / ステータス信号を説明します。

#### 表 8-4. 制御信号とその機能

| 信号名                     | 記 述                                                                             |

|-------------------------|---------------------------------------------------------------------------------|

| 送信制御信号                  |                                                                                 |

| tx_k_ch[3:0]            | チャネル別。アクティブ High 制御キャラクタ・インジケータ                                                 |

| tx_force_disp_ch[3:0]   | チャネル別。disp_sel_ch(0-3) FPGA インターフェイス入力からのディスパリティ値を PCS が受け付けるようにするアクティブ High 信号 |

| tx_disp_sel_ch[3:0]     | チャネル別。FPGA ロジックから供給されるディスパリティ値。force_disp_ch(0-3) がハイのときに有効                     |

| tx_correct_disp_ch[3:0] | チャネル別。ネイティブ・ディスパリティ状態で開始するよう 8b10b エンコーダを調整することで、アサートされたときにディスパリティ識別子を修正        |

| 受信ステータス信号               |                                                                                 |

| rx_k_ch[3:0]            | チャネル別。アクティブ High 制御キャラクタ・インジケータ                                                 |

| rx_disp_err_ch[3:0]     | チャネル別。関連データでディスパリティ・エラーが検出されたことを示す、PCS がドライブするアクティブ High 信号                     |

| rx_cv_err_ch[3:0]       | チャネル別。関連データでエラーが検出されたことを示すコード違反信号                                               |

#### 制御

各モードにはそれ特有の制御信号の組があり、FPGA ロジックから様々な PCS 機能の直接制御を可能にします。通常これらの制御入力は、それぞれの制御レジスタビットへのライト操作と同等の作用を与えます。

{signal}\_c は、FPGA コアから FPGA ブリッジへの制御信号です。全ての制御信号は、SERDES/PCS 内部で同期化されてから使用されます。

## ステータス

各モードにはそれ特有のステータスやアラーム信号の組があり、FPGA ロジックからモニタできます。通常これらのステータス出力は、特定のステータス・レジスタビットにそれぞれ対応しています。Diamond デザインツールは、これらのポートを PCS FPGA インターフェイスに取り出すためのオプションをユーザに与えます。

8-8 tn1176J\_02.4

{signal}\_s は、FPGA ブリッジから FPGA コアへのステータス信号です。全てのステータス信号は、SERDES/PCS から同期出力されます。これらをクロックドメインと同期してから、FPGA デザインで使用する必要があります。

制御とステータスに関する詳細な情報については "モードごとの制御 / ステータス信号" セクションを参照してください。

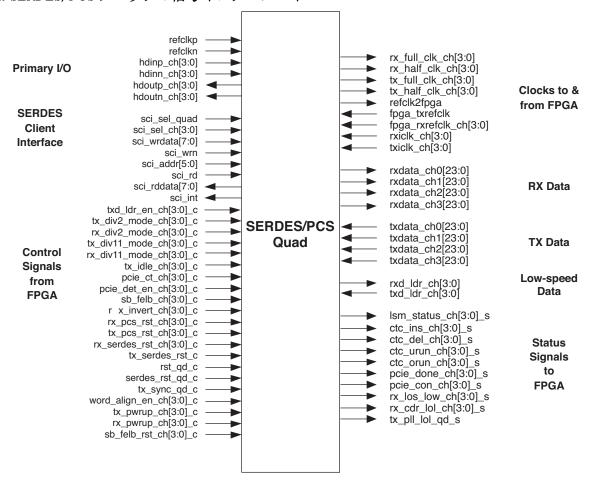

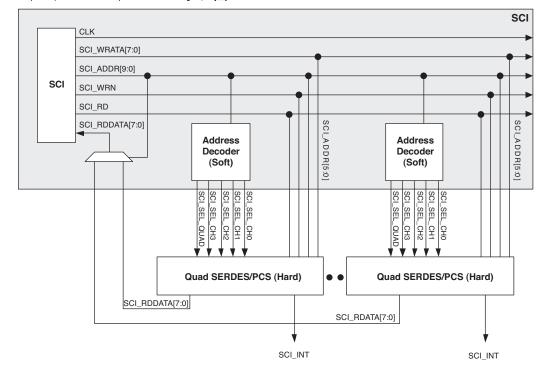

#### SERDES/PCS

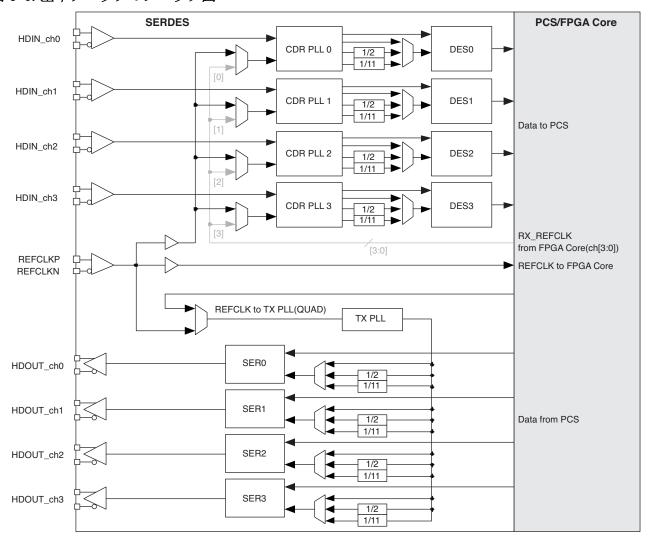

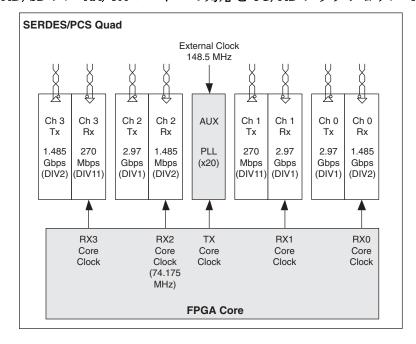

クワッドは4チャネルのRxとTx回路、及びTxPLLを含む補助チャネルを含んでいます。TxPLLへの基準クロックは、基準クロック差動入力ピンかFPGAコアから供給することができます。クワッドSERDES/PCSマクロは4レーンのデータのためにシリアル化及びパラレル化機能を実行し、マクロ内のTxPLLはFPGAロジックにシステムクロックを提供します。またクワッドはTxとRx各回路で、フルデータレートとハーフデータレート動作モードの両方を独立してサポートします。ブロックレベルの図を図8-4に示します。

#### 図 8-4. SERDES/PCS ブロックの信号インターフェイス

8-9 tn1176J 02.4

# I/O 記述

表 8-5 に PCS クワッドに対する全てのデフォルト及びオプションの I/O をリストアップします。IPexpress ™ GUI を用いることで PCS クワッドのオプションポートを選ぶことができます。

表 8-5. SERDES\_PCS I/O 記述

| 信号名                     | I/O     | タイプ    | 記 述                                                                                                          |

|-------------------------|---------|--------|--------------------------------------------------------------------------------------------------------------|

| プライマリ I/O, SERDES クワ    | フッド     |        |                                                                                                              |

| hdinp_ch0               | I       | チャネル   | 高速 CML 入力、非反転、チャネル 0                                                                                         |

| hdinn_ch0               | I       | チャネル   | 高速 CML 入力、反転、チャネル 0                                                                                          |

| hdinp_ch1               | I       | チャネル   | 高速 CML 入力、非反転、チャネル 1                                                                                         |

| hdinn_ch1               | I       | チャネル   | 高速 CML 入力、反転、チャネル 1                                                                                          |

| hdinp_ch2               | I       | チャネル   | 高速 CML 入力、非反転、チャネル 2                                                                                         |

| hdinn_ch2               | I       | チャネル   | 高速 CML 入力、反転、チャネル 2                                                                                          |

| hdinp_ch3               | I       | チャネル   | 高速 CML 入力、非反転、チャネル 3                                                                                         |

| hdinn_ch3               | I       | チャネル   | 高速 CML 入力、反転、チャネル 3                                                                                          |

| hdoutp_ch0              | 0       | チャネル   | 高速 CML 出力、非反転、チャネル 0                                                                                         |

| hdoutn_ch0              | 0       | チャネル   | 高速 CML 出力、反転、チャネル 0                                                                                          |

| hdoutp_ch1              | 0       | チャネル   | 高速 CML 出力、非反転、チャネル 1                                                                                         |

| hdoutn_ch1              | 0       | チャネル   | 高速 CML 出力、反転、チャネル 1                                                                                          |

| hdoutp_ch2              | 0       | チャネル   | 高速 CML 出力、非反転、チャネル 2                                                                                         |

| hdoutn_ch2              | 0       | チャネル   | 高速 CML 出力、反転、チャネル 2                                                                                          |

| hdoutp_ch3              | 0       | チャネル   | 高速 CML 出力、非反転、チャネル 3                                                                                         |

| hdoutn_ch3              | 0       | チャネル   | 高速 CML 出力、反転、チャネル 3                                                                                          |

| refclkp                 | I       | クワッド   | 基準クロック入力、非反転、専用 CML 入力                                                                                       |

| refclkn                 | I       | クワッド   | 基準クロック入力、反転、専用 CML 入力                                                                                        |

| 送受信データバス(詳細な/           | (ス使用法につ | ついては表8 | -3 及び 8-4 を参照)                                                                                               |

| rxdata_ch0[23:0]        | 0       | チャネル   | チャネル0受信データパスのデータ信号                                                                                           |

| rxdata_ch1[23:0]        | 0       | チャネル   | チャネル 1 受信データパスのデータ信号                                                                                         |

| rxdata_ch2[23:0]        | 0       | チャネル   | チャネル2受信データパスのデータ信号                                                                                           |

| rxdata_ch3[23:0]        | 0       | チャネル   | チャネル3受信データパスのデータ信号                                                                                           |

| txdata_ch0[23:0]        | I       | チャネル   | チャネル 0 送信データパスのデータ信号                                                                                         |

| txdata_ch1[23:0]        | I       | チャネル   | チャネル 1 送信データパスのデータ信号                                                                                         |

| txdata_ch2[23:0]        | I       | チャネル   | チャネル2送信データパスのデータ信号                                                                                           |

| txdata_ch3[23:0]        | I       | チャネル   | チャネル3送信データパスのデータ信号                                                                                           |

| 制御信号                    |         |        |                                                                                                              |

| tx_idle_ch[3:0] _c      | I       | チャネル   | SERDES トランスミッタによる電気的アイドルの送信制御<br>1 = SERDES トランスミッタが電気的アイドルを強制的に出力<br>0 = 通常動作                               |

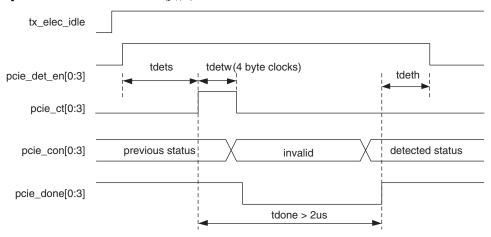

| pcie_det_en_ch[3:0]_c   | I       | チャネル   | FPGA ロジック(ユーザロジック)が SERDES ブロックに、PCI<br>Express レシーバ検出動作の要求があることを通知<br>1 = PCI Express レシーバ検出をイネーブル、0 = 通常動作 |

| pcie_ct_ch[3:0]_c       | I       | チャネル   | 1 = トランスミッタにファーエンド・レシーバ検出を要求<br>0 = 通常のデータ動作                                                                 |

| rx_invert_ch[3:0]_c     | I       | チャネル   | 受信データの反転制御<br>1 = データを反転、0 = データを反転しない                                                                       |

| word_align_en_ch[3:0]_c | I       | チャネル   | カンマアライナを制御<br>1 = カンマアライナをイネーブル<br>0 = カンマアライナを現在の位置にロック                                                     |

8-10 tn1176J\_02.4

表 8-5. SERDES\_PCS I/O 記述 (Continued)

| 信 <del>号</del> 名        | I/O | タイプ  | 記 述                                                                        |

|-------------------------|-----|------|----------------------------------------------------------------------------|

| sb_felb_ch[3:0]_c       | I   | チャネル | SERDES ブリッジ・パラレルループバック<br>1 = RX から TX へのループバックをイネーブル、0 = 通常のデータ動作         |

| sb_felb_rst_ch[3:0]_c   | I   | チャネル | SERDES ブリッジ・パラレルループバック FIFO のクリア<br>1 = ループバック FIFO をリセット、0 = 通常のループバック動作  |

| tx_sync_qd_c            | I   | クワッド | シリアライザのリセット<br>遷移 = リセット、レベル = 通常動作                                        |

| rx_div2_mode_ch[3:0]_c  | I   | チャネル | レシーバのレートモード選択(フル / ハーフレート)<br>1 = ハーフレート、0 = フルレート                         |

| tx_div2_mode_ch[3:0]_c  | I   | チャネル | トランスミッタのレートモード選択(フル / ハーフレート)<br>1 = ハーフレート、0 = フルレート                      |

| rx_div11_mode_ch[3:0]_c | I   | チャネル | レシーバのレートモード選択(DIV11/ フルレート)<br>1 = DIV11 レート、0 = フルレート                     |

| tx_div11_mode_ch[3:0]_c | I   | チャネル | トランスミッタのレートモード選択(DIV11/ フルレート)<br>1 = DIV11 レート、0 = フルレート                  |

| txd_ldr_en_ch{3:0]_c    | I   | チャネル | 低データレート TX シリアルパスのイネーブル<br>1 = イネーブル、0 = ディセーブル                            |

| リセット信号                  |     |      |                                                                            |

| rx_pcs_rst_ch[3:0]_c    | I   | チャネル | アクティブ High、非同期入力。PCS 内の個々の受信チャネルロジック<br>のみをリセット                            |

| tx_pcs_rst_ch[3:0]_c    | I   | チャネル | アクティブ High、非同期入力。PCS 内の個々の送信チャネルロジック<br>のみをリセット                            |

| rx_serdes_rst_ch[3:0]_c | I   | チャネル | アクティブ High、SERDES 受信チャネル内の一部ロジックのみをリセット                                    |

| tx_serdes_rst_c         | I   | クワッド | アクティブ High、SERDES 全送信チャネル内の一部ロジックのみをリセット                                   |

| rst_qd_c                | I   | クワッド | アクティブ High、非同期入力。補助チャネル及び PCS を含む SERDES<br>全チャネルをリセット                     |

| serdes_rst_qd_c         | I   | クワッド | アクティブ High、SERDES クワッドへの非同期入力。PCS ロジック以<br>外のクワッドチャネルを含む SERDES 全チャネルをリセット |

| tx_pwrup_ch[3:0]_c      | I   | チャネル | アクティブ High 送信チャネル・パワーアップ。0 = 送信チャネルパ<br>ワーダウン                              |

| rx_pwrup_ch[3:0]_c      | I   | チャネル | アクティブ High 受信チャネル・パワーアップ。0 = 受信チャネルパ<br>ワーダウン                              |

| ステータス信 <del>号</del>     |     |      |                                                                            |

| pcie_done_ch[0:3]_s     | 0   | チャネル | 1 = ファーエンド・レシーバ検出完了<br>0 = ファーエンド・レシーバ検出未完了                                |

| pcie_con_ch[3:0]_s      | 0   | チャネル | ファーエンド・レシーバ検出の結果<br>1 = ファーエンド・レシーバ検出<br>0 = ファーエンド・レシーバ不検出                |

| rx_los_low_ch[3:0]_s    | 0   | チャネル | 各チャネル用 LOS(LO THRESHOLD RANGE)検出                                           |

| Ism_status_ch[3:0]_s    | 0   | チャネル | 1 = レーンはカンマに同期<br>0 = レーンはカンマを不検出                                          |

| ctc_urrun_ch[3:0]_s     | 0   | チャネル | 1 = 受信クロック補償 FIFO のアンダーランエラー<br>0 = FIFO エラーなし                             |

| ctc_orun_ch[3:0]_s      | 0   | チャネル | 1 = 受信クロック補償 FIFO のオーバーランエラー<br>0 = FIFO エラーなし                             |

| rx_cdr_lol_ch[3:0]_s    | 0   | チャネル | 1 = 受信 CDR LOL<br>0 = ロックを維持                                               |

| tx_pll_lol_qd_s         | 0   | クワッド | 1 = 送信 PLL LOL<br>0 = ロックを維持                                               |

| ctc_ins_ch[3:0]_s       | 0   | チャネル | 1 = CTC がスキップキャラクタを挿入                                                      |

## 表 8-5. SERDES\_PCS I/O 記述 (Continued)

| 信号名                           | I/O        | タイプ    | 記述                                                                                                                                                                                           |

|-------------------------------|------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ctc_del_ch[3:0]_s             | 0          | チャネル   | 1 = CTC がスキップキャラクタを削除                                                                                                                                                                        |

| FPGA インターフェイス・                | クロック       | •      |                                                                                                                                                                                              |

| rx_full_clk_ch[3:0]           | 0          | チャネル   | 受信チャネル再生クロック。ユーザモードでは、ソースは常にチャネルの再生クロック。10 GbE などの CTC サポートの規格では、ソースは当該送信チャネルのシステムクロック。PCS バイパスモードでも送信システムクロックであり、8b10b モードで 8b10b デコーダをディセーブルして(10 ビットまたは 20 ビット・データパス)実行する "raw" モードの必要あり。 |

| rx_half_clk_ch[3:0]           | О          | チャネル   | 受信チャネル再生ハーフクロック。2:1 ギアリングモードでは 2 分周<br>された出力                                                                                                                                                 |

| tx_full_clk_ch[3:0]           | 0          | チャネル   | 送信 PLL フルレート・クロック。プライマリクロック配線を直接ドライブできるのは tx_full_clk_ch0 のみ。tx_full_clk_ch[3:0] の全信号で、セカンダリクロックのルーティングを直接ドライブ可能(適用する制約 USE SECONDARY が必要)注3                                                 |

| tx_half_clk_ch[3:0]           | 0          | チャネル   | 送信 PLL ハーフクロック。プライマリクロックのルーティングを直接ドライブできるのは tx_half_clk_ch0 のみ。tx_half_clk_ch[3:0] の全信号で、セカンダリクロックのルーティングを直接ドライブ可能(適用する制約 USE SECONDARY が必要)注3                                               |

| refclk2fpga                   | 0          | クワッド   | FPGA コアへの基準クロック。選択された場合、このクロックは基準クロックがある限り、クワッドがパワーダウン・モードになっていても常に有効                                                                                                                        |

| fpga_rxrefclk_ch[3:0]         | I          | クワッド   | FPGA ロジックからの Rx 基準クロック。CDR PLL 用                                                                                                                                                             |

| fpga_txrefclk                 | I          | クワッド   | FPGA ロジックからの Tx 基準クロック。TX SERDES PLL 用                                                                                                                                                       |

| ebrd_clk_ch[3:0] <sup>2</sup> | I          | チャネル   | FPGA からの受信チャネルクロック入力。CTC FIFO リード用                                                                                                                                                           |

| rxiclk_ch[3:0]                | I          | チャネル   | FPGA からの受信チャネルクロック入力。基準クロックや受信基準クロックに同期した FIFO と Rx FPGA 部のインターフェイス用クロック                                                                                                                     |

| txiclk_ch[3:0]                | I          | チャネル   | FPGA からの送信チャネルクロック入力。FPGA からのチャネルごとの送信クロック入力。基準クロックに同期した FIFO と Tx FPGA 部のインターフェイス用クロック。CTC が用いられる場合は、基準クロックに同期した FIFO と Rx FPGA 部のインターフェイス用クロックとしても用いられる                                    |

| 低速送受信データ及び SEF                | RDES クライア: | ント・インタ | マーフェイス(SCI)信号                                                                                                                                                                                |

| rxd_ldr_ch[3:0]               | 0          | チャネル   | FPGA コアへのシングルエンド・シリアル低速データ出力(RX)                                                                                                                                                             |

| txd_ldr_ch[3:0]               | I          | チャネル   | FPGA コアからのシングルエンド・シリアル低速データ入力(TX)                                                                                                                                                            |

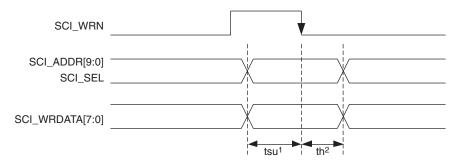

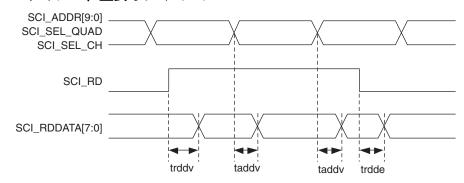

| sci_wrdata[7:0]               | I          | _      | ライトデータ入力                                                                                                                                                                                     |

| sci_wrn                       | I          | _      | ライト入力ストローブ                                                                                                                                                                                   |

| sci_sel_quad                  | I          |        | クワッドレジスタを選択                                                                                                                                                                                  |

| sci_sel_ch[3:0]               | I          | _      | チャネルレジスタを選択                                                                                                                                                                                  |

| sci_addr[5:0]                 | I          | _      | アドレスバス入力                                                                                                                                                                                     |

| sci_rd                        | I          | _      | リードデータ選択                                                                                                                                                                                     |

| sci_rddata[7:0]               | 0          | _      | リードデータ出力                                                                                                                                                                                     |

| sci_int                       | 0          | _      | 割り込み出力                                                                                                                                                                                       |

- 1. コンフィグレーションの間、hdoutp と hdoutn は共に VCCOB にプルアップされます。

- 2. このクロックは、ラッパーモジュールのポートリストで提供されません。CTC モードに応じて、ソフトウェアが自動的にクロックを割り当てます。詳細については、本ドキュメントの "FPGA インターフェイス・クロック" のセクションを参照してください。

- 3. セカンダリ・クロックネットワークを用いる場合には一般配線を経由します。PAR でウォーニングが生成されるかもしれませんが、殆どのアプリケーションで無視できる程度に遅延値は少ないでしょう。タイミング制約を与えて、タイミング違反がないことをレポートで確認して下さい。

8-12 tn1176J\_02.4

# SERDES/PCS の機能記述

LatticeECP3 デバイスには、組み込み SERDES/PCS ロジックのクワッドが  $1 \sim 4$  あります。各クワッドは、独立する全二重データチャネルを 4 系統サポートします。単一チャネルはデータリンクを 1 系統サポートすることができ、各クワッドはそのようなチャネル 4 つまでに対応できます。

組み込み SERDES CDR PLL と TX PLL は、広範囲の業界標準プロトコルをカバーするデータレートに対応しています。

以下のそれぞれについては図8-3を参照してください。

- · SERDES

- イコライザ

- CDR (クロックデータ再生)

- デシリアライザ

- プリエンファシス

- シリアライザ

- 2 つのシリアル・ループバックモード。TX から RX、または RX から TX

- · SERDES ブリッジ (SB)

- インバータ:受信データを反転。PCI Express で必要

- SERDES ブリッジ・パラレルループバック

- ・ PCS コア

- ワードアライメント (WA)

- 8b10b デコーダ

- 8b10b エンコーダ

- リンクステートマシン (LSM)

- クロックトレランス補償 (CTC)

- ・FPGA ブリッジ(FB)

- ダウンサンプル FIFO

- アップサンプル FIFO

#### **SERDES**

#### イコライザ

デジタル伝送のデータレートが Gbps 以上に進化するにつれて、周波数依存の減衰によって受信信号に著しいシンボル間干渉が発生します。したがってイコライザを用いることは、正しくデータを復元するために必須になります。Mid\_Low、Mid\_Med、Mid\_High、Long\_Low、Long\_Med、Long\_High という 6 つの極配置が用意されています。

#### プリエンファシス

プリエンファシスとは、一部周波数の振幅を他の周波数の振幅に対して増大させる信号処理のことです。目的は、減衰量の差などの現象による悪影響を最小限に抑え、全体としての S/N 比を改善することです。最大80% のプリエンファシスを選択できます。

#### 基準クロック

SERDES クワッドは 4 チャネルの Rx と Tx 回路、及び Tx PLL を含む補助チャネルを含んでいます。Tx PLL への基準クロックは、プライマリ差動基準クロックピン、隣接クワッドの基準クロック、または FPGA コアから供給することができます。また、SERDES ブロック内の PLL は出力クロックを提供し、FPGA ファブリックをドライブするシステムクロックとして使用できます。

Rx への基準クロックは、Tx PLL への基準クロックか FPGA コアから供給することができます。FPGA コアから Tx PLL へ、及び Rx への基準クロックは様々なソースから得ることができます。

8-13 tn1176J 02.4

#### SERDES クロック・アーキテクチャ

図 8-5 に SERDES のクロック・アーキテクチャ全体を示します。この図はクワッドとチャネルの2つの部分に分かれています。簡略化のため、チャネルごとに共通のセクションのみを一系統分示してあります。またブロック用に異なる様々な制御ビットも示してあります。これらはクワッドベースの制御レジスタビット、またはチャネルベースの制御レジスタビットになっています。場合によっては、チャネル制御ポートベースとなっていることもあり、中にはレジスタと制御ポートの両方の組み合わせになっているものがあります。両方のモードを使用すると、特定の機能プロパティの動的制御が可能になります。

#### 図 8-5. SERDES クロック・アーキテクチャ

- 1. All control bits are quad based.

- 2. All control bits are channel based, except as indicated (\*).

- 3. These clocks are user-transparent.

クロック・アーキテクチャの主要コンポーネントには、次のものがあります。

- ・RXごと及びTXごとの分周器(DIV)モード: DIV2、DIV11

- ・マルチクワッド REFCLK 接続

- ・FPGA からの tx\_sync\_qd\_c 信号を使用したマルチチャネル送信同期

- ·OOB 低速データ用途サポート

## レートモード

各チャネルの TX は、次のレートで動作するよう個別にプログラムできます。

- · FULL\_RATE

- · HALF RATE (DIV2)

- DIV11

Rx もチャネルごとに個別の基準クロックを使用できるため、トランスミッタとレシーバが完全に異なるレートで動作できます。

重要な点は、PLL VCO に変更はないことであり、従ってそのプロトコルに対する最速レートに対応できます。そのプロトコルに必要な分周後の全レートは、分周器の MUX 選択をプログラムすることで対応できま

8-14 tn1176J 02.4

す。その結果、PLLをプログラムし直す必要がないため、非常に高速なデータレート切り替えが可能になります。この機能は多くの用途で有用です。

注: LatticeECP3 PCS は動作中に refclk の周波数を変更するだけでは、SERDES が新しいレートで動作するようにはなりません。(日本語注:本注記は英語オリジナルの表記と異なりますが、いずれ更新予定です。)

通常 TX PLL と 4 つの CDR PLL は、基準クロック周波数の倍数となる同一周波数で動作します。表 8-6 に動作可能なクロックレートの各種モードを示します。ここに示したビットクロックは、基準クロック周波数の倍数になっています。

表 8-6. TXPLL 及び RX CDRPLL が対応可能なモード

| 基準クロックのモード | refclkPmode(クワッド) | Bus_width | ビットクロック(フル<br>レート) | ビットクロック (div2,<br>div11)    |

|------------|-------------------|-----------|--------------------|-----------------------------|

| 20x        | 0                 | 10        | Refclk x 20        | Refclk x 10                 |

| 16x        | 0                 | 8         | Refclk x 16        | Refclk x 8                  |

| 10x        | 1                 | 10        | Refclk x 10        | Refclk x 5                  |

| 8x         | 1                 | 8         | Refclk x 8         | Refclk x 4                  |

| 25x        | _                 | 8         | Refclk x 25        | Refclk x 12.5               |

| 25x        | _                 | 10        | Refclk x 25        | Refclk x 12.5               |

| 20x        | 0                 | 10        | Refclk x 20        | Refclk x 20/11 <sup>1</sup> |

<sup>1.</sup> DIV11 モード

## FPGA コアからの基準クロック

図 8-5 に示すとおり、TX 基準クロックは FPGA コアからも供給できます。この場合、クロックを SERDES まで配線する FPGA のリソースに起因する、過剰なジッタが送信データに加わり、場合によっては TX ジッタ 規格を満たさなくなる可能性があります。 FPGA で生成した SERDES TX 基準クロックを使用する場合は注意 が必要です。

8-15 tn1176J 02.4

## 図 8-6. 基準クロックのブロック図

# フルデータレート、DIV2、DIV11 データレート

各 TX シリアライザと RX デシリアライザは、プロトコルに応じてフルデータレートと DIV2 レートまたは DIV11 レートに分けられるため、方向ごと及びチャネルごとに異なるデータレートが可能です。詳細については図 8-6 を参照してください。

図 8-7 に示すとおり、4つ全てのチャネルで異なる構成が可能です。

## 図 8-7. IPexpress GUI でのフルデータレートとハーフデータレートの例

この例の実際のデータレート及び FPGA インターフェイスのクロックレートを、表 8-7 に示します。IPexpress GUI については、本ドキュメントで詳しく後述します。

#### 表 8-7. クロックレートの例

| チャネル      | データレート   | 基準クロッ<br>クの乗数 | データレー<br>ト・モード    | 基準クロッ<br>クレートの<br>計算値 | FPGA インター<br>フェイスのデー<br>タバス幅 |         | tx_full_clk | tx_half_clk |

|-----------|----------|---------------|-------------------|-----------------------|------------------------------|---------|-------------|-------------|

| Channel 0 | 1 Gbps   | 10 x          | FULL              | 100 MHz               | 8 (10) <sup>3</sup>          | 100 MHz | 100 MHz     | 50 MHz      |

| Channel 1 | 500 Mbps | 10 x          | DIV2              | 100 MHz               | 8 (10)                       | 50 MHz  | 50 MHz      | 25 MHz      |

| Channel 2 | 1 Gbps   | 10 x          | FULL              | 100 MHz               | 16 (20)                      | 50 MHz  | 100 MHz     | 50 MHz      |

| Channel 3 | 500 Mbps | 10 x          | DIV2 <sup>2</sup> | 100 MHz               | 16 (20)                      | 25 MHz  | 50 MHz      | 25 MHz      |

- 1. グレーで示したセルのクロックは、各モードで FPGA インターフェイス・クロックとして使用されます。

- 2. DIV2 モードでは、tx\_full\_clk がハーフレートに調整されます。tx\_half\_clk は 16 ビットバス・インターフェイスにのみ使用されます。

- 3.10 ビット SERDES 専用モードまたは SDI モード。

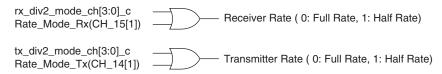

## フルレートとハーフレート (DIV2) の動的切り替え

このセクションでは、フルレートとハーフレート(DIV)を動的に切り替える方法について説明します。

2つのレートモード制御信号は、図 8-8 に示すように OR 接続されます。

#### 図8-8. レートモード制御信号

8-17 tn1176J\_02.4

tx\_div2\_mode\_chx\_c は FPGA ファブリックから TX パスへの入力制御信号です。

rx\_div2\_mode\_chx\_c は FPGA ファブリックから RX パスへの入力制御信号です。

Rate Mode Tx(CH 14[1]) は TX パス用の制御レジスタビットです。

Rate\_Mode\_Rx(CH\_15[1]) は RX パス用の制御レジスタビットです。

受信レーンには、切り替え後に pcs\_rst を与える必要があります。

送信レーンは、リセットなしで新しいレートが有効になります。

## 基準クロックのソース

#### refclkp, refclkn

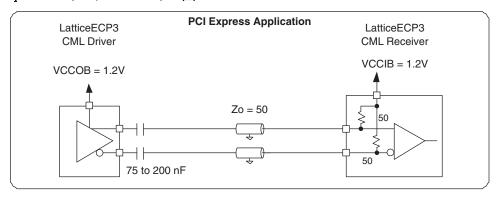

CML 入力専用。送受信用に別々のソースが使用されていない限り、第一の選択肢です。クロック信号は CML、LVDS、LVPECL のいずれかです。インターフェイス回路の例については、TN1114 "Electrical Recommendations for Lattice SERDES (ラティス SERDES の電気的推奨事項)"を参照してください。

#### fpga\_txrefclk, fpga\_rxrefclk

FPGA ロジックからの基準クロック。FPGA へのクロック入力ピンとしては、プライマリクロック・パッド (PCLK) を使用する必要があります。クロック信号は CML、LVDS、LVPECL、シングルエンドのいずれかです。

#### **FPGA PLL**

FPGA PLL が基準クロックとして用いられるとき、その PLL に対する基準クロックを専用 PLL 入力パッドに割り当てる必要があります。高速データレート時は、FPGA PLL 出力のジッタがシステム仕様を満たさないことがあります。ジッタが重要な用途では FPGA PLL を使用しないことを推奨します。

# スペクトル拡散クロック(SSC)の対応

リンク両端のポートは、常に 600ppm 以内のレートで相互にデータを送信する必要があります。これは  $\pm 300$ ppm のビットレートのクロックソースを許容するための仕様です。最小クロック周期に違反してはいけません。これに適した方法は、公称周波数を上回る変調が発生しないよう、拡散技術を調整することです。 データレートは、変調レートの範囲が 30  $\sim$  33KHz を超えない状態で、公称データレート +0%  $\sim$  -0.5% の範囲の変調が許容されます。  $\pm 300$ ppm というトレランスの上限があるため、SSC でデータを変調する場合は、両方のポートに同じビットレートのクロックが必要です。

PCI Express では、基準クロックを拡散するソースとなるのはルートコンプレックスです。エンドポイントは同じクロックを使用して、拡散スペクトルを返します。そのため、独立した RXREFCLK が不要です。主要な用途としてはアドインカードがあります。アドインカードはコネクタからの REFCLK を使用する必要がありませんが、PCI Express コネクタの REFCLK と同じ SSC で送受信する必要があります。

LatticeECP3 のアーキテクチャでは、同一クワッド内で PCI Express チャネルと、ギガビット・イーサネット、Serial RapidIO、または SGMII チャネルを混在できますが、送信基準クロックとして PCI Express の SSC を使用する場合は、ギガビット・イーサネット、Serial RapidIO、及び SGMII の送信ジッタ仕様に違反します。

## LOS(Loss of Signal、信号の喪失)

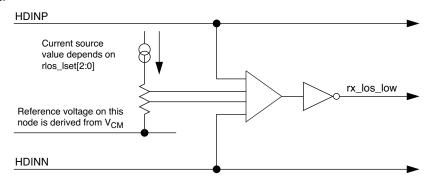

各チャネルは、図 8-9 に示すようにプログラマブルな LOS 検出器が含まれています。

LOS 閾値はプログラマブル電流源の値に依存し、電流源の値は rlos\_lset[2:0] 制御ビットを使用して選択されます。 閾値検出結果は、rx\_los\_low ステータス信号によって FPGA に通知されます。

8-18 tn1176J 02.4

#### 図 8-9. 検出器

Note: rx\_los\_low shows that a signal has been detected for data rates above 1 Gbps with a maximum CID (Consecutive Identical Digits) of 7 bits (i.e., a minimum input signal transition density as is sent by 8b10b).

rx\_los\_low is supported with a default setting of rlos\_lset[2:0] = 2, except in PCI Express mode and SDI mode. In PCI Express mode, 2 and 3 are supported.

In SDI mode, it is recommended to use the carrier detect output signal (/CD) from the external SDI cable equalizer.

#### 表 8-8. LOS 検出器の応答時間

| 記述                                   | Min. | Тур. | Max. | 単位 |

|--------------------------------------|------|------|------|----|

| 信号の喪失を検出するまでの時間(rx_los_low が 0 から 1) | _    | 8    | 10   | ns |

| 信号の存在を検出するまでの時間(rx_los_low が 1 から 0) | _    | 8    | 10   | ns |

## LOL (Loss of Lock、ロックはずれ)

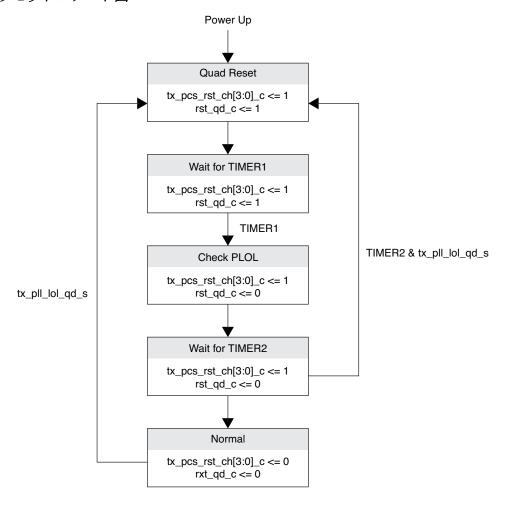

送信 PLL と個別チャネルの CDR には、どちらもカウンタベースのデジタル LOL 検出器があります。送信 PLL のロックがはずれると LOL がアサートされ、PLL が再ロックするまでそのままになります。CDR のロックがはずれると、そのチャネルの LOL がアサートされ、CDR の VCO を基準クロックにロックしようと試みます。これが達成されるとそのチャネルの LOL はネゲートされ、CDR は入力データにロックするために元に戻ります。CDR はデータにロックし続けるか、または再びロックはずれに戻り再トレーニングへと、その繰り返しとなります。CDR の LOL の詳細については、本ドキュメントの "SERDES/PCS のリセット" セクションを参照してください。

#### 表 8-9. LOL 検出器の応答時間

| 記述                                                 | Min. | Тур. | Max. | 単位 |

|----------------------------------------------------|------|------|------|----|

| ループのロックはずれを検出するまでの時間(x_pll_lol、rx_cdr_lo が 0 から 1) | _    | 200  | 500  | us |

| ループのロックを検出するまでの時間(x_pll_lol、rx_cdr_lo が 1 から 0)    | _    | 200  | 500  | us |

#### TX レーン間スキュー

制御信号 tx\_sync\_qd\_c は、アクティブな全 TX チャネルをリセットし、bit0 位置からシリアル化を開始します。 ほとんどのマルチチャネル・プロトコル規格では、ある規定値の中に TX レーン間スキューが収まることを保証する要件があります。

TX シリアライザへのリセットは、tx\_sync\_qd\_c 信号をトグルするか、PLL LOL の遷移によって生成されます。

8-19 tn1176J 02.4

## SERDES PCS 構成のセットアップ

LatticeECP3 PCS は様々な用途で使用するように構成(パラメータ / オプションの設定)ができます。セットアップは IPexpress モジュール生成ツールで選択され、PCS のモードと機能オプションを選択できます。選択オプションは自動構成(auto-configuration)ファイルの中に保存され、これはデザインツール内のビットストリーム・ジェネレータによって用いられて、選択内容がビットストリーム内に書き出されます。PCS 選択オプションを変えるためには、IPexpress を再実行して PCS モジュールを作り直し、新しい自動構成ファイルを作成することを推奨します。ビットストリーム・ジェネレータを実行する前に、自動構成ファイルを手動編集することによって、一部のオプションを変えることもできます。或いはデバイスのコンフィグレーション後に、オプションの SERDES クライアント・インターフェイス(SCI)バスを通して PCS レジスタにライトすることによって、動的に PCS オプションを変えることもできます。SCI では、コンフィグレーション・メモリセルではなく、レジスタによって SERDES/PCS クワッドを制御します。 SCI からアクセス可能な制御 / ステータスレジスタの一覧表を、本ドキュメントの付録 A に示してあります。

## 自動構成(Auto-Configuration)ファイル

IPexpress の自動構成機能を用いることで、それぞれの PCS モードのための初期レジスタ設定を行うことが可能です。モジュール・ジェネレータは、選ばれたモード用にクワッド / チャネルレジスタ設定の自動構成ファイル (〈module\_name〉.txt) を生成します。このファイルはフロントエンド・シミュレーションで参照することができ、またビットストリームに統合されます。自動構成ファイルがビットストリームに統合されると、全てのクワッド / チャネルレジスタが、コンフィグレーションの際に自動構成ファイルで定義された値に設定されます。ユーザがデバイス動作中に制御レジスタの値を変えるか、またはステータスレジスタをモニタする必要がある場合は、デザイン内に SCI インターフェイスを含める必要があります。

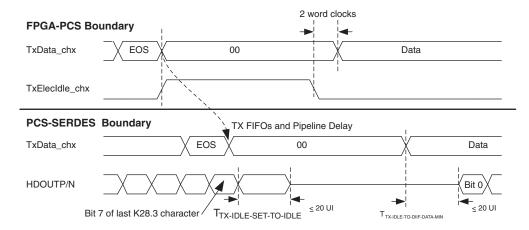

## 送信データ

PCS クワッド送信データパスは、チャネル単位の 8b10b エンコーダとシリアライザで構成されます。

#### 8b10b エンコーダ

本モジュールはIEEE 802.3ae-2002 1000BASE-X 仕様の中で記述されている 8b10bエンコーダを実装しています。エンコーダは仕様で説明されるように 8 ビットから 10 ビットコードへの変換を実行し、同時に規定されているディスパリティ規則を維持します。属性 (Attribute、アトリビュート) CHx\_8B10B (x はチャネル番号) を "BYPASS" に設定することによって、8b10b エンコーダをバイパスすることができます。

#### シリアライザ

8b10b 符号化されたデータはパラシリ変換され、組み込み SERDES を介してチップ外部に送信されます。

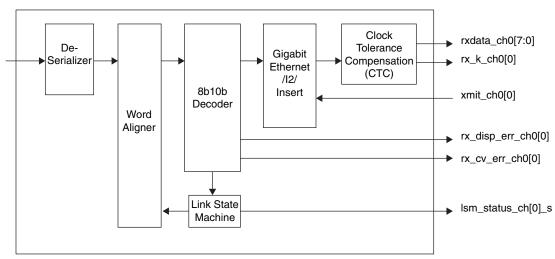

#### 受信データ

PCS クワッド受信データパスは、チャネルごとのデシリアライザ、ワードアライナ、8b10b デコーダ、オプションのリンクステートマシン、及びオプションの受信クロックトレランス補償(CTC) FIFO で構成されます。

## デシリアライザ

データはチップに取り込まれて組み込み SERDES に送られ、シリアルからパラレルに変換されます。

#### ワードアライメント (バイト境界の検出)

このモジュールはカンマ符号語の検出とアライメント動作を実行します。受信ロジックで入力されるデータストリームに 10 ビットのワードアライメントを実行するために、カンマキャラクタが用いられています。カンマ記述は 802.3.2002 1000BASE-X 仕様のセクション 36.2.4.9 と、セクション 48.2.6.3 (10GBASE-X 仕様のFigure 48-7) にあります。

ワードアライメント・モジュール内で多くのプログラマブル・オプションがサポートされます。

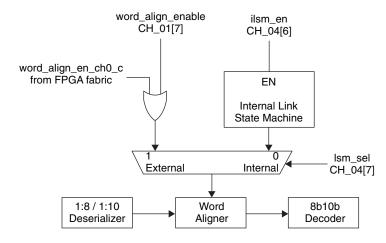

・組み込みリンクステートマシン (LSM) または FPGA 制御からのワードアライメント制御。8b10b パケットモードに加えて、8-bit SERDES Only、10-bit SERDES Only、SDI の各モードが対応しています。

- ・2 つのプログラマブル・ワードアライメント・キャラクタ (通常正と負のディスパリティのためにそれぞれ1つ)を設定できる機能と、アライメント・コンペア (比較) のためのビット単位でプログラマブルなマスクレジスタ。アライメント・キャラクタとマスクレジスタはクワッド毎に設定されます。多くのプロトコルにおいて、"XX00000011" (正のランニング・ディスパリティ・カンマキャラクタでコードグループ K28.1、K28.5、及び K28.7 に適合する jhgfiedcba ビット) と "XX01111100" (負のランニング・ディスパリティ・カンマキャラクタでコードグループ K28.1、K28.5、及び K28.7 に適合する jhgfiedcba ビット) にワードアライメント・キャラクタを設定することができます。ただし、任意の 10 ビットパターンを定義できます。

- ・最初のアライメント・キャラクタは COMMA\_A 属性に割り当てられた 10 ビットの値によって定義されます。この値は PCS クワッドの全チャネルに適用されます。

- ・第2のアライメント・キャラクタは COMMA\_B 属性に割り当てられた 10 ビットの値によって定義されます。この値は PCS クワッドの全チャネルに適用されます。

- ・マスクレジスタは、どのワードアライメント・ビットを比較したらよいかを定義します(マスクレジスタで'1'のビットは、ワードアライメント・キャラクタレジスタで対応するビットをチェックすることを意味します)。COMMA\_M 属性に割り当てられた10ビットの値によって定義されたマスクレジスタ。この値はPCS クワッドの全チャンルに適用されます。ワードアライメント属性CHx\_RXWAが "ENABLED"、CHx\_ILSM(内部リンクステートマシン)が "ENABLED" にそれぞれ設定されると、プロトコルベースのリンクステートマシンの1つがワードアライメントを制御します。プロトコルベースのリンクステートマシン動作の詳細については、後述するプロトコルごとのリンクステートマシンのセクションを参照してください。

## 8b10b デコーダ

8b10b デコーダは、IEEE 802.3-2002 規格に記述された 8b10b デコーダ動作を実装しています。このデコーダはランニング・ディスパリティの検証と共に、10 ビットから 8 ビットコードへの変換を実行します。コード違反が検出されると、受信データ rxdata は 0xEE に、rx\_k\_chn は '1' に設定されます。

## 外部リンクステートマシンのオプション

内部リンクステートマシン属性 CHx\_ILSM が "DISABLED"、CHx\_RXWA (ワードアライメント) が "ENABLED" にそれぞれ設定されているときに、ワードアライナをイネーブルするためには制御信号 word\_align\_en\_ch(0-3)\_c が用いられます。これは FPGA ファブリックに実装される外部リンクステートマシンから生成されなければなりません。この信号が High になると、ワードアライナはアライメントをロックし、ロックしたままになります。受信データとユーザ定義のワードアライメント・キャラクタとの比較をやめ、COMMA\_A またはCOMMA\_B との最初の比較一致で現在のアライメントを維持します。再アライメントが必要な場合は、word\_align\_en\_ch(0-3)\_c を Low から High のパルスを与えます。ワードアライナは、いずれかのユーザ定義ワードアライメント・キャラクタとの次回の一致で再ロックします。必要であれば、PCS クワッドの外部に実装したリンクステートマシンによって word\_align\_en\_ch(0-3)\_c を制御でき、特定の条件下でのみワードアライメントを変更することができます。

図 8-10 にリンクステートマシンのオプションを示します。

8-21 tn1176J\_02.4

#### 図 8-10. PCS ワードアライナとリンクステートマシンのオプション

リンクステートマシンが選択され、特定のチャネル用にイネーブルにした場合、リンクが同期するとそのチャネルの lsm\_status\_ch(0-3)\_s ステータス信号が High になります。

## ギガビット・イーサネットモードのアイドル挿入

Generic 8b10b モードには、さらにワードアライメントのために LSM を選択するオプションがあります。ギガビット・イーサネットモードに設定された PCS は、自動ネゴシエーションのために、受信データストリームの中に /I2/ シンボル挿入を行います。ギガビット・イーサネットの自動ネゴシエーションはソフトロジックで実行されます。この機能は 2048 クロックサイクル毎に 8 つの /I2/ オーダセット・シーケンスを挿入します。/I2/ 挿入は自動ネゴシエーション・ソフトロジックからドライブされる PCS への xmit\_ch(0-3) 入力で制御されます。図 8-11 は PCS がギガビット・イーサネットモードに設定されたときの、1 チャネルの受信ロジックを示し(この例ではチャネル 0)、これらの制御 / ステータス信号を示しています。

# 図 8-11. ギガビット・イーサネットモードの PCS 受信パス (チャネル 0 の例)

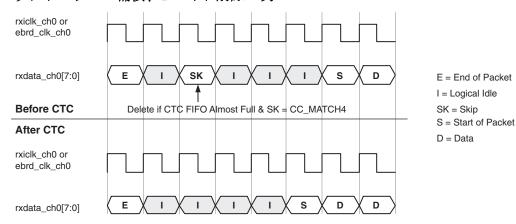

## クロックトレランス補償(CTC)

CTC (Clock Tolerance Compensation) モジュールは、受信再生クロックとロックする基準クロックの間のクロックレートの調整を実行します。クロック補償は、パケットデータの損失を引き起こすことなく、事前に定められた位置でバイトを挿入するか、または削除することによって実行されます。16 バイトの CTC FIFOは、2 つのクロックドメイン間のデータ転送に用いられ、Lattice ECP3 SERDES のためにクロック偏差の規定

8-22 tn1176J 02.4

ppm 上限まで対応します (LatticeECP3 ファミリ・データシートの "DC and Switching Characteristics" セクションを参照してください)。

CHx\_CTC 属性が "ENABLED" に設定されると、そのチャネルのCTCブロックはイネーブルされ、"DISABLED" に設定されるとバイパスされます。

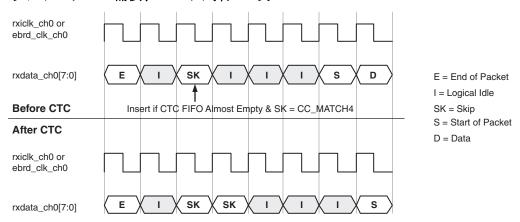

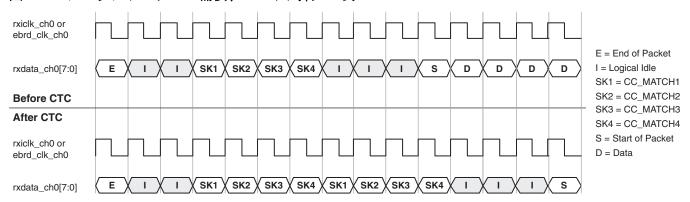

1バイト削除について図8-12に示します。

## 図 8-12. クロックトレランス補償、1 バイト削除の例

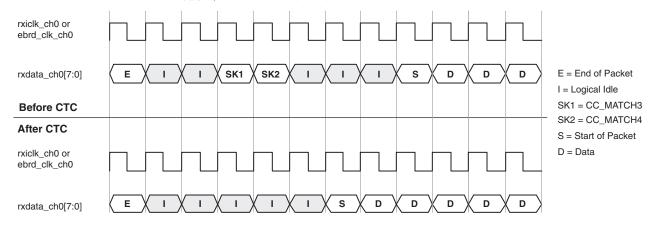

1 バイト挿入について図 8-13 に示します。

## 図 8-13. クロックトレランス補償、1 バイト挿入の例

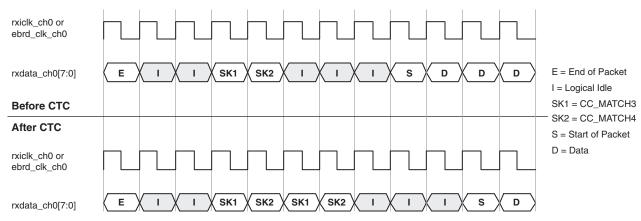

2 バイト削除について図 8-14 に示します。

8-23 tn1176J 02.4

## 図 8-14. クロックトレランス補償、2 バイト削除の例

2 バイト挿入について図 8-15 に示します。

# 図 8-15. クロックトレランス補償、2バイト挿入の例

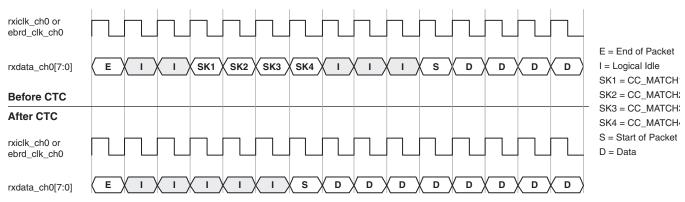

4 バイト削除について図 8-16 に示します。

## 図 8-16. クロックトレランス補償、4 バイト削除の例

4 バイト挿入について図 8-17 に示します。

8-24 tn1176J 02.4

## 図 8-17. クロックトレランス補償、4 バイト挿入の例

CTC が使用されるとき、意図されたアプリケーションのクロック補償のために、以下の設定を適用しなければなりません。

- ・CC\_MATCH\_MODE 属性を用いて、挿入/削除パターン長を設定します。これは挿入や削除を実行する前に CTC が比較しスキップするバイト数を設定します。CC\_MATCH\_MODE の値は、"1"(1 バイトの挿入/削除)、"2"(2 バイトの挿入/削除)、及び"4"(4 バイトの挿入/削除)です。また、ターゲット・アプリケーションに適した最小パケット間ギャップを設定する必要があります。パケット間ギャップは CC\_MIN\_IPG 属性に値を割り当てることによって設定されます。CC\_MIN\_IPG の許容値は"0"、"1"、"2"、及び"3"です。これらの属性設定に基づいてスキップキャラクタ削除が実行された後の、許容される最小パケット間ギャップを表 8-10 に示します。

- ・**選ばれた CC\_MATCH\_MODE に対応するように、スキップバイトかオーダセットが設定される必要があります。** 4 バイトの挿入 / 削除(CC\_MATCH\_MODE = "4")に関しては、CC\_MATCH1 属性に最初のバイトを割り当て、 CC\_MATCH2 属性に第 2 バイト、CC\_MATCH3 属性に第 3 バイト、そして CC\_MATCH4 属性に第 4 バイトをそれぞれ割り当てる必要があります。割り当てられる値は 2 進の 10 ビット値です。

#### 例:

4 バイトのスキップ・オーダセットが /K28.5/D21.4/D21.5/D21.5 の場合、"CC\_MATCH1" は "0110111100"、 "CC\_MATCH2" = "0010010101"、"CC\_MATCH3" = "0010110101"、そして "CC\_MATCH4" = "0010110101" となる必要があります。

2 バイトの挿入 / 削除 (CC\_MATCH\_MODE = "2") に関しては、CC\_MATCH3 に最初のバイトを割り当て、CC\_MATCH4 に第 2 バイトを割り当てる必要があります。

1 バイトの挿入 / 削除(CC\_MATCH\_MODE = "1")に関しては、CC\_MATCH4 にスキップバイトを割り当てる必要があります。

- ・クロック補償 FIFO において、ターゲット・プロトコル用の High/Low ウォーターマークを設定する必要があります。値の範囲は  $0 \sim 15$  で、High ウォーターマークは Low ウォーターマークよりも高い値に設定する必要があります(等しい値に設定してはいけません)。CCHMARK 属性に値を割り当てることによって、High ウォーターマークが設定されます。CCHMARK の許容値は 16 進値の 0 から 1 がら 1 です。CCLMARK 属性に値を割り当てることによって、1 から 1 から 1 です。

- ・モジュール・ジェネレータで PCS ブロックを生成するとき、"Error Status Ports" が選択されている場合、チャネルごとのクロック補償 FIFO オーバーランは、PCS/FPGA インターフェイスで cc\_overrun\_ch(0-3) という名称のポートでモニタすることができます。

- ・モジュール・ジェネレータで PCS ブロックを生成するとき、"Error Status Ports" が選択されている場合、チャネルごとのクロック補償 FIFO アンダーランは、PCS/FPGA インターフェイスで cc\_underrun\_ch(0-3) という名称のポートでモニタすることができます。

## 最小パケット間ギャップの計算

表 8-10 は CC\_MIN\_IPG 属性で定義されるパケット間ギャップのユーザ定義の値と、PCS からのスキップキャラクタ削除後の保証されるパケット間最小バイト数との関係を示しています。この表は、乗数としてのパケット間ギャップを示しています。パケット間の最小バイト数と、挿入/削除のバイト数を表に示す乗数倍したものは等しくなります。例えば、挿入/削除あたりのバイト数が 4(CC\_MATCH\_MODE を "4" に設定)で、かつ最小パケット間ギャップの CC\_MIN\_IPG が "2" のとき、最小のパケット間ギャップは 4(CC\_MATCH\_MODE = "4")掛ける 3(表 8-10 の CC\_MIN\_IPG = "2")、すなわち 12 バイトに等しくなります。最小のパケット間バイト数が CTC を通過するまで、PCS はスキップキャラクタの削除を実行しません。

# 表 8-10. 最小パケット間ギャップの乗数

| CC_MIN_IPG | 挿入/削除の乗数 |

|------------|----------|

| 0          | 1x       |

| 1          | 2x       |

| 2          | 3x       |

| 3          | 4x       |

(注) デバイス品番 TW サフィックスの LatticeECP3-150EA デバイスファミリの CTC 対応について: 末尾が TW となっている初期リリースの LatticeECP3-150EA デバイスでは、PCS が CTC に対応していません。CTC 機能がバイパスされ、ソフト IP で実装されています。ラティスの多くの IP コアでは、CTC ロジックがソフト形式で実装されています。

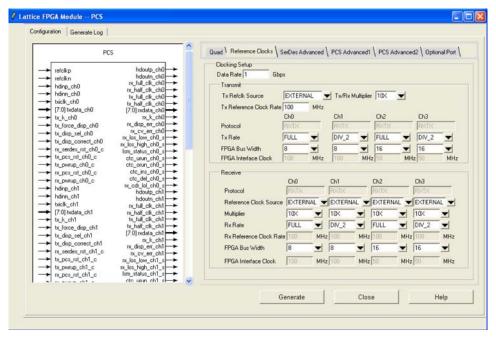

#### Diamond における IPexpress の使用

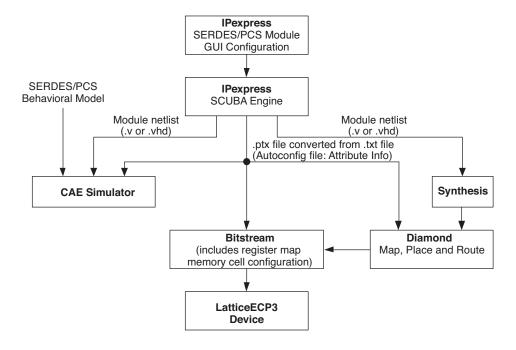

IPexpress は SERDES 及び PCS ブロックの生成と構成(パラメータ等の指定)に使用されます。設計者は GUI を使用して、特定のクワッドまたはチャネルの SERDES プロトコル規格を選択します。IPexpress はこの GUI から入力を受け取り、自動構成ファイル(.txt ファイル)と HDL ネットリストを生成します。HDL モデルは、シミュレーション及び論理合成フローで使用されます。自動構成ファイルには属性レベルのマップ情報が格納されます。このファイルは、シミュレーション及び bitgen プログラムの入力となります。設計者は変更と更新を IPexpress で行ってから、自動構成ファイルを再生成するようにしてください。一部の例外的な状況では、ユーザが構成ファイルを修正することもできます。

図 8-18 に IPexpress を使用して SERDES プロトコル規格用の SERDES/PCS ブロックを生成するためのツールフローを示します。

8-26 tn1176J 02.4

# 図 8-18. SERDES\_PCS、Diamond のユーザフロー

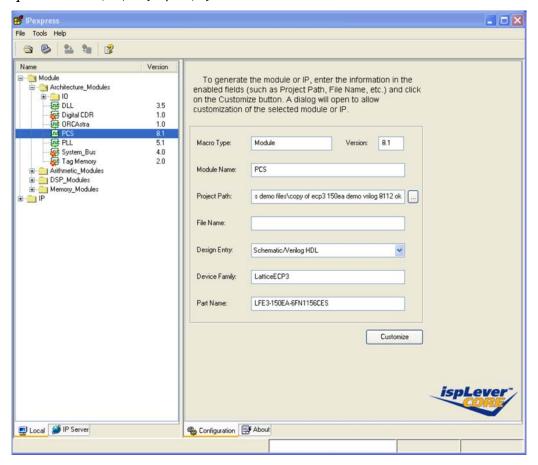

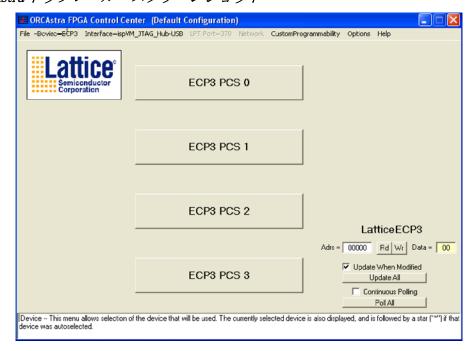

図 8-19 は IPexpress の GUI で PCS を選択したときのメインウィンドウを示しています。

8-27 tn1176J\_02.4

# 図 8-19. IPexpress の PCS メインウィンドウ

8-28 tn1176J\_02.4

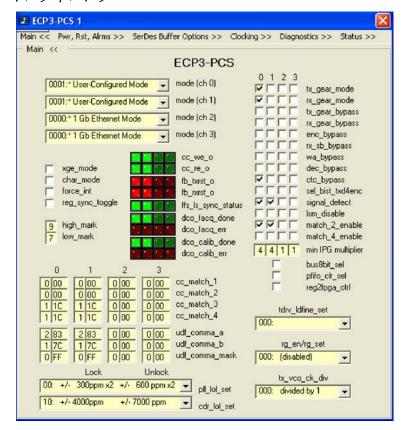

## クワッド・セットアップタブ

図 8-20 にファイル名を入力しメインウィンドウで **Customize** (カスタマイズ) ボタンをチェックしたときの、Quad (クワッド) セットアップタブ・ウィンドウを示します。このウィンドウで最初に行うことは、各チャネルのプロトコルモードの選択です。各チャネルは、'RX and TX'(送受信)、'RX Only'(受信のみ)、'TX Only'(送信のみ)、'Disabled'(ディセーブル)、または 'Low Speed Data Port'(低速データポート)として設定できます。

図 8-20. パラメータ設定 GUI ~ Quad (クワッド) セットアップタブ

表 8-11. SERDES PCS GUI の属性 ~ Quad (クワッド) タブの設定

| GUI テキスト                                        | 属性名          | 範囲                                                                     | デフォルト値   |

|-------------------------------------------------|--------------|------------------------------------------------------------------------|----------|

| Channel Protocol<br>(チャネルのモード)                  | CHx_MODE     | RX and TX, RX Only, TX Only, DISABLE                                   | DISABLE  |

| Disable Channel <sup>注 1</sup><br>(チャネルのディセーブル) | CHx_MODE     | ENABLE, DISABLE                                                        | DISABLE  |

| Protocol<br>(プロトコル)                             | CHx_PROTOCOL | GIGE, SGMII, XAUI, SRIO, PCIE, SDI, G8B10B, 10BSER, 8BSER, CPRI, OBSAI | G8B10B   |

| Low Speed Data Port<br>(低速データポート)               | CHx_LDR      | RX and TX, RX Only, TX Only                                            | DISABLED |

1. ECP3-17EA の 328csBGA では、チャネル 0 と 3 のみが使用できます

8-29 tn1176J 02.4

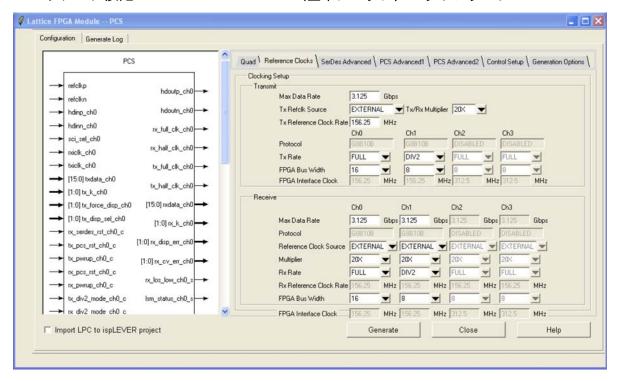

# 基準クロック・セットアップタブ

このタブでは TX 及び RX 基準クロックソースの属性を選択します。基準クロックは EXTERNAL または INTERNAL を選択できます。また、特定のデータレートに必要なクロックレートと乗数の設定を提供するツールがあります。選択したデータバス幅に対して、クワッドをコアとインターフェイスするために必要なクロックレートが表示されます。

#### 図 8-21. パラメータ設定 GUI ~ Reference Clocks (基準クロック) セットアップタブ

8-30 tn1176J 02.4

## 表 8-12. SERDES\_PCS GUI の属性 ~ Reference Clocks (基準クロック) タブの設定

| GUI テキスト                                   | 属性名                       | 範囲                     | デフォルト値 (GUI) | デフォルト値<br>(属性) |

|--------------------------------------------|---------------------------|------------------------|--------------|----------------|

| 送信                                         |                           |                        |              |                |

| Max. Data Rate <sup>1</sup><br>(最大データレート)  | N/A                       | 0.23 ~ 3.2 Gbps        | 2.5 Gbps     | N/A            |

| TX Refclk Source<br>(送信基準クロックソース)          | PLL_SRC                   | INTERNAL, EXTERNAL     | INTERNAL     | REFCLK_INT     |

| TX/RX Multiplier<br>(乗数)                   | REFCK_MULT                | 8X, 10X, 16X, 20X, 25X | (プロトコル依存)    |                |

| TX Reference clock Rate<br>(送信基準クロックレート)   | #REFCLK_RATE <sup>2</sup> |                        | (プロトコル依存)    |                |

| Protocol (プロトコル)                           | ユーザ設定不可                   |                        |              |                |

| TX Rate (送信レート)                            | CHx_TX_DATA_RATE          | FULL, DIV2, DIV11      | FULL         | FULL           |

| FPGA Bus Width<br>(FPGA I/F バス幅)           | CHs_TX_DATA_WIDTH         | 8, 10, 16, 20          | (プロトコル依存)    |                |

| FPGA Interface Clock<br>(FPGA I/F クロックレート) | #CH0_TX_FICLK_RATE        |                        |              |                |

| 受信                                         |                           |                        |              |                |

| Max. Data Rate <sup>1</sup><br>(最大データレート)  | N/A                       | 0.23 ~ 3.2 Gbps        | 2.5 Gbps     | N/A            |

| Protocol (プロトコル)                           | ユーザ設定不可                   |                        |              |                |

| Refclk Source<br>(受信基準クロックソース)             | CHx_CDR_SRC               | INTERNAL, EXTERNAL     | INTERNAL     | REFCLK_INT     |

| Multiplier(乗数)                             | ユーザ設定不可                   |                        |              |                |

| RX Rate(受信レート)                             | CHx_RX_DATA_RATE          | FULL, DIV2, DIV11      | FULL         | FULL           |

| RX Reference Clock Rate<br>(受信基準クロックレート)   | #CH0_RXREFCLK_RATE        |                        |              |                |

| FPGA Bus Width<br>(FPGA I/F バス幅)           | CHx_RX_DATA_WIDTH         | 8, 10, 16, 20          | (プロトコル依存)    |                |

| FPGA Interface Clock<br>(FPGA I/F クロックレート) | #CH0_RX_FICLK_RATE        |                        |              |                |

<sup>1.</sup> レートは自動構成ファイルに反映されません。選択したデータレートに対して DATARATE RANGE の指定は次の通り: 150 Mbps  $\leq$  LOWLOW  $\leq$  230 Mbps、230 Mbps < LOW  $\leq$  450 Mbps、450 Mbps < MEDLOW  $\leq$  0.9 Gbps、0.9 Gbps < MED  $\leq$  1.8 Gbps、1.8 Gbps < MEDHIGH  $\leq$  2.55 Gbps、2.55 Gbps < HIGH  $\leq$  3.2 Gbps。

8-31 tn1176J\_02.4

<sup>2. &#</sup>x27;#' で始まる属性は、ユーザ情報専用を表しています。このような属性は、参照用として自動構成ファイルにも格納されます。

#### SERDES アドバンスト・セットアップ

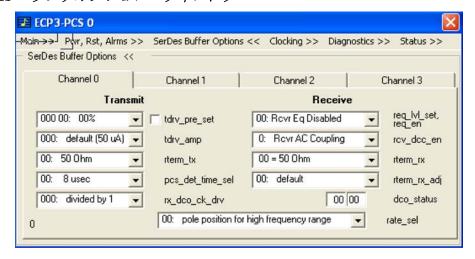

このタブは4チャネル全ての送受信 SERDES のアドバンスト属性にアクセスするために使用されます。送信属性としてはプリエンファシスや終端、差動出力電圧などを選択します。受信属性ではイコライザ、終端、I/O 結合などを選択します。送信 SERDES クロックと PLL の属性も選択します。

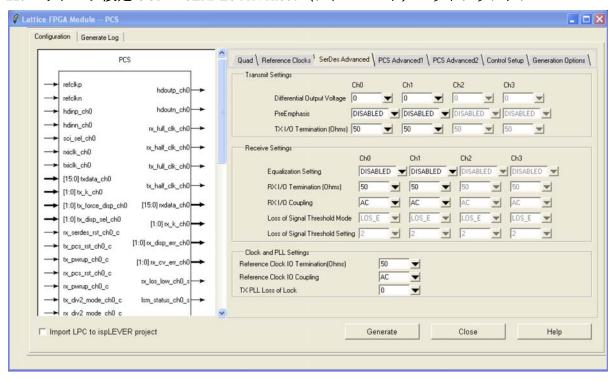

図 8-22. パラメータ設定 GUI ~ SERDES Advanced (アドバンスト) セットアップタブ

8-32 tn1176J 02.4

## 表 8-13. SERDES\_PCS GUI の属性 ~ SERDES Advanced (アドバンスト) タブの設定

| GUI テキスト                                                                                | 属性名                   | 値                                                                                                                                                                                       | デフォルト<br>値            |

|-----------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Differential Output Voltage<br>(差動出力電圧)                                                 | CHx_TDRV <sup>8</sup> | -4 (640mV) <sup>5</sup> , -3 (780mV), -2 (870mV), -1 (920mV), 0 (1040mV:default), 1 (1130mV) <sup>6</sup> , 2 (1260mV) <sup>7</sup> , 3 (1350mV) <sup>7</sup> , 4 (1440mV) <sup>7</sup> | 0                     |

| PreEmphasis<br>(プリエンファシス)                                                               | CHx_TX_PRE            | Disabled, 0 (0%), 1 (5%), 2 (12%), 3 (18%), 4 (25%), 5 (33%), 6 (40%), 7 (48%)                                                                                                          | DISABLED              |

| TX I/O Termination (Ohms) <sup>3</sup><br>(送信 I/O 終端抵抗値)                                | CHx_RTERM_TX          | 50, 75, 5K                                                                                                                                                                              | 50                    |

| Equalization <sup>1</sup><br>(イコライザ)                                                    | CHx_RX_EQ             | Disabled, Mid_Low, Mid_Med, Mid_High,<br>Long_Low, Long_Med, Long_High                                                                                                                  | DISABLED              |

| RX I/O Termination (Ohms) <sup>3</sup><br>(受信 I/O 終端抵抗値)                                | CHx_RTERM_RX          | 50, 60, 75, High                                                                                                                                                                        | 50                    |

| RX I/O Coupling(受信 I/O 結合)                                                              | CHx_RX_DCC            | AC, DC                                                                                                                                                                                  | AC <sup>2</sup>       |

| Loss of Signal Threshold(LOS 閾値)                                                        | CHx_LOS_THRESHOLD_LO  | 2 (+15%), 3 (+25%)                                                                                                                                                                      | <b>2</b> <sup>4</sup> |

| TX PLL Reference Clock I/O<br>Termination (Ohms) <sup>3</sup><br>(送信 PLL 基準クロック I/O 終端) | PLL_TERM              | 50, 2K                                                                                                                                                                                  | 50                    |

| TX PLL Reference Clock I/O Coupling<br>(送信 PLL 基準クロック I/O 結合)                           | PLL_DCC               | AC, DC                                                                                                                                                                                  | AC <sup>10</sup>      |

| PLL Loss of Lock<br>(PLL LOL 周波数偏差)                                                     | PLL_LOL_SET           | 0: +/- 1350ppm x2 <sup>9</sup> 1: +/- 2400ppm x2 2: +/- 6800ppm 3: +/- 400ppm                                                                                                           | 0                     |

- 1. 詳細については表 8-106 を参照してください。

- 2. 内部オンチップ AC 結合の典型的コンデンサ値は 5pF です。

- 3. 終端抵抗とその使い方:

#### RX I/O 終端:

- 50:現在のところ、SMTPE 以外の全プロトコルでは  $50\Omega$  終端抵抗が使用されます。

- 60:柔軟性のため用意されています。

- 75: SMPTE では 75Ω 終端抵抗が使用されます。

- HIGH: Rx が未使用の場合のデフォルト。

#### TX I/O 終端:

- 50:現在のところ、SMTPE 以外の全プロトコルでは  $50\Omega$  終端抵抗が使用されます。

- 75: SMPTE では 75Ω 終端抵抗が使用されます。

- 5K: PCI Express の電気的アイドル、及び PCI Express の R レシーバ検出など。ユーザがレシーバ検出用にこの終端値を設定することはありません。"PCI Express のレシーバ検出"のセクションを参照してください。

#### TX PLL 終端:

- 50: PCB 上に 50Ω 終端抵抗がない場合。

- 2K: PCB 上に 50Ω 終端抵抗がある場合。

- 4. PCS の設定では、GUI は PCI Express 以外の全てのプロトコルに対して値 2 のみに対応しています。PCI Express に対して は、値 2 と 3 の両方に対応しています。

- 5. この振幅を得るためには TDRV\_AMP\_BOOST(CH\_13[3]) を 1 に設定します。

- 6. この設定は PCI Express のデフォルト設定です。PCI Express プロトコルではこのデフォルト設定の使用を推奨します。そのため、IPexpress GUI の TDRV ドロップダウン・ウィンドウはグレー表示となります。他の設定は、自動構成ファイル(.txt ファイル)で CHn\_TDRV 属性を編集して使用できます。

- 7. これらの設定では VCCOB を 1.5V にする必要があります。

- 8. 値は典型的数値です。周波数全域に対して約  $\pm 20\%$  のマージンがあります。詳細については、表 8-105 の CHn\_TDRV の行を参照してください。

- 9. 'x2' は、内部 LOL カウンタの ppm の正常な 2 倍カウントを示しています。

- 10.多くの用途では AC 結合を推奨します。DC 結合を使用する必要があるのは、外部 AC 結合コンデンサを組み合わせる場合のみです。

8-33 tn1176J 02.4

## PCS の位置指定(割り当て)

制約ファイル (.lpf) を記述することで、PCS クワッドの希望する位置を指定できます。制約(プリファレンス)"locate" を使用します。構文例を次に示します。

LOCATE COMP "pcs\_inst\_name" SITE "PCSB" ;

クワッド名 サイト名

Quad A PCSA

Quad B PCSB

Quad C PCSC

Quad D PCSD

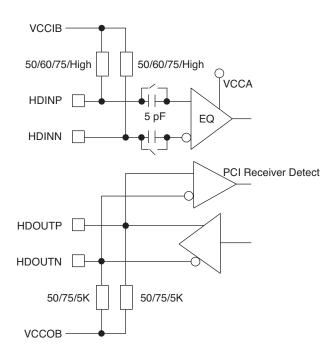

高速 I/O 終端トポロジを図 8-23 に示します。

## 図 8-23. 高速 I/O 終端

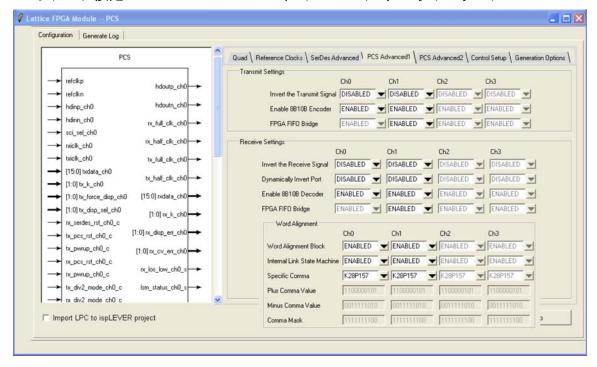

## PCS アドバンスト 1 セットアップ

このタブは 4 チャネル全ての送受信 PCS のアドバンスト属性にアクセスするために使用されます。各 TX 及び RX チャネルの極性と動作モード(8b10b など)は個別に選択できます。さらに、カンマ値、カンママスク、カンマアラインなどのワードアライメント値も選択できます。

8-34 tn1176J 02.4

# 図 8-24. パラメータ設定 GUI ~ PCS Advanced1 (アドバンスト 1) セットアップタブ

表 8-14. SERDES/PCS GUI ~ PCS Advanced1 (アドバンスト 1) セットアップタブ

|                                    | GUI テキスト                                    | 属性名                      | デフォルト値                 |

|------------------------------------|---------------------------------------------|--------------------------|------------------------|

|                                    | Invert the Transmit Signal(送信信号を反転)         | CHx_TX_SB                | DISABLED               |

|                                    | Enable 8b10b Encoder<br>(8B10B エンコーダをイネーブル) | CHx_TX_8B10B             | (プロトコル依存)              |

|                                    | FPGA FIFO Bridge(FPGA FIFO ブリッジ)            | CHx_TX_FIFO              | (プロトコル依存)              |

|                                    | Invert the Receive Signal(受信信号を反転)          | CHx_RX_SB                | DISABLED               |

| Receiver<br>(レシーバ)                 | Dynamically Invert Port<br>(ダイナミックにポートを反転)  | N/A                      | DISABLED               |

|                                    | Enable 8b10b Decoder<br>(8B10B デコーダをイネーブル)  | CHx_RX_8B10B             | (プロトコル依存)              |

|                                    | FPGA FIFO Bridge(FPGA FIFO ブリッジ)            | CHx_RX_FIFO              | (プロトコル依存)              |

|                                    | Word Alignment Block(WA ブロック)               | CHx_RXWA                 | (プロトコル依存)              |

|                                    | Internal Link(内部リンク)                        | CHx_ILSM                 | (プロトコル依存)              |

| Word Alignment<br>(ワード・アライ<br>メント) | Specific Comma(特定のカンマ)                      | #CHx_SCOMMA              | (プロトコル依存)              |

|                                    | Plus Comma Value(正のカンマ値)                    | CHx_COMMA_A <sup>1</sup> | 1100000101             |

|                                    | Minus Comma Value(負のカンマ値)                   | CHx_COMMA_B              | 0011111010             |

|                                    | Comma Mask(カンママスク)                          | CHx_COMMA_M              | (プロトコル依存) <sup>2</sup> |

- 1. 定義上、COMMA\_A と COMM\_B は正と負のランニング・ディスパリティを持つ1組の8b10b コード化制御キャラクタです。プロトコルごとに正しいIDLEシーケンスを指定し、リンクステートマシンを同期する必要があります。例えば、1GbEプロトコルではIDLE(ワードアライメントと同期ステートマシン)としてK28.5+D5.6またはD16.2が必要です。デフォルト値は、リトルエンディアン形式です。

- 2. 多くの用途では、カンマキャラクタとして K28.5 が使用されます。マスクのデフォルト値は 1111111111 です。G8B10B モードでは任意のカンマを使用でき、マスクを 1111111100 にすると 3 つのカンマキャラクタ K28.1、28.5、28.7 を全て検出できます。

8-35 tn1176J 02.4

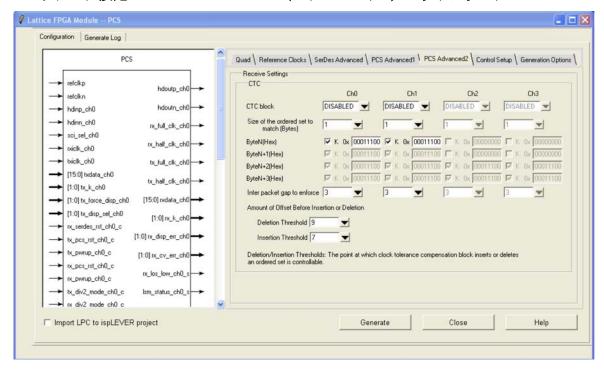

#### PCS アドバンスト 2 セットアップ

このタブはクロックトレランス補償ブロックの値の設定に使用されます。

## 図 8-25. パラメータ設定 GUI ~ PCS Advanced2 (アドバンスト 2) セットアップタブ

表 8-15. SERDES/PCS GUI ~ PCS Advanced2(アドバンスト 2)セットアップタブ

| GUI テキスト                            | 属性名               | デフォルト値      |

|-------------------------------------|-------------------|-------------|

| CTC block                           | CHx_CTC           | (プロトコル依存) 1 |

| Size of ordered set<br>(オーダセットのサイズ) | CHx_CC_MATCH_MODE | (プロトコル依存)   |

| Byte N                              | CHx_CC_MATCH1     | (プロトコル依存)   |

| Byte N+1                            | CHx_CC_MATCH2     | (プロトコル依存)   |

| Byte N+2                            | CHx_CC_MATCH3     | (プロトコル依存)   |

| Byte N+3                            | CHx_CC_MATCH4     | (プロトコル依存)   |

| Interpacket gap<br>(パケット間ギャップ)      | CHx_CC_MIN_IPG    | (プロトコル依存)   |

| Deletion threshold<br>(削除の閾値)       | CCHMARK           | 9           |

| Insertion threshold<br>(挿入の閾値)      | CCLMARK           | 7           |

1. 常にディセーブル: XAUI、SDI、CPRI、OBSAI、10 ビット SERDES、8 ビット SERDES 常にイネーブル: Serial RapidIO

その他の全モード:デフォルトでディセーブル。ほとんどの CTC 機能は IP で提供されます。

8-36 tn1176J 02.4

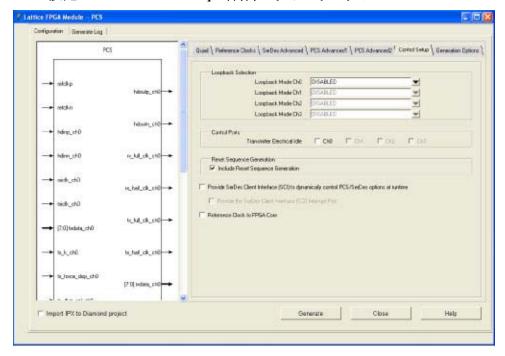

## 制御セットアップ

このタブは SCI インターフェイスとデバッグ及び制御オプションの選択に使用されます。また、SCI、エラーレポート、PLL クォータ・クロック、ループバック機能もイネーブルにできます。

#### 図 8-26. パラメータ設定 GUI ~ Control Setup (制御セットアップ) タブ

表 8-16. Tab 5, SERDES\_PCS GUI 属性 ~ Control Setup (制御セットアップ) タブ

| GUI テキスト                                                                | 属性名                                                                                                                                 | デフォルト値                |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Loopback Mode (Ch0, Ch1, Ch2, Ch3)                                      | DISABLED Loopback serial data after equalizer Loopback serial data after transmit driver Loopback parallel data after de_serializer | DISABLED <sup>1</sup> |

| Transmitter Electrical Idle<br>(トランスミッタ電気的アイドル)                         | signal tx_idle_ch0_c is provided                                                                                                    | DISABLED              |

| Include Reset Sequence Generation <sup>2</sup><br>(リセットシーケンス生成回路を含める)   | Include the TX and RX Reset Sequence                                                                                                | ENABLED               |

| Provide SERDES Client Interface<br>(SCI インターフェイスを設ける)                   | N/A                                                                                                                                 |                       |

| Provide the SERDES Client Interface Interrupt Port<br>(SCI 割り込みポートを設ける) | INT_ALL                                                                                                                             | DISABLED              |

| Reference Clock to FPGA core<br>(基準クロックを FPGA ファブリックに出力する)              | QD_REFCK2CORE                                                                                                                       | DISABLED              |

<sup>1.</sup> ループバックモードがデフォルトモード (DISABLED) のときは、2 つの SERDES ブリッジ・パラレルループバック制御信号 (sb\_felb\_ch[3:0]\_c と sb\_felb\_rst\_ch[3:0]\_c) を HDL モジュールで使用し、ループバックモードを動的にオン / オフできます。ループバックモードを使用しない場合は、これらの信号をグランドに接続する必要があります。

## FPGA への基準クロックとリセットシーケンス

リセットシーケンスはリセット制御用ステートマシンで基準クロックを使用します。

Tx Revclkソースとして"Internal"が選択されると、リセット・ステートマシンは内部基準クロックを用います。

8-37 tn1176J 02.4

<sup>2.</sup> リセット・シーケンス生成については、本ドキュメントの "SERDES/PCS のリセット" セクションに説明があります。

もし "External" が選択されると、リセット・ステートマシンは FPGA コアへの基準クロックを用います。 REFCLK2FPGA 信号がラッパモジュールに現れ (制御レジスタビット、QD\_0A[1] がセット)、これはユーザ も使用できます。

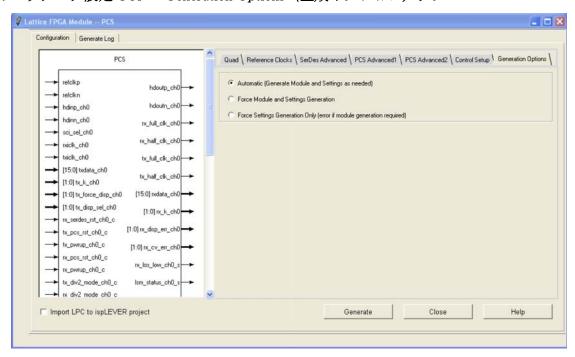

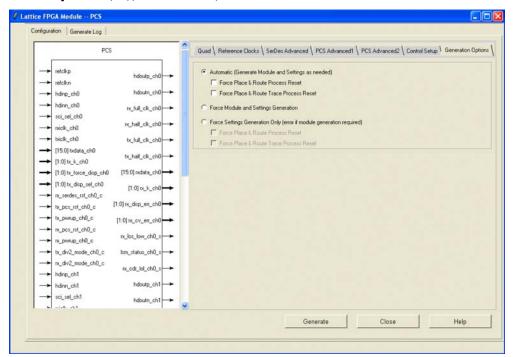

## 生成オプション

このタブには PCS モジュール生成出力ファイルをユーザが自分で選択するためのオプションがあります。

## 図 8-27. パラメータ設定 GUI ~ Generation Options (生成オプション) タブ

以前のバージョンの Diamond で作成した古いプロジェクトを最新バージョンに初めて移行する場合は、パラメータ設定を変更する必要がなくても、最新バージョンで PCS モジュールを再生成するようにしてください。そうすることで、最新のプリミティブ・ライブラリが確実に使用されるようになります。再生成しなかった場合は、デザインがフローの途中で停止するか、フローは完了するものの、ボードが予期しない動作となる可能性があります。

既存のプロジェクト内の PCS モジュールを再生成した場合、HDL ファイルには変化がなく、自動構成ファイルのみの再生成が必要になることがよくあります。その場合は、"Generate Bitstream Data"(ビットストリーム・データの生成)及び "Force One Level"(1 レベルのみ)オプションを実行するとコンパイル時間を節約できます。

- ・Automatic(自動)~ 選択すると、IPexpress で必要なファイルのみが生成されます。HDL ファイルと TXT ファイルの両方が含まれる場合と、TXT ファイルのみの場合があります。これがデフォルト設定で す。

- ・Force Module and Settings Generation (強制的にモジュールと設定を生成) ~ 選択すると、HDL ファイルと TXT ファイルの両方が生成されます。Project Navigator の処理が強制的にリセットされ、論理合成に戻ります。

- ・Force Settings Generation Only (強制的に設定のみを生成) ~ 選択すると、TXT ファイルのみが生成されます。HDL の生成が必要な場合は、エラーメッセージが表示されます。

- ・フロー定義 ~ 生成オプションは2つのモジュールフローで異なる機能を持ちます。

- HDL ソースフロー:プロジェクトナビゲータ内の HDL ファイル 再生成のため、既存の LPC ファイルを IPexpress から開くことができます。この場合、GUI で設定したリ

8-38 tn1176J 02.4

セット点が新しい開始点になります。そのため、ユーザがプロセスをダブルクリックするか、"Force One Level" (1 レベルのみ) オプションを実行すると、そのリセット点から開始されます。

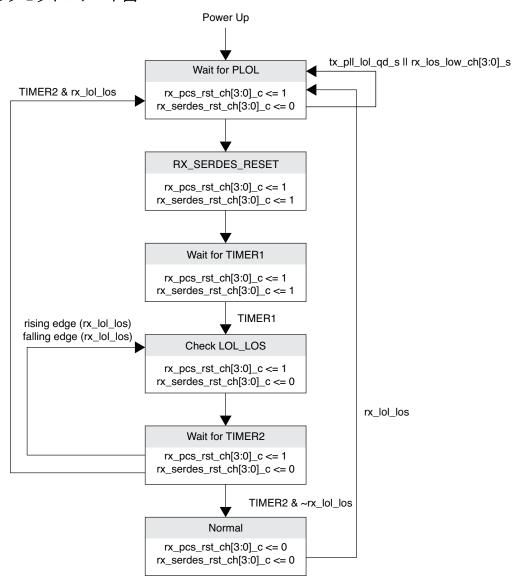

- LPC ソースフロー:プロジェクトナビゲータ内の LPC ファイル LPC ファイルを開いて PCS モジュールを再生成すると、HDL モジュールが再生成されたかどうかに関係なく、プロセス全体がリセットされます。