# 计算机外设的电源管理

莱迪思半导体白皮书 2012年5月

Lattice Semiconductor 5555 Northeast Moore Ct. Hillsboro, Oregon 97124 USA Telephone: (503) 268-8000 www.latticesemi.com

### 标准化的要求

通过附加外设来扩展计算机的功能时,需要使用标准接口才能实现不同厂商应用的全部功能。使用无线通信增加台式机的功能,或者通过使用更多的内存条来增加笔记本电脑的内存,这些方法使得低价的入门级计算机可以升级或根据个人需要进行添减。20世纪90年代初,个人电脑附加卡标准的出现使得不同供应商的内存条都可以用到笔记本电脑上。PCMCIA(个人计算机存储卡国际协会)的成立规范了接口标准,允许使用闪存或硬盘驱动器等插入式附加卡来扩展笔记本电脑内存。许多其他厂商自然很快就意识到,他们的专用功能也可以通过PCMCIA卡添加到这些设备上。

存储、通信和游戏应用等方面制造商加入了 PCMCIA,理解这个接口标准或对这个标准施加影响,使笔记本电脑可以使用他们的器件。随着主机系统和卡应用的多样化,设计师们很快就发现需要慎重考虑卡的工作和启动电源要求,防止供电和系统故障。例如,许多应用所需的磁盘驱动器马达启动或电源保持电容是一个潜在的问题。它们可能会导致很大的浪涌电流,使得主机电源过载,导致系统崩溃或超过主机供电 MOSFET 电源开关的安全工作区(SOA)。PCMCIA 标准委员会需要解决的问题包括电压、电流(包括浪涌电流)和定序。虽然 PCMCIA 早已解散,其标准化的电源供电规范现在仍在其他各种附加卡中使用,包括取代 PCMCIA 卡的 PC 卡。

### 系统设计方法

类似 PC 卡,PCI Express(PCIe)解决了 PC 中附加卡的电源要求。并且适用同样的电源供电考虑,类似 PC 卡,PCIe 卡也可以生成次级电压,根据不同的应用,需要定序和监测。此外,仍需使用外设来预防浪涌电流,而其输入电容循环充放电,相当于添加和移除外设。电源管理已经从由分立逻辑电路和 ASIC 控制器实现的 MOSFET 开关,控制一个或两个电压,发展到 ASSP,如热插拔/软启动控制器、电源定序器和跟踪器、电压监控器、复位发生器和看门狗定时器。然而,随着不同应用需要不同的组合和不同版本的 ASSP,全面的电源管理设计可能会昂贵而且复杂。由于有来自许多不同的厂商提供的数

百种器件,选择正确组合的器件可能是十分艰巨的任务。因而,设计师们常常会简化他们的电源管理设计,无视某些可能出现的故障情况或者假设某种特定的序列会一直出现。举一个例子,一个电源管理设计仅监测输入电源电压,然后通过一个稳压器电压正常来使能下一个稳压器,从而实现其他次级电压的上电。可以肯定的是,这种方法不需要独立的定序器和多个高精度电压监测器来监视每个电压,从而降低了成本和复杂性。但是,尽管这种顺序上电的方法降低了成本和复杂性,电源故障的响应时间可能显著延迟,这将导致严重的数据损坏,产生不完整的数据包并且破坏已经存储的数据。

| PCle 线 | X1            | X1, X4, X8, X16 | X16           |

|--------|---------------|-----------------|---------------|

| 电源     | 10 W 插槽       | 25 W 插槽         | 75W 插槽        |

| +3.3V  |               |                 |               |

| 电压容限   | +/- 9% (最大值)  | +/- 9% (最大值)    | +/- 9% (最大值)  |

| 电源电流   | 3.0 A (最大值)   | 3.0 A (最大值)     | 3.0 A (最大值)   |

| 容性负载   | 1000 uF (最大值) | 1000 uF (最大值)   | 1000 uF (最大值) |

|        |               |                 |               |

| +12V   |               |                 |               |

| 电压容限   | +/- 8% (最大值)  | +/- 8% (最大值)    | +/- 8% (最大值)  |

| 电源电流   | 0.5 A (最大值)   | 2.1 A (最大值)     | 5.5 A (最大值)   |

| 容性负载   | 300 uF (最大值)  | 1000 uF (最大值)   | 2000 uF (最大值) |

图 1——PCIe 电源需求

PCIe 为各种插槽定义了电压、电流和卡输入电容。图 1显示了 PCIe 规范,定义了+12 V和 3.3 V电源和容限、容性负载和最大电流,包括不同的卡的浪涌电流。PCIe 还支持热插拔卡,需要仔细考虑限制热插拔卡的启动电压摆率。应使用电压监控器监测输入电源,以确定电压摆率的限制。虽然 PCIe 不指定电源上电时序,一个使用次级电源的独立应用可能需要复杂的时序。

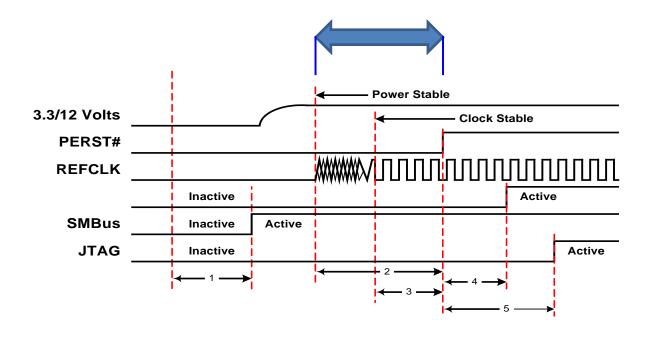

图 2——PCIe 启动波形

图 2 显示了一个 PCIe 卡的启动时序。箭头所示的一个关键参数是在卡插入后的 100ms 周期内,12V 和 3V 电源稳定。100ms 后,该卡通过 PCIe 总线主机发出 PERST#高电平信号使能。通常 100ms 时间太短,不足以完成卡上次级电源上电和大型 FPGA、ASIC 和其他配置器件的初始化。通常需要脉冲展宽或 PERST#信号延迟来满足每块板的需求。

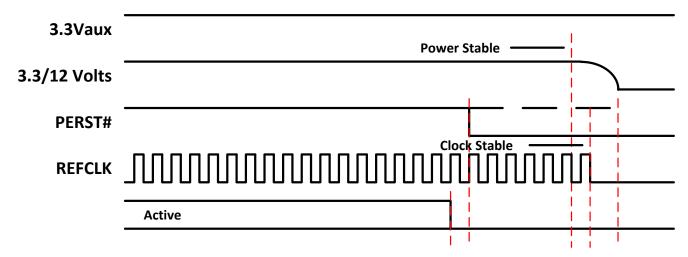

图 3——断电波形

图 3 显示了一个 PCIe 卡的断电时序。PERST#初始化关断,使器件能够以可控的方式在供电电源衰减之前断电。如果卡在插槽通电时突然拔出,器件将突然断电,这可能会导致灾难性的后果。因而,应当小心设计电路板,使它们能够处理突然的拔出并以可控的方式使电路板断电。

设计 PCIe 电源管理时需要应对大量挑战。例如:

- 狼涌□流随每个□□而□化,但是不能有任何瞬□超□ PCle 最大的□源□流□范。浪涌□流的幅度和持□□□取决于□路板的□入□容和其他各种因素,如 FPGA或 ASIC 的启□□流。

- □□每个□用,卡可能需要不同的□插拔控制器□路。

- 定时可能会延□到超□ 100ms PERST#信号,延□复位□序、□□□源上□、FPGA 配置□□和 CPU 复位。

- 设□必□足□快,以至于在□拔出□能□瞬□响□并使□路板断□,从而不破坏系□。

- 所有电源都□□□欠□和□□条件,从而保□工作数据的完整性。

- □源□序□□是灵活的,因□它□于每个□用而言是唯一的,需要根据□□ 更改的需要而改□。

- 包含 CPU 等复□芯片的□路板通常在 I/O □□初始化前需要一个□定的内核□□。

### 分立设计的限制

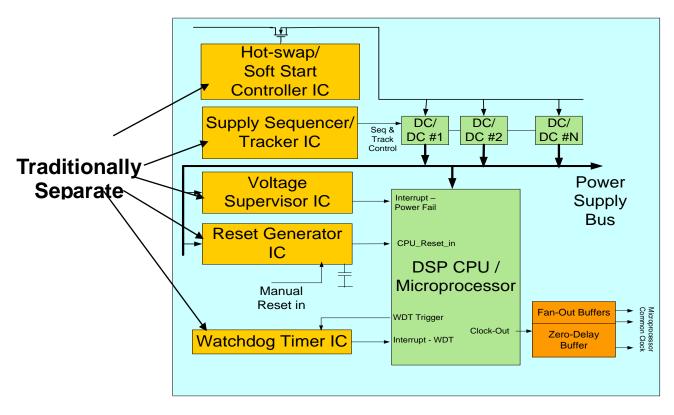

这些挑战如何解决? 传统的设计 PCIe 卡电源管理的方法是使用一个分立的解决方案。图 4 说明了这样一个方法,热插拔控制器、定序器、监控器、复位发生器和看门狗定时器都单独实现。然而,这种方法有严重的缺点。分立的实现方案需要研究数据手册,以便从广泛的器件中进行选择。分立的设计不灵活,因为任何设计上的变化或者一个不同的应用,都将需要不同的分立器件组合。依靠 R/C 网络建立的时序和控制电路,它们的时序将会随着元器件、使用时间和电源电压的变化而改变。最后,由于来自多个厂商的器件之间的互操作性问题,导致分立设计对诸如意外拔出等故障情况的响应速度慢。

图 4——电源管理的分立实现

### 集成的解决方案

电源管理集成到一个系统能显著降低成本,不仅可以提供所有电源管理功能,而且避免了相同功能的重复实现。共享资源的功能可以合并。例如,多个电压监控器、定序器、热插拔控制器、复位发生器集成电路和微调和裕度的功能,可以使用一块集成电路实现。一个

非常精确的带隙基准可以由多种功能共享,进一步降低成本而不牺牲准确性和可靠性。更重要的是,集成将消除分立解决方案中的通信时间延迟。可以在几十微秒内实现故障响应,而不是使用微处理器监控的系统通常所需的几百毫秒。微调、裕度和电压测量可以通过添加一个 ADC 和一个 DAC 轻松实现。

ASIC 可以结合一些电源管理所需的分立器件。但是,它们通常需要一些额外的集成电路,包括一个微处理器来实现解决方案,并且还包括一些不属于该应用所需的功能。此外,基于 ASIC 的解决方案很难仿真,而且作为一种"固定"的方法,它要求任何更改都在电路板外实现。

另一种更有效的方法是使用一个单一的集成电源管理 IC。通过集成所有的电源管理功能,解决了分立解决方案的几个关键问题。来自不同供应商的独立器件所引起的内部通信以及对系统错误情况响应慢的问题得到缓解:可以在短短几微秒内进行处理。整体成本也降低了,因为关键的功能由几个通道共享。

例如,莱迪思 POWR1014A 集成了 10 个可编程电压监控器,使用一个带隙基准,实现了所有通道 0.3%的电压监测精度。

Power Management for Computer Peripherals

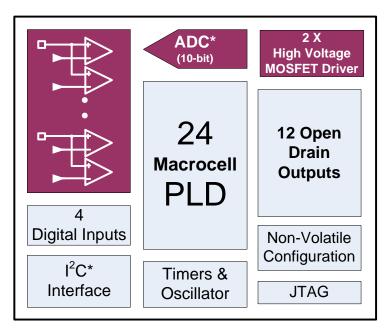

#### 图 5---POWR10414A 结构

内部时钟和内置数字定时器解决了使用外部 R/C 网络的器件所引起的不精确的问题。数字 I/O、可编程定时器和 CPLD 内核监测 PERST#和 PRSNT#,并且产生特定卡的时序以确保正确的时序和配置。根据输入可以产生额外的信号,通知系统复位或欠压情况。POWR1014A 包含两个充电泵,用于控制 N 沟道的 MOSFET。通过改变栅极电压和充电率,同时监控系统的电流和电压以保证满足 PCle 的限制,可以很容易地为每个应用定制热插拔功能。CPLD 内核可以轻松地为各种应用、电路板和供应商更改而修改设计。使用莱迪思的 PAC- Designer 设计软件,可以很容易地配置输入和输出,对 CPLD 内核进行编程。

## 总结

PCI Express 已经标准化了个人电脑和附加卡之间的接口和时序。各种应用需要为每一个独特的电流、时序、电压和定序功能定制设计。分立的解决方案昂贵且缺乏精确的时序、精度低,还有由于较多元器件材料所引起的可靠性问题和一旦设计需要更改时的灵活性问题。莱迪思的 POWR1014A 将 PCIe 电源管理集成到了一个精确、灵活、可编程和低成本解决方案中。

###