# RAM-Type Interface for Embedded User Flash Memory

# **Reference Design**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS and with all faults, and all risk associated with such information is entirely with Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

# **Contents**

| 1. Introduction                                                                                                 | 4     |

|-----------------------------------------------------------------------------------------------------------------|-------|

| 2. Architecture                                                                                                 | 4     |

| 3. Port Descriptions                                                                                            | 5     |

| 4. Functional Description                                                                                       | 5     |

| 4.1. UFM                                                                                                        |       |

| 4.2. DPRAM                                                                                                      | 6     |

| 5. Commands                                                                                                     | 6     |

| 5.1. Command Descriptions                                                                                       | 6     |

| 5.2. Typical Command Sequences                                                                                  |       |

| 6. HDL Simulation and Verification                                                                              | 10    |

| 6.1. Enable Command                                                                                             | 10    |

| 6.2. Write Command                                                                                              | 10    |

| 6.3. Read Command                                                                                               | 11    |

| 6.4. Disable Command                                                                                            | 12    |

| 7. Implementation                                                                                               | 12    |

| Appendix A. UFM Command Sequences                                                                               | 13    |

| Technical Support Assistance                                                                                    |       |

| Revision History                                                                                                |       |

| Figures                                                                                                         |       |

| Figure 2.1. MachXO2 UFM Simplified RAM-Type Interface Block Dia                                                 | gram4 |

| Figure 5.1. Write to UFM Waveform Description                                                                   | 7     |

| Figure 5.2. Read from UFM Waveform Description                                                                  |       |

| Figure 5.3. Read-Modify and Write Back to UFM Waveform Descrip                                                  |       |

| Figure 6.1. Enable Command HDL Simulation Waveform                                                              |       |

| Figure 6.2. Loading of DPRAM HDL Simulation Waveform                                                            |       |

| Figure 6.3. Write to UFM Command Sequence HDL Simulation Way                                                    |       |

| Figure 6.4. Read from UFM Command Sequence HDL Simulation W Figure 6.5. Disable Command HDL Simulation Waveform |       |

| rigure 0.5. Disable Command TDL Simulation Waveform                                                             | 12    |

|                                                                                                                 |       |

| Tables                                                                                                          |       |

| Table 3.1. Port Descriptions                                                                                    | 5     |

| Table 5.1. List of Commands                                                                                     | 6     |

| Table 7.1. Performance and Resource Utilization                                                                 |       |

| Table A.1. MachXO2 Embedded Function Block Commands                                                             | 13    |

## 1. Introduction

MachXO2<sup>™</sup>-640/U and higher density devices provide a User Flash Memory (UFM) block, which can be used for a variety of applications including PROM data storage, or general purpose non-volatile Flash memory. In some design contexts, the UFM may be used concurrently to store EFB initialization data, or in rare situations configura- tion data overflow, as specified by user settings.

The UFM is page addressable. Each page has 128 bits (16 bytes). The UFM block connects to the device core through the Embedded Function Block (EFB) WISHBONE interface. If desired, users can also access the UFM block independently through the hardened JTAG, I2C and SPI interfaces of the device.

This reference design is intended to provide a familiar and intuitive extension to the MachXO2 Embedded Func- tional Block User Flash Memory (EFB UFM). This design facilitates users to access the MachXO2 EFB UFM mod- ule without the knowledge of WISHBONE protocol..

# 2. Architecture

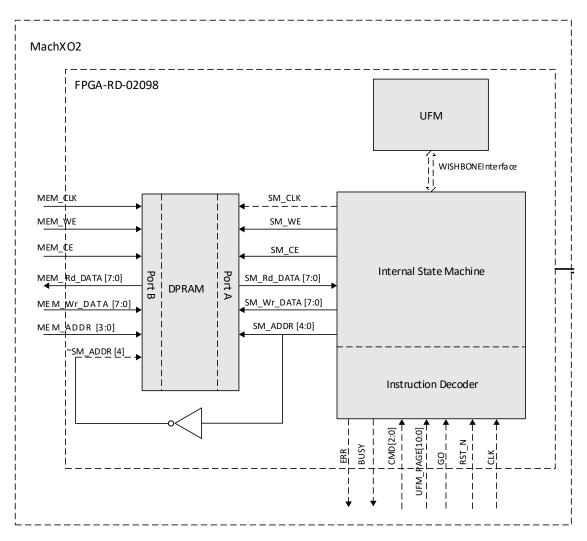

Figure 2.1. MachXO2 UFM Simplified RAM-Type Interface Block Diagram

# 3. Port Descriptions

**Table 3.1. Port Descriptions**

| Port              | Direction | Width (Bits) | Description                                                             |

|-------------------|-----------|--------------|-------------------------------------------------------------------------|

| CLK               | Input     | 1            | Clock input*                                                            |

| RST_N             | Input     | 1            | Active low reset signal                                                 |

| Command Interface |           |              |                                                                         |

| GO                | Input     | 1            | High ('1') starts command process. GO is ignored if BUSY is asserted.   |

| CMD               | Input     | 3            | Command operation                                                       |

| UFM_PAGE          | Input     | 11           | Target UFM Page                                                         |

| BUSY              | Output    | 1            | Status bit. Indicates operation in progress.                            |

| ERR               | Output    | 1            | Error bit. The last operation failed. Will be cleared on subsequent GO. |

| Data Interface    |           |              |                                                                         |

| MEM_CLK           | Input     | 1            | Clock for the DPRAM module                                              |

| MEM_WE            | Input     | 1            | Write enable for the DPRAM module                                       |

| MEM_CE            | Input     | 1            | Clock enable for the DPRAM module                                       |

| MEM_ADDR          | Input     | 4            | DPRAM address                                                           |

| MEM_Wr_DATA       | Input     | 8            | DPRAM write data                                                        |

| MEM_Rd_DATA       | Output    | 8            | DPRAM read data                                                         |

<sup>\*</sup>Note: Modify the design parameter READ\_DELAY when CLK > 16.6 MHz. See discussion below.

# 4. Functional Description

This design facilitates user access to the MachXO2 EFB UFM module without the knowledge of WISHBONE protocol. The user has to provide the necessary command sequence with UFM page address. A GO signal will trigger the interface to perform the necessary WISHBONE transactions to read or write the UFM.

#### 4.1. UFM

The User Flash Memory of the MachXO2 device features non-volatile storage in a single sector. Other features include:

- Non-volatile storage up to 256Kbits

- 100K write cycles

- Write access is performed page-wise; each page has 128 bits (16 bytes)

- Auto-increment addressing

Typical of Flash technology, the array must be cleared (erased) before data can be overwritten. The erased state of the UFM bits is '0'. The smallest erasable unit is the entire sector. Thus, any data which must be preserved (e.g. Config data overflow, or EBR init data) must be read out and stored in another available memory (e.g. EBR) prior to the Erase command. After the erase is complete, the data is written back to the UFM. The user is responsible for performing the storage operation. This requirement, along with limited erase cycles and long erase/program times, renders the UFM a poor solution for 'scratch pad' RAM (or similar) applications. MachXO2 Embedded Block RAM (EBR) is the recommended on-board memory type for high-churn, volatile data storage.

In the design's default configuration, the internal UFM read operation has been optimized for lower CLK rates. For CLK rates exceeding 16.6 MHz, this design must be configured to insert additional Retrieval Delay into the state machine which generates the UFM read command. A parameter, READ\_DELAY, is provided for this purpose. The source file "UFM\_WB\_top.v" can be modified directly or the parameter passed in the module instantiation. The min- imum value for READ\_DELAY can be calculated as follows:

READ DELAY(min) = 240/PERIOD - 4

where PERIOD = CLK period in ns

Example, for CLK = 47 MHz, PERIOD = 21.28 ns thus READ\_DELAY >= 8 (7.28 rounded up)

Refer to the *Reading Flash Pages* section of TN1204, MachXO2 Programming and Configuration Usage Guide for more information on the Read UFM command structure and timing requirements.

#### 4.2. DPRAM

The design incorporates a 32-byte (2 UFM page), byte addressable True Dual port RAM. The internal state machine accesses one port of the DPRAM. During the UFM write operation the state machine reads data from the DPRAM and writes it to the UFM. During UFM read operations the data read from the UFM is stored in the DPRAM.

The second DPRAM port is accessed by the user to exchange data to or from the UFM. The DPRAM memory is divided into two pages of 16 bytes data each. The Most Significant Bit (MSB) of the DPRAM addresses are controlled by the internal state machine for page swapping. Thus, only one page (16 bytes) of the DPRAM is available through the user port at any given time. The available page is synchronized by the reference design and optimized for maximum throughput.

During a UFM write operation, the DPRAM page swap happens once a GO is recognized. For higher throughput in back-to-back writes, this allows the user to immediately start loading the next page to be transferred to the UFM. During a read operation, the DPRAM page swap happens at the end of a read UFM operation and the user can start reading the DPRAM data once BUSY signal is low. In the case of back-to-back Read operations, the data remains available in the DPRAM until the subsequent Read is complete, allowing for higher throughput operation.

## 5. Commands

Table 5.1. List of Commands

| Command | Operation          | BUSY Signal                | Page Swap                |

|---------|--------------------|----------------------------|--------------------------|

| 000     | Read 1 page        | Clear when finished        | End of transaction       |

| 001     | Read next page     | Clear when finished        | End of transaction       |

| 010     | Write 1 page       | Clear upon UFM busy clear. | Beginning of transaction |

| 011     | Write next page    | Clear upon UFM busy clear  | Beginning of transaction |

| 100     | Enable UFM access  | Clear upon UFM busy clear. | N/A                      |

| 101     | Disable UFM access | Clear when finished        | N/A                      |

| 110     | (undefined)        | _                          | _                        |

| 111     | Erase UFM          | Clear upon UFM busy clear  | N/A                      |

#### 5.1. Command Descriptions

- Enable UFM access (100) Required to enable UFM read/write access. Exercising this command will tempo- rarily disable certain features of the device, notably GSR, User SPI port and Power Controller. These features are restored when UFM access is disabled using Disable UFM access command (101). See Using User Flash Memory and Hardened Control Functions in MachXO2 Devices Reference Guide (TN1246), for more information on this behavior. BUSY is asserted until the devices internal Flash pumps are fully charged.

- Write 1 page (010) The 16 bytes of data from DPRAM is written into the UFM page specified by UFM\_PAGE. The

internal UFM page pointer is auto incremented at the completion of the command. Make sure that 16 bytes of

data that has to be written to the UFM is loaded to the DPRAM prior to issuing a GO. BUSY will be asserted as soon

as a GO is recognized and will be de-asserted when programming is complete.

- Write next page (011) The 16 bytes of data from DPRAM are written into the subsequent UFM page pointed by

the internal UFM page pointer. The internal UFM page pointer is auto-incremented at the completion of the

command. Make sure that 16 bytes of data that has to be written to the UFM is loaded to the DPRAM prior to

issuing a GO. BUSY will be asserted as soon as a GO is recognized and will be de-asserted when programming is

complete.

- Read 1 page (000) 16 bytes of data is read back from the UFM page specified by UFM\_PAGE and stored in the DPRAM. The internal UFM page pointer is auto-incremented at the completion of the command. Following a Read command, the 16 bytes of UFM data can be read from the DPRAM after BUSY de-asserts.

- Read next page (011) The subsequent UFM page pointed by the internal UFM page pointer is read and stored

into the DPRAM. The internal UFM page pointer is auto-incremented at the completion of the command. Following a Read command, the 16 bytes of UFM data can be read from the DPRAM after BUSY de-asserts.

- Disable UFM access (101) This command disables UFM interface for change access.

- Erase UFM (111) This command is issued to completely erase (set to '0') the UFM. BUSY is asserted until era- sure is complete.

## 5.2. Typical Command Sequences

#### Notes:

- A GO will be ignored when BUSY is asserted.

- Any UFM read/write or erase command while UFM is disabled will assert the ERR signal.

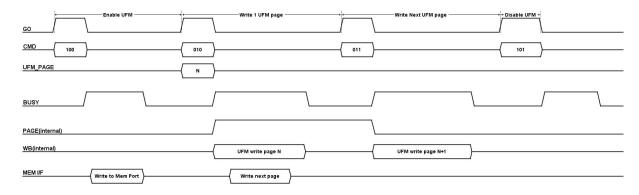

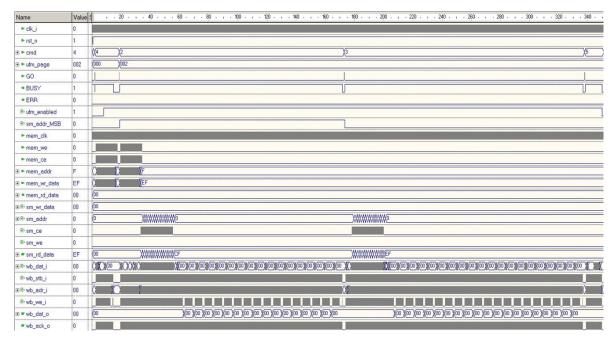

#### Write to UFM

The following sequence explains the necessary commands to be followed for a UFM write operation. The sequence assumes the target UFM row is in the erased state.

- 1. Enable UFM access (100) Check for BUSY signal to be low and issue enable UFM command on the CMD bus and issue a GO. BUSY signal is asserted once a GO is recognized.

- 2. Write 1 page (010) Load the DPRAM with one page (16 bytes) of data to be written to the UFM. Check for BUSY signal to be low, issue the Write 1 Page command on the CMD bus, UFM page address on the UFM\_PAGE bus and issue a GO. The DPRAM page swap happens once a GO is recognized so that the user can load the next page to be written to the UFM into the DPRAM while the first page is being trans- ferred to the UFM.

- 3. Write next page (011) Wait for the previous page to be transferred to the UFM successfully and the BUSY signal goes low. Now issue a write next page command and issue GO. The internal UFM page pointer is auto-incremented.

- 4. Repeat steps 2 and 3 until all desired pages are written. Figure 5.1. illustrates steps 2 and 3.

- 5. Disable UFM access (101) Check for BUSY signal to be low and issue disable UFM command on the CMD bus and issue a GO. BUSY signal is asserted once a GO is recognized.

Figure 5.1. Write to UFM Waveform Description

© 2012-2021 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

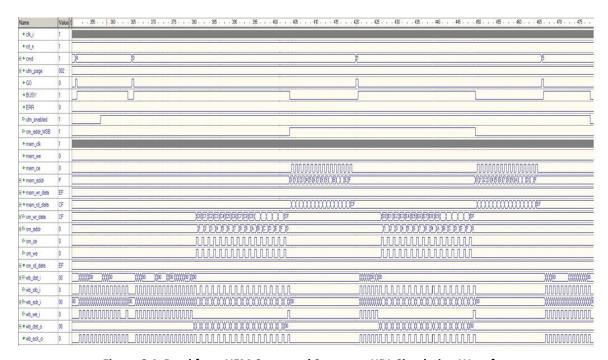

#### **Read from UFM**

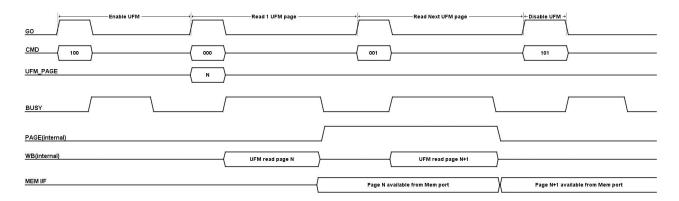

The following sequence explains the necessary commands to be followed for a UFM read operation.

- 1. Enable UFM access (100) Check for the BUSY signal to be low and issue an enable UFM command on the CMD bus and issue a GO. BUSY signal is asserted once a GO is recognized.

- 2. Read 1 page (000) Check for BUSY signal to be low, issue the Read 1 Page command on the CMD bus, UFM page address on the UFM\_PAGE bus and issue a GO. Data read from UFM will be loaded in the DPRAM and user can access the data once BUSY signal goes low.

- 3. Read next page (011) Check for the BUSY signal to be low, issue the read next page command on the CMD bus and issue a GO. The internal UFM page pointer is auto. Data read from UFM will be loaded in the DPRAM and user can access the data once the BUSY signal goes low.

- 4. Repeat steps 2 and 3 until all desired pages have been read. Figure 5.2. illustrates steps 2 and 3.

- 5. Disable UFM access (101) Check for the BUSY signal to be low and issue a disable UFM command on the CMD bus and issue a GO. The BUSY signal is asserted once a GO is recognized.

Figure 5.2. Read from UFM Waveform Description

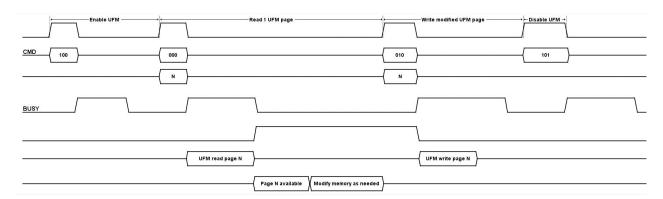

#### **Read Modify Write Back to UFM**

The page read from UFM can be retained in the DPRAM and data modification may be performed directly on the DPRAM, followed by a Write 1 Page operation. The following sequence explains the necessary commands to be followed in order to modify the contents of UFM.

**Note:** The modified data cannot be arbitrary. Only erased bits/bytes (='0') of the UFM can be given new values. This sequence is provided to support applications where small amounts of data, or data unaligned to UFM page boundaries, is accumulated over time (e.g. a data logger application).

- 1. Enable UFM access (100) Check for BUSY signal to be low and issue an enable UFM command on the CMD bus and issue a GO. BUSY signal is asserted once a GO is recognized.

- 2. Read 1 page (000) Check for BUSY signal to be low, issue the Read 1 Page command on the CMD bus, UFM page address on the UFM\_PAGE bus and issue a GO. Data read from the UFM will be loaded in the DPRAM and is available to read or edit once the BUSY signal goes low.

- 3. Modify DPRAM data as needed. The DPRAM data is byte addressable. The user may modify the intended byte(s) directly in the DPRAM. Alternatively, the data may be read from, and re-written to, the DPRAM.

- 4. Write 1 page (010) Once the data in the DPRAM has been modified or re-written, check for the BUSY signal to be low, issue the Write 1 Page command on the CMD bus, set the UFM page address on the UFM\_PAGE bus and issue a GO. Note that UFM page address must be specified for both read and write.

- 5. Repeat steps 2 through 4 until all desired pages have been modified. Figure 5.3. illustrates steps 2 through 4.

- 6. Disable UFM access (101) Check for the BUSY signal to be low and issue a disable UFM command on the CMD bus and issue a GO. BUSY signal is asserted once a GO is recognized.

Figure 5.3. Read-Modify and Write Back to UFM Waveform Description

# 6. HDL Simulation and Verification

#### 6.1. Enable Command

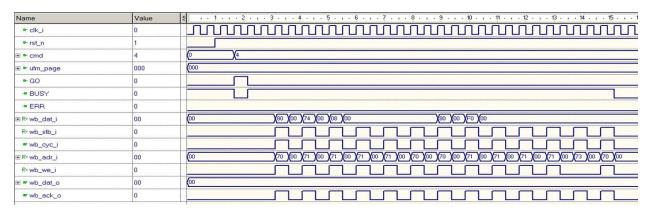

Figure 6.1. Enable Command HDL Simulation Waveform

#### 6.2. Write Command

Figure 6.2. Loading of DPRAM HDL Simulation Waveform

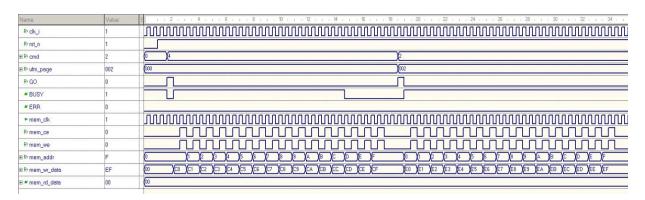

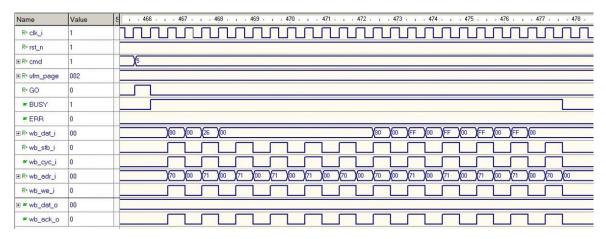

Figure 6.3. Write to UFM Command Sequence HDL Simulation Waveform

#### 6.3. Read Command

Figure 6.4. Read from UFM Command Sequence HDL Simulation Waveform

### 6.4. Disable Command

Figure 6.5. Disable Command HDL Simulation Waveform

# 7. Implementation

This design is implemented in VHDL and Verilog. When using the design in a different device, density, speed, or grade, performance and utilization may vary. Default settings are used during the fitting of the design.

Table 7.1. Performance and Resource Utilization

| Family   | Language    | Speed Grade | Utilization | fMAX (MHZ) | I/Os | Architecture Resources |

|----------|-------------|-------------|-------------|------------|------|------------------------|

| MachXO2* | Verilog-LSE | -3          | 143 LUTs    | >50        | 42   | 1 EFB, 1 EBR           |

|          | Verilog-Syn | -3          | 244 LUTs    | >50        | 42   | 1 EFB, 1 EBR           |

|          | VHDL-LSE    | -3          | 133 LUTs    | >50        | 42   | 1 EFB, 1 EBR           |

|          | VHDL-Syn    | -3          | 255 LUTs    | >50        | 42   | 1 EFB, 1 EBR           |

<sup>\*</sup>Note: Performance and utilization characteristics are generated using LCMXO2-1200ZE-3TG100C with Lattice Diamond® 3.3 design software.

# **Appendix A. UFM Command Sequences**

The following table explains the different UFM internal command structure involved for the various operations of this reference design.

**Table A.2. MachXO2 Embedded Function Block Commands**

| Operation               | Command (Hex)           | Operand (Hex) | Write Data               | Read Data              |  |  |

|-------------------------|-------------------------|---------------|--------------------------|------------------------|--|--|

| Enable UFM Access (100  | Enable UFM Access (100) |               |                          |                        |  |  |

| Enable UFM              | 74                      | 08 00 00      | _                        | _                      |  |  |

| Status check            | F0                      | 00 00 00      | _                        | 1 byte status data     |  |  |

| Write One Page (010)    |                         |               |                          |                        |  |  |

| Set Address             | B4                      | 00 00 00      | 40 00 aa aa*             | _                      |  |  |

| Write UFM               | C9                      | 00 00 01      | 16 bytes data from DPRAM | _                      |  |  |

| Status check            | F0                      | 00 00 00      | _                        | 1 byte status data     |  |  |

| Write Next Page (011)   |                         |               |                          |                        |  |  |

| Write UFM               | C9                      | 00 00 01      | 16 bytes data from DPRAM | _                      |  |  |

| Status check            | F0                      | 00 00 00      | _                        | 1 byte status data     |  |  |

| Read One Page (000)     |                         |               |                          |                        |  |  |

| Set Address             | B4                      | 00 00 00      | 40 00 aa aa*             | _                      |  |  |

| Read UFM                | CA                      | 10 00 01      | _                        | 16 bytes data from UFM |  |  |

| Read Next Page (011)    |                         |               |                          |                        |  |  |

| Read UFM                | CA                      | 10 00 01      | _                        | 16 bytes data from UFM |  |  |

| Disable UFM Access (101 | 1)                      |               |                          |                        |  |  |

| Disable UFM             | 26                      | 00 00 00      | _                        | _                      |  |  |

| Bypass                  | FF                      | FF FF FF      | _                        | _                      |  |  |

| Erase UFM (111)         |                         |               |                          |                        |  |  |

| Erase UFM               | 0E                      | 08 00 00      | _                        | _                      |  |  |

| Status check            | F0                      | 00 00 00      | _                        | 1 byte status data     |  |  |

<sup>\*</sup>Note: The aa aa value is copied from the 11-bit UFM\_PAGE module input.

# **Technical Support Assistance**

Submit a technical support case through www.latticesemi.com/techsupport.

14

# **Revision History**

#### Revision 1.6, September 2021

| Section | Change Summary |                                                                                          |

|---------|----------------|------------------------------------------------------------------------------------------|

| All     | •              | Corrected revision number of previous release. It should be Revision 1.5 instead of 1.2. |

|         | •              | Updated contents to include changes from version 1.3 to version 1.4.                     |

#### Revision 1.5, December 2019

| Section | Ch | Change Summary                                        |  |

|---------|----|-------------------------------------------------------|--|

| All     | •  | Changed document number from RD1126 to FPGA-RD-02098. |  |

|         | •  | Updated document template.                            |  |

#### Revision 1.4, October 2014

| Section                      | Change Summary                                                               |

|------------------------------|------------------------------------------------------------------------------|

| All                          | Updated Table 3, Performance and Utilization. Added support for Diamond 3.3. |

|                              | Added support for Lattice Synthesis Engine (LSE).                            |

| Technical Support Assistance | Updated information.                                                         |

#### Revision 1.3, October 2012

| Section                                 | Change Summary                                                                                                              |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Commands                                | Updated the following waveforms: Write to UFM Waveform, Read from UFM Waveform, Read-Modify and Write Back to UFM Waveform. |

| Performance and Resource<br>Utilization | Updated Performance and Resource Utilization table for Diamond 2.0 support and to include VHDL implementation information.  |

#### Revision 1.2, July 2012

| Section | Change Summary                                                      |

|---------|---------------------------------------------------------------------|

| All     | Updated design and document to include READ_DELAY parameterization. |

#### Revision 1.1, June 2012

| Section | Change Summary                         |

|---------|----------------------------------------|

| All     | Corrected functional simulation issue. |

#### Revision 1.0, April 2012

| Section | Change Summary   |

|---------|------------------|

| All     | Initial release. |

© 2012-2021 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

www.latticesemi.com