1

# Gen2 SerialRapidIO와 저가 저전력 FPGA

Lattice 반도체 백서 2011년 8월

Lattice Semiconductor 5555 Northeast Moore Ct. Hillsboro, Oregon 97124 USA

Telephone: (503) 268-8000 www.latticesemi.com

## 머리말

유무선 및 의료, 영상처리와 같은 어플리케이션을 처리하기 위한 대역폭의 지속적인 성장으로 인해, 설계자는 실시간 신호처리에서 필요로 하는 특정 기능과 그들에게 제공 되는 Tool에 의지할 수 밖에 없다. 무선통신의 영역에서는 기존의 3 세대의 HSPA+ 와 EV-DO(3G+), 현재 새롭게 만들어진 4G 시스템의 설치로 인해 데이터 처리능력과 Backhaul의 요소가 중요하다.

외견상으로 빠르게 증가하는 가입자 기반을 지원하기 위해 비디오와 데이터 어플리케이션의 지속적인 양적 데이터 처리 기술이 필요하다.

이것은 결국 고속처리, 높은 신뢰성, 높은 처리량과 다양한 DSP 영역에서 필요로 하는 것을 제공하고 낮은 지연을 위해 인터페이스 프로토콜, 코프로세싱과 필수 브리지 어플리케이션이 중요하게 요구 된다. 그리고 대부분의 시스템과 마찬가지로 비용과 전력소비를 줄이는 것이 가장 중요하다. 낮은 비용으로 처리되는 DSP와 네트워크 프로세스 유닛 (NPU), SerialRapidIO(SRIO) Gen2를 지원하는 저전력 FPGA는 이러한 목적을 충족하기위해 이상적인 플랫폼을 제공한다.

#### SRIO Gen2

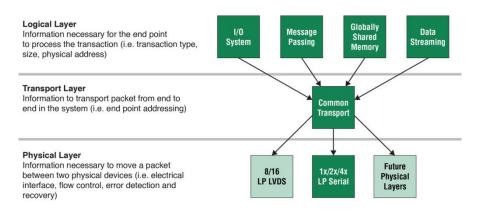

RapidIO사양은 패킷의 발생과 처리 그리고 다른 endpoint와의 연결을 위해 스위칭하는 Endpoint를 정의한 패킷 베이스의 기술이다. 그림 1에 나타난 바와 같이 프로토콜 스택은 물리 계층 프로토콜, 패킷 전송(Routing) 계층 프로토콜과 다중전송 형식인 논리 계층의 세 계층으로 나누어진다.

넓게 보면 Gen2 사양에서 중요하게 추가된 것은 5/6Gbps 직렬 데이터 속도 (SERDES) 를 지원하고 이러한 고속 직렬 채널을 위해 X2 Lane 사양이 지원되는 것이다(이전의 1.3 버전의 사양에는 1x/4x이 가능함). 이미 설명한 것처럼 프리미엄은 설계의 비용이나 전력 예산을 희생하지 않고 성능을 유지하는 것이다. 그래서 이 문서는 Gen2 사양의 2x의 출력 가능성에 초점을 두고 있다. 이것이 향상된 중요한 점이다. 왜냐하면 많은 경우의 시스템은 한 Lane에서 제공하는 3.125Gbps 이상의 처리량을 필요로 하고 있다. 그러나 그이상의 처리를 위해 4x Lane을 구성하는 것은 과잉이다.

2x SERDES Lane 구성은 현재 3.125Gbps의 속도로 구성된 4x Lane까지 대부분의 어플리케이션이 지원되는 래티스 ECP3 같은 저비용, 저전력 FPGA와 함께 설계자에게 효과적인 솔루션을 제공할 수 있다. 프로그램이 가능한 것과 FPGA의 유연성은 여러 트래픽을 전달하는 기법을 구현할 수 있는 논리 계층에서 빛을 발휘한다. 그림 1을 보면 4가지

데이터 패싱 프로토콜이 있다. 이러한 것을 다이렉트 I / O 액세스, 메시지 패싱, GSM, 데이터 스트리밍 이라고 한다.

논리 계층은 어떻게 SRIO Endpoint가 데이터를 교환하는지를 정의하고, 시스템 구성, 요구사항을 정의 한다. 그림 1은 RapidIO 스펙에서 사용되는 프로토콜 스텍을 보여준다.

그림 1 - RapidIO Protocol Stack

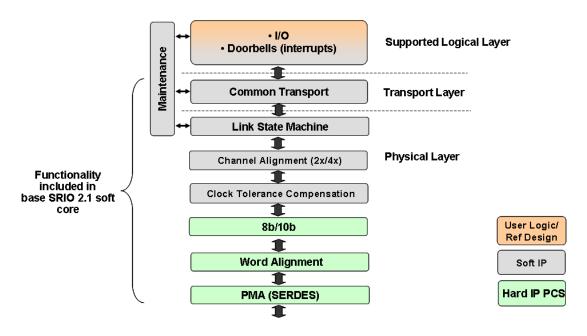

그림2는 어떻게 프로토콜 스텍이 저가의 프로그램 가능한 플랫폼 내에서 실행되는지 보여준다.

물리계층과 전송계층은 소프트 IP코어에서 실행되는 반면에 논리계층의 많은 부분은 디자인의 요구사항을 만족시키기 위해 사용자가 구성할 수 있게 남겨둔다.

그림 2 - FPGA 실행의 예제

## 저비용 저전력 SRIO-처리가 가능한 FPGA의 역할과 이점

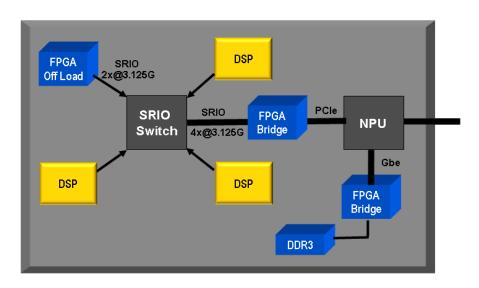

위에서 언급한 것과 같이 DSP와 NPU를 위해 많은 처리를 하지만 일반적으로 각각 처리하는 고유의 영역을 가지고 있다. 집중 처리를 위한 DSP 응용프로그램일지라도 그것들은 실행 영역 내에서 실행되거나 SRIO 스위치나 SRIO로부터 GbE 이나 PCle와 같은 기본적인 프로토콜 기반인 SERDES로 제공되는 브리지 장치인 endpoint 와 인터페이스를 위해 좀더 많은 인터럽트를 처리하는(doorbells) 경향이 있다. NPU는 반면에 트래픽쉐이핑과 큐링을 위해 주로 책임 있는 감시 역할을 한다.

그림3은 어떻게 저비용 저전력 FPGA가 성공적이고 효율적인 시스템을 위해 사용되는지 보여주는 예제이다.

그림3 FPGA 어플리케이션의 예제

ASIC 보다 월등한 FPGA는 유연성과 타임투마켓에 여유롭게 진입할 수 있는 장점으로 오랫동안 높이 평가 되었다. 그러나 최근까지 이런 장점들은 오직 이러한 프리미엄을 이용하는 것과 가격과 전원을 고려하지 않는 하이엔드 디바이스를 사용 함으로서 가능해졌다. 현재의 저렴한 비용, 낮은 전력의 FPGA는 주로 글루 로직과 버그수정 어플리케이션에 사용이 제한되어 있다. 그러나 FPGA의 필요성이 점점 크게 확대되었으며, 이제 간단한 처리를 위해서만 FPGA를 사용하는 것은 아니다.

설계자의 요구사항을 처리하고 타이트한 비용과 파워를 유지하기 위해 FPGA 구조는 이전의 전통적인 FPGA에 비해 성능을 향상 시켰으며, 기능과 로직의 집적도를 증가 시키고, 저전력 및 저비용으로 원하는 기능을 구현할 수 있도록 점진적인 변화를 가져왔다. 내장된 SERDES, 고속 DSP 블록, DDR3 메모리 인터페이스 지원과 내부 메모리 블록과

같은 향상된 기능이 가능해 졌고, 그것들은 디자인을 위해 매우 중요한 구성요소가 되고 있다.

시스템 엔지니어와 설계 엔지니어는 RRH와 베이스밴드 처리뿐만 아니라 유선과 이미지 프로세싱 어플리케이션의 처리 및 복잡한 신호 처리 어플리케이션을 구현하기 위해 파워를 줄이고 이전의 고가의 SERDES를 내장하는, 프로그램 가능한 FPGA를 플랫폼을 활용할 수 있다.

# 요약

시스템 설계자는 낮은 운영 비용과 유지 비용으로 고속의 시스템을 생산하기 위해 다양한 측면으로, 어떻게 계획을 세워야 할 지 생각해야 한다.

그리고 이러한 부분은 끊임없이 진행 될 것으로 예상된다. FPGA는 전체적인 시스템 성능의 향상과 운용 비용을 낮춰줌으로 앞으로 새로운 단계를 개척하기 위해 시스템 설계자에게 매우 중요한 역할을 할 것이다. 기능이 풍부한 저가의 FPGA는 빠르게 타임투 마켓에 진입할 수 있고, 이익 실현을 할 수 있으며, 점점 발전하는 기술 표준에 부응하기위한 성능과 유용성을 가능하게 한다.

이제 시스템 / 설계 엔지니어들은 끊임없이 진화하는 신호 처리 시장의 어려움을 극복하기 위해 흥미롭고 향상된 툴세트를 갖추게 되었다.