# MachXO2 デバイスにおける高速 インターフェイスの実装

2014年1月

テクニカルノート TN1203

## はじめに

広帯域データ転送に対するニーズの高まりに応じて、業界は従来のシングルデータレート(SDR)から、ダブルデータレート(DDR)アーキテクチャへ移行しました。SDR はクロック信号の立ち上がりエッジ、または立ち下がりエッジのいずれかにデータを合わせて転送します。一方 DDR はクロック信号の両エッジを利用してデータを転送します。DDR の場合、クロック一周期につきデータが2回転送されるため、同じクロック周波数の場合、本質的にデータ転送速度がSDR の2倍になります。DDR クロッキング技法はDDR SDRAMなどのメモリインターフェイスで幅広く採用されています。その結果、DDR SDRAMメモリはシステムの信号波形の品質要件を厳しくすることなく、SDR SDRAMメモリに比べて2倍の帯域を得ることができます。

Lattice MachXO2  $^{\text{M}}$  PLD ファミリは、プログラマブル I/O (PIO) に作り込みロジックを通じて、DDR と SDR の両アプリケーションに対して高速インターフェイスをサポートします。また MachXO2 デバイスは DDR や DDR2、及び LPDDR SDRAM メモリインターフェイスをサポートする専用回路を備えています。このドキュメントは、MachXO2 デバイスにおける高速汎用 DDR インターフェイスと、DDR / DDR2 及び LPDDR メモリインターフェイスの実装に焦点を当てています。また MachXO2 デバイスの組み込み機能を利用して、高速インターフェイスにおいて最良の性能を得るためのガイドラインも提供します。

## 高速インターフェイス・アーキテクチャ

## ギアリングロジック

高速汎用 DDR(Generic DDR、GDDR) インターフェイスは、プログラマブル I/O(PIO) セルに組み込まれたギアリングロジック(Mux / DeMux)で対応します。このギアリングは、FPGA ファブリックに対する性能要件を抑えつつ高速 I/O に対応するために必要です。

MachXO2 デバイスでは、I/O バンクの位置と論理規模に応じて 4 種類のギアリング比を設定できます。x1 ギアリング比は全てのデバイス規模の全バンクで使用できます。x2 と x4、及び 7:1 ギアリング比は MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの上辺と下辺バンクで使用できます。7:1 ギアリング比は主にビデオディスプレイ・アプリケーションに使用します。x2/x4 ギアリング回路は、受信側と送信側の両方を 7:1 回路と共有しています。x2/x4 MachXO2-1200/U、及びこれより大規模デバイスの右辺バンクは、x2/x4 DDR メモリインターフェイスをサポートしています。x2/x4 DDR メモリはメモリ PIO セルに組み込まれた専用の x1 ギアリングロジックを利用します。

| 表 11-1. MachXO2-640U &     | <sup>L</sup> MachXO2-1200/U. | 及びこれよりっ              | <i>ト規模デバ</i> ・ | イスのギアリン  | グロジック |

|----------------------------|------------------------------|----------------------|----------------|----------|-------|

| 20 11 1. Macili 102 0100 ( | _ 10100112102 1200/ 0\       | 74 U U U U U U U U U | VVUIDE /       | 17147177 | / / / |

| ギアリングロジック           | 定義      | ギアリング比     | 左辺  | 右辺  | 下辺  | 上辺  |

|---------------------|---------|------------|-----|-----|-----|-----|

| DDR x1 <sup>1</sup> | GDDR    | 1:2 又は 2:1 | Yes | Yes | Yes | Yes |

| Input DDR x2        | GDDR    | 1:4        | _   | _   | Yes | _   |

| Input DDR x4        | GDDR    | 1:8        | _   | _   | Yes | _   |

| Input DDR 7:1       | GDDR    | 1:7        | _   | _   | Yes | _   |

| Output DDR x2       | GDDR    | 4:1        | _   | _   | _   | Yes |

| Output DDR x4       | GDDR    | 8:1        | _   | _   | _   | Yes |

| Output DDR 7:1      | GDDR    | 7:1        | _   | _   | _   | Yes |

| mem DDR x1          | メモリ DDR | 1:2 又は 2:1 | _   | Yes | _   | _   |

<sup>1.</sup> DDRx1 は全ての規模の MachXO2 デバイスで利用可能

<sup>© 2011</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

<sup>(</sup>日本語版は日本語による理解のため一助として提供しています。その作成にあたっては可能な限り正確を期しておりますが、原文英語版との不一致や不適切な訳文がある場合を含み、英語版が正(有効)です。特に電気的特性・仕様値係わる事項については最新版の英語版を必ず参照するようにお願い致します。)

表 11-1 は様々な I/O バンクが対応するギアリングロジックの詳細を示したものです。PIO セルの詳細については MachXO2 ファミリデータシートを参照してください。

## 様々なタイプの I/O ロジックセル

様々なギアリング比に対応するために、MachXO2 デバイスには 3 種類の PIO ロジックセルがあります。これらは基本(basic)PIO セルとメモリ PIO セル、そしてビデオ PIO セルです。

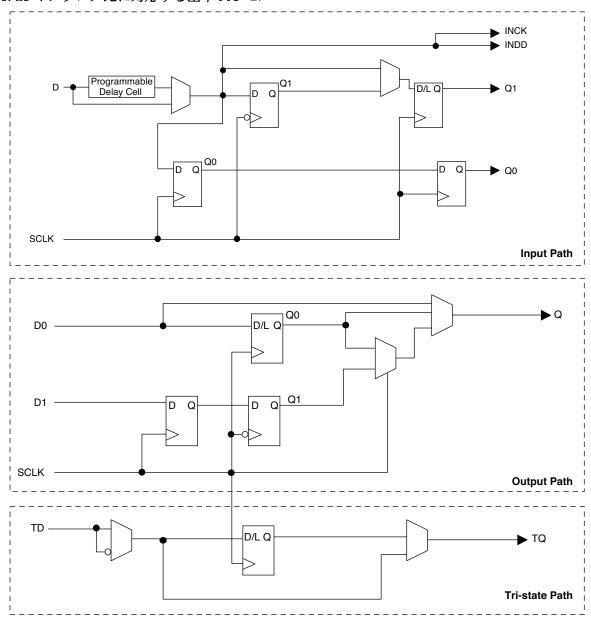

図 11-1. x1 ギアリング比に対応する基本 PIO セル

基本 PIO セルは従来型の SDR レジスタと DDR x1 レジスタを含みます。これは MachXO2 デバイスの全ての辺・バンクで利用できます。メモリ PIO セルは DDR メモリアプリケーションに対応し、MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの右辺で利用できます。ビデオ PIO セルは、x2 / x4 および7:1 ギアリング用途に対応し、MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスで利用でき、下辺が受信インターフェイス用、上辺が送信インターフェイス用です。各タイプの PIO セルに関する入出力構造の詳細については MachXO2 ファミリデータシートを参照してください。参考として PIO セルのブロック図を下に示します。

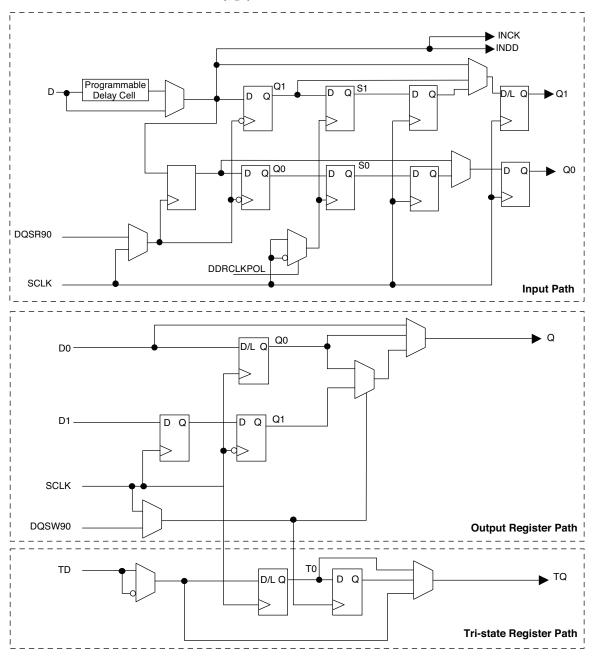

## 図 11-2. DDR メモリアプリケーションに対応するメモリ PIO セル

## 図 11-3. x2 / x4 と 7:1 アプリケーション用のビデオ PIO セル

## PIO セルのクロックドメイン転送

MachXO2 のギアリングロジックは、PIO セル内で高速データのシリアル化及びパラレル化を実行します。高速エッジクロック(ECLK)から低速システムクロック(SCLK)へのデータのクロックドメイン転送は、2本の内部信号である UPDATE と SEL によって、デバイス設計として確実に動作するようになっています。 SEL 信号は 7:1 ギアリングの場合、データの 3 ビット分と 4 ビット分を一度にサンプルするために Low と High にトグルします。 x2/x4 ギアリングの場合、SEL 信号はトグルしません。UPDATE 信号は全てのギアリング時に同じ動作をし、正しいデータバイト数でレジスタを更新します。その後、これらデータは次段での処理のために SCLK でクロッキングされます。図 11-3 に x2/x4 入力ギアリングロジックのアーキテクチャを示します。

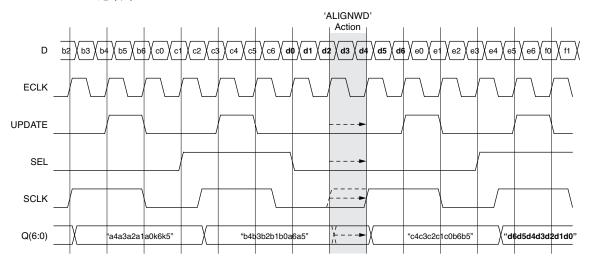

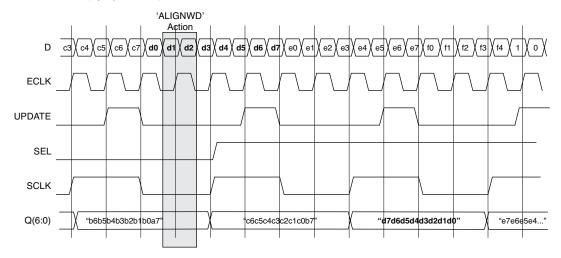

MachXO2 デバイスには、最小限の FPGA リソースでワードアライメントができるロジックがあります。ワードアライメントの結果、UPDATE と SEL、及び SCLK 信号がシフトします。ワードアライメントは、高速インターフェイス・コンポーネントの ALIGNWD ポートに、アライメント要求信号を与えることでアクティブにされます。ALIGNWD は ECLK ドメインと非同期にできますが、少なくとも 2 ECLK 周期幅が必要です。7:1 ギアリングの場合、最大で 7 通りのワードオーダの組み合わせをループするため、ALIGNWD は 7 回パル

ス入力される必要があります。x2/x4 ギアリングの場合は、最大で 8 通りのワードオーダの組み合わせをループするため、ALIGNWD は 8 回パルス入力される必要があります。

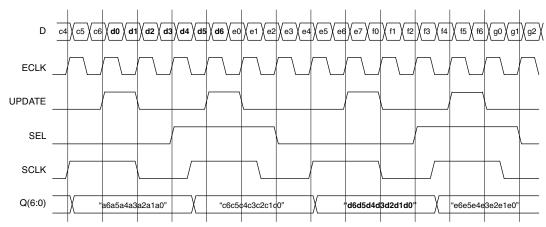

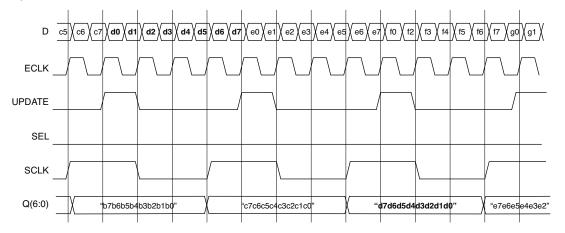

図 11-4 と 11-5 は、異なるギアリング要件における UPDATE と SEL、ECLK、及び SCLK 信号のタイミング 関係を示したものです。図 11-6 と 11-7 は、様々なギアリング比におけるワードアライメント処理を示した ものです。ギアリングロジックについてのこの説明は、高速インターフェイスの受信側と送信側の両方に当 てはまります。7:1 ギアリング機能を利用したワードアライメントの実装の詳細については、参照デザイン "RD1093 - MachXO2 Display Interface (MachXO2 ディスプレイ・インターフェイス)"を参照してください。

DDR メモリインターフェイスのクロックドメイン転送は、メモリリード / ライト動作用にデバイスに組み込まれた 90° 位相シフト・クロックツリーを使用して実行されます。DLL 及び DQS 検出ロジックにより、DDR メモリに対するデータの正しいリードとライトが確保されます。

## 図 11-4. 7:1 デシリアライザのタイミング

## 図 11-5. x2/x4 デシリアライザのタイミング

## 図 11-6. ALIGNWD に応答する 7:1 デシリアライザのタイミング

図 11-7. ALIGNWD に応答する x2 / x4 デシリアライザのタイミング

## 外部高速インターフェイスの説明

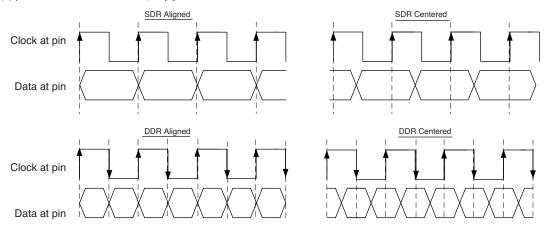

MachXO2 デバイスに対して使用できる外部高速インターフェイスの定義として、"センター"と"アライン"の 2 種類があります。センター外部インターフェイスの場合、デバイスピンでクロックエッジがデータの中央にあります。アライン外部インターフェイスの場合、デバイスピンでクロックエッジとデータ遷移が揃っています。これは"エッジオンエッジ (edge-on-edge)"と呼ばれることもあります。

図 11-8 は SDR と DDR における外部インターフェイス波形を示します。アライン・インターフェイスでは、キャプチャ・フリップフロップのセットアップタイムとホールドタイムを満足するため、クロックエッジがデータの中央に位置するように、受信側でクロック遅延調整が必要です。同様にセンター・インターフェイスでは、クロックエッジがデータの中央に位置して送信するように、送信側でクロックの遅延調整をする必要があります。

特定のバスインターフェイスでは、センターとアライン・インターフェイスの両方が使用されるかもしれません。例えば DDR SDRAM メモリの場合、リード時のクロックとデータの関係はアライン・インターフェイスですが、ライト時のクロックとデータの関係はセンター・インターフェイスです。

### 図 11-8. 外部インターフェイスの定義

## 高速インターフェイスを構成するブロック

MachXO2 デバイスは、高速インターフェイスを構成する専用の論理ブロックを備え、各ブロックは独自の機能を実行します。様々なブロックを組み合わせることにより、特定インターフェイスについて究極の性能を実現できます。このセクションでは、デバイスのハードウェア・コンポーネントについて説明します。"DDR ソフトウェアのプリミティブとアトリビュート"セクションで、これらコンポーネントのライブラリ・エレメントを説明します。クロッキングと PLL アーキテクチャの詳細については TN1199 "MachXO2 sysCLOCK PLL Design and Usage Guide (MachXO2 sysCLOCK PLL の設計と使用ガイド)"を参照してください。

#### **ECLK**

エッジクロック ECLK は高速で低スキューの I/O 専用クロックです。MachXO2-640U と MachXO2-1200/U、及びこれより大規模のデバイスでは、上下辺のそれぞれに 2 本のエッジクロックがあります。プライマリ・クロックネット PCLK は、ECLK と直接接続することができます。また下辺の PCLK ピンは、ビデオアプリケーション用などのために、PLL に対して最短配線になっています。

### **ECLKSYNC**

これは ECLK 同期ブロックです。各 ECLK にはそれぞれこの ECLKCYNC コンポーネントがあり、クロックドメイン転送でデータを同期化します。またこのコンポーネントは、エッジクロックを動的にディセーブルすることにより、動作時の省電力化のために使用できます。

### **SCLK**

SCLK はデザインでのシステムクロックです。高速インターフェイスを実現するためには、SCLK はプライマリ・クロックピンやプライマリ・クロックネットを使用する必要があります。MachXO2 デバイスあたり 8 本のプライマリ・クロックピン(PCLK)と、8 本のプライマリ・クロックネットがあります。

#### **CLKDIV**

クロック分周器 CLKDIV は、高速エッジクロックから低速システムクロックを生成するために使用します。 MachXO2-640U と MachXO2-1200/U、及びこれより大規模のデバイスには、上辺と下辺のそれぞれに 2 個の CLKDIV があります。本コンポーネントを介して、ECLK 周波数は 2、3.5、または 4 分周することができます。

### **PLL**

MachXO2 デバイスには最大 2 つの PLL があり、その数は論理規模により異なります。MachXO2-640U と MachXO2-1200/U、及び MachXO2-2000 には 1 つ、MachXO2-2000U と MachXO2-4000、及び MachXO2-7000 には、2 つの PLL があります。また、あらかじめ割り当て済みのデュアルファンクション I/O ピンがあり、基準クロック入力として PLL に供給します。

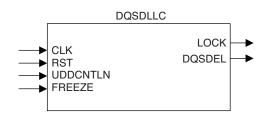

## **DQSDLL**

MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスには、最大 2 つの DQSDLL があります。右上の DQSDLL は上辺と右辺のバンクを制御し、左下の DQSDLL は下辺と左辺のバンクで利用できます。本コンポーネントは、DDR メモリと汎用高速インターフェイスの両方で使用でき、クロックスレーブ遅延セル (DLLDEL) とともに、アライン・インターフェイスでレシーバでの 90° クロック位相シフト / 遅延に用いられます。

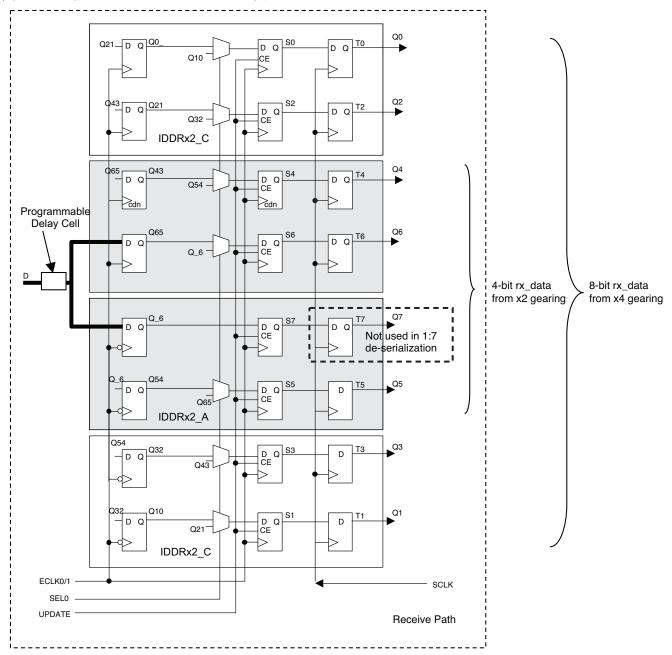

## 入力 DDR (IDDR)

汎用入力 DDR コンポーネントは、PIO セルの受信側で x1 と x2、x4、及び 7:1 ギアリング(この場合シリパラ変換)比に対応します。x1 ギアリング比は IDDRX、すなわち基本 PIO セルによりサポートされます。この場合 1 ビット DDR データを受信し、SCLK と同期した 2 ビット幅のパラレルデータを出力します。x1 ギアリングにはクロックドメイン転送はありません。x2 ギアリングは IDDRX2 によりサポートされ、ECLK に同期した 1 ビット DDR データを受信し、SCLK に同期した 4 ビットのパラレルデータを出力します。IDDRX4 にも同じ機能が適用され、ECLK に同期した 1 ビット DDR データを受信し、SCLK に同期した 8 ビットのパラレルデータを出力します。7:1 ギアリングは、x4 ギアリングと同一構造を共有していますが、8 ビットではなく、7 ビットのパラレルデータを出力します。汎用高速インターフェイスのギアリングは、ビデオ PIO セルによりサポートされます。

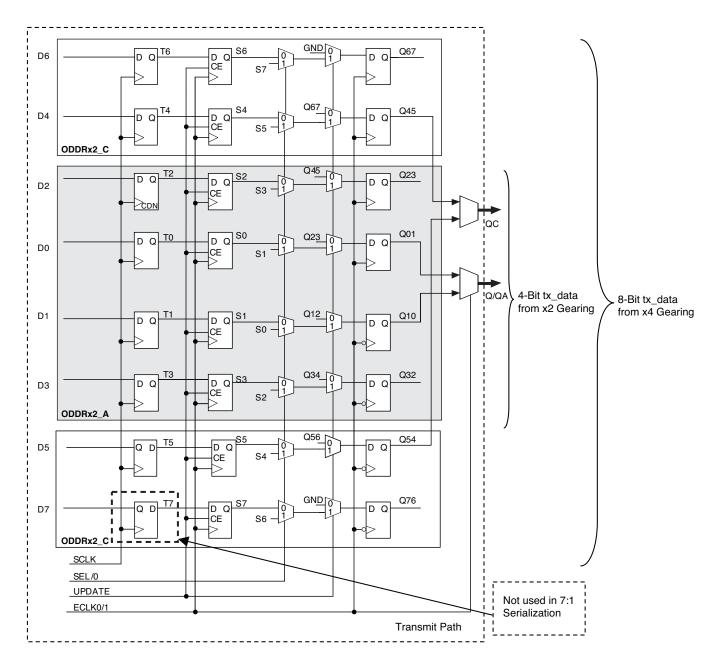

## 出力 DDR (ODDR)

汎用出力 DDR コンポーネントは、PIO セルの送信側で x1 と x2、x4、及び 7:1 ギアリング(この場合パラシリ変換)比に対応します。x1 ギアリングは ODDRX、すなわち基本 PIO セルによりサポートされます。この場合 SCLK を基準に 2 ビットデータをシリアライズします。x1 ギアリングにはクロックドメイン転送はありません。x2 ギアリングは ODDRX2 によりサポートされ、4 ビットのパラレルデータが、SCLK によりクロッキングされ、ECLK を基準にシリアライズされます。x4 ギアリングは、ODDRX4 によりサポートされ、8 ビットのパラレルデータが SCLK によりクロッキングされ、ECLK を基準にシリアライズされます。7:1 ギアリングは x4 ギアリングと同一構造を共有しており、7 ビットのパラレルデータが ECLK を基準にシリアライズされます。汎用高速インターフェイスのギアリングは、ビデオ PIO セルによりサポートされます。

## 遅延

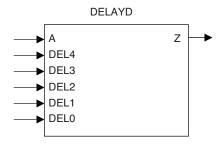

高速インターフェイスでは 2 種類の遅延が利用可能です。1 番目のタイプは I/O ロジック遅延で、入力データパスに適用されます。32 タップの I/O ロジック遅延は、静的(固定)または動的のいずれも可能ですが、データパスの動的遅延をサポートするのは MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの下辺のみです。Lattice 設計ソフトウェアでインターフェイスをパラメータ設定する場合、I/O ロジック遅延(DELAYE)にはデフォルトとして固定値が使用されます。ソフトウェアが使用するインターフェイスに応じた固定遅延値を適用します。下辺の入力データパスの動的遅延(DELAYD)は、動的遅延値またはユーザ指定の遅延値が与えられます。動的遅延の場合、モジュールにはユーザロジックと接続して遅延を制御するためのポートが必要になります。I/O ロジック遅延を利用することで、SDR のゼロ・ホールドタイムや、x1 ギアリング用のプライマリクロック注入遅延(インジェクション・ディレイ)補償、x2 / x4 ギアリング用のエッジクロック注入遅延補償を実現できます。

2番目のタイプはクロックスレーブ遅延セル(DLLDEL)で、入力クロックを 90° 位相遅延し、クロックエッジをデータの中央に合わせます。このブロックは、7ビット制御コードを介して DQSDLL によりデジタル的に制御されます。プライマリ・クロックピン 1 本ごとにクロックスレーブ遅延セルが一つあります。その入力はプライマリ・クロックピンから得られ、出力は x1 アライン・インターフェイスに対してプライマリ・クロックネットをドライブするか、x2 /x4 アライン・インターフェイスに対して ECLK をドライブします。

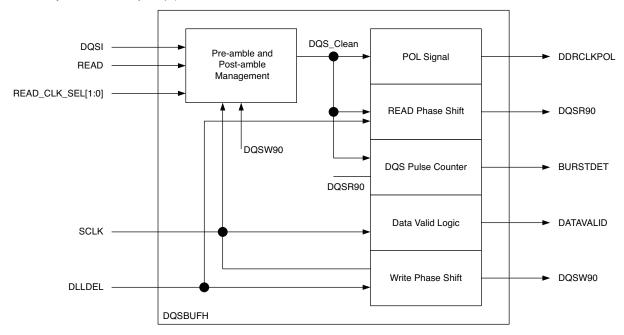

## **DQSBUF**

このコンポーネントは DDR メモリ専用の DQS 回路です。メモリリード動作では DQS 入力信号を 90° 位相シフトし、メモリライト動作では SCLK を 90° 位相シフトします。このブロックからはクロック極性検出 (DDRCLKPOL)、バースト検出 (BURSTDET)、及びデータ有効 (DATAVALID) の各信号が生成されます。 DQSBUF は MachXO2-640U と MachXO2-1200/U、及びこれより大規模なデバイスの右辺バンクにあります。

## **IDDRDQS**

これは DDR メモリの入力バッファで、DQS から SCLK へのクロックドメイン転送をサポートします。これらの PIO セルは DDR メモリインターフェイス専用で、DDR メモリのリード動作で使用されます。IDDRDQS は MachXO2-640U と MachXO2-1200/U、及びこれより大規模なデバイスの右辺バンクにあります。

## **ODDRDQS**

これは DDR メモリの出力バッファで、SCLK から DQS へのクロックドメイン転送をサポートします。これらの PIO セルは DDR メモリインターフェイス専用で、DDR メモリのライト動作で使用されます。ODDRDQS は MachXO2-1200 及びこれより大規模なデバイスの右辺バンクにあります。

## 汎用高速 DDR インターフェイス

汎用高速インターフェイス、或いは汎用 DDR (GDDR: Generic DDR) は、MachXO2 においては専用のロジックブロックでサポートされます。このセクションでは GDDR のタイプやインターフェイス・ロジック、及びシリコンで GDDR 機能をサポートするソフトウェアについて説明します。

## 高速 GDDR インターフェイスのタイプ

MachXO2 デバイスファミリがサポートする GDDR インターフェイスは、ソフトウェアで事前に定義され、キャラクタライズされています。表 11-2 に対応する全インターフェイスと、各インターフェイスの簡単な説明を示します。

以下は表 11-2 で用いられているインターフェイスの略称の説明です。

- · G ~ 汎用

- ・IREG ~ SDR 入力 I/O レジスタ

- ・ OREG ~ SDR 出力 I/O レジスタ

- ・DDRX1 ~ DDR x1 I/O レジスタ

- ・ DDRX2 ~ DDR x2 I/O レジスタ

- ・DDRX4 ~ DDR x4 I/O レジスタ

- ・ DDR71 ~ DDR 7:1 I/O レジスタ

- · \_RX ~ 受信インターフェイス

- · TX ~ 送信インターフェイス

- ・ECLK ~ GDDR インターフェイスで ECLK(エッジクロック)リソースを使用

- ・SCLK ~ GDDR インターフェイスで SCLK (プライマリクロック) リソースを使用

- · Centered (センター) ~ デバイス入力端でクロックエッジがデータの中央にある

- · Aligned (アライン) ~ デバイス入力端でクロックエッジとデータエッジが揃っている

## 表 11-2. 汎用高速 I/O DDR インターフェイス

| モード                | インターフェイス名               | 説明                                          | サポートするデバイスと<br>辺               |

|--------------------|-------------------------|---------------------------------------------|--------------------------------|

| RX SDR             | GIREG_RX.SCLK           | SCLK を用いる SDR 入力                            | 全デバイス、全辺                       |

| RX GDDRx1 Aligned  | GDDRX1_RX.SCLK.Aligned  | SCLK を用いる DDRx1 入力、データは<br>入力クロックのエッジと揃っている | 640U と 1200/U これ以上の<br>デバイス、全辺 |

| RX GDDRx1 Centered | GDDRX1_RX.SCLK.Centered | SCLK を用いる DDRx1 入力、入力クロックエッジはデータの中央にある      | 全デバイス、全辺                       |

| RX GDDRx2 Aligned  | GDDRX2_RX.ECLK.Aligned  | ECLK を用いる DDRx2 入力、データは<br>入力クロックのエッジと揃っている | 640U と 1200/U これ以上の<br>デバイス、下辺 |

| RX GDDRx2 Centered | GDDRX2_RX.ECLK.Centered | ECLK を用いる DDRx2 入力、入力クロックエッジはデータの中央にある      | 640U と 1200/U これ以上の<br>デバイス、下辺 |

| RX GDDRx4 Aligned  | GDDRX4_RX.ECLK.Aligned  | ECLK を用いる DDRx4 入力、データは<br>入力クロックのエッジと揃っている | 640U と 1200/U これ以上の<br>デバイス、下辺 |

| RX GDDRx4 Centered | GDDRX4_RX.ECLK.Centered | ECLK を用いる DDRx4 入力、入力クロックエッジはデータの中央にある      | 640U と 1200/U これ以上の<br>デバイス、下辺 |

| RX GDDR71          | GDDR71_RX.ECLK.7:1      | ECLK を用いる GDDR 7:1 入力                       | 640U と 1200/U これ以上の<br>デバイス、下辺 |

| TX SDR             | GOREG_TX.SCLK           | SCLK を用いる SDR 出力                            | 全デバイス、全辺                       |

| TX GDDRx1 Aligned  | GDDRX1_TX.SCLK.Aligned  | SCLK を用いる DDRx1 出力、データは<br>出力クロックのエッジと揃っている | 全デバイス、全辺                       |

| TX GDDRx1 Centered | GDDRX1_TX.SCLK.Centered | SCLK を用いる DDRx1 出力、出力クロックエッジはデータの中央にある      | 640U と 1200/U これ以上の<br>デバイス、全辺 |

| TX GDDRx2 Aligned  | GDDRX2_TX.ECLK.Aligned  | ECLK を用いる DDRx2 出力、データは<br>出力クロックのエッジと揃っている | 640U と 1200/U これ以上の<br>デバイス、上辺 |

| TX GDDRx2 Centered | GDDRX2_TX.ECLK.Centered | ECLK を用いる DDRx2 出力、出力クロックエッジはデータの中央にある      | 640U と 1200/U これ以上の<br>デバイス、上辺 |

| TX GDDRx4 Aligned  | GDDRX4_TX.ECLK.Aligned  | ECLK を用いる DDRx4 出力、データは<br>出力クロックのエッジと揃っている | 640U と 1200/U これ以上の<br>デバイス、上辺 |

| TX GDDRx4 Centered | GDDRX4_TX.ECLK.Centered | ECLK を用いる DDRx4 出力、出力クロックエッジはデータの中央にある      | 640U と 1200/U これ以上の<br>デバイス、上辺 |

| TX GDDR71          | GDDR71_TX.ECLK.7:1      | ECLK を用いる GDDR 7:1 出力                       | 640U と 1200/U これ以上の<br>デバイス、上辺 |

### 高速 GDDR インターフェイスの詳細

本セクションでは、使用されるクロッキングも含めて各汎用高速インターフェイスについて詳細に説明します。MachXO2 のクロッキング構造の詳細については、TN1199 "MachXO2 sysCLOCK PLL Design and Usage Guide" を参照してください。表 11-2 に示すように、各インターフェイスは MachXO2 デバイスの特定バンクで対応します。これらのインターフェイスを問題なく構築するためには、それぞれのインターフェイスに関するアーキテクチャならびにインターフェイスの規則、さらに設計制約に従うことが重要です。本ドキュメントの "DDR ソフトウェアのプリミティブとアトリビュート"に、各コンポーネントについて説明されています。

## 受信インターフェイス

Lattice IPexpress ™ ソフトウェアでは、8 種の定義済み受信インターフェイスがサポートされています。

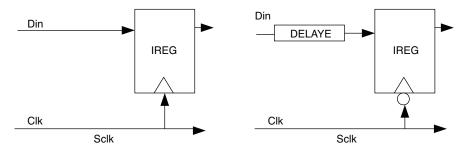

## GIREG RX.SCLK

これはシングルデータレート(SDR)のための汎用インターフェイスです。実装には基本 PIO セル(図 11-1)内の標準 I/O レジスタが使用されます。オプションのインバータを使用して、クロック信号を入力データの中央に合わせることもできます。或いは PLL または DLL を利用して、クロック注入遅延を補償することや、セットアップタイムとホールドタイムを調整することもできます。アーキテクチャ的に DLL 数が限られているため、場合によってはこれらを高速インターフェイス用に確保しておく必要があります。本インターフェイスは IPexpress で生成後に I/O レジスタエレメントをインスタンスするか、論理合成ツールに推論させることで構築できます。

### 図 11-9. GIREG\_RX インターフェイス

入力データパスの遅延セルはインターフェイスの Din パスに使用できます。DELAYE エレメントは固定遅延を与えることで、SCLK の注入遅延に合わせます。このインターフェイスでは動的入力遅延の DELAYD を使用できません。図 11-9 に本インターフェイスであり得る実装例を示します。

## インターフェイス規則:

・ クロックソースとして必ず専用のクロックピン PCLK を使用すること

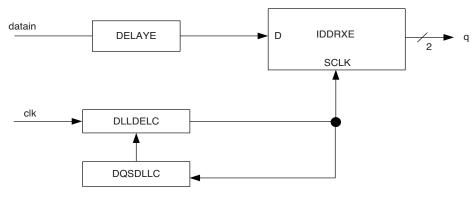

#### GDDRX1\_RX.SCLK.Aligned

本 DDR インターフェイスでは、DQSDLL を用いてクロックを 90° 位相シフトさせ、IDDRXE の SCLK ポートでクロックエッジをデータの中央に合わせます。あるいは、DQSDLL の代わりに PLL を使用して同じクロックシフト機能を行うこともできます。DELAYE エレメントで、SCLK のクロック注入時間にデータ遅延を調整します。x1 インターフェイスで DELAYD は使用できません。

## 図 11-10. DQSDLL を使用した GDDRX1\_RX.SCLK.Aligned インターフェイス

## インターフェイス規則:

- ・DLLDELC のクロックソースとして、必ず専用のクロックピン PCLK を使用すること

- ・本インターフェイスで PLL を使用する場合、専用のデュアルファンクション PLL クロックピンを使用することも可能

- ・DLL または PLL 出力を SCLK ポートに接続する場合、必ずプライマリ・クロックネットを使用すること

- ・最良のタイミングを得るために、DELAYE 値を SCLK\_ALIGNED に設定すること

- ・ DQSDLLC や PLL はデバイスあたり最大 2 つのため、インターフェイスのクロック周波数もデバイスあたり最大 2 つに制限される

### GDDRX1\_RX.SCLK.Centered

本 DDR インターフェイスでは、DELAYE を用いて、IDDRXE ポートで SCLK 遅延に整合させます。x1 インターフェイスで DELAYD は使用できません。センター・インターフェイスではクロックエッジが既にデータの中央に合わせられていますので、クロックを位相シフトするためのロジックは不要です。

#### 図 11-11. GDDRX1\_RX.SCLK.Centered

## インターフェイス規則:

- ・ クロックソースとして必ず専用のクロックピン PCLK を使用すること

- ・最良のタイミングを得るために、DELAYE 値を SCLK\_CENTERED に設定すること

- · SCLK の接続は必ずプライマリ・クロックネットを使用すること

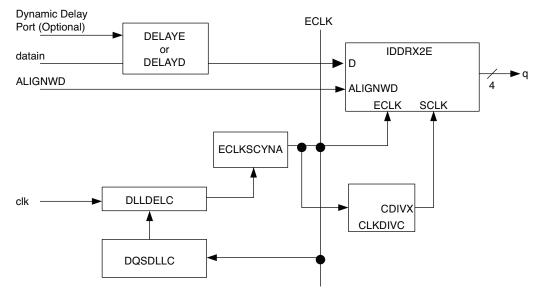

#### GDDRX2 RX.ECLK.Aligned

本 DDR x2 インターフェイスでは、DQSDLL を用いてクロックを 90° 位相シフトさせ、IDDRX2E の SCLK ポートでクロックエッジをデータの中央に合わせます。DELAYEを使用してデータを遅延させることでECLK の注入遅延に整合させますが、DELAYD を使用して遅延を動的に制御することもできます。このインターフェイスは、IDDRX2E エレメントによる x2 ギアリングを利用しているため、CLKDIVC を使用して周波数が ECLK の半分の SCLK を生成する必要があります。ECLKSYNCA エレメントは ECLK に関連づけられているブロックで、ECLK をドライブするために必ず使用する必要があります。インターフェイスでのワードアライメント用に ALIGNWD ポートが使用できます。

## 図 11-12. GDDRX2\_RX.ECLK.Aligned インターフェイス

- ・ DLLDELC のクロックソースとして必ず専用のクロックピン PCLK を使用すること

- · SCLK の接続は必ずプライマリ・クロックネットを使用すること

- ・ DQSDLLC はデバイス当たり最大2つのため、クロック周波数もデバイスあたり最大で2つに制限される

- ・ DELAYE は ECLK\_ALIGNED に設定すること

- · DELAYD を使用する場合、バス全体で1つの動的遅延ポートのみが必要

・本インターフェイスは MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの下辺でのみサポート

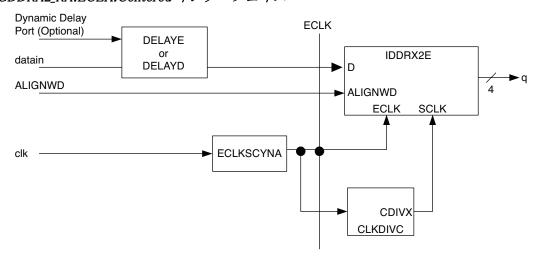

## GDDRX2\_RX.ECLK.Centered

本 DDR x2 インターフェイスでは、DELAYE または DELAYD を用いてデータを遅延させ、IDDRX2E ポートで ECLK の遅延に整合させます。このインターフェイスはエッジクロック・ネットワークを用いるため、デバイスの一辺全体にわたる広いデータバス幅に対応するように拡張できます。本インターフェイスは、IDDRX2D エレメントによる x2 ギアリングを用いるため、CLKDIVC で周波数が ECLK の半分の SCLK を生成する必要があります。インターフェイスでのワードアライメント用に ALIGNWD ポートが使用できます。

## 図 11-13. GDDRX2\_RX.ECLK.Centered インターフェイス

- ・ ECLKSYNCA のクロックソースとして、必ず専用のクロックピン PCLK を使用すること

- · SCLK の接続は必ずプライマリ・クロックネットを使用すること

- ・ DELAYE は ECLK CENTERED に設定すること

- ・ DELAYD を使用する場合、バス全体で1つの動的遅延ポートのみが必要

- ・本インターフェイスは MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの下辺でのみサポート

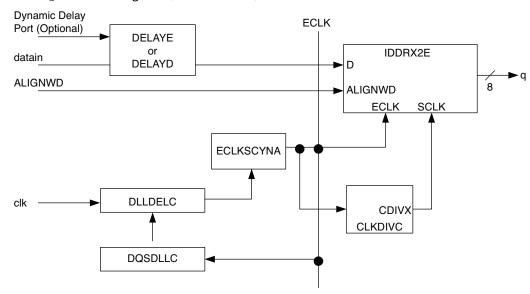

#### GDDRX4\_RX.ECLK.Aligned

本 DDR x4 インターフェイスは、DQSDLL を用いてクロックを 90° 位相シフトさせ、IDDRX4B ポートで ECLK エッジをデータの中央に合わせます。DELAYE でデータを遅延させ、ECLK の注入遅延に整合させますが、DELAYD を用いて遅延を動的に制御することもできます。このインターフェイスではエッジクロック・ネットワークを使用するため、デバイスの一辺全体にわたる広いデータバス幅に対応するように拡張できます。本インターフェイスでは IDDRX4B エレメントによる x4 ギアリングを用いるため、CLKDIVC で周波数が ECLK の 1/4 の SCLK を生成する必要があります。ECLKSYNCA エレメントは ECLK に関連づけられているブロックで、ECLK をドライブするために必ず使用する必要があります。インターフェイスでのワードアライメント用に ALIGNWD ポートが使用できます。

### 図 11-14. GDDRX4 RX.ECLK.Aligned インターフェイス

- ・ DLLDELC のクロックソースとして必ず専用のクロックピン PCLK を使用すること

- · SCLK の接続は必ずプライマリ・クロックネットを使用すること

- ・DQSDLLC はデバイスあたり最大で2つのため、クロック周波数もデバイスあたり最大で2つに制限される

- ・x4 ギアリングには、データ入力に必ず I/O ロジックセルの A/B ペアを使用すること

- ・ DELAYE は ECLK ALIGNED に設定すること

- · DELAYD を使用する場合、バス全体で1つの動的遅延ポートのみが必要

- ・本インターフェイスは MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの下辺でのみサポート

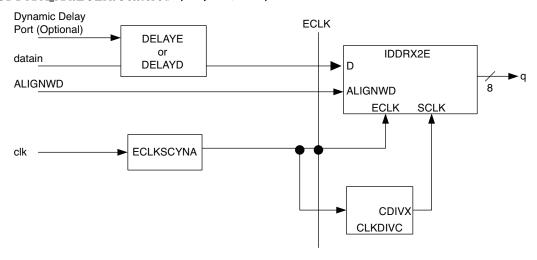

### GDDRX4\_RX.ECLK.Centered

本 DDR x4 インターフェイスは、DELAYE または DELAYD を用いてデータを遅延させ、IDDRX4B ポートで ECLK の遅延に整合させます。このインターフェイスはエッジクロック・ネットワークを使用しているため、デバイスの一辺全体にわたる広いデータバス幅に対応するように拡張できます。本インターフェイスは、IDDRX4B エレメントによる x4 ギアリングを用いるため、CLKDIVC で周波数が ECLK の 1/4 の SCLK を生成する必要があります。インターフェイスでのワードアライメント用に ALIGNWD ポートが使用できます。

#### 図 11-15. GDDRX4\_RX.ECLK.Centered インターフェイス

- ・ ECLKSYNCA のクロックソースとして、必ず専用のクロックピン PCLK を使用すること

- · SCLK の接続は必ずプライマリ・クロックネットを使用すること

- ・x4 ギアリングには、データ入力は必ず I/O ロジックセルの A/B ペアを使用すること

- ・ DELAYE は ECLK\_CENTERED に設定すること

- · DELAYD を使用する場合、バス全体で1つの動的遅延ポートのみが必要

- ・本インターフェイスは MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの下辺でのみサポート

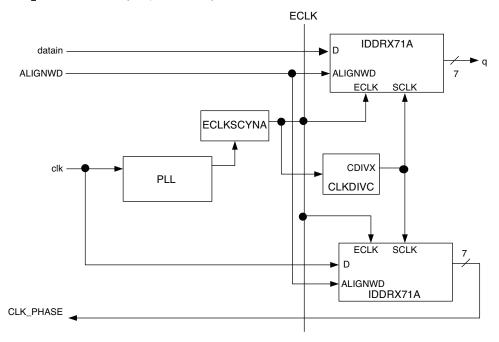

#### GDDR71\_RX.ECLK.7:1

GDDR 7:1 受信インターフェイスは、サポートする高速 DDR インターフェイスの中でも特異です。ここではビットアライメント処理において、PLL を用いてデータポジションに対して最良のクロックエッジをサーチします。PLL には 16 通りの位相ステップが設定できますので DDR の場合データ当たり 8 点のサンプリングポイントを提供します。本インターフェイスでは、データパス遅延は使用しません。1:7 デシリアライズ要件に従い、CLKDIVC を使用して ECLK を 3.5 分周します。即ち SCLK は、入力データレートに対して 7 分の一で動作するということです。 ECLKSYNCA エレメントは ECLK に関連するブロックで、ECLK のドライブに必ず使用しなければなりません。完全な 7:1 LVDS ビデオディスプレイ・アプリケーションを実現するためには、ハードマクロで組み込み済みの I/O ギアリングとアライメント・ロジックに加え、FPGA リソースでビットアライメントとワードアライメントを構築する必要があります。そのために CLK\_PHASE 信号がFPGA 側に転送されます。

### 図 11-16. GDDR71\_RX.ECLK.7:1 インターフェイス

- ・PLL のクロックソースとして、必ず下辺の専用クロックピン PCLK を使用すること

- · SCLK の接続は必ずプライマリ・クロックネットを使用すること

- ・PLLはデバイスあたり最大で2つのため、クロック周波数もデバイスあたり最大で2系統に制限される

- ・7:1 ギアリングには、データ入力は必ず I/O ロジックセルの A/B ペアを使用すること

- ・本インターフェイスは MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの下辺でのみサポート

### 送信インターフェイス

Lattice IPexpress ソフトウェアにより、8 種の送信インターフェイスがあらかじめ規定され、サポートされています。

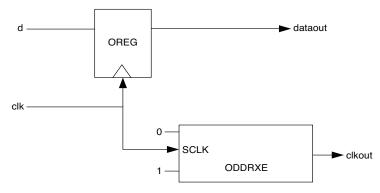

### GOREG TX.SCLK

これは SDR データとフォワードクロックのための汎用インターフェイスです。基本 PIO セル内の標準レジスタを使用して、このインターフェイスを実装します。クロック出力に ODDRXE を使用して、クロックパスとデータパスを整合させます。また ODDRXE からのクロック出力として、PLL を使用して位相シフトしたクロック信号を用いることで、データ出力に対して正確なクロック位相とすることもできます。各デバイス搭載の PLL 数が限られるため、場合によってはこれらを高速インターフェイス用に確保しておく必要があります。本インターフェイスは、IPexpress による生成か、I/O レジスタ・エレメントのインスタンス化、あるいは論理合成ツールによる推論によって構築することができます。

## 図 11-17. GOREG\_TX.SCLK インターフェイス

#### インターフェイス規則:

· SCLK の接続は必ずプライマリ・クロックネットを用いること

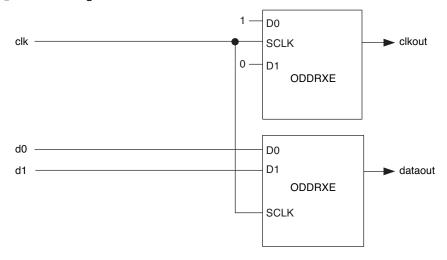

### GDDRX1 TX.SCLK.Aligned

この出力 DDR インターフェイスは、1本の SCLK を使用してエッジアラインされたクロック信号とデータ出力です。クロック出力用に ODDRXE を使用して、クロックパスとデータパスとを整合させます。

#### 図 11-18. GDDRX1\_TX.SCLK.Aligned インターフェイス

#### インターフェイス規則:

· SCLK の接続は必ずプライマリ・クロックネットを用いること

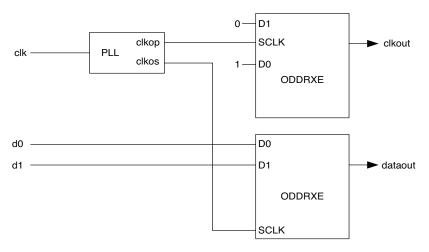

#### GDDRX1\_TX.SCLK.Centered

この出力 DDR インターフェイスは、データの中央にクロックエッジがあるクロックとデータの出力です。 PLL は clkop と clkos ポートを使用して、データとクロック間に  $90^\circ$  の位相差を与えます。出力データの I/O セルと出力クロックの I/O セルをドライブするためには、2本の SCLK リソースが必要です。

## 図 11-19. GDDRX1\_TX.SCLK.Centered インターフェイス

### インターフェイス規則:

· SCLK と 90° 位相シフトした SCLK は必ずプライマリ・クロックネットを用いること

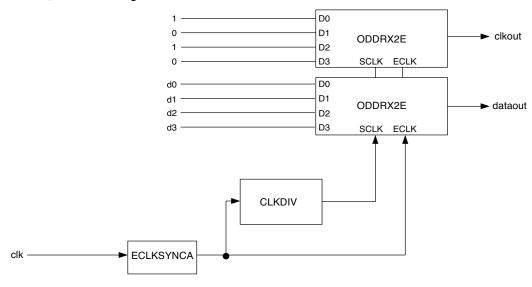

## GDDRX2\_TX.ECLK.Aligned

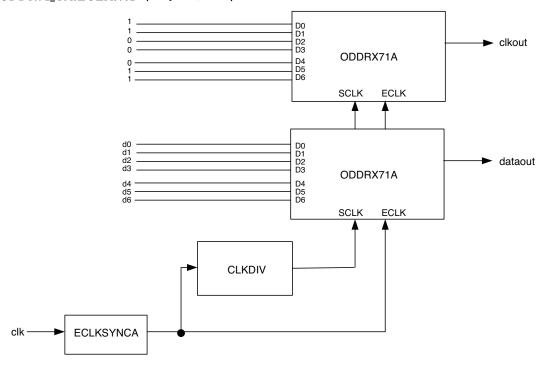

この出力 DDR x2 インターフェイスは、エッジアラインされたクロック信号とデータを出力します。CLKDIV を使用して周波数が ECLK の半分の SCLK を生成します。また ECLK パスに対して ECLKSYNC エレメントを使用し、データ同期を実行します。

## 図 11-20. GDDRX2\_TX.ECLK.Aligned インターフェイス

- · ECLK の接続は必ずエッジクロック・ネットワークを使用すること

- · SCLK の接続は必ずプライマリ・クロックネットを使用すること

- ・本インターフェイスは MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの上辺でのみサポート

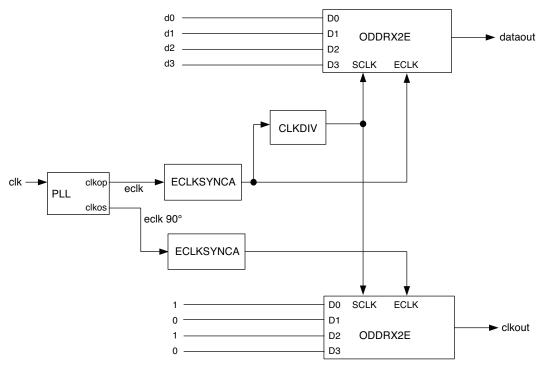

### GDDRX2\_TX.ECLK.Centered

この出力 DDR x2 インターフェイスは、データ開口の中央にエッジがあるクロックとデータを出力します。 PLL の clkop と clkos ポートを使用してデータとクロック間に  $90^\circ$  の位相差を与え、2 本の ECLK 配線リソースを使用して出力データと出力クロックをドライブします。また CLKDIV を使用して周波数が ECLK の半分の SCLK を生成します。

### 図 11-21. GDDRX2\_TX.ECLK.Centered インターフェイス

- · ECLK の接続は必ずエッジクロック・ネットワークを使用すること

- ・ 本インターフェイスは2本の ECLK を使用するため、一度に実装できるのは1つのバスのみ

- · SCLK の接続は必ずプライマリ・クロックネットを使用すること

- ・本インターフェイスは MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの上辺でのみサポート

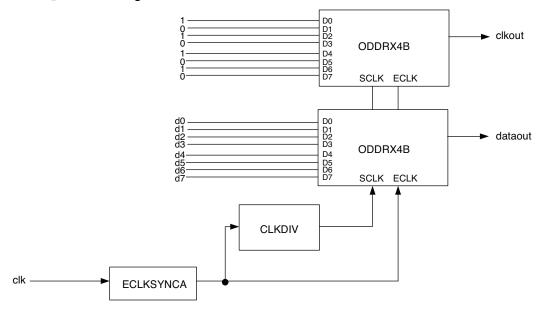

## GDDRX4\_TX.ECLK.Aligned

この出力 DDR x4 インターフェイスは、エッジアラインされたクロック信号とデータを出力します。CLKDIV を使用して周波数が ECLK の 1/4 の SCLK を生成します。また ECLK パスに対して ECLKSYNC エレメントを使用し、データ同期を実行します。

## 図 11-22. GDDRX4\_TX.ECLK.Aligned インターフェイス

- · ECLK の接続は必ずエッジクロック・ネットワークを使用すること

- · SCLK の接続は必ずプライマリ・クロックネットを使用すること

- ・x4 ギアリングには、データ出力に必ず I/O ロジックセルの A/B ペアを使用すること

- ・本インターフェイスは MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの上辺でのみサポート

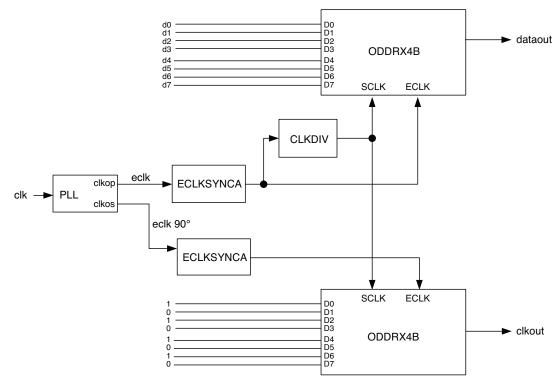

### GDDRX4\_TX.ECLK.Centered

この出力 DDR x4 インターフェイスは、データ開口の中央にエッジがあるクロックとデータを出力します。 PLL の clkop と clkos ポートを使用して、データとクロック間に  $90^\circ$  の位相差を与え、2 本の ECLK 配線リソースを使用して出力データと出力クロックをドライブします。また CLKDIV を使用して周波数が ECLK の 1/4 の SCLK を生成します。

### 図 11-23. GDDRX4\_TX.ECLK.Centered インターフェイス

- · ECLK の接続は必ずエッジクロック・ネットワークを使用すること

- ・本インターフェイスは2本のECLKを使用するため、一度に実装できるのは1つのバスのみ

- · SCLK の接続は必ずプライマリ・クロックネットを使用すること

- ・x4 ギアリングには、データ出力に必ず I/O ロジックの A/B ペアを使用すること

- ・本インターフェイスは MachXO2-640U、MachXO2-1200/U、及びこれより大規模デバイスの上辺でのみサポート

#### GDDR71\_TX.ECLK.7:1

GDDR 7:1 送信インターフェイスは、サポートされている高速 DDR インターフェイスの中でも特異です。このインターフェイスは特定パターンを使用し、ピクセルクロックと呼ぶ出力クロックを生成します。CLKDIVC を使用して、7:1 シリアライズ要件に基づいて ECLK を 3.5 分周します。即ち SCLK は送信データレートより 7 分の一の周波数で動作するということです。ECLKSYNCA エレメントは ECLK に関連するブロックで、ECLK をドライブするために必ず使用しなければなりません。

### 図 11-24. GDDR71\_TX.ECLK.7:1 インターフェイス

#### インターフェイス規則:

- · ECLK の接続は必ずエッジクロック・ネットワークを使用すること

- · SCLK の接続は必ずプライマリ・クロックネットを使用すること

- ・7:1 ギアリングには、データ出力に必ず I/O ロジックの A/B ペアを使用すること

- ・本インターフェイスは MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの上辺でのみサポート

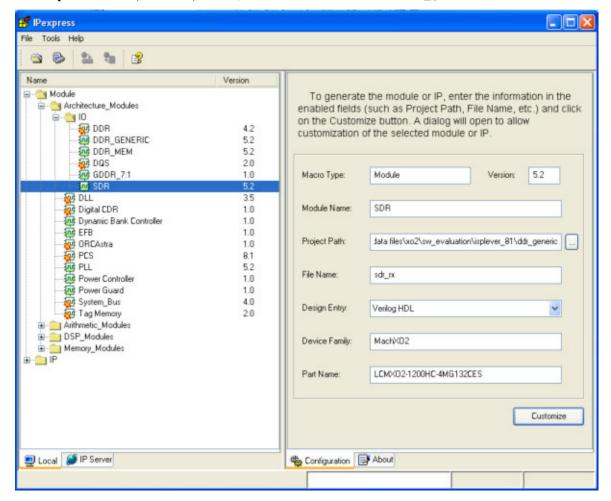

# IPexpress を使用した汎用高速 DDR インターフェイスの構築

上記の汎用高速インターフェイスは全て、Lattice 設計ソフトウェアの IPexpress ツールを使用して、パラメータ設定ならびに生成をおこないます。 IPexpress は各インターフェイスのクロッキング要件を含む HDL モジュールー式を生成します。 IPexpress の GUI では全ての DDR モジュールが **Architecture Modules > IO** に配置されています。 このセクションでは、 IPexpress の SDR と DDR\_GENERIC、 及び GDDR\_71 インターフェイスについて説明します。

表 11-3 は IPexpress モジュールで使用される信号名を示します。各信号は全てのインターフェイス、あるいは特定のインターフェイスで用いられます。信号は GDDR 受信インターフェイスと送信インターフェイスで別々にリストされています。

## 表 11-3. IPexpress モジュールで使用される信号名

| 信号名                | 方向   | 記述                                                                                                   | サポートする<br>インターフェイス |

|--------------------|------|------------------------------------------------------------------------------------------------------|--------------------|

| 受信インター             | フェイス |                                                                                                      |                    |

| clk                | 入力   | ソースシンクロナス・クロック                                                                                       | 全て                 |

| reset              | 入力   | インターフェイスへの非同期リセット、High アクティブ                                                                         | 全て                 |

| datain             | 入力   | Rx インターフェイスでのシリアルデータ入力                                                                               | 全て                 |

| uddentln           | 入力   | 遅延コードのホールド / アップデート制御、Low アクティブ (DQSDLLC の DQSDEL 出力は、UDDCNTLN が Low の時に PTV バラ つきに依存してアップデートされる)    | x1, x2, x4 アライン    |

| freeze             | 入力   | DLL をフリーズ、またはリリース。High アクティブ(High の時、遅延値が維持されている間は DLL をフリーズして電力消費を節約する。Low の時は DLL が動作を再開するように解放する) | x1, x2, x4 アライン    |

| alignwd            | 入力   | ワードアライメント制御信号、High アクティブ<br>(ALIGNWD は ECLK ドメインに対して非同期でも可。最低 ECLK の 2<br>サイクル分以上の幅である必要がある)         | x2, x4, 7:1        |

| dqsdll_reset       | 入力   | 非同期 DQSDLL リセット、High アクティブ                                                                           | x2, x4 アライン        |

| clk_s <sup>1</sup> | 入力   | リセット同期用の低速クロック<br>(このクロックは ECLK よりも低速であること)                                                          | x2, x4, 7:1        |

| init               | 入力   | リセット同期を初期化、High アクティブ                                                                                | x2, x4, 7:1        |

| phase_dir          | 入力   | ダイナミック位相調整の方向(位相シフトは Low の時は 1 ステップ<br>遅らせられ、High の時は 1 ステップ進ませられる)                                  | 7:1                |

| phase_step         | 入力   | ダイナミック位相調整のステップ<br>(ステップごとに 45 度シフト。アクティブ Low)                                                       | 7:1                |

| sclk               | 出力   | FPGA ファブリックへのシステムクロック                                                                                | 全て                 |

| q                  | 出力   | Rx インターフェイスのパラレルデータ出力                                                                                | 全て                 |

| lock               | 出力   | DLL / PLL ロック                                                                                        | x2, x4, 7:1        |

| eclk               | 出力   | 入力クロックから生成されたエッジクロック                                                                                 | x2, x4 アライン, 7:1   |

| rx_ready           | 出力   | リセット同期完了を示す                                                                                          | x2, x4, 7:1        |

| clk_phase          | 出力   | 入力クロック位相の7ビット表記<br>(ビットアライメント用論理回路のために用いられる)                                                         | 7:1                |

| 送信インター             | フェイス |                                                                                                      |                    |

| clk                | 入力   | Tx インターフェイスへの主入力クロック                                                                                 | 全て                 |

| reset              | 入力   | インターフェイスへの非同期リセット、High アクティブ                                                                         | 全て                 |

| dataout            | 入力   | Tx インターフェイスへのパラレル入力データ                                                                               | 全て                 |

| clk_s <sup>1</sup> | 入力   | リセット同期用の低速クロック<br>(このクロックは ECLK よりも低速であること)                                                          | x2, x4, 7:1        |

| sclk               | 出力   | FPGA ファブリックへのシステムクロック                                                                                | 全て                 |

| dout               | 出力   | Tx インターフェイスへのシリアル出力データ                                                                               | 全て                 |

| clkout             | 出力   | ソースシンクロナス・クロック                                                                                       | 全て                 |

| tx_ready           | 出力   | リセット同期の完了を示す                                                                                         | x2, x4, 7:1        |

<sup>1.</sup> リセット同期処理用の clk\_s はどのような低速クロックでも可。 eclk より低速であること

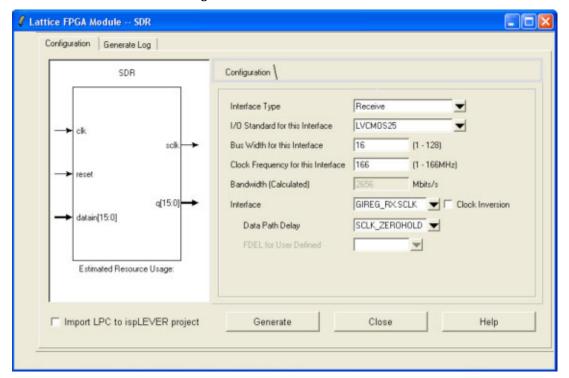

## SDR インターフェイスの構築

図 11-25 に示すように、インターフェイスタイプとして SDR を選択し、モジュール名を入力して **Customize** をクリックすると、Configuration タブが開きます。

## 図 11-25. IPexpress メインウインドウにおける SDR インターフェイスの選択

図 11-26 は IPexpress における SDR モジュールの Configuration タブを示しています。表 11-4 は SDR モジュールで利用できる様々なコンフィグレーション・パラメータを示しています。

## 図 11-26. SDR インターフェイスの Configuration タブ

## 表 11-4. SDR インターフェイスの GUI オプション

| GUI オプション                             | 説明                                                       | 値・範囲                                              | デフォルト値        |

|---------------------------------------|----------------------------------------------------------|---------------------------------------------------|---------------|

| Interface Type                        | インターフェイスタイプ                                              | Transmit, Receive                                 | Receive       |

| I/O Standard for this interface       | 本インターフェイスの I/O 規格                                        | 選択したタイプごとに、全<br>ての I/O をサポート                      | LVCMOS25      |

| Bus Width for this Interface          | インターフェイスのバス幅                                             | $1 \sim 128$                                      | 16            |

| Clock Frequency for this<br>Interface | インターフェイスの動作速度                                            | 1 ~ 378MHz(HP 品)<br>1 ~ 210MHz(LP 品)              | 166MHz        |

| Interface Bandwidth (calculated)      | 入力されたクロック周波数から算出                                         | (算出)                                              | (算出)          |

| Interface                             | それまでの入力に基づいて選択された<br>インターフェイス                            | Transmit: GOREG_TX.SCLK<br>Receive: GIREG_RX.SCLK | GIREG_RX.SCLK |

| Clock Inversion                       | I/O レジスタに対してクロック入力を<br>反転させるオプション                        | DISABLED, ENABLED                                 | DISABLED      |

| Data Path Delay                       | データ入力を DELAY ブロックを用い<br>て任意に遅延                           | Bypass, SCLK_ZEROHOLD,<br>User Defined            | Bypass        |

| FDEL for User Defined                 | 上記で User Defined が選択された遅延<br>タイプの場合、このパラメータで遅延<br>値を入力可能 | Delay0 ∼ Delay31                                  | Delay0        |

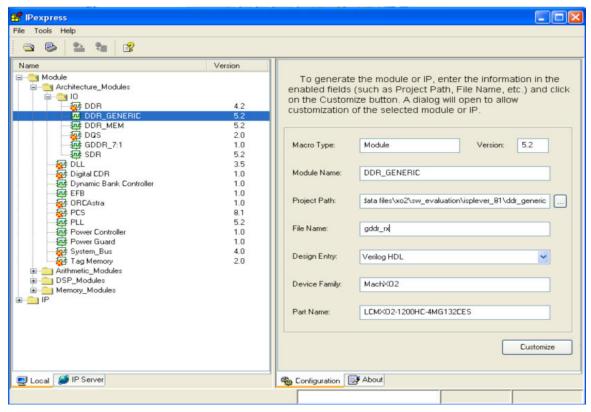

## 汎用 DDR (DDR Generic) インターフェイスの構築

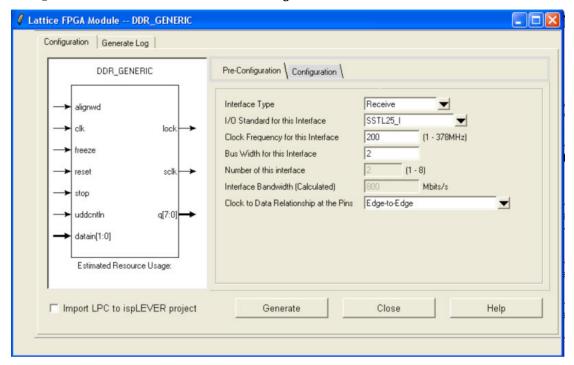

図 11-27, に示すように、インターフェイスタイプ DDR\_Generic を選択し、モジュール名を入力して **Customize** をクリックすると、Configuration タブが開きます。

DDR\_Generic インターフェイスには Pre-Configuration タブと Configuration タブがあります。Pre-Configuration タブで構築するインターフェイスタイプに関する情報を入力できます。その入力に基づいて、Configuration タブには最適なインターフェイスが自動的に選択されます。必要であればパラメータを書き換えて、設計要件に応じてインターフェイスをカスタマイズできます。図 11-28 は IPexpress における DDR\_Generic モジュールの 2 つのタブを示しています。表 11-5 と 11-6 は、DDR\_Generic モジュールで利用可能な様々なコンフィグレーション・パラメータを示します。

## 図 11-28. DDR\_Generic インターフェイスの Pre-Configuration タブ

表 11-5. DDR\_Generic モジュール、Pre-Configuration タブの GUI オプション

| GUI オプション                              | 説明                       | 範囲                                   | デフォルト値   |

|----------------------------------------|--------------------------|--------------------------------------|----------|

| Interface Type                         | インターフェイスタイプ              | Transmit, Receive                    | 注 1      |

| I/O Standard for this interface        | このインターフェイスの I/O 規格       | 選択したタイプごとに、全て<br>の I/O タイプをサポート      | LVCMOS25 |

| Clock Frequency for this<br>Interface  | インターフェイスの動作速度            | 1 ~ 378MHz(HP 品)<br>1 ~ 210MHz(LP 品) | 注 1      |

| Bus Width for this Interface           | インターフェイスのバス幅             | 選択したインターフェイスに<br>応じて種々               | 注 1      |

| Number of this Interface               | サポートされる最大バス数             | (算出)                                 | (算出)     |

| Interface Bandwidth (calculated)       | 入力されたクロック周波数とバス幅<br>から算出 | (算出)                                 | (算出)     |

| Clock to Data Relationship at the Pins | 外部インターフェイスのタイプを選<br>択    | Edge-to-Edge, Centered               | 注 1      |

<sup>1.</sup> Pre-Configuration タブの全フィールドは、デフォルトでは空白

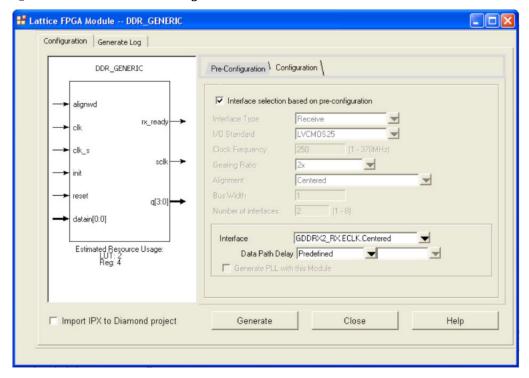

## 図 11-29. DDR\_Generic モジュールの Configuration タブ

Pre-Configuration タブの選択内容に基づいて、Configuration タブは図 11-30 で示すように各フィールド内が自動的に埋められます。このタブの一番上のチェックボックスは、このインターフェイスが Pre-Configuration タブの入力に基づいて選択されていることを示しています。ユーザはこの入力を無効にして値を変更できます。IPexpress は Pre-Configuration タブで選択された入力に基づいて、最適なインターフェイスを選択していることに留意してください。

## 表 11-6. DDR Generic モジュール、Configuration タブの GUI オプション

| GUI オプション                                             | 説明                                                                                           | 範囲                                        | デフォルト値                 |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------|------------------------|

| Interface Selection<br>based on pre-<br>configuration | Pre-configuration タブの選択に基づいてインターフェイスが選択されたことを示す。このチェックボックスを無効にすることで、ユーザはギアリング比や遅延タイプなどを選択できる | ENABLED,<br>DISABLED                      | ENABLED                |

| Interface Type                                        | インターフェイスのタイプ                                                                                 | Transmit, Receive                         | Receive                |

| I/O Standard                                          | このインターフェイスの I/O 規格                                                                           | 選択したタイプに応じ<br>た全ての I/O タイプ                | LVCMOS25               |

| Clock Frequency                                       | インターフェイスの動作速度                                                                                | 1 ~ 378 MHz(HP品)<br>1 ~ 266 MHz(LP品)      | 200MHz<br>100MHz       |

| Gearing Ratio                                         | インターフェイスのギアリング比を選択                                                                           | x1, x2, x4                                | x1                     |

| Alignment                                             | 外部インターフェイスのタイプを決定                                                                            | Edge-to-Edge, Centered                    | Edge-to-Edge           |

| Bus Width                                             | インターフェイスのバス幅                                                                                 | $1 \sim 128$                              | 4                      |

| Number of Interfaces                                  | サポートされる最大バス数                                                                                 | 1~8                                       | (算出)                   |

| Interface                                             | サポートされる GDDR インターフェイス<br>のリスト                                                                | 選択したギアリング比<br>とアライメントに依存<br>する            | GDDRX1_RX.SCLK.Aligned |

| Data Path Delay <sup>1</sup>                          | DELAY ブロックを用いてデータ入力を任<br>意に遅延可能                                                              | Bypass, Predefined, User defined, Dynamic | Predefined             |

| Generate PLL with this Module <sup>2</sup>            | このモジュールで PLL を生成するかしな<br>いかのオプション                                                            | Enabled, Disabled                         | Enabled                |

<sup>1.</sup> User Defined が選択されると、遅延値フィールドがイネーブルになり、ユーザは遅延値を 0 から 31 の範囲で選択できる。Dynamic が選択されると、モジュールに 5 ビットのポートが追加される。Dynamic が使用できるのは x2 と x4 受信インターフェイスのみ

Pre-Configuration タブが使用されると、インターフェイスのギアリング比はインターフェイスの速度により 決定されます。表 11-7 にギアリング比がどのように選択されるかを示します。

表 11-7. ソフトウェアによるギアリング比の選択

| デバイスタイプ         | インターフェイス速度            | ギアリング比 |

|-----------------|-----------------------|--------|

|                 | =< 166MHz             | x1     |

| 高性能 (HP) デバイス   | > 166MHz かつ =< 266MHz | x2     |

|                 | > 266MHz              | x4     |

|                 | =< 70MHz              | x1     |

| 低消費電力 (LP) デバイス | >70MHz かつ =< 133MHz   | x2     |

|                 | >133MHz               | x4     |

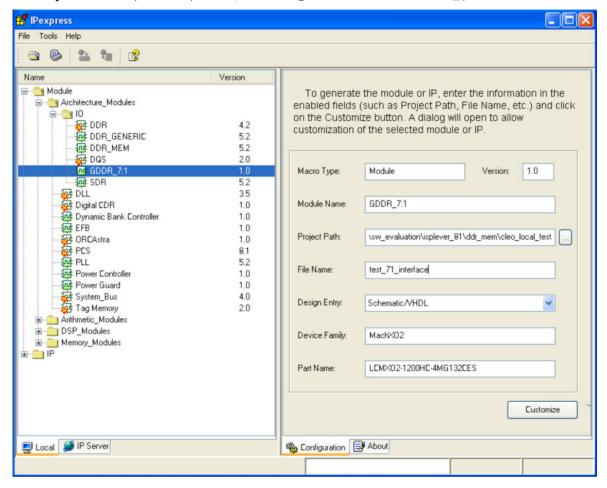

## 汎用 DDR 7:1 インターフェイスの構築

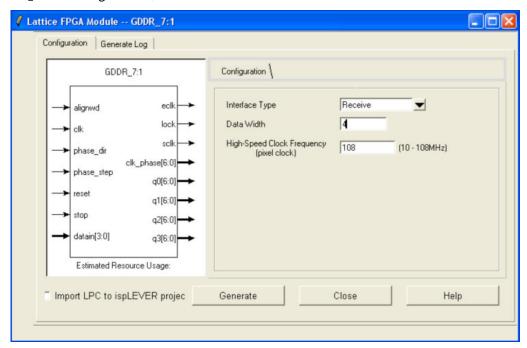

図 11-30, に示すように、インターフェイスタイプ GDDR\_71 を選択し、モジュール名を入力して **Customize** をクリックすると、Configuration タブが開きます。このセクションでは Configuration タブの GUI ユーザパラメータを説明します。DDR 7:1 インターフェイスは、特有のアプリケーションなので、GUI オプションは比較的シンプルです。必要なロジックのほとんどがソフトウェアに組み込まれ、使いやすくなっています。

<sup>2.</sup> 本オプションは PLL を用いるインターフェイスのみで、GDDRX1\_RX.SCLK.Aligned や GDDRX1\_TX.SCLK.Centered、GDDRX2\_TX.ECLK.Centered、及び GDDRX4\_TX.ECLK.Centered が含まれる

## 図 11-30. IPexpress メインウインドウにおける GDDR\_71 インターフェイスの選択

図 11-31. GDDR 71 の Configuration タブ

## 表 11-8. GDDR\_71、Configuration "タブの GUI オプション

| GUI オプション                                | 説明                                 | 範囲                   | デフォルト値  |

|------------------------------------------|------------------------------------|----------------------|---------|

| Interface Type                           | ンターフェイスのタイプ                        | Transmit,<br>Receive | Receive |

| Data Width                               | 入力されるチャネル数                         | $1 \sim 16$          | 4       |

| High Speed Clock Frequency (Pixel Clock) | 7:1 LVDS インターフェイスのピクセル・<br>クロック周波数 | 10 ~ 108             | 108     |

## 汎用高速 DDR の設計ガイドライン

## I/O ロジックセルとギアリングロジック

それぞれのプログラマブル IO セル (PIC) には、4つのプログラマブル I/O (PIO) があり、2組の I/O バッファペアを形成します。A PIO 自体は x1 ギアリング比に対応します。A/B や C/D の PIO ペアはいずれも x2ギアリング比に対応できます。x4か7:1ギアリング比のサポートにはPICブロック 1つの 4 PIO すべてが必要です。パッケージに A/B ペアのピンが C/D ピンと独立して用意されているときのみ、x4 と 7:1 ギアリング比に対応することができます。特定のパッケージで利用できる x2 インターフェイスの総数は、A/B ペアと C/D ペアの総数によって決定されます。特定のパッケージで利用できる x4 や 7:1 インターフェイスの総数は、A/B ペアの総数によって決定されます。

### 表 11-9. I/O ロジックセルのミクストモードでサポートされるギアリングロジック

|                      | I/O ロジック A                | I/O ロジック B                | I/O ロジック C                | I/O ロジック D                |

|----------------------|---------------------------|---------------------------|---------------------------|---------------------------|

| x2 ギアリング (A/B<br>ペア) | IDDRX2 又は ODDRX2          | 非該当                       | 基本 I/O レジスタ又は<br>x1 ギアリング | 基本 I/O レジスタ又は<br>xl ギアリング |

| x2 ギアリング<br>(C/D ペア) | 基本 I/O レジスタ又は x1<br>ギアリング | 基本 I/O レジスタ又は<br>x1 ギアリング | IDDRX2 又は ODDRX2          | 非該当                       |

| x4 ギアリング             | IDDRX4 又は ODDRX4          | 非該当                       | 基本 I/O レジスタ又は<br>x1 ギアリング | 基本 I/O レジスタ又は<br>x1 ギアリング |

| 7:1 ギアリング            | IDDRX71 又は ODDRX71        |                           | 基本 I/O レジスタ又は<br>x1 ギアリング | 基本 I/O レジスタ又は<br>x1 ギアリング |

## 高速 ECLK ブリッジ

高速 ECLK ブリッジは、MachXO2 デバイス内の ECLK 通信を拡張するために用いられ、主に高速ビデオ用途で利用されます。これは MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスで使用可能です。このブリッジを使用すると、クロックソースがデバイスの上辺と下辺にあるエッジクロックを低スキューでドライブできるようになります。このブリッジへの入力信号には、上辺と下辺のプライマリ・クロックピン入力と、両辺からの PLL 出力、及びクロックツリー配線が含まれます。

ECLK ブリッジには、デバイス上下辺の ECLK に 1 つずつ、計 2 つのブリッジ・マルチプレクサがあります。これらのマルチプレクサは、2 本のエッジクロック間で動的に切り替えできます。ECLK ブリッジの接続性の詳細については、TN1199 "MachXO2 sysCLOCK PLL Design and Usage Guide (MachXO2 sysCLOCK PLL 設計と使用ガイド)" を参照してください。

ECLK ブリッジは、高速 x2/x4 受信インターフェイスを除く全ての汎用高速インターフェイスでサポートします。ブリッジ機能の使用や配線用途に使用するためには、デザイン内で ECLK ブリッジ・コンポーネントをインスタンスする必要があります。

## リセット同期化要件

汎用 DDR インターフェイスは、高速アプリケーション用に最適化された複数の専用回路で構築されます。したがって、ECLK と SCLK 間のクロックドメイン転送におけるマージンを確保し、リセットパルスの様々な遅延に起因するバスのビット順が乱れることを回避するために、CLKDIV や IDDR / ODDR などの全コンポーネントを、同一の高速エッジクロックサイクルでの動作開始を確実にする必要があります。

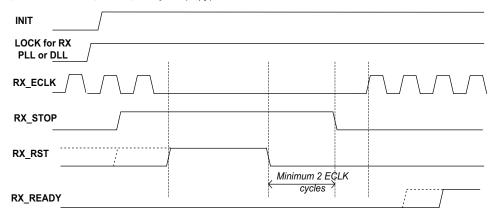

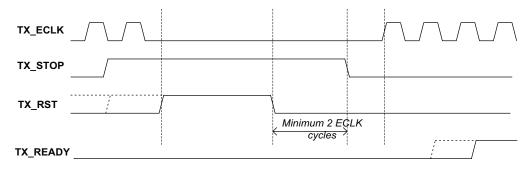

x2やx4、及び7:1ギアリングを使用したインターフェイスのシステム実装を成功させるためには、ECLKSYNCA コンポーネントと特定のリセットシーケンスが必要になります。図 11-32 と 11-33 は受信インターフェイス と送信インターフェイスのタイミング要件を示しています。図中のRX\_STOPやTX\_STOP信号は、ECLKSYNCA コンポーネントの STOPポートです。RX\_RST と TX\_RST 信号は、ODDR/IDDR や CLKDIV コンポーネントの リセットポートです。図中 RX\_ECLK および TX\_ECLK は ECLKSYNCA コンポーネントの出力です。図に示す とおり、RX\_RST から RX\_STOP までは最低でも ECLK の 2 サイクル分以上あける必要があります。受信インターフェイスのリセットプロセスが完了するまで開始されるべきではありません。最小 2 サイクルの ECLK 遅延を作り出すためのクロック信号は、ECLK より遅い周波数であれば任意のクロックを使用できます。

## 図 11-32. 受信インターフェイスのリセット同期

#### 図 11-33. 送信インターフェイスのリセット同期

これらのタイミング要件は、IPexpress で生成される際に汎用 DDR x2/x4/7:1 モジュールに組み込まれます。この場合 RX\_STOP / TX\_STOP / RX\_RST / TX\_RST / RX\_ECLK / TX\_ECLK は内部信号になります。汎用 DDR インターフェイスを IPexpress 以外で構築する場合は、リセットタイミング要件に従って、かつ RTL を記述して実装する必要があります。

## 高速 GDDR インターフェイスのタイミング解析

それぞれの高速インターフェイスでは、ユーザが STA (静的タイミング解析) を実行することをお勧めします。本セクションは、各インターフェイス・タイプに用いるタイミング制約と、期待される Trace (= タイミング解析) 結果について記述します。プリファレンス (preference、設計制約) は、プリファレンス・ファイル (.lpf) に直接記述するか、スプレッドシート・ビュー (Spreadsheet View) GUI を通して入力することができます。

本セクションと共に、MachXO2ファミリデータシートの外部スイッチング特性セクションを参照してください。データシートでは、それぞれのインターフェイスに対するこれら制約の実際の値について規定しています。

## 周波数制約

デザイン内の全入力クロックに対して、ユーザが明示的に FREQUENCY (または PERIOD) PORT 制約を指定することが必要です。ただし、クロックが PLL か DLL から生成されるか、またはクロックが PLL か DLL

に入力される場合は、必ずしもこの制約は必要ではありません。すべてのクロックピンとクロック配線要件については、本ドキュメントの『高速 GDDR インターフェイスの詳細 "セクションを参照してください。

## セットアップとホールドタイム制約

すべての受信インターフェイスでは、セットアップとホールド時間に制約を与えることができます。

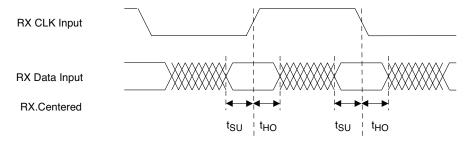

<u>受信センター・インターフェイス</u>:図 11-34 は受信センターインターフェイスでのデータとクロックの関係を示します。クロックエッジがデータの中央にあるため、これはデバイス・インタフェース点でしばしば十分なセットアップとホールドタイムを提供します。

## 図 11-34. RX.CLK.Centered レシーバ波形

ユーザはセットアップとホールドタイムの許容される値について、ソフトウェア・プリファレンスとして規定しなければなりません。これらのパラメータは  $t_{SU}$  (セットアップ時間) と  $t_{HO}$  (ホールドタイム) として図示されています。以下に示すように INPUT\_SETUP と HOLD プリファレンスを用いることで,直接それらを与えることができます。

INPUT\_SETUP PORT "Data" <tSU> ns HOLD <tHO> ns CLKPORT "CLK";

ここで、Data = データ入力ポート; CLK= クロック入力ポート

MachXO2ファミリデータシートの外部スイッチング特性セクションでは、最速周波数で動作する各高速インターフェイスで必要となる、最小セットアップ / ホールドタイムについて規定しています。最速周波数で動作しないデザインにおいては、セットアップとホールドタイム値を計算するためにソフトウェアの STA ツールを用いることができます。

例えば 250MHz で動作する GDDRX2\_RX.ECLK.Centered インターフェイスを用いる場合、制約は次のように設定できます。ソフトウェアは本インターフェイスに最小  $t_{\rm SU}$  と  $t_{\rm HO}$  値を与えます。

## INPUT\_SETUP PORT Data 0.500000 ns HOLD 0.500000 ns CLKPORT "CLK";

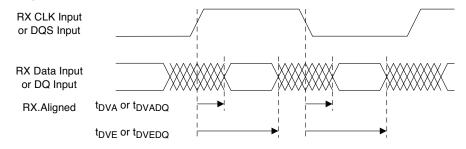

<u>受信アラインインターフェイス</u>:図11-35 は受信アライン・インターフェイスにおけるデータとクロックの関係を示します。クロックとデータはそれらのエッジが揃って(アラインされて)います。DDR メモリでは、リード動作時に同じタイミングの関係になります。

### 図 11-35. RX.CLK.Aligned および MEM DDR レシーバ入力波形

最悪ケースでは、データがクロックエッジの後に到来するかもしれず、したがってデバイス入力時に負のセットアップ時間を持つことになります。このインターフェイスでは、最悪ケースのセットアップ時間はt<sub>DVA</sub>によって規定され、これはクロックエッジ後にデータ有効になる時間です。最悪ケースのホールドタイムは

t<sub>DVE</sub> で規定され、これはクロックエッジ後のデータ保持期間です。本インターフェイスのセットアップ / ホールドタイムについては、以下のように規定することができます。

INPUT\_SETUP PORT Data <-tDVA > ns HOLD < tDVE> ns CLKPORT "CLK";

ここで、Data = データ入力ポート; CLK= クロック入力ポート

SETUP タイムには負数が用いられていますが、この場合データがクロックエッジの後に現れます。MachXO2ファミリデータシートの外部スイッチング特性セクションでは、最速周波数で動作する各高速インターフェイスで必要となる、最大  $t_{DVA}$  と最小  $t_{DVE}$  について規定しています。データシートでこの制約の規定は単位が UI (Unit Intervals) として記載されています。1UI はクロック半周期に等しくなります。したがって、実際の数値は用いられるクロックの周期から計算する必要があります。

250MHz (UI=2.0ns) で動作する GDDRX2\_RX.ECLK.Aligned インターフェイスでは、

$t_{DVA} = 0.32UI = 0.64ns$ ,  $t_{DVE} = 0.70UI = 1.4ns$

この場合の制約は以下の通りです。

INPUT SETUP PORT Data -0.640000 ns HOLD 1.400000 ns CLKPORT "CLK":

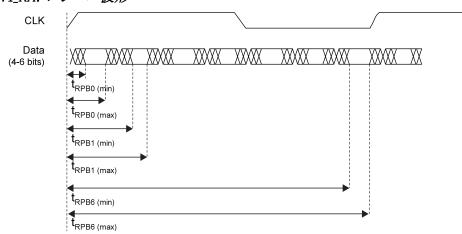

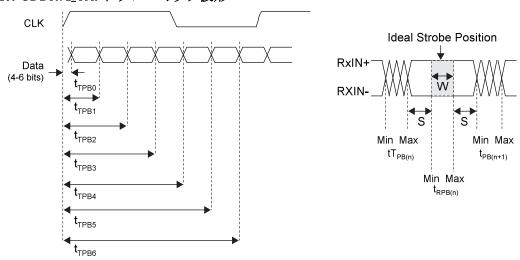

7:1 LVDS 受信インターフェイス: 7:1 LVDS インターフェイスは特異な GDDR インターフェイスで、これはピクセルクロックー周期を用いて 7 ビットデータを受信します。図 11-36 はこのインターフェイスのタイミングを示しますが、 $t_{RPBi}$  がビット "i" の入力ストローブ位置です。このインターフェイスとして、bit0 の最大セットアップタイムは  $t_{RPB0}$  min によって規定され、最小ホールドタイムが  $t_{RPB0}$  max として規定されます。本インターフェイスではbit i用の入力ストローブ位置が $t_{RPBi}$  minと $t_{RPBi}$  max内に制限されます。値はMachXO2ファミリデータシートの外部スイッチング特性セクションに記載されています。

### 図 11-36. GDDR71 RX. レシーバ波形

7:1 インターフェイスの実装には、参照デザイン RD1093 "MachXO2 ディスプレイ・インターフェイス" を用いることをお勧めします。

受信ダイナミック・インターフェイス:実動作時にクロックかデータ遅延のどちらかが動的に更新される場合は、STAがダイナミック・インターフェイス全ケースについてタイミングを解析することはありません。

## Clock-to-Out (クロックから出力) 制約

すべての送信(Tx)インターフェイスでは、デバイス端でのクロックとデータ出力との関係を検出するために clock-to-out (クロック対出力)制約を与えることができます。

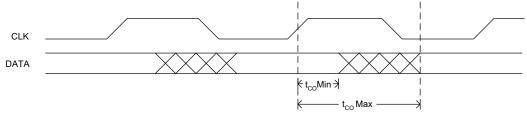

図 11-37 はソフトウェアで clock-to-out がどのように制約されるかを示します。最小  $t_{CO}$  は、クロックエッジ遷移後にデータが変化しない最小時間です。したがって、いかなるデータ遷移も  $t_{CO}$  の最小値と最大値の間で起こらなければなりません。

## 図 11-37. t<sub>CO</sub> の最小と最大タイミング解析

$t_{\rm CO}$  Min = Data cannot transition BEFORE Min  $t_{\rm CO}$  Max = Data cannot transition AFTER Max

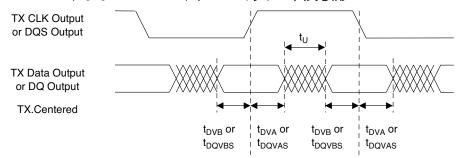

<u>送信センター・インターフェイス</u>:デバイスから出力されるとき、送信クロックエッジはデータの中央にあることが期待されています。図 11-38 は送信センター・インターフェイスのタイミングを示します。**DDR** メモリへのライト出力時には、送信センター・インターフェイスと同じタイミングの振舞いになります。

### 図 11-38. TX.CLK.Centered および MEM DDR トランスミッタの出力波形

図 11-38 で  $t_U$  はデータ遷移期間です。 $t_{DVB}$  はクロックエッジの前にデータが有効であるべき期間の最大値が  $-t_{DVB}$  であることを示します。また、クロックエッジ後のデータ有効データ(ホールドタイム)最小値  $t_{DVA}$  です。

MachXO2 ファミリデータシートは、最速周波数における  $t_{DVB}$  と  $t_{DVA}$  値について規定しています。しかし、ここでは  $t_{IJ}$  値が不明なため、以下の数式を用いることで最小  $t_{CO}$  について計算することができます。

$$t_{CO}$$

Min. =  $-(t_{DVB} + t_{U})$

$$\frac{1}{2}T = t_{DVA} + t_{DVB} + t_{U}$$

$$-(t_{DVB} + t_{U}) = t_{DVA} - \frac{1}{2}T$$

$$t_{CO}$$

Min. =  $t_{DVA} - \frac{1}{2}T$

ソフトウェアでの clock-to-out 時間は以下のように規定することができます。

CLOCK\_TO\_OUT PORT "Data" MAX <-tDVB> MIN <tDVA-1/2 Clock Period> CLKPORT "CLK" CLKOUT PORT "Clock":

ここで、Data = データ出力ポート; Clock = フォーワードクロック出力ポート; CLK = クロック入力ポート

最速時の  $t_{DVB}$  と  $t_{DVA}$  値は、MachXO2 ファミリデータシートの外部スイッチング特性セクションに記載されています。

250MHz で動作する GDDRX2\_TX.SCLK.Centered インターフェイスでは、制約は以下になります。

CLOCK\_TO\_OUT PORT "Data" MAX -0.670000 ns MIN -1.330000 ns CLKPORT "CLK" CLKOUT PORT "Clock";

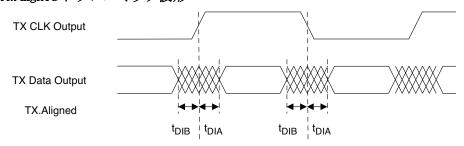

<u>送信アライン・インターフェイス</u>:この場合、デバイスから出力されるときクロックとデータはエッジが揃っています。図 11-39 は本インターフェイスのタイミング図を示します。

## 図 11-39. TX.CLK.Aligned トランスミッタ波形

図 11-39 で、t<sub>DIA</sub> はクロックエッジ後のデータが遷移期間の最大値を示します。データが遷移する最小値は -t<sub>DIB</sub> ですが、これはクロックの前でデータが無効になる値です。負数が最小値に用いられていますが、これ は最小の条件がクロックエッジの前に出現するためです。

ソフトウェアの clock-to-out 時間は以下のように規定することができます。

CLOCK\_TO\_OUT PORT "Data" MAX <tDIA> MIN <-tDIB> CLKPORT "CLK" CLKOUT PORT "Clock"; ここで、Data = データ出力ポート; Clock = フォーワードクロック出力ポート; CLK = クロック入力ポート

最速動作時の  $t_{DIA}$  と  $t_{DIB}$  値は、MachXO2 ファミリデータシートの外部スイッチング特性セクションに規定されています。

250MHz で動作する GDDRX2\_TX.Aligned インターフェイスでは、 $t_{\rm DIA}$  =  $t_{\rm DIB}$  = 0.215ns です。制約は以下の通りです。

CLOCK\_TO\_OUT PORT "Data" MAX 0.215000 ns MIN -0.215000 ns CLKPORT "CLK" CLKOUT PORT "Clock";

送信 7:1 LVDS インターフェイス: 7:1 LVDS インターフェイスは特異な GDDR インターフェイスで、これはピクセルクロックの一周期を用いて 7 ビットデータを送信します。図 11-40 は本インターフェイスのタイミングを示します。本インターフェイスでは、bit0 の送信出力パルス位置は、 $t_{TPB0}$  min と  $t_{TPB0}$  max 内に制限されます。 $t_{TPBi}$  値は、 $t_{TPBi}$  値は、 $t_{TPBi}$  値は、 $t_{TPBi}$  ではこれでいます。

## 図 11-40. GDDR71\_TX. トランスミッタ波形

## クロックドメイン転送のタイミング・ルールチェック

これらのエレメントが設計で用いられているとき、IDDR と ODDR モジュール内のクロックドメイン転送は Trace (タイミング解析) によって自動的にチェックされます。クロックドメイン転送は、高速と低速のクロック入力がある GDDR X2、X4、および 7:1 モジュールで起こります。

ソフトウェアでこのクロックドメイン転送のチェックを実行するために、どのような特別な制約も不要です。 クロックドメイン転送の確認はソフトウェアで自動的に行われ、Trace (タイミング解析) レポート内の "Timing Rule Check (タイミング・ルールチェック)" セクションで報告されます。レポートでは、クロック ドメイン転送が起こる入出力 GDDR ブロック両方でのタイミングをリストアップします。

## DDR/DDR2/LPDDR SDRAM インターフェイス概要

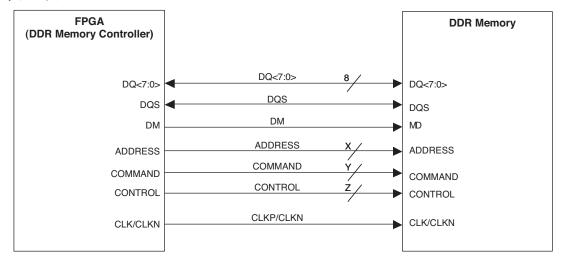

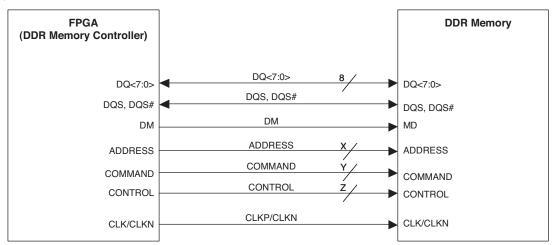

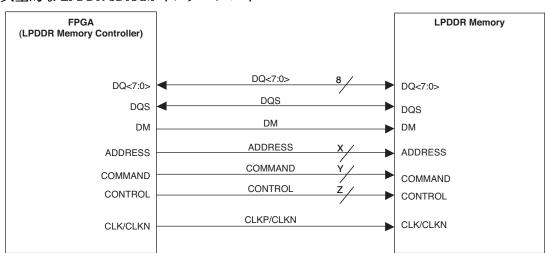

DDR SDRAM インターフェイスは、クロックの立ち上がりエッジと立ち下がりエッジの両方でデータを転送します。DDR2 は第2世代の DDR SRDRAM メモリですが、LPDDR は電池駆動アプリケーションに特化した低消費電力インターフェイスです。

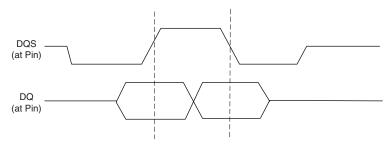

DDR と DDR2、及び LPDDR SDRAM インターフェイスは、高速動作を実現するためにデータストローブ信号である DQS を使用しています。DDR と LPDDR SDRAM インターフェイスは、シングルエンド DQS ストローブ信号を使用し、DDR2 インターフェイスには差動 DQS ストローブ信号を使用するオプションがあります。以降の図は標準的な DDR や DDR2、及び LPDDR SDRAM インターフェイス信号を示します。SDRAM インターフェイスは、通常 DQS 当たり DQ データ 8 ビットで実装されます。例えば x16 インターフェイスは 2 本の DQS 信号線を使用し、各 DQS 信号は各 8 ビットの DQ データに関連づけられます。DQ 及び DQS はともに 双方向ポートで、DDR メモリデバイスとのリード / ライトに使用されます。

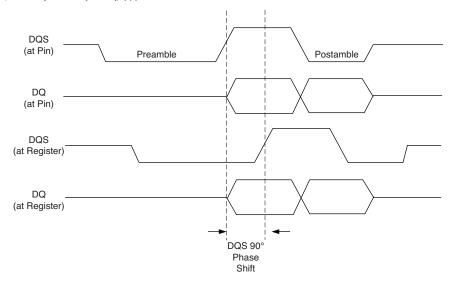

外部メモリからデータを読み出す場合、デバイスに入力されるデータは DQS 信号に対してエッジが揃っています(アライン)。この DQS ストローブ信号は、90° 位相シフトして FPGA ロジックがリードデータを取り込めるできるようにする必要があります。 DDR / DDR2 / LPDDR SDRAM にライトする場合、メモリコントローラ(FPGA)は DQS を 90° 位相シフトして出力し、エッジをデータ信号(DQ)の中央に合わせる必要があります。またクロック信号はメモリにも出力されますが、これは差動クロックとして提供され(CLKPと CLKN)、デューティ比のバラつきを最小限にします。メモリはこれらのクロック信号を使用し、メモリ内部の DLL を介してリード時の DQS 信号を生成します。LPDDR デバイスには、標準的な DDR デバイスで使用される DLL は省電力化のために存在しません。次ページの図は、リード / ライトサイクルにおける DQ とDQS のタイミング関係を示します。

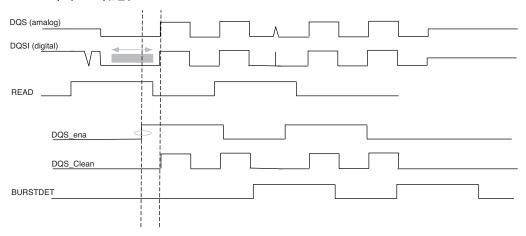

リード実行時、DQS 信号はトライステートから抜けた後しばらくは Low です。このステートを "プリアンブル (Preamble) "と呼びます。またトライステートに戻る前の DQS Low 期間を "ポストアンブル (Postamble) "ステートと呼びます。これは最後の有効データ遷移後のステートです。

また DDR SDRAM では、ライトサイクル中にデータビットをマスクするためのデータマスク (DM) 信号が必要です。DQS とデータビットとの比は、メモリ全体の幅とは独立なことに留意してください。8 ビットインターフェイスは、1 本のストローブ信号を持ちます。

DDR SDRAM インターフェイスは、I/O 規格として SSTL25 Class I/II を採用し、DDR2 SDRAM インターフェイスは SSTL18 Class I/II 規格を、そして LPDDR SDRAM インターフェイスは LVCMOS18 規格を採用しています。DDR2 はシングルエンドまたは差動 DQS のいずれかを使用できます。

以下の表と図は、DDR メモリの仕様と標準的インターフェイス、及びピンレベルの DQ と DQS の関係を示したものです。

## 表 11-10. MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの DDR / DDR2 及び LPDDR 仕様

|          | DDR                           | DDR2                                      | LPDDR                 |

|----------|-------------------------------|-------------------------------------------|-----------------------|

| データレート   | $190M \sim 300 \mathrm{Mbps}$ | $266 \mathrm{M} \sim 300 \mathrm{\ Mbps}$ | $0\sim 300 { m Mbps}$ |

| DQS      | シングルエンド                       | シングルエンド / 差動                              | シングルエンド               |

| インターフェイス | SSTL25                        | SSTL18                                    | LVCMOS18              |

| 終端       | 外付け                           | オンチップ                                     | なし                    |

## 図 11-41. 典型的な DDR SDRAM インターフェイス

図 11-42. 典型的な DDR2 SDRAM インターフェイス

図 11-43. 典型的な LPDDR SDRAM インターフェイス

### 図 11-44. リード時の DQ と DQS の関係

### 図 11-45. ライト時の DQ と DQS の関係

## DDR/DDR2/LPDDR SDRAM インターフェイスの実装

DDR メモリの概要セクションで説明したように、全ての DDR SDRAM インターフェイスは、高速動作を実現するためにデータストローブ信号である DQS を使用しています。外部メモリデバイスからデータを読み出すとき、MachXO2 デバイスに入力されるデータは DQS 信号に対してエッジが揃っています。MachXO2 は、DQSを 90°位相シフトしてリードデータの取り込みを可能にします。メモリコントローラから DDR SDRAM にデータをライトするとき、MachXO2 デバイスはデータ信号 DQ の中央にエッジを持つ DQS 信号を生成する必要があります。これは、DQ データに対して DQS ストローブ信号を 90°位相シフトすることで実現します。

MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスは、DQS を適切に位相シフトさせる専用の DQS サポート回路を備えています。この回路は汎用 DDR 回路とは別で、デバイスの右辺でのみ使用可能です。この回路はメモリインターフェイス用に x1 ギアリングを利用し、結果としてコア性能に対して 2 倍の周波数でメモリインターフェイスを動作させます。

DDR2 及び LPDDR ともに、XO2 は対デバイス接続となる実装を意図しており、従って DQ / DQS のファンアウトを 1 つにする必要があり、また CLKP / CLKN とアドレス / コマンドのファンアウトは 2 つでも可能でしょう。

DQS 位相シフト回路は専用の各 DQS ピンに関連する遅延制御信号を生成するために周波数基準 DLL (Frequency Referenced DLL) を使用し、PVT (プロセス/電圧/温度) バラつきを補正するように設計されています。周波数基準は PCLK グローバル・クロックピンの 1 本を介して与えられます。また専用の DDR サポート回路は、データサンプリング・ウインドウに対して適度で一定のマージンを与えるように設計されています。本セクションでは、DDR メモリインターフェイスのリードとライトセクションの実装方法について説明します。

## DQS グルーピング

1つの DQS グループは、通常 8 本の DQ ピンと 1 本の DM ピン、1 本の DQS ピンまたは 2 組の DQS / DQSNペア、及び 1 本の Vref ピンから構成されます。 DQS グループは DDR / DDR2、または LPDDR SDRAM インターフェイス一式を実装するために、少なくとも 11 個の I/O ロジックセルを必要とします。MachXO2-640Uと MachXO2-1200/U、及びこれより大規模のデバイスでは、DQS 信号が DQS / DQSN 用の 2 個と 12 個の I/Oセルのスパンをカバーできるように DQS-14 グループをサポートします。デバイスの右辺でサポートされるメモリ回路は、最大で DDR / DDR2 / LPDDR バスの 16 ビット幅実装を可能にします。これは 2 つの DQS グループを一緒に使用する必要があります。

各 DQS 信号は 14 I/O のスパンをカバーします。シングルエンド DQS を使用する場合、最大 13 本の 1/O スパンに対して、8 ビットの DDR メモリインターフェイスを実装できます。ユーザは DQS-14 グループ内の任意の 8 個の 1/O パッドを、DQ データピンに割り当てることができます。DQSN を使用しない場合、その DQS グループに対して DQ または DM として使用できます。MachXO2 デバイスファミリは、任意の 1/O ピンを Vref ピンとして使用できます。この結果、DQS-14 グループ構造と相まって DDR メモリインターフェイスに対するピン配置の柔軟性が高まります。DQS 及び DQS-14 グループの配置の詳細については MachXO2 ファミリデータシートを参照してください。

## DQS 回路

DQS 回路 (DQSBUF) は DDR メモリインターフェイスの実装を簡素化するように設計されています。この 回路は以下を含むいくつかの機能を統合しています。

- · DQS プリアンブル / ポストアンブル管理

- · DLL 補正された DQS の遅延

- ・ 有効データ及びデータバーストの検出

## DQS プリアンブル / ポストアンブル管理

DDR / DDR2 / LPDDR SDRAM メモリインターフェイスは、リード / ライトバーストの前後にプリアンブルとポストアンブル・ステートが必要です。プリアンブルとポストアンブル管理回路は、MachXO2 デバイスに組み込まれています。これはデバイス内部のクリーンな DQS パルスを確実にし、プリアンブル期間に内部ロジックに対して DQS を起動し、信号の最後の立ち下がりエッジ後に DQS をオフにします。デバイス内部へのクリーンな DQS で、下流のロジック回路がクロック極性検出(DDRCLKPOL)を確実に行えるようにします。この信号を使用して、同期レジスタに対するクロック極性を制御します。

## DLL 補正された遅延ロジック

マスタ DLL(DQSDLL)は必要な 90° 位相シフトをするために DQSBUF 内の遅延ロジックとともに動作します。DQSBUF はチップ右辺の DQSDLL から 7 ビット遅延制御コードを受けとります。この制御信号は 2 つの DQSBUF 内クロックスレーブ遅延ラインで使用されます。一方はリード動作時のクロック 90° 位相シフトに使用され、他方はライト動作時のデータ 90° 位相シフトに使用されます。

DQS 回路 (DQSBUF) は ECLK を 90° 位相シフトして DQSR90 を生成します。DQSR90 信号は、続いてチップ右辺にある全 DDR メモリ I/O ロジックセルに送られ、メモリのリード動作で入力データを取り込むクロックになります。

DQSW90 もまた DQSBUF によって生成され、メモリライト動作に使用されます。DQSW90 は SCLK 信号を 90° 位相シフトしたもので、DDR データ出力に使用されます。これはライト動作時に DQ データの中央に DQS エッジを合わせるという要件を満たします。

## データ有効信号とデータバースト検出

DQSBUF は有効なデータが入力 DDR レジスタから FPGA コアに転送されたことを FPGA に通知する、データ有効 (Data Valid) 信号の生成にも責任を負います。データ有効信号はレベルセンシティブで、FPGA コアとの境界でデータと整合します。

DQSBUF のデータバースト検出は、DDR リード動作時に READ パルスを最適な位置に合わせるために用いられます。トレーニングプロセスで十分なバースト長 (BL) が用いられることが重要です。MachXO2 の DDR メモリ実装では、デバイスが正しい READ パルス位置を検出できるように、少なくとも連続した 2 つの BL2 (BL=2)、または 1 つの BL4 (BL=4)、或いはこれらバースト長を複数回トレーニングプロセスで使用することが必要です。

## I/O ロジック・データパス

DDR メモリの I/O ロジック、或いはメモリ PIO セルは本ドキュメントの始めに図 11-2 で示しました。DDR メモリ入力パスで、第 1 段 DDR レジスタ組を用いて、位相シフトした DQS 信号の立ち上がりと立ち下がりエッジで、DDR データを多重分離します。次に、第 2 段の組を使用してそれらデータを DQS ドメイン (DQSR90) から SCLK ドメインに転送します。そしてレジスタの最終組を使用して、DDRCLKPOL に基づく SCLK によって再度入力データをクロッキングします。出力側で DQS と DQ は同じ論理を共有します。パラレルデータはライトクロック DQSW90 により多重化され、DQS 出力パルスは SCLK により制御されます。

DDR メモリのビルディングブロックの詳細については、"DDR ソフトウェアのプリミティブとアトリビュート"を参照してください。

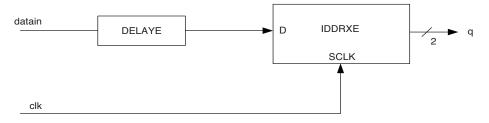

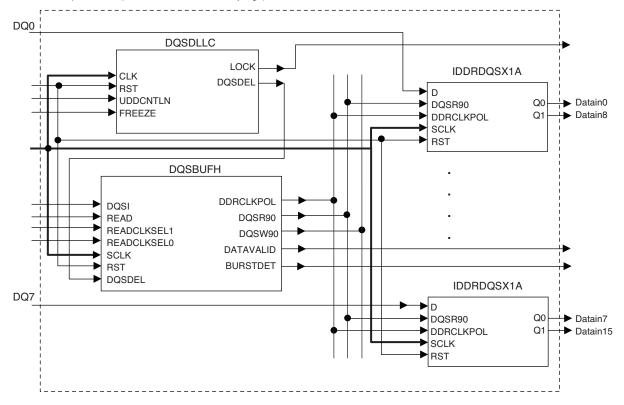

## DDR / DDR2 / LPDDR メモリリードの実装

MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスでは、IPexpress ツールで生成された DDR メモリモジュールによって、DDR / DDR2 / LPDDR メモリインターフェイス機能をサポートします。IPexpress を使用することにより、設計者は DDR / DDR2 / LPDDR メモリから入力されたデータのリードに必要な、様々なモジュールを生成できます。

DDR / DDR2 / LPDDR のリード側は、次の3つのソフトウェア・エレメントにより実装されます。DQSDLL は較正に使用する DLL です。IDDRDQS は入力 DDR レジスタを実装します。DQSBUF は DQS 遅延ブロック とクロック極性制御ロジック、そしてデータ有効モジュールです。DQSR90 は専用クロックツリーを介して 各 IDDRDQS セルに分配されます。SCLK の配線は必ずプライマリ・クロックネットの1本を使用する必要が あります。

### 図 11-46. DDR / DDR2 / LPDDR リードの実装

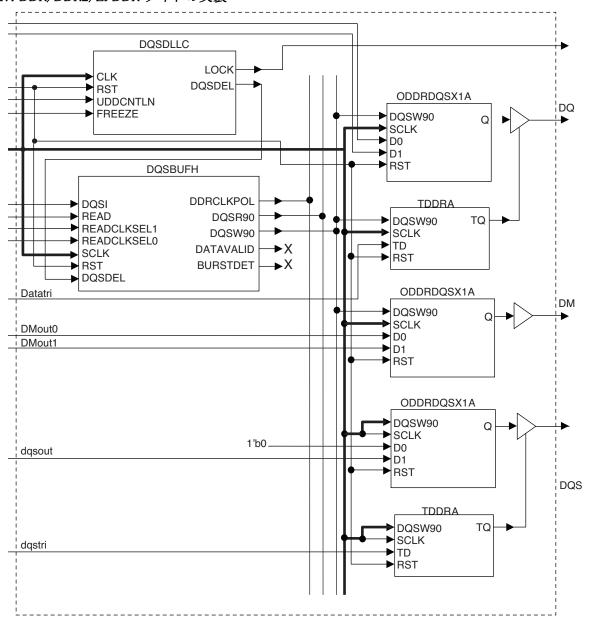

## DDR / DDR2 / LPDDR メモリライトの実装

DDR メモリインターフェイスのライト部分を実装するには、シングルデータレート(SDR)の2本のデータストリームを、クロックの両エッジ遷移時に合わせて多重化する必要があります。さらに、DQS はメモリピンに入力されるとき、データ(DQ)の中央にエッジがあり、かつ差動出力クロック(CLKP / CLKN)のエッジに揃っている必要があります。これらの信号に加え、アドレス / コマンド及びデータマスク(DM)信号を生成する必要があります。このインターフェイスの生成には IPexpress を使用する必要があります。

DQSW90 は、専用クロックツリーを介して各 ODDRDQS セルに分配されます。SCLK の配線は必ずプライマリ・クロックネットの 1 本を使用する必要があります。

### DDR / DDR2 / LPDDR のライトデータ (DQ) とストローブ (DQS) の生成

図 11-47 はライト動作での DQ / DQS 信号の生成を示します。DQS90 は SCLK を  $90^\circ$  位相シフトした信号です。前述のように、DQS ではなく DQSW90 を使用して DQ を  $90^\circ$  位相シフトします。DQ と DM の生成には DQSW90 を使用し、DQS の生成には SCLK を使用します。これにより DQS のエッジが DQ と DM の中央に合わされます。DQS は DDR と LPDDR ではシングルエンドですが、DDR2 では差動になります。

## 図 11-47. DDR/DDR2/LPDDR ライトの実装

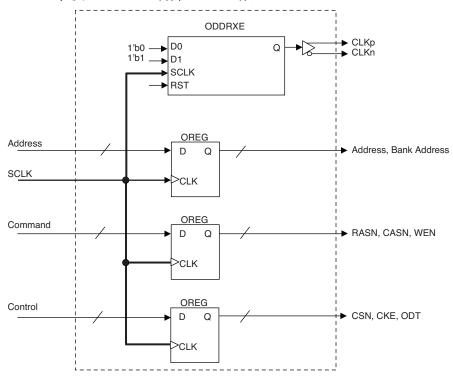

## DDR / DDR2 / LPDDR のライトクロック、アドレス、及びコマンド生成

メモリのライト動作は、コントローラが SDRAM メモリに対して差動クロックとアドレス、及びコマンドを生成する必要があります。クロックは ODDRX (x1) プリミティブを使用して生成され、その 2 入力を Low と High に固定することで出力クロックを生成します。DDR SDRAM メモリとインターフェイスする場合、CLKP を SSTL25D I/O で接続する必要があります。DDR2 メモリとインターフェイスする場合は SSTL18D I/O で接続し、差動クロック出力を生成する必要があります。LPDDR SDRAM メモリとインターフェイスする場合は、CLKP を LVCMOS18 I/O で接続する必要があります。同様に CLKN を生成することで 2 信号間のスキューを防止できます。

DDR / DDR2 / LPDDR SDRAM インターフェイスのアドレスとコマンド信号は、通常の出力レジスタ OREG により生成されます。DQ / DQS とクロック / アドレス、及びコマンド生成には、同一の SCLK が使用されます。SCLK の配線は、必ずプライマリ・クロックネットの 1 本を使用する必要があります。

### 図 11-48. CLK とアドレス、及びコマンド制御ピンの生成

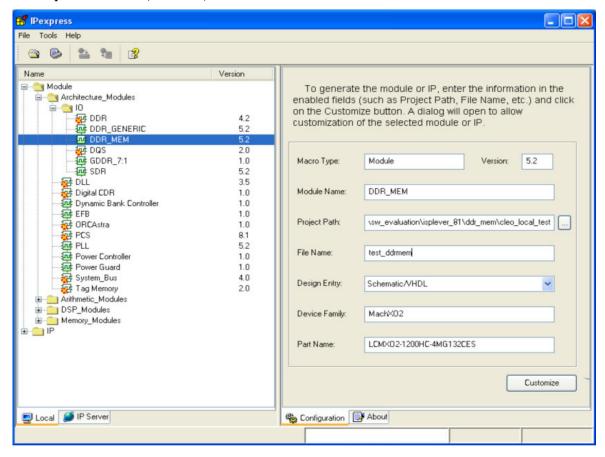

# IPexpress を使用した DDR メモリインターフェイスの生成

上記の全ての DDR / DDR2 / LPDDR インターフェイスのパラメータ設定と生成には、IPexpress ツールを使用する必要があります。IPexpress の GUI では、全 DDR メモリモジュール **Architecture Modules > IO** に配置されています。図 11-49 に示すように、DDR MEM を使用して DDR メモリインターフェイスを生成します。

## 図 11-49. IPexpress のメインウインドウ

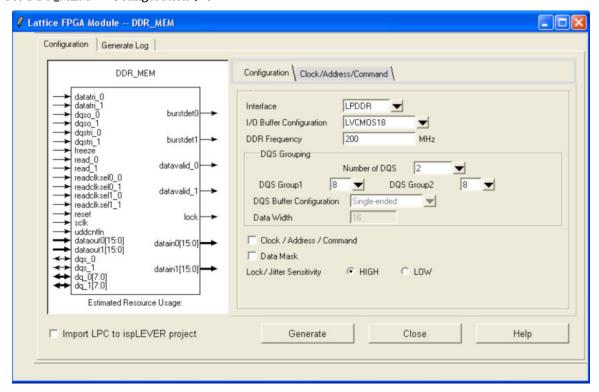

DDR\_MEM モジュールには、2 つのタブがあります。図 11-50 に示す Configuration タブを使用して、DDR やDDR2、及び LPDDR とそれらに対応するパラメータを選択します。

図 11-50. DDR\_MEM の Configuration タブ

表 11-11 に DDR\_MEM の Configuration タブの GUI オプションの詳細を示します。

表 11-11. DDR\_MEM モジュール、Configuration タブのオプション

| オプション                                          | 説明                                                | 値・範囲                                                       | デフォルト値                                             |

|------------------------------------------------|---------------------------------------------------|------------------------------------------------------------|----------------------------------------------------|

| Interface Type                                 | インターフェイスのタイプ                                      | DDR, DDR2, LPDDR                                           | DDR                                                |

| I/O Buffer Configuration                       |                                                   | SSTL25_I, SSTL18_I,<br>LVCMOS18                            | SSTL25_I                                           |

| DDR Frequency                                  |                                                   | DDR = 83-100MHz<br>DDR2 = 125 - 150MHz<br>LPDDR = 0-133MHz | DDR = 100 MHz<br>DDR2 = 150 MHz<br>LPDDR = 133 MHz |

| Number of DQS                                  | 利用可能な DQS グループ数                                   | 1, 2                                                       | 2                                                  |

| Number of DQ for DQS<br>Group1 and DQS Group 2 | DQS グループのデータ幅                                     | 1 ~ 8                                                      | 8                                                  |

| DQS Buffer Configuration for DDR2              | DQS バッファタイプ                                       | シングルエンド、差<br>動                                             | Single-ended                                       |

| Data Width (calculated)                        | インターフェイスのデータ幅                                     | 1-16                                                       | (算出)                                               |

| Clock/Address/Command                          | 本オプションがチェックされるとクロック / アドレス / コマンド・インターフェイスが生成される  | Enabled, Disabled                                          | Disabled                                           |

| Data Mask                                      | 本オプションがチェックされると、データマスク<br>信号が生成される                | Enabled, Disabled                                          | Disabled                                           |

| Lock/Jitter Sensitivity                        | DQSDLL のロック感度アトリビュート。Low は<br>ジッタに対する感度が低いことを意味する | High, Low                                                  | Low                                                |

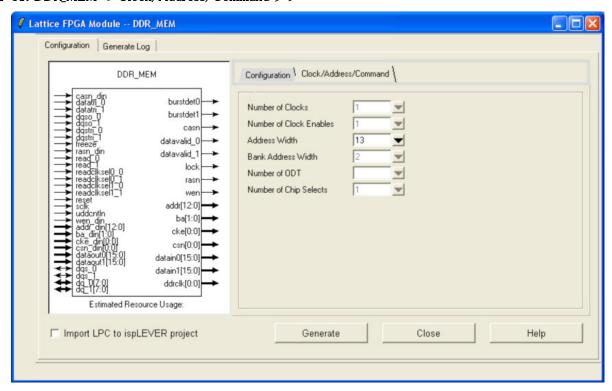

ユーザが IPexpress を使用してクロック / アドレス / コマンド信号の生成を選択した場合、Clock / Address / Command タブの設定が有効になり、必要に応じてセットアップできます。

図 11-51. DDR\_MEM の Clock/Address/Command タブ

## 表 11-12. DDR MEM モジュール、Configuration タブのオプション

| GUI オプション               | 值•範囲                                     | デフォルト値                          |

|-------------------------|------------------------------------------|---------------------------------|

| Number of Clocks        | DDR/DDR2: 1, 2LPDDR: 1                   | 1                               |

| Number of Clock Enables | DDR/DDR2: 1, 2 LPDDR: 1                  | 1                               |

| Address Width           | DDR: 12 - 14 DDR2: 13 - 16 LPDDR: 12 -14 | DDR: 13DDR2: 14LPDDR: 13        |

| Bank Address Width      | DDR: 2 DDR2: 2, 3 LPDDR: 2               | DDR: 2 DDR2: 2 LPDDR: 2         |

| Number of ODT           | DDR: blank DDR2: 1, 2 LPDDR: blank       | DDR: Blank DDR2: 1 LPDDR: Blank |

| Number of Chip Selects  | DDR / DDR2: 1, 2 LPDDR: 1                | DDR/DDR2: 1 LPDDR: 1            |

## DDR メモリの DQ / DQS の設計規則とガイドライン

以下に示すのは MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスにおける、DDR メモリインターフェイス実装に関するいくつかの規則とガイドラインです。

- ・DDR メモリの I/O ロジックと DQS 回路は、デバイスの右辺バンクで使用可能。即ち DDR メモリイン ターフェイスは、デバイスの右辺バンクでのみ実装が可能

- ・デバイスには2つのDQSDLLがあり、一方は左辺と下辺バンク用で、他方は右辺と上辺バンク用。DDRメモリインターフェイスの実装には、右辺と上辺バンク用のみが使用できる

- ・DQSDLLにより生成される遅延制御コードは、右辺バンクの全DDRメモリ用I/Oロジックに適用される

- ・ DDR1 SDRAM インターフェイスを実装する場合、全てのインターフェイス信号は SSTL25 I/O で接続する

- ・ DDR2 SDRAM インターフェイスの場合、信号を SSTL18 I/O で接続する

- ・ LPDDR SDRAM インターフェイスの場合、信号を LVCMOS18 で接続する

- ・DDR メモリインターフェイスは全て差動クロック信号が必要で、メモリインターフェイスで指定された 差動 I/O で接続する

- ・ DDR2 に対する差動 DQS の使用はオプション。差動の場合は SSTLD18 I/O で接続する

## DDR/DDR2/LPDDR のピン配置ガイドライン

- · DQS と DQ の関連にかんする規則に必ず従うこと

- DQS に関連する全ての DQ (8 または 4 本) は同一の DQS-14 グループ内になければならない

- ・データマスク(DM)は対応する DQS-14 グループ内の一部であることが必要

- 例えば DM[0] は DQ[7:0] と DQS[0] のある DQS-14 グループ内にあること

- · DQS は専用の DQS パッドに割り当てなければならない

- 差動 DQS を選択する場合 DQSN パッドが使用される

- ・SSTL18D を DQS パッドに適用する場合 DQSN パッドには信号を割り当てないこと

- ソフトウェアが自動的に DQS# を配置する

- ・出力生成に使用する PLL へのクロックは正しい専用 PLL ピンの入力に割り当てなければならない

- ・ DQS-14 グループに加え、DDR メモリインターフェイスは通常、メモリ規模に応じて CLK / CLKN やアドレス、コマンドピンなど、これ以外に  $20\sim24$  ピンが必要。デバイスの右辺バンク以外のピンをこれらの信号に使用できる

- ・ MachXO2 デバイスファミリは任意の I/O を Vref ピンとして使用できる。しかし DDR / DDR2 用の Vref は DQS-14 グループの一部でなければならない。Vref ピンの割当て規則については、TN1202 "MachXO2 sysIO Usage Guide (MachXO2 sysIO 使用ガイド)"を参照のこと

# DDR ソフトウェア・プリミティブとアトリビュート

このセクションでは、全ての汎用 DDR インターフェイスと DDR メモリインターフェイスの実装に使用する ソフトウェア・プリミティブについて説明します。プリミティブは、その使用法に従って分割されます。一 部は汎用 DDR インターフェイスのみに使用され、一部は DDR メモリの DQS ロジックに使用され、またその 他は汎用とメモリインターフェイスが制御機能を共有します。最初に DDR 入力のプリミティブについて説明 し、続いて DDR 出力のプリミティブを、そして DDR 制御ロジックのプリミティブについて説明します。

表 11-13. MachXO2 DDR ソフトウェア・プリミティブ

| タイプ          | プリミティブ     | 使用法                              |

|--------------|------------|----------------------------------|

|              | IDDRXE     | 汎用 DDR x1                        |

|              | IDDRX2E    | 汎用 DDR x2                        |

| Data Input   | IDDRX4B    | 汎用 DDR x4                        |

|              | IDDR71A    | 汎用 DDR 7:1                       |

|              | IDDRDQSX1A | DDR メモリ                          |

|              | ODDRXE     | 汎用 DDR x1                        |

|              | ODDRX2E    | 汎用 DDR x2                        |

| Data Output  | ODDRX4B    | 汎用 DDR x4                        |

|              | ODDR71A    | 汎用 DDR 7:1                       |

|              | ODDRDQSX1A | DDR メモリ                          |

| DQS Tristate | TDDRA      | DDR メモリ                          |

| DQSBUF Logic | DQSBUFH    | DDR メモリ                          |

| DLL          | DQSDLLC    | 汎用 x2、x4、及び DDR メモリ用のマスタ DLL     |

|              | DELAYD     | 汎用 x2、x4 用の動的制御を備える遅延ブロック        |

| Input Delay  | DELAYE     | 汎用 DDR x1、x2、x4 用の固定遅延を備える遅延ブロック |

|              | DLLDELC    | 汎用 DDR x2、x4 用のクロックスレーブ遅延セル      |

## 入力 DDR プリミティブ

入力 DDR プリミティブは、メモリインターフェイスから入力される GDDR データと DDR データの両方を捕捉するために使用するモジュールです。GDDR インターフェイスに対して様々なギアリングを実装する DDR 入力レジスタには、いくつかのモードがあります。メモリ DDR は、GDDR プリミティブとは異なるプリミティブを使用します。入力プリミティブの全データポートで受信される最初のビットは、パラレルデータのQ0です。

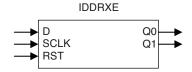

## **IDDRXE**

このプリミティブは入力レジスタブロックを x1 ギアリングモードで実装し、MachXO2 デバイスの全辺で使用可能な、汎用 DDR x1 インターフェイス(ギアリング比 1:2)に対してのみ使用されます。このプリミティブでは全体で 1 本のクロックソース SCLK を使用するため、クロックドメイン転送はありません。

### 図 11-52. IDDRXE シンボル

このプリミティブの内部レジスタ構造は、図 11-1 で示す基本 PIO セルに基づいています。初段の組は SCLK の両エッジでデータを捕捉する DDR レジスタです。次段の組は捕捉したデータを FPGA コアに転送する同期レジスタです。

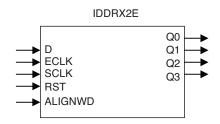

### **IDDRX2E**

このプリミティブは入力レジスタブロックを x2 ギアリングモードで実装し、MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの下辺の汎用 DDR x2 インターフェイス(ギアリング比 1:4)に対してのみ使用します。このレジスタは GDDR インターフェイスでエッジクロック配線を、FPGA コアでシステムクロックを使用するように設計されています。エッジクロックは ECLK ポートに接続され、システムクロックは SCLK ポートに接続されます。本プリミティブはデバイス下辺の I/O セルの、A/B または C/D ペアの両方に使用できます。

### 図 11-53. IDDRX2E シンボル

このプリミティブの内部レジスタ構造は、図 11-3 の受信パスで示すようなビデオ PIO セルに基づいています。初段の組は ECLK の両エッジでデータを捕捉する DDR レジスタです。次段の組はクロックドメイン転送のためにデータを保持する同期レジスタです。第3段の組は ECLK から SCLK へのクロックドメイン転送を行います。

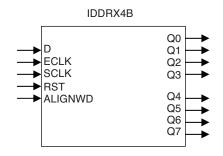

#### **IDDRX4B**

このプリミティブは入力レジスタブロックを x4 ギアリングモードで実装し、MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの下辺の汎用 DDR x4 インターフェイス(ギアリング比 1:8)に対してのみ使用します。このレジスタは GDDR インターフェイスでエッジクロック配線を、FPGA コアでシステムクロックを使用するように設計されています。エッジクロックは ECLK ポートに接続され、システムクロックは SCLK ポートに接続されます。このプリミティブはデバイス下辺の I/O セルの A/B ペアだけに使用できます。

#### 図 11-54. IDDRX4B シンボル

IDDRX4B の 1:8 ギアリングは 2 つの 1:4 ギアリングを使用し、IDDRX2E と基本アーキテクチャを共有しています。このプリミティブの内部レジスタ構造は、図 1c の受信パスで示すビデオ PIO セルに基づいています。初段の組は ECLK の両エッジでデータを捕捉する DDR レジスタです。次段の組はクロックドメイン転送のためにデータを保持する同期レジスタです。第 3 段の組は ECLK から SCLK へのクロックドメイン転送を行います。

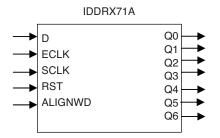

#### IDDRX71A

このプリミティブは入力レジスタブロックを 7:1 ギアリングモードで実装し、MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイス下辺の、汎用 DDR71 インターフェイス(ギアリング比 1:7)に対してのみ使用します。このレジスタは GDDR インターフェイスでエッジクロック配線を、FPGA コアでシステムクロックを使用するように設計されています。エッジクロックは ECLK ポートに接続され、システムクロックは SCLK ポートに接続されます。このプリミティブは入力 x4 ギアリングのプリミティブと同様に、デバイス下辺の PIO セルの A/B ペアだけに使用できます。

図 11-55. IDDRX71A シンボル

IDDRX71A の 1:7 ギアリングは、IDDRX4B プリミティブの 1:8 ギアリングと同じアーキテクチャを共有します。一度に選択するのが 3 ビットデータか 4 ビットデータかは、内部制御信号に依存します。このプリミティブの内部レジスタ構造は、図 11-3 の受信パスで示すビデオ PIO セルに基づいています。初段の組は ECLK の両エッジでデータを捕捉する DDR レジスタです。次段の組はクロックドメイン転送のためにデータを保持する同期レジスタです。第 3 段の組は ECLK から SCLK へのクロックドメイン転送を行います。

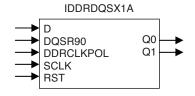

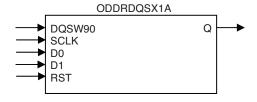

#### IDDRDQSX1A

このプリミティブは DDR メモリの入力バッファで、MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの右辺の、DQ または DQS 入力ピンに対してのみ使用できます。このプリミティブは 3 段のレジスタから構成されており、DDR レジスタの初段は、DQS 回路(DQSBUF)で生成する DQS ストローブを90°位相シフトした DQSR90 信号の、立ち上がりと立ち下がりエッジで入力データを捕捉します。捕捉されたデータはその後、やはり DQSBUF で生成されてクロックドメイン転送を保証する役割を果たすDDRPOLCLK 信号の極性に対応して、SCLK の立ち上がりエッジまたは立ち下がりエッジで次段のレジスタに転送されます。。信号は最終段のレジスタで SCLK の立ち上がりエッジで再びサンプルされ、フルクロック周期の転送をコアに提供します。

### 図 11-56. IDDRXQSX1A シンボル

このプリミティブの内部レジスタ構造は、図 11-2で示すようにメモリPIOセルの入力パスに基づいています。

### 出力 DDR プリミティブ

出力 DDR プリミティブは、2 本のデータストリームを GDDR インターフェイスまたは DDR メモリデバイス に出力するために多重化する、出力 DDR モジュールです。GDDR インターフェイスに対して様々なギアリングを実装する DDR 出力レジスタには、幾つかのモードがあります。メモリ DDR 出力は、GDDR インターフェイスとは異なるプリミティブを使用します。出力プリミティブの全データポートで送信される最初のビットは、パラレルデータの D0 です。

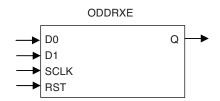

#### **ODDRXE**

このプリミティブは出力レジスタブロックをx1ギアリングモードで実装し、MachXO2デバイスの全辺で使用できます。このプリミティブではFPGAコアからの1本のプライマリ・クロックソースSCLKを使用します。

## 図 11-57. ODDRXE シンボル

このプリミティブの内部レジスタ構造は、図 11-1 で示す基本 PIO セルに基づいています。SCLK を使用し、2 ビット・パラレルデータを多重化してシリアル・データストリームを生成します。

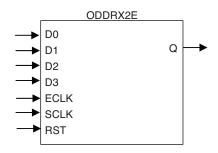

#### ODDRX2E

このプリミティブは出力レジスタブロックを x2 ギアリングモードで実装し、MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイス上辺の、汎用 DDR x2 インターフェイス(ギアリング比 4:1)に対してのみ使用されます。このレジスタは FPGA でシステムクロックを使用し、DDR インターフェイスでエッジクロックを使用するように設計されています。エッジクロックは ECLK ポートに接続され、システムクロックは SCLK ポートに接続されます。このプリミティブはデバイス上辺の PIO セルの、A/B と C/D ペアの両方で使用できます。

### 図 11-58. ODDRX2E シンボル

このプリミティブの内部レジスタ構造は、図 11-3 の送信パスで示すビデオ PIO セルに基づいています。パラレルデータはレジスタ初段の組で SCLK によって取り込まれます。各アップデート時に、パラレルデータが SCLK によりクロッキングされ、次段レジスタの組で保持されます。第 3 段レジスタ組の出力データは ECLK により多重化されシリアルデータとして出力されます。

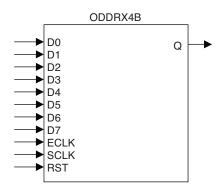

#### ODDRX4B

このプリミティブは出力レジスタブロックを x4 ギアリングモードで実装し、MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイス上辺の、汎用 DDR x4 インターフェイス(ギアリング比 8:1)に対してのみ使用されます。このレジスタは FPGA でシステムクロックを使用し、GDDR インターフェイスでエッジクロックを使用するように設計されています。エッジクロックは ECLK ポートに接続され、システムクロックは SCLK ポートに接続されます。このプリミティブは、デバイス上辺の I/O セルの A/B ペアでのみ使用できます。

#### 図 11-59. ODDRX4B シンボル

このプリミティブの内部レジスタ構造は、図 11-3 の送信パスで示すビデオ PIO セルに基づいています。パラレルデータはレジスタ初段の組で SCLK により取り込まれます。各アップデート時にパラレルデータが SCLK により取り込まれ、次段レジスタの組で保持されます。第3段レジスタの組のデータは、ECLK により多重化されシリアルデータとして出力されます。

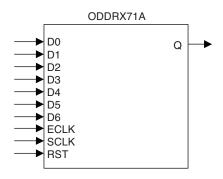

## ODDRX71A

このプリミティブは、出力レジスタブロックを 7:1 ギアリングモードで実装し、MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイス上辺の、汎用 DDR71 インターフェイス(ギアリング比 7:1)に対して

のみ使用されます。このレジスタは FPGA でシステムクロックを使用し、GDDR インターフェイスでエッジクロック配線を使用するように設計されています。エッジクロックは ECLK ポートに接続され、システムクロックは SCLK ポートに接続されます。このプリミティブは、デバイス上辺の I/O セルの A/B ペアでのみ使用できます。

### 図 11-60. ODDRX71A シンボル

ODDRX71A の 7:1 ギアリングは、ODDRX4B プリミティブの 8:1 ギアリングと同じアーキテクチャを共有しています。送信のために一度に選択するのが 3 ビットデータか 4 ビットデータかは、内部制御信号に依存します。このプリミティブの内部レジスタ構造は、図 11-3 の送信パスで示すビデオ PIO セルに基づいています。パラレルデータは、SCLK で初段レジスタの組に取り込まれます。各アップデート時、パラレルデータが SCLK で次段レジスタの組で保持されます。第 3 段レジスタの組のデータは、ECLK により多重化されシリアルデータとして出力されます。

#### ODDRDQSX1A

このプリミティブは DDR メモリの出力バッファで、MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイス右辺の DQ または DQS 出力ピンに対してのみ使用できます。DQ 出力データの場合、パラレルデータはシステムクロック SCLK でこのプリミティブに取り込まれます。捕捉されたデータは、SCLK を DQS 回路(DQSBUF)で 90°位相シフトした DQSW90 信号により多重化され、ピンに出力されます。DQS 出力の場合も同じ出力バッファ・アーキテクチャを共有しますが、DQ とは異なりクロックは SCLK により制御され、DQS は 90°位相シフトしません。これにより送信時に DQS が DQ の中央にアラインされます。

### 図 11-61. ODDRDQSX1A シンボル

このプリミティブの内部レジスタ構造は、図 11-2 で示すメモリ PIO セルの出力パスに基づきます。

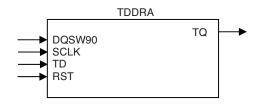

#### **TDDRA**

これは MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの右辺で DQ または DQS ピンに対して使用される、特別なトライステート・プリミティブです。このレジスタ構造は、図 11-2 のメモリ PIO セルのトライステート・レジスタブロックに示されています。

#### 図 11-62. TDDRA シンボル

このコンポーネントを DQ ピンに対して使用する場合、DQSW90 ポートは DQSBUF コンポーネントからの DQSW90 信号でドライブされる必要があります。DQS に対して使用する場合は、DQSW90 ポートは SCLK でドライブされる必要があります。このプリミティブは、表に記載されているアトリビュート(属性)があり、 DDR のメモリライト時に DQS を DQ データの中央に確実にアラインさせます。

## 表 11-14. TDDRA アトリビュート

| アトリビュート | 説明                                                       | 値                    | ソフトウェア・デ<br>フォルト |

|---------|----------------------------------------------------------|----------------------|------------------|

|         | DQS ピンに対する TDDRA のクロック極性を選択<br>する。DDR ライト時に DQS に対してのみ使用 | ENABLED,<br>DISABLED | DISABLED         |

(和訳版注:英語オリジナルでは本表と異なるがこれは誤り。次改訂版では本表のように更新予定)

## DDR 制御ロジック・プリミティブ

以下に説明する DDR プリミティブには DLL と DQS 回路、及び遅延エレメントが含まれます。 DLL は GDDR と DDR メモリで共有しています。 DQS 回路は DDR メモリに対してのみ使用され、遅延エレメントはデータパスまたはクロックスレーブ遅延パス用です。

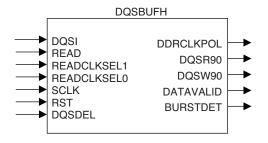

#### **DQSBUFH**

このプリミティブは DDR メモリインターフェイスで使用する DQS 回路です。DDR メモリのリード / ライト動作のために DQS を位相シフトします。このプリミティブはプリアンブル及びポストアンブル検出、データ有効(Data Valid)検出、及び DDR メモリインターフェイスのアプリケーションに必要な多くの機能を提供します。

## 図 11-63. DQSBUFH シンボル

#### 表 11-15. DQSBUFH 信号

| 信号                          | I/O | 説明                                                                                                                  |

|-----------------------------|-----|---------------------------------------------------------------------------------------------------------------------|

| DQSI                        | I   | ピンからの DQS 信号                                                                                                        |

| READ                        | I   | FPGA ロジックからの DDR リードモード信号                                                                                           |

| READCLKSEL1,<br>READCLKSEL0 | I   | READ パルスの位置制御に関する READ クロックソースと極性制御を T/4 精度で選択する。4つの位置とは、SCLK または DQSW90 のそれぞれ立ち上がり / 立ち下がりエッジ。信号は FPGA ロジックから入力される |

| SCLK                        | I   | システムクロック                                                                                                            |

| RST                         | I   | このブロックのリセット信号                                                                                                       |

| DQSDEL                      | I   | DQSDLLC からの DQS スレーブ遅延制御                                                                                            |

| DDRCLKPOL                   | О   | SCLK の極性制御                                                                                                          |

| DQSR90                      | О   | 90° 位相シフトした DQS 出力                                                                                                  |

| DQSW90                      | О   | 90° 位相シフトした SCLK 出力                                                                                                 |

| DATAVALID                   | О   | リードモードのデータ有効信号                                                                                                      |

| BURSTDET                    | О   | バースト検出信号                                                                                                            |

図 11-64 は DQSBUFH プリミティブ内の機能ブロック概要です。

### 図 11-64. DQSBUFH ブロック図

DQS\_Clean はデジタル的に生成された DQS 信号で、下流ロジック用にグリッチを除去した DQSI 信号です。 READCLKSEL 信号はユーザロジックによりドライブされる、DDR メモリコントローラ IP の一部です。 SCLK と DQSW90 信号間の 4 つの位相の 1 つを選択し、リードプロセスを開始します。

DDR クロック極性 (DDRCLKPOL) 信号は、最初の DQS 遷移時に SCLK の位相に基づいて生成されます。 SCLK が High のときに DQS 遷移が発生すると、DDRCLKPOL が High になり、SCLK の立ち上がりエッジでデータを FPGA コアに出力します。その他の場合は DDRCLKPOL は Low になり、SCLK の立ち下がりエッジでデータを FPGA コアに出力します。

DQSR90 は、DQSDLL からの DQSDEL 遅延制御コードに基づき、DQS\_Clean 信号を 90° 位相シフトした信号です。この信号は DQSR90 ツリーに分配されて DDR メモリに入力する全 DQ データで使用され、リード動作時に入力データを取り込むクロックとなります。DQSW90 は SCLK 信号を 90° 位相シフトした信号です。これは選択信号として使用され、ライト動作時に出力データをシリアライズします。ライト動作時にDQS バッファは DQ データと 90° の位相差があります。

DDR メモリのリード動作では、BURSTDET を使用してリードプロセスの開始時に READ パルスの位置を最適化します。トレーニングプロセスでは、起動時に少なくとも 4 バースト長(BL)が必要です。これを実現するのは、2 連続の BL2(BL=2)か偶数個の BL2、任意個の BL4(BL=4)、またはこれより長いです。またリード動作中には、BURSTDET 信号を用いて READ パルス位置を定期的にキャリブレーションします。 DDR メモリコントローラ IP は、必要なステップで BURSTDET 信号をモニタリングし、最適な READ パルスの位置を検出します。

DQSBUF ブロックへの READ 信号は、DDR メモリコントローラ IP から生成されます。READ コマンドは DDR-SDRAM を制御した後 High になります。これは通常 1 サイクルだけ DQS プリアンブルに先行する必要がありますが、前回のリードサイクルのトレーリングビットに重なることもあります。READ 信号を使用して、図 11-65 のグレー部分で内部信号の DQS\_ena をアクティブにします。すると BURSTDET が High になり、DQS\_Clean 信号がアクティブになります。READ 信号はバースト長期間を維持する必要があります。

### 図 11-65. READ パルス位置の最適化

#### **DQSDLLC**

DQSDLLC はオンチップ DLL で、DQS 信号に必要な 90° 位相シフトを生成します。DDR 実装には DQSDLLC を 1 つだけ使用します。この DLL に対する入力クロックは DDR インターフェイスと同じ周波数にする必要があります。DQSDLLC はこのクロック周波数に基づき遅延を生成し、このブロックへの制御入力をアップデートします。このアップデート制御(UDDCNTLN)入力がアサートされると、DQSDLLC は DQS 遅延ブロックに対する動的遅延制御コード (DQSDEL) をアップデートします。これ以外の場合アップデートはホールド状態です。UDDCNTLN に対する Low アクティブ信号が、DQS 位相アライメントをアップデートします。

## 図 11-66. DQSDLLC シンボル

## 表 11-16. DQSDLLC 信号

| 信号       | I/O | 説明                                                        |

|----------|-----|-----------------------------------------------------------|

| CLK      | I   | DLL への入力クロック、DDR インターフェイスと同じ周波数                           |

| RST      | I   | DLL リセット制御                                                |

| UDDCNTLN | I   | 調整に先立つ遅延コードの制御をアップデートか維持する。Low アクティブ信号で遅延<br>コードをアップデートする |

| FREEZE   | I   | DLL の入力 CLK をフリーズまたはリリースする                                |

| LOCK     | 0   | DLL ロック信号                                                 |

| DQSDEL   | О   | スレーブ遅延セルへの DLL 遅延制御コード。DQSBUFH エレメントの DQSDEL に接続する        |

DQSの遅延は、UDDCNTLN入力を使用することでPVTバラつきに対してアップデートできます。UDDCNTLNを Low にすることで、バラつきが予測されるとき DQSDEL をアップデートできます。 DDR メモリのリードまたはライト動作中以外はいつでもアップデートできます。

このコンポーネントの FREEZE 入力ポートを使用して、DLL をフリーズまたはリリースします。FREEZE が High になるとデバイスは DLL をフリーズして、遅延コードが保持される間の節電をします。FREEZE が Low になると DLL を解放して動作を再開します。クロックを停止する前に、DQSDLLC に必ず FREEZE を与えなければなりません。

DLL への入力基準クロックの周波数に基づいて、DLL はデフォルトでは DQS ストローブの 90° 位相シフト信号を生成します。ユーザは LOCK\_SENSITIVITY アトリビュートを用いることで、ジッタに対する感度を制御できます。Lock\_sensitivity の HIGH はジッタに対する感度が高いことを意味しますが、LOW にプログラムすることを推奨します。

DQSDLLC は最大 400MHz までの幅広い周波数に対応します。このプリミティブに関する FIN アトリビュートにより、ユーザは DLL 周波数を設定できます。周波数が非常に低い場合、DLL ロックプロセスをバイパスでき、その目的のためにアトリビュートの FORCE\_MAX\_DELAY を使用できます。セットされた場合、DLLはロックプロセスに入ることなく、最大遅延 (maximum delay) ステップにロックします。FORCE\_MAX\_DELAYアトリビュートの効果は、シミュレーションモデルには反映されていなく、常に 90° 位相シフト動作しますので留意してください。FORCE\_MAX\_DELAYが有効な周波数範囲については MachXO2 ファミリデータシートを参照してください。

### 表 11-17. DQSDLLC のアトリビュート

| アトリビュート          | 説明                                       | 値             | ソフトウェア・<br>デフォルト |

|------------------|------------------------------------------|---------------|------------------|

| LOCK_SENSITIVITY | ジッタ感度                                    | HIGH, LOW     | LOW              |

| FIN              | DLL の入力クロック周波数                           | DLL がサポートする範囲 | 100 MHz          |

|                  | 低周波数での DLL ロック手順をバイパスし、<br>最大遅延設定値をセットする | YES, NO       | NO               |

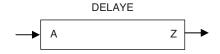

#### **DELAYE**

DDR レジスタへの入力データは、遅延ブロック DELAYE によりオプション的に遅延できます。32 タップの DELAYE ブロックは、クロック注入遅延時間を補正するために用いられます。遅延量はアトリビュートの DEL\_MODE によって、実装するインターフェイス・タイプに基づいてソフトウェアが決定します。ユーザは、ブロックに対して USER\_DEFINED モードを選択することで遅延値を設定できます。このモードではユーザが手動で遅延ステップをセットする必要があります。各ステップごとの遅延は約 105ps です。全ての汎用 DDR インターフェイスに対しては PREDEFINED モードを使用することを推奨します。何らかのインターフェイスに対して正しくないアトリビュート値を設定すると、DELAYE 設定値が不正になり、DDR インターフェイスの性能が最適になりません。DELAYE ブロックは DDR インターフェイスの受信モードに適用されます。 MachXO2 デバイス全辺の全ての入力レジスタパスで利用できます。

#### 図 11-67. DELAYE シンボル

## 表 11-18. DELAYE 信号

| 信号 | I/O | 説明                     |

|----|-----|------------------------|

| А  | I   | sys I/O バッファからの DDR 入力 |

| Z  | О   | 遅延をともなう出力              |

## 表 11-19. DELAYE アトリビュート

| アトリビュート   | 説明                              | 値                                                                                | ソフトウェア・<br>デフォルト |

|-----------|---------------------------------|----------------------------------------------------------------------------------|------------------|

| DEL_MODE  | インターフェイス及びユーザ指定の遅延値に依存<br>する固定値 | SCLK_ZEROHOLD ECLK_ALIGNED ECLK_CENTERED SCLK_ALIGNED SCLK_CENTERED USER_DEFINED | USER_DEFINED     |

| DEL_VALUE | ユーザ定義の値                         | DELAY0···DELAY31                                                                 | DELAY0           |

## 表 11-20. GDDR インターフェイスに対応する DEL\_MODE 値

| インターフェイス名               | DEL_MODE 値    |

|-------------------------|---------------|

| GIREG_RX.SCLK           | SCLK_ZERHOLD  |

| GDDRX1_RX.SCLK.Aligned  | SCLK_ALIGNED  |

| GDDRX1_RX.SCLK.Centered | SCLK_CENTERED |

| GDDRX2_RX.ECLK.Aligned  | ECLK_ALIGNED  |

| GDDRX2_RX.ECLK.Centered | ECLK_CENTERED |

| GDDRX4_RX.ECLK.Aligned  | ECLK_ALIGNED  |

| GDDRX4_RX.ECLK.Centered | ECLK_CENTERED |

| GDDRX71_RX.ECLK.71      | Bypass        |

| GOREG_TX.SCLK           | N/A           |

| GDDRX1_TX.SCLK.Centered | N/A           |

| GDDRX1_TX.SCLK.Aligned  | N/A           |

| GDDRX2_TX.ECLK.Aligned  | N/A           |

| GDDRX2_TX.ECLK.Centered | N/A           |

| GDDRX4_TX.ECLK.ALIGNED  | N/A           |

| GDDRX4_TX.ECLK.CENTERED | N/A           |

| GDDRX_TX.ECLK.7:1       | N/A           |

## **DELAYD**

MachXO2-640U と MachXO2-1200/U、及びこれより大規模デバイスの下辺で、DDR レジスタへの入力データは DELAYD ブロックによって遅延することもできます。デバイスが動作する時に遅延値が決定される DELAYE ブロックと異なり、DELAYD ブロックはユーザがデバイス動作中でもデータ遅延量を制御できます。このブロックは 5 ビット(32 タップ)遅延制御を受けとり、ユーザロジックが遅延ポートを介して動的に制御します。各ステップごとの遅延は約 105ps です。

## 図 11-68. DELAYD シンボル

### 表 11-21. DELAYD 信号

| 信号                           | I/O | 説明                    |

|------------------------------|-----|-----------------------|

| A                            | Ι   | I/O バッファからのデータ入力      |

| DEL4, DEL3, DEL2, DEL1, DEL0 | Ι   | FPGA ロジックからの動的遅延入力ポート |

| Z                            | О   | 遅延をともなう出力             |

## **DLLDELC**

これはクロックスレーブ遅延セルで、全ての受信アライン・インターフェイスにおいて 90° 遅延信号を生成し、遅延は DQSDLLC エレメントの入力クロックに基づいて算出されます。必要な遅延量は、DQSDLLC によって生成される遅延制御コード DQSDEL に基づきます。

## 図 11-69. DLLDELC シンボル

## 表 11-22. DLLDELC 信号

| 信号     | I/O | 説明                |

|--------|-----|-------------------|

| CLKI   | I   | I/O バッファからのデータ入力  |

| DQSDEL | I   | DQSDLLC からの動的遅延入力 |

| CLKO   | О   | 遅延をともなう出力         |

# テクニカルサポート支援

e-mail: techsupport@latticesemi.com インターネット: www.latticesemi.com

# 日本語版改訂履歷

| 日付       | パージョン | 該当新ページ    | 改訂内容                                                                     |

|----------|-------|-----------|--------------------------------------------------------------------------|

| 2010年11月 | 01.0  | _         | 初版                                                                       |

| 2011年1月  | 01.1  | _         | 超多ピン(ultra-high, "U")デバイスを更新                                             |

| 2011年4月  | 01.2  | _         | IPexpress モジュールの信号名とタイミング情報を追記                                           |

| 2011年8月  | 01.3  |           | [1] 図 11-44 差し替え<br>[2] 英語オリジナルでは 1200-R1 デバイスに関する注記が追加されているが、日本語版では省略した |

| 2013年4月  | 01.5  | _         | (EN:ver.1.4) 会社ロゴ更新、ステータス更新(Preliminary-> 正規)                            |

|          |       | 11-61     | 表 11-17、FORCE_MAX_DELAY の記述を追加                                           |

|          |       | 11-61, 63 | DELAYE, DELAYD 節、遅延タップ 105ps の追記                                         |