# Implementing Video Display Interfaces Using MachXO2 PLDs

使用 MachXO2 PLD 实现视频显示接口

莱迪思白皮书

2010 年 11 月

Lattice Semiconductor

5555 Northeast Moore Ct.

Hillsboro, Oregon 97124 USA

Telephone: (503) 268-8000

[www.latticesemi.com](http://www.latticesemi.com)

# 简介

莱迪思半导体公司已经开发并支持大量适用于各种设备中显示接口的参考设计。目前 **MachXO2 PLD** 系列中配有一款显示接口。因为目前 **MachXO2** 器件支持这个接口，设计人员拥有一个更低成本和极低功耗的选择来实现嵌入式显示。如本白皮书中所述，**MachXO2** 为该类应用提供了极佳的选择。

显示接口是一个 **7:1 LVDS** 接口。在下面的章节中，将简要介绍该显示标准，并说明如何使用 **MachXO2** 器件的关键功能来实现该应用。此外，还将讨论现有的参考设计和相关应用示例的详细信息。

## 显示接口（7:1 LVDS）概述

需要集成的 **LCD** 屏幕的应用通常会使用一个显示接口（**7:1 LVDS**）连接。该接口通常也被称为 **Channel Link**、**Flatlink** 或来自其他供应商的 **Camera Link**。从技术上讲，**Channel Link** 和 **Flatlink** 专用于 **LCD** 显示器，**Camera Link** 专用于数字摄像机和图像采集卡。无论是哪一种，**7:1** 接口采用 **LVDS** 差分信号 **I/O** 标准。**VESA**（视频电子标准协会）定义了用于 **LCD** 显示器的 **7:1 LVDS** 接口。它已成为将笔记本电脑和上网本中的主板与 **LCD** 屏幕连接的非常常用的方法。今天，大量不同的引脚接口，从 **20- 50** 引脚，可以支持各种 **LCD** 显示分辨率。参见下面图 1，用于笔记本电脑的 **7:1** 布线示例。

图 1——用于连接 LCD 显示屏和笔记本主板的 7:1 LVDS 连接线

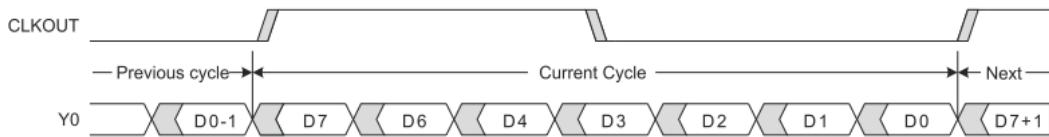

为了方便数字显示数据传输到 LCD 屏幕和尽量减少连接，从主板发送的数据将转换为串行格式。显示接口通常使用三条或四条 LVDS 数据通道和一条 LVDS 时钟线。更高分辨率的显示器将使用四条 LVDS 数据通道和一个 LVDS 时钟。在一个时钟周期内，每根数据线有 7 位串行数据，如图 1 所示。

图 1——嵌入式显示接口（7:1 LVDS）时序

因此，在 LVDS 显示接口，数据传输速率是时钟频率的 7 倍。一条时钟线通常支持三或四个数据通道。因此在显示端接收到的是 21 或 28 位数据。参考信息：时钟线通常工作在 60-100Mhz。

LCD 显示的每个像素有红、绿、蓝三种元素，构成了屏幕上所有可能的颜色。如果三条 LVDS 数据通道正在发送数据，例如从一台笔记本电脑的主板，那么颜色将包含 6 位 RGB（红，绿，蓝）数据外加一个控制位。然后，这些位序列化进入 LVDS 差分通道。参见表 1，了解三条数据通道及其 21 个串行数据位的 RGB 数据表示。四条数据通道的 28 位数据的关系也是类似的。四线接口使用 8 位的 RGB 颜色。

| Serial Channel | Data Bits | Format |

|----------------|-----------|--------|

| Y0             | D0        | Red0   |

|                | D1        | Red1   |

|                | D2        | Red2   |

|                | D3        | Red3   |

|                | D4        | Red4   |

|                | D6        | Red5   |

|                | D7        | Green0 |

| Y1             | D8        | Green1 |

|                | D9        | Green2 |

|                | D12       | Green3 |

|                | D13       | Green4 |

|                | D14       | Green5 |

|                | D15       | Blue0  |

|                | D18       | Blue1  |

| Y2             | D19       | Blue2  |

|                | D20       | Blue3  |

|                | D21       | Blue4  |

|                | D22       | Blue5  |

|                | D24       | Hsync  |

|                | D25       | Vsync  |

|                | D26       | Enable |

表 1——三线 7:1 LVDS 数据

通常情况下，发送器将发送串行数据到接收器件，如 LCD 屏。然后 LCD 屏将对这 3 或 4 条 LVDS 通道进行解串。如前所述，串行信号表示红、绿、蓝以及控制位。当使用 4 条 LVDS 通道进行发送，那么每个 RGB 像素将有 8 位数据和相关的控制位。不论是 21 位还是 28 位的视频数据，LCD 使用该 RGB 数据将相应的图像显示在屏幕上。有关显示接口（7:1 LVDS 接口、Flatlink、Camera Link 或 Channel Link）的进一步详细信息，请参阅参考设计文件 RD1093 : MachXO2 显示接口。

## ***MachXO2 特性支持显示接口 (7:1 LVDS)***

可以使用几种设计技巧来实现显示接口。一般的方法是接收输入时钟，乘以 7 得到每个数据位的时钟。在实际中，这是相当困难的，因为时钟运行速度极快。典型的显示接口的

时钟频率为 60-100MHz 或更高，乘以 7 得到频率为 420-700Mhz。由于印刷电路板增加了走线延迟变化、电容、噪声等，因此该接口对于整个设计而言是一个重大的挑战。

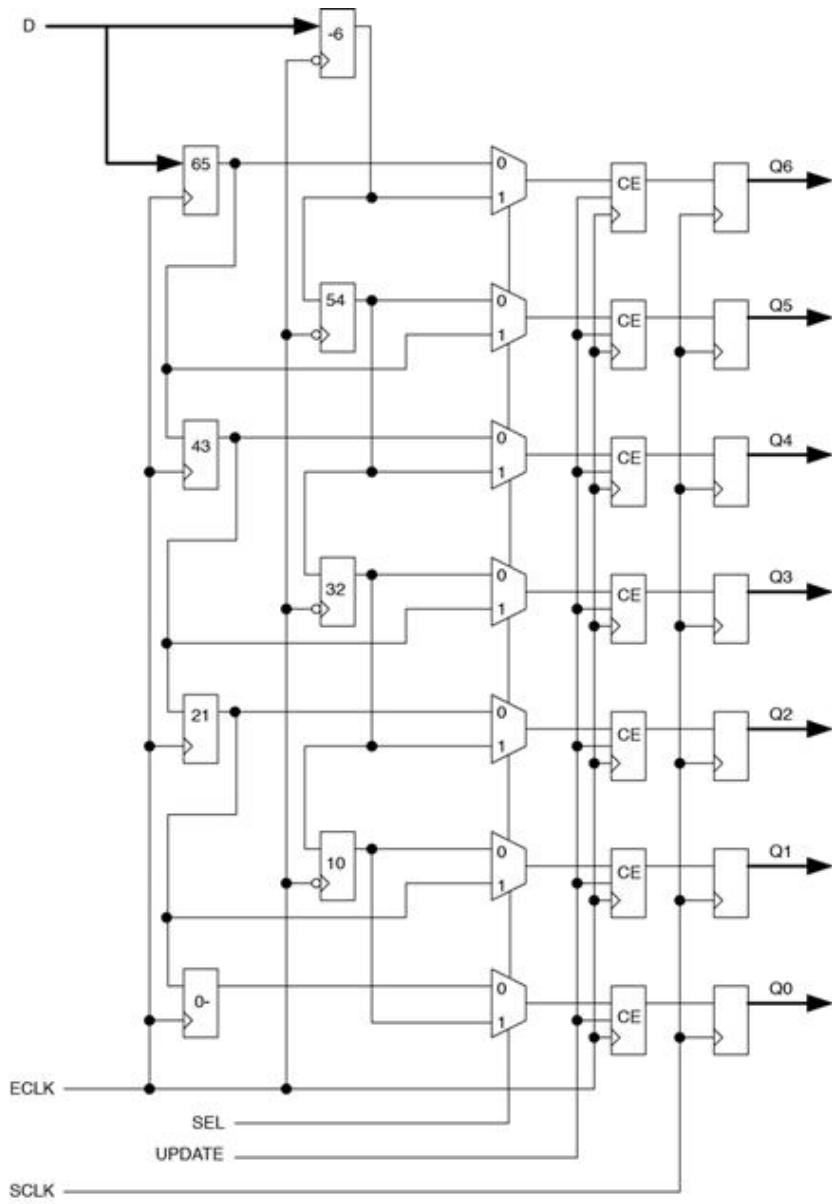

MachXO2 结构设计具有特定功能用以支持显示接口。包括双倍数据速率 (DDR) I/O 寄存器、I/O 寄存器 **gearing** 逻辑和 3.5 分频的专用时钟分频器。事实上，MachXO2 有特定的 7:1 输入和输出 I/O bank 以及软件宏，使这个实现非常简便。在 MachXO2-1200 和更大的器件中，底部的 I/O bank 支持显示器接口输入，顶部的 I/O bank 支持显示输出。我们将进一步详细研究每种结构特性。

MachXO2 中的 DDR I/O 寄存器允许显示接口使用半速的接口数据速率提供时钟。例如，如果显示接口的像素时钟频率为 100MHz，使用 DDR I/O 寄存器允许时钟在两边以 350MHz 运行，而不是一个 700Mhz 的时钟。器件中的 PLL 时钟乘以 3.5 并且两边都可以作为数据通道的时钟。这降低了时钟速率，支持更高的吞吐速率。MachXO2 可以支持高达 108MHz 或 756Mbps 的吞吐量的最高时钟速率。

I/O 寄存器 **gearing** 逻辑执行了从 DDR I/O 获得输出并且时分复用到更宽的总线。与 DDR I/O 一起工作，寄存器 **gearing** 逻辑的输出是 7 位宽的数据总线，由一条 7 倍于其他数据线速率的数据线产生。例如，如果一条数据线的速率是 560Mbps ( $7 \times 80\text{MHz}$ )，那么寄存器 **gearing** 逻辑的输出将时分复用为 7 位，运行速率为 80MHz。如果显示接口有四条数据线，那么寄存器 **gearing** 逻辑的输出将为 28 位内部数据，数据速率与外部时钟速率相同。请参见图 2，DDR I/O 寄存器和 I/O 寄存器的 **gearing** 逻辑。

图 2——DDR I/O 寄存器和 I/O 寄存器的 Gearing 逻辑

通过专用的 3.5 时钟分频器准确地转换倍乘的输入时钟，因此 I/O 寄存器 gearing 输出可以可靠地用作 FPGA 结构的时钟。由于这个分频器，I/O gearing 可以保证将数据从 I/O 传输到 MachXO2 PLD 结构。尽管这可能看起来奇怪，在输入时钟上使用一个 PLL 乘以 3.5，再使用专用分频器除以 3.5，但这样做是有好处的。如果不使用这个专用分频器，原始输入时钟或其他 PLL 输出将直接输入到 I/O 寄存器 gearing 逻辑的输出。设计人员必

须仔细地进行时钟布线，以确保 21-28 个数据位之间最小的时钟偏移或不同的延迟。此外，接口速率会受到时钟偏移的影响。专用分频器也不会消耗任何其他的系统资源，如另一个 PLL 输出。使用专用分频器，确保了时钟域转换时序和从 I/O gearing 逻辑接口到 MachXO2 结构。有关支持显示接口的 I/O 功能的进一步详细信息，请参见 [TN1023](#)（MachXO2 高速源同步和存储器接口）。

## 显示接口设计示例

除了 MachXO2 之外，莱迪思还为各种 FPGA 器件的显示接口同时提供了发送（Tx）和接收（Rx）功能（请参见 [RD1030 – LatticeECP3, LatticeECP2/M, LatticeXP2 7:1 LVDS 视频接口参考设计](#)）。由于大量的莱迪思器件都可以实现 7:1 LVDS，因而可以支持嵌入式或消费电子设计中的各种显示应用。MachXO2 系列的显示接口（7:1 LVDS 接口）使其成为电池供电的产品和所有较低成本产品的理想选择，如笔记本电脑、上网本等。

MachXO2 是实现显示接口的一种低成本、低功耗的解决方案。

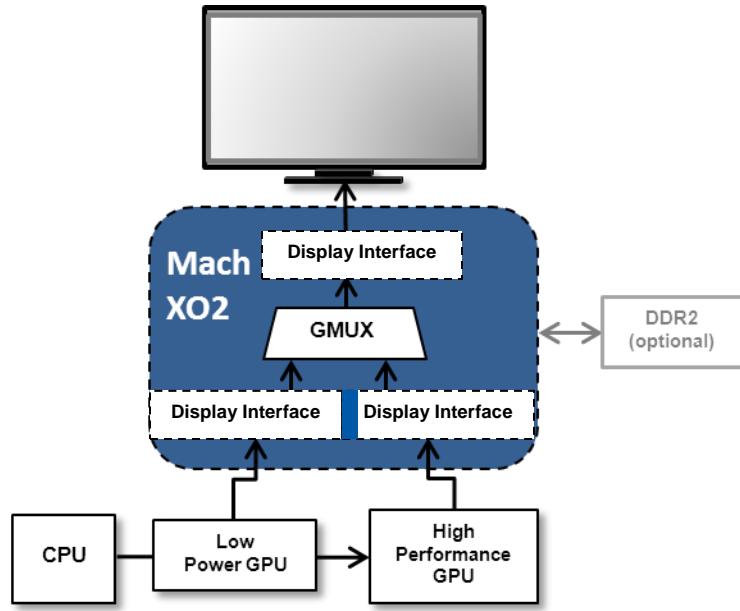

笔记本电脑上常见的一个显示接口应用是图形多路复用控制器，或 GMUX。GMUX 只是简单地用来选择两个图形控制器中的一个来驱动 LCD 屏幕。这是高分辨率的笔记本电脑屏幕的最常用功能。这些笔记本电脑有两个视频源可驱动 LCD 屏幕。两个图形控制器共享一个 LCD 屏幕。通常一个控制器进行了优化或内置到一块处理器芯片中，用于低功耗和要求不高的如文字处理等任务。另一个图形控制器是专为高性能和更密集型显示应用而设计的，如游戏或视频编辑。请参见图 3 了解更多详细信息。

图 3——图形多路复用控制器

通过实现两个显示接口 Rx 接口并多路复用到 MachXO2 器件中的显示接口 Tx 输出，可以为笔记本带来以下几个好处：

1. 分立的图形多路复用器使得 PC 供应商不必使用特定公司的图形交换标准。并非所有的处理器和图形处理器的都是设计为无缝协同工作的。例如，如果一个特定的英特尔微处理器是最好的 CPU 选择，而高性能 AMD GPU 是最佳的图形处理器，那么 GMUX 就促成了这两者的结合。

2. 第二，还可以灵活地决定何时以及如何切换到图形处理器。一台笔记本可以在检测到连接上 HDMI 线后使用更高性能的 GPU，然后拔掉线后再恢复到低功耗的 GPU。另外，如果显示数据存储在小缓冲器中，如 DDR2 存储器，切换可以在运行时实现。这确保了用户不会感觉到切换的变化，并且不需要系统重启。

最后，分立的 GMUX 还将允许系统关断不使用的图形控制器。实际上，笔记本电脑中的一些自动切换图形机制从不关断集成的控制器电源。它们低效地使得更高性能的 GPU 上电并重写从集成图形控制器中获得的帧缓冲器的数据。通过将低功耗的 MachXO2 器件用于 Gmux 功能，您可以关断图形处理器从而最大限度地延长电池使用时间。

## 总结

本白皮书提供了显示接口的详细介绍和 MachXO2 器件可实现该接口的功能，以及设计实例。MachXO2 器件的丰富结构特性与其超低功耗和低成本相结合，使它成为实现显示接口（7:1 LVDS）的极具吸引力的选择。下表列出了所有可用的莱迪思器件系列，以及支持这些应用的文档。

| Supported Device Families for 7:1 LVDS |                                                |                                                |                                                |

|----------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|

| <b>MachXO2</b>                         | <b>ECP3</b>                                    | <b>ECP2M</b>                                   | <b>XP2</b>                                     |

| TN1203                                 | <a href="#">RD1030</a>                         | <a href="#">RD1030</a>                         | <a href="#">RD1030</a>                         |

| RD1093                                 | <a href="#">TN1134</a><br><a href="#">UG37</a> | <a href="#">TN1134</a><br><a href="#">UG37</a> | <a href="#">TN1134</a><br><a href="#">UG37</a> |

[TN1023](#) – MachXO2 高速源同步和存储器接口技术说明

[RD1093](#) – MachXO2 设计接口参考设计

[RD1030](#) – LatticeECP3, LatticeECP2/M, LatticeXP2 7:1 LVDS 视频接口参考设计

[TN1134](#) - 7:1 LVDS 到 DVI 技术说明

[UG37](#) – 适用于 7:1 LVDS 到 DVI 演示示例的用户指南