# Reducing Cost and Power in Consumer Applications Using PLDs

在消费电子应用中使用 PLD 来降低成本和功耗

莱迪思白皮书

2010年11月

Lattice Semiconductor 5555 Northeast Moore Ct. Hillsboro, Oregon 97124 USA Telephone: (503) 268-8000

www.latticesemi.com

# *简介*

为了在较短时间内满足不断变化的市场标准要求,各种消费电子应用开始广泛使用可编程逻辑器件(PLD)。专用集成电路(ASIC)和专用标准产品(ASSP)的开发需要高额的非重复性工程费用,而 PLD 是标准的现成产品,可以使用灵活的软件工具为各种不同应用进行定制。不同于 ASIC 和 ASSP,PLD 不需要很长的订货至交货时间:它们的功能可以随时进行更改以适应产品需求的变化。在许多市场,如手持设备等,已经开始采用 PLD,因为其新的产品结构可以降低功耗,提供新的封装选择和更低的单位成本。

### 消费电子应用——趋势和挑战

#### 降低成本

根据 iSuppli 的预测,2010 年消费电子产品的销售收入预计将达到 2590 亿美元,标志着前几年市场低迷期的结束。并且在这一强劲趋势下,未来几年的销售收入将继续上升,2011 年预计增长 6.7%,2012 年增长 7%。大批量产品的销售推动了收入的增长,如蓝光 DVD 播放机、液晶电视机、机顶盒、数码相机、智能手机和GPS 设备等。与此同时,新产品的设计需要满足新兴市场的需要,在大幅调低价格的同时,消费者在购买时还在寻求更高的价值和功能。因此,设计人员正不断面临着压力,需要提供具有更高系统集成度和更低价格的产品。

## 降低功耗预算

降低静态功耗一直是消费电子应用设计人员面临的挑战。对于许多使用电池供电的应用来说,如智能电话、GPS设备、移动计算和数码相机,延长电池供电时间是最重要的产品差异化特征之一。对于许多通过墙面插座供电的电子设备而言,低功耗也变得越来越重要,因为设计人员需要遵守最新的 EnergyStar 和欧盟行为守则的规定。

#### 缩短产品生命周期

消费电子市场正在飞速发展,正如现在不断涌现的新标准,提高了消费电子产品的质量并降低了其成本。发展的两大趋势——有线和无线器件宽带接入的激增,以及多媒体和数据的融合——推动了这些新标准的制定。

制造商们承受着巨大的竞争压力,需要做到第一时间将具有差异化特性的产品推向市场。然而,一个成功的产品会迅速吸引仿冒的竞争者,从而导致产品迅速跌价。为了保持竞争的领先优势,消费电子产品制造商被迫不断提升其产品或支持新兴的技术。基于这些原因,目前消费电子产品的生命周期显著缩短。

## PLD 在消费电子应用中的使用

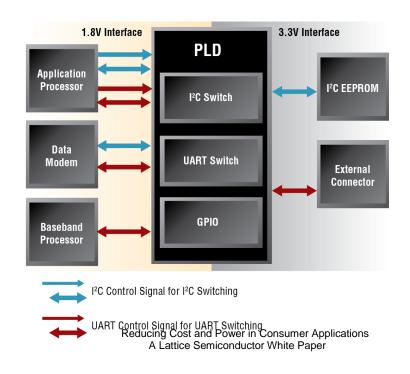

使用改进的结构降低了功耗,新的更小尺寸的封装,更低的单位成本以及高度的产品差异化,PLD 越来越多地用于消费电子应用。在许多消费电子系统中,PLD 可通过提供高级的总线接口和桥接功能,扩展了现代应用处理器或 CPU 的使用。这些总线接口和桥接功能通常没有非常高的性能要求。图 1 显示了一个这类应用的实例。

#### 图 1: PLD 在移动电话中的使用

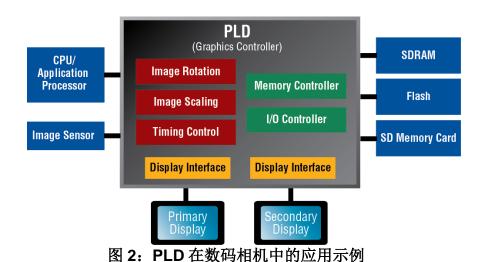

PLD 还经常用来实现人机接口控制器、显示控制器、外部存储器接口控制器和 PWM 控制器。表 2 显示了在消费电子领域的一些常见的 PLD 应用。有时通过两个或更多的功能相结合来解决一个特定需求;这类应用实例如图 2 所示。

| PLD 功能     | 示例应用                                                     |  |

|------------|----------------------------------------------------------|--|

| 人机接口控制器    | 键盘矩阵解码器,数字触摸屏控制,中断管理器                                    |  |

| 显示控制器      | 图像旋转,图像缩放,LCD 控制,显示接口复用/解复用器                             |  |

| 外部存储器接口控制器 | 安全数字(SD)存储器控制器,紧凑型闪存<br>(CF)存储器,记忆棒,DDR/DDR2/LPDDR存储器    |  |

| PWM 控制器    | LCD 背光控制,步进电机控制                                          |  |

| 总线接口和桥接    | I <sup>2</sup> C, SPI, UART, I <sup>2</sup> S, USB, SDIO |  |

表 1: 在消费电子应用中常用的 PLD 功能

Reducing Cost and Power in Consumer Applications A Lattice Semiconductor White Paper

现在的低密度 PLD 如高端的 FPGA 那样,拥有了先进的 I/O 功能,包括支持不同的 I/O 标准、多个 I/O bank 以及多种电压。这些特性使得 PLD 可以用来实现 ASIC/ASSP、存储器、处理器和其他器件之间的非互连逻辑,这些器件之间通常会出现电压和 I/O 标准不匹配。

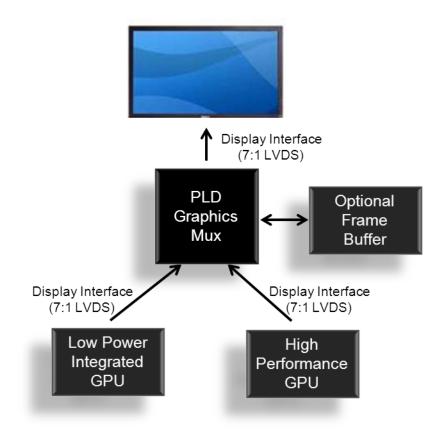

如图 3 所示,图形复用器是适用于高级互连逻辑的低成本、低密度 PLD 的理想示例。在笔记本电脑和便携式功耗管理方面的最新趋势是英特尔的物理显卡切换技术。图形多路复用器根据应用需求选择图形控制器。低功耗集成的图形处理器(GPU)是用于诸如文字处理、电子邮件和互联网浏览等常规应用。高性能的独立 GPU 是用于诸如游戏、视频编辑和高清视频播放的高性能应用。支持低摆幅差分 I/O 标准、内置的 gear box 和 PLL 使得 PLD 可以接口到图形处理器,从而实现智能多路复用算法,以减少或消除开关引起的视觉失真并且直接驱动 LCD 显示屏。

图 3: 基于 PLD 的图像多路复用器

莱迪思的 MachXO2 PLD 系列是实现上述消费电子应用中常用功能的理想选择。结合优化的查找表(LUT)结构和 65-nm 嵌入式闪存工艺技术,MachXO2 器件为消费电子设计提供了一个灵活的"全功能"解决方案。

#### 使用 MachXO2 器件降低成本

#### 焊盘受限的设计

过去,对大批量、价格敏感的应用而言,PLD 并不是成本最低的解决方案。然而,由于 ASIC 和 PLD 都开始变得焊盘数量受限,这一情况开始改变。在焊盘受限的设计中,裸片的大小仅由所需的 I/O 焊盘数量决定,而不受到内核逻辑大小的影响。价格最终是由裸片尺寸决定的——当器件焊盘受限后,定制和可编程产品之间的价格差异开始缩小。MachXO2 器件设计成焊盘受限。根据器件密度,I/O 焊盘以两排或三排交错的 I/O 环放置,实现确定 IO 数下的最小裸片大小。

#### 低成本封装

MachXO2 器件有各种低成本、无卤素封装。可用的封装选择包括低成本的 BGA和 TQFP,以及先进的晶圆级芯片级封装和微型芯片级封装。BGA 封装包含尽可能少的信号布线层,以降低封装总成本。这些封装设计使得所有的 I/O 和电源连接可以引到 2 至 4 层的印刷电路板布线。这样做避免了需要使用成本较高的印刷电路板制造技术,如埋孔、盲孔或者激光钻孔。MachXO2 封装上的 I/O 分配还实现了同一封装下的密度迁移。这有助于当需要一个更大或更小的 MachXO2 器件时,可以通过可行的设计更改仍使用同一块电路板。

## 功能集成

设计人员经常面临着需要支持更高的功能性来降低总成本的挑战。分立器件增加了成本、电路板面积要求和系统的总功耗预算。分立器件还降低了电路板可靠性。所有这些因素使得消费电子应用希望能拥有更高的功能集成。

MachXO2 器件通过单芯片解决方案实现了高度的系统集成,不需要外部配置存储器、外部用户闪存或 EEPROM 和振荡器,实现了更小的电路板面积、更少的元器件数量和更低的系统总成本。

图 4 显示了在一个 MachXO2 器件中集成了分立逻辑,诸如 I/O 扩展器、电压级和总线桥接转换器、电压调节器、时钟源和配置器件。

图 4: MachXO2 功能集成

#### 集成外部非易失性存储器

MachXO2 器件包括多达 256Kbit 的嵌入式闪存。这个片上用户闪存(UFM)使 MachXO2 器件集成了外部非易失性存储器,并且可用于各种应用,包括存储部分 配置、存储 PROM 数据,或用作通用用户闪存。

#### 减少振荡器的数量

MachXO2 器件带有精度为+/- 5%(标称值)的内部振荡器,可以用作设计中的时钟源,省去了一个外部振荡器。

#### 固化的 SPI、I2C、定时器/计数器

SPI和 I<sup>2</sup>C 控制器和定时器/计数器是消费电子设计中最常见实现的功能。设计人员经常需要在 PLD 中实现 SPI 或 I<sup>2</sup>C 总线扩展。定时器/计数器也经常被用来产生状态信号。所有 MachXO2 器件包括这些常用的功能的固化实现。使用固化的 I<sup>2</sup>C、SPI 和定时器/计数器功能,设计者可节省多达 600 LUT,可用于设计中其他逻辑的实现。表 2 显示了可以通过固化常用的控制功能,从而节省的逻辑需求。

| 功能                  | PLD 需要的 LUT 数<br>(典型值) | MachXO2 器件需要<br>的 LUT 数(典型<br>值) |

|---------------------|------------------------|----------------------------------|

| SPI 主控              | 115                    | 0                                |

| I <sup>2</sup> C 主控 | 234                    | 0                                |

| 定时器/计数器             | 50-80                  | 0                                |

表 2: 使用固化的 I<sup>2</sup>C、SPI 和定时器/计数器功能所节省的逻辑需求(典型值)

# 使用 MachXO2 器件降低功耗预算

## 静态和动态功耗

PLD 的总功率为两个功耗的和:静态功耗和动态功耗。静态功耗主要是器件中的晶体管漏电流引起的。漏电流是小额电流"泄漏",无论是从源极到漏极或通过栅氧化层,甚至即使在晶体管逻辑"关断"时。动态功耗是内核或器件 I/O 开关所消耗的功耗,因此与频率和用户逻辑相关。

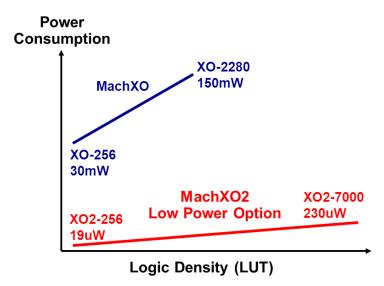

静态功耗取决于 PLD 设计本身,并且与应用设计无关。MachXO2 PLD 通过创新的工艺、电路设计和结构水平,实现最低的静态功耗。这些措施包括了使用低功耗的 65 纳米工艺、可变沟道长度、优化的晶体管选择以及改进的默认布线和算法,实现了 256 LUT 低至 19uW 的待机功耗。图 5 显示了 65-nm MachXO2 和 130-nm MachXO 器件的静态功耗比较。

图 5: MachXO2 和 MachXO PLD 之间的静态功耗比较

由于动态功耗由某个时刻开关的节点数决定,因此更多地与设计相关。设计人员可以使用各种技术来降低动态功耗。例如,可以在时钟树源而不是在每个终端来使能时钟,从而尽量减少系统中的时钟转换。I/O对动态功耗也有很大影响。使用LVTTL/LVCMOS标准和较低的I/O电压有助于降低功耗。使用低摆幅差分信号也降低了动态功耗。MachXO2器件提供了各种结构特性来降低动态功耗,如功耗控制器、I/O bank 控制器、动态时钟使能、power guard 和可编程低摆幅差分信号。

#### 由于非易失性而获得的更低功耗

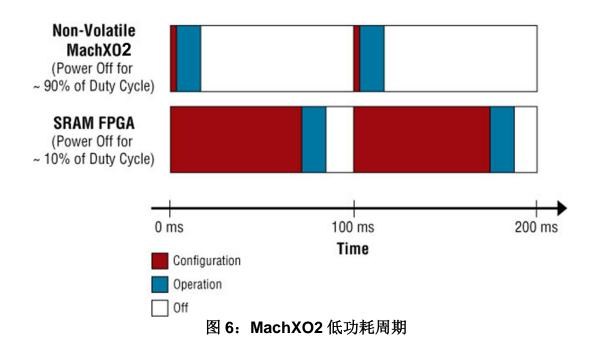

除了静态和动态功耗之外,还有浪涌和配置引起的额外功耗。这是 PLD/FPGA 进入用户模式之前,上电和配置过程中的功耗。所需功耗与进入用户模式所需的时间成正比。电路板设计人员必须在决定功耗需求时考虑到这部分额外的功耗。许多消费电子系统设计需要 FPGA 或 PLD 有频繁的开/关周期。由于频繁的开/关这一系统特性增加了额外功耗。因为 MachXO2 器件固有的特性(即带有片上配置存储器的 PLD),该器件可以用微秒来配置,尽量减少浪涌和配置过程中的功耗。图 6显示了 MachXO2 PLD 和基于 SRAM 的 FPGA 进入用户模式所需时间的比较。

# *使用免费的设计工具进行快速创新*

设计人员可以开始使用 Lattice Diamond v1.1 软件进行 MachXO2 器件设计,该软件可从莱迪思网站免费下载。此外,还可以使用免费的带有安装的控制包的 ispLEVER® v8.1 SP1 Starter 软件,该软件也可以从莱迪思网站下载。

一整套专为消费电子应用而优化的参考设计可以从莱迪思网站免费下载。包括(列举一些消费电子参考设计)。参考设计源代码,包括 HDL 和固件,可以根据实际应用的要求进行修改。欲了解更多有关参考设计的信息,请访问

http://www.latticesemi.com/ip

# <u>总结</u>

PLD 是实现消费电子应用中许多功能的一种很好的选择,因为它们通过提供成本有效、低功耗和灵活的解决方案,克服了 ASIC 和 ASSP 的局限性。MachXO2 PLD 系列是专为低成本、低功耗的消费电子应用而设计的,并且给设计人员带来

了诸多好处,包括更低成本、更低功耗并在小尺寸封装中实现了更高的系统集成。此外,MachXO2 器件包含了消费电子应用中最常用的一些功能的固化实现,例如用户闪存(UFM)、I<sup>2</sup>C、SPI 和定时器/计数器。