# 在系统应用中使用低成本、非易失性可编程逻辑 器件

莱迪思半导体公司白皮书 2010年11月

Lattice Semiconductor 5555 Northeast Moore Ct. Hillsboro, Oregon 97124 USA Telephone: (503) 268-8000

www.latticesemi.com

# 引言

系统市场由许多应用所组成,如电信基础设施、计算、高端产业和高端医疗设备。在这些应用中,电源定序、电压和电流的监测、总线桥接、电平转换、接口控制,温度测量是典型的电路板功能。系统设计人员面临着不断受到的压力,以实现他们的开发计划,以及需要以最少的工作量和最小的风险实现设计,同时保持最大的灵活性。通过使用基于可编程的方法取代一些分立器件或特殊应用标准产品(ASSP),设计人员可以加速将产品推向市场,解决系统成本和减少空间的问题,并确保高水平的产品差异化。

## 在典型系统应用中使用 PLD

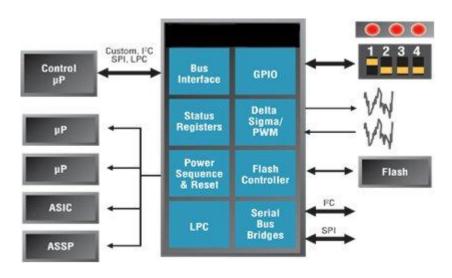

图 1 展示了在典型系统应用中使用 PLD 实现一些功能,如存储器接口控制、电源定序和 复位,以及串行接口控制。

图 1 使用 PLD 的典型系统应用

在此应用中,PLD以不同的电平与微控制器、ASIC、 ASSP,LED 和闪存进行通信。通过 I2C,SPI 或 LPC 接口,微控制器通过 PLD 的寄存器组监测系统的状态。通过 LED,PLD 提供状态指示,并控制接口至闪存。 PLD 管理上电时序,复位几个 IC 并提供至模拟信号的接口。此外,通过串行总线桥与电路板上的其他元件进行通信。

# 系统应用的挑战

典型的系统应用挑战包括以下几个方面:

# 与多个器件接口

由于电路板上的器件数量不断增加,需要与这些器件之间接口的 I/O 数量也相应增加了。PLD 可用于对多个器件进行监测并对许多信号进行控制。此外,他们还可以与微控制器或 ASSP 相结合,以增加可用的用户 I/O 数量。通过采用先进的工艺节点,PLD 内的逻辑、存储器,锁相环和其他核功能的尺寸明显减少,但 I/O 结构仍大致相同,因为它需要特殊的电路,例如 ESD,这不能从缩小工艺尺寸中得到好处。这就导致焊盘受限的设计。

# 在噪声环境中可靠工作

在系统应用中的主要要求之一是有效地管理电路板上器件的上电和断电时序。这推动了一些独特的要求,包括即时启动、支持输入迟滞, 3.3V 单电源供电和单芯片解决方案。

# 即时启动

总线桥接和控制逻辑功能必须在系统内的其他器件上电之前工作。这包括能够控制其他器件以特定的时序供电的功能,以确保它们能够正确运行。

# 输入滞后

由于板级布线资源的大量使用,系统应用中经常产生低摆率信号。对于缓慢上升的输入,具有输入滞后的器件提供了噪声免疫力,提高了系统的整体可靠性。

# 3.3V 电源

在系统应用中,典型的 PLD 的工作要用辅助电源,因为在电源供电周期中它是首先上电,最后一个关断的。对于许多系统,辅助电压是 3.3 伏。直接用这个电压工作省去了这项费用,以及一个额外的稳压器元件。

# 单芯片

通过独立工作及尽量减少元件的数量,不需要额外 PROM 或配置器件的可编程器件有助于系统的可靠性。

# 通过功能整合使电路板的面积减少

针对改变特性和标准,为了满足客户的需求,设计人员经常面临着支持差异化特性的高级功能的挑战,同时试图减少整个系统的成本。分立器件和 ASSP 不提供所需的差异化特性,且增加了材料清单(BOM)的费用并占用了大量的电路板面积。专用集成电路(ASIC)提供定制和功能的集成,但会对交货时间不利,并由于其昂贵的掩模集增加了开发成本。提供功能集成和产品差异化的解决方案,同时节省电路板面积和降低成本正在系统市场中受到青睐。

#### 使用 MachXO2 可编程逻辑器件实现系统功能

莱迪思的 MachXO2 PLD 系列对实现上面提及的系统应用中使用的功能是理想的选择。 将优化的查找表(LUT)结构和 65 纳米嵌入式闪存工艺技术结合在一起,MachXO2 器件为系统设计提供了一个灵活的"全功能"解决方案。

MachXO2 器件使系统设计人员能够用大量的低成本 I/O 以不同的电平进行接口,提高了整个系统的鲁棒性,提供了更多的功能集成,所有的特性都在单个器件之中。

下面阐述解决系统设计挑战的 MachXO2 系列的特性和优点。

# 大量的低成本 I/O

MachXO2 器件有多种封装选择,提供了多达 335 个用户 I/O。除了全面支持 I/O 标准的预置源同步 I/O,还有几个特点,如默认的下拉,热插拔及输入滞后使设计实现更加灵活。

#### 三重交错的 I/O 焊盘

MachXO2 器件被设计成焊盘受限。根据不同的器件密度,给定 I/O 数量的的裸片尺寸,I/O 焊盘以两排或三排交错的 I/O 环形式放置。这对诸如与逻辑功能相比,需要较高比例 I/O 的电压转换,总线桥接和接口控制特别有吸引力。

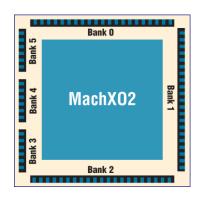

## 不对称的 Bank 方案

系统应用通常使用数量有限的其他 I/O 电压和标准的 3.3V LVCMOSI/O。对于对称的 I/O bank,设计人员经常发现对低电压未能充分利用 I/O bank。 MachXO2 器件提供非对称的 I/O bank,使设计人员可以最大限度地提高 I/O 的使用率。这对电平转换和桥接功能有益,数量有限的 I/O 需要不同的电源电压,以提供最大限度的灵活性和 I/O 使用率。

图 2 在 MachXO2- 2000, 4000 和 7000 器件中非对称的 I/O Bank

#### 低成本 BGA 封装

MachXO2 系列提供各种低成本封装选择,以节省空间、每个 I/ O 的成本和制造费用。使用电气模拟来确定最低成本的基板设计功能,使封装能够支持器件的性能指标。这些封装设计使得所有的 I/O 和电源连接可以引到 2 至 4 层的印刷电路板布线。这样做避免了需要使用成本较高的制造技术,如埋孔、盲孔或者激光钻孔。MachXO2 封装上的 I/O 分配还实现了同一封装下的密度迁移,消除了倘若要进行设计变更而设计一块新电路板所需的成本和交货期。

# 稳定的设计

MachXO2 系列的几个特性有助于设计的稳定性,以及在噪声环境中的功能,这些特性如下:

## 不到 1ms 的瞬时启动

在同一器件中 Flash 和 SRAM 的组合为远程现场升级,瞬时启动非易失性的操作提供了显著的优势。上电时,SRAM 配置位加载到器件的非易失性存储器,能够在上电后小于 1ms 立即运行。

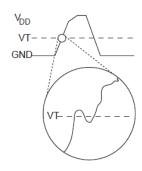

## 输入滞后

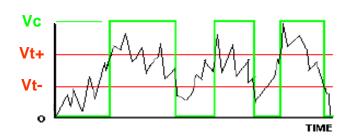

在输入路径和输入缓冲器中固有的寄生电容,电阻,和电感会导致区输入信号有无限量的 上升或下降时间。如图 3 所示,如果输入信号变得过于缓慢,器件输入电压阈值周围的 噪声会导致多个状态的变化。

图 3 围绕输入电压阈值的噪声

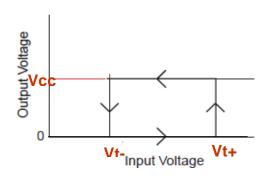

MachXO2 器件的施密特触发缓冲器能够使一个缓慢变化的或有噪声的信号在传递到 PLD 核之前转换成一个干净的信号,能够在噪声环境中可靠的工作。施密特触发缓冲器具有如图 4 所示的滞后传输功能。

图 4 迟滞曲线

当输入电压从 0V 向更低的阈值变化时,输出将保持在 0 伏特。只有当输入超过更高的阈值,输出会跳变到 Vcc。在这一点上,减少输入电压不会导致输出立即降至零。只有当输入电压降低到更低的阈值电压时输出才会下降至零。滞后理论应用到噪声信号的情况如图 5 所示,从一个缓慢变化的有很大噪声的输入恢复出一个几乎完美的输出。

图 5 应用迟滞理论至噪声信号

#### 默认下拉 的输入缓冲器

对于 MachXO2 器件的 I / O 端默认状态是下拉。对默认上拉(毛刺状态)造成的问题起到保护作用,这与电路板上的的复位或高电平信号触发相关。

#### 单电源工作

MachXO2 器件只需要一个电源。它们可直接用一个电压工作,避免了需要使用额外的稳压器,从而减少了元件数量并提高了系统的可靠性。

## 单芯片

MachXO2 器件将 SRAM 和闪存配置存储器整合在同一器件之中,无需器件配置所需要的 PROM 和/或额外的存储器。

# 高级的功能整合

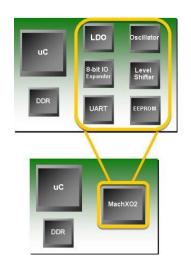

MachXO2 器件由于其结构属性而有很高的系统集成度,如片上用户闪存(UFM)、振荡器、PLL 和固化的 I2C、SPI 和定时器/计数器功能,从而减少了电路板的面积,元件数量和系统的总成本。

图 6 展示了离散逻辑的集成,如 I / O 扩展器、电平和总线桥接转换器、电压调节器,时钟源和配置器件,所有这些功能都在单个 MachXO2 器件之中。

图 6 MachXO2 的功能整合

# 整合外部非易失性存储器

MachXO2 器件内含多达 256Kbit 的嵌入式闪存。这些片上用户 Flash 存储器(UFM)使 MachXO2 器件集成了外部非易失性存储器,可用于多种应用,包括存储配置的一部分,储存 PROM 数据或作为一般用途的用户闪存。

#### 减少振荡器的数量

MachXO2 器件具有内部振荡器,其标称精度为+/-5%,可以用来作为设计的时钟源, 省去了需要使用外部振荡器。

## 固化的 SPI、 I2C、定时器/计数器

在系统设计中,SPI、I2C 控制器和定时器/计数器是最常见的功能。设计人员经常在 PLD 器件中实现 SPI 或 I2C 总线的扩展。定时器/计数器也经常被用来生成状态信号。所有 MachXO2 器件包括这些常用功能的固化实现。有了固化的 I2C,SPI 和定时器/计数器功能,设计人员可节省多达 600LUT,可用于在设计中实现其他的逻辑。表 1 展示了所节约的逻辑资源,通过固化来实现这些常用的控制功能。

| 功能         | PLD 中所需的典型 LUT | MachXO2 中所需的典型 |

|------------|----------------|----------------|

|            |                | LUT            |

| SPI Master | 115            | 0              |

| I2C Master | 234            | 0              |

| 定时器/计数器    | 50-80          | 0              |

# 表 1 用固化的 I2C, SPI 和定时器/计数器节省的典型 LUT

# 加快开发时间的免费设计工具

设计人员可以开始用 Lattice Diamond 1.1 版软件进行 MachXO2 器件的设计,软件可以免费从莱迪思网站下载。此外,设计人员还可以使用免费的带有安装控制包的 ispLEVER® v8.1 SP1 Starter 软件,也可以从莱迪思的网站上下载。

可以从莱迪思网站免费下载全面的针对系统应用而优化的参考设计套件。

表 2 展示了针对系统设计而优化的 MachXO2 参考设计。

| 系统管理      | 处理器和外设                                |

|-----------|---------------------------------------|

| 控制链接串行接口  | Lattice Mico8 微控制器                    |

| 增量累加 ADC  | LCD 控制器 (WISHBONE 兼容)                 |

| PWM 风扇控制  | 针对 EEPROM 的 I2C 总线控制器                 |

| I2S 控制器   | SPI 控制器(WISHBONE 兼容)                  |

| PMBUS 控制器 | I <sup>2</sup> C Master (WISHBONE 兼容) |

| 单线温度传感器接口 | UART WISHBONE 兼容                      |

| SMBUS 控制器 | LED/OLED 驱动器                          |

| 存储器控制器           |

|------------------|

| 紧凑闪存             |

| 快速页模式 SDRAM      |

| NOR 闪存           |

| 带有 SD 总线的 SD 控制器 |

| NAND 闪存          |

| SDR DRAM         |

| 具有损耗均衡的闪存控制器     |

表 2 针对 MachXO2 器件的参考设计

# 结论

MachXO2 PLD 通常是在电信基础设施、计算、高端工业及高端医疗应用中实现系统功能的理想选择。他们为降低整个系统的成本提供了几个重要的好处。免费的设计工具和参考设计为设计者提供一个全面和方便的解决方案,以加速系统设计的速度和效率。