# **Wafer-Level Chip-Scale Package Guide**

# **Technical Note**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults and associated risk the responsibility entirely of the Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

### **Contents**

| Acronyms in This Document4                                  |        |

|-------------------------------------------------------------|--------|

| Acronyms in This Document4  1. Introduction                 |        |

| 2. WLCSP Shipping Options5                                  |        |

| 3. WLCSP PCB Layout and Considerations6                     |        |

| 4. WLCSP Solder Reflow and Rework6                          |        |

| Technical Support Assistance                                |        |

| Revision History8                                           |        |

|                                                             |        |

|                                                             |        |

|                                                             |        |

|                                                             |        |

| Figures                                                     |        |

| Figure 1.1. 25-Ball WLCSP Package (Actual Size: 2.5x2.5 mm) | 5<br>5 |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym | Definition                     |

|---------|--------------------------------|

| IC      | Integrated Circuit             |

| PCB     | Printed Circuit Board          |

| TNR     | Tape-and-Reel                  |

| WLCSP   | Wafer-Level Chip-Scale Package |

### 1. Introduction

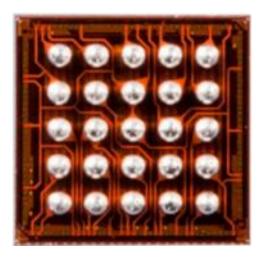

Wafer-level chip-scale packages (WLCSP) are an advanced package style in which the semiconductor integrated circuit (IC) is mounted directly to the printed circuit board (PCB), face-down, by way of solder balls that are attached directly to the IC without the need for an interposer or wirebonds. This enables the use of a smaller solder ball diameter and tighter ball pitch, as well as a shorter electrical path between the IC and PCB, resulting in improved electrical and thermal performance, as well as reduced package assembly requirements.

Figure 1.1. 25-Ball WLCSP Package (Actual Size: 2.5x2.5 mm)

### 2. WLCSP Shipping Options

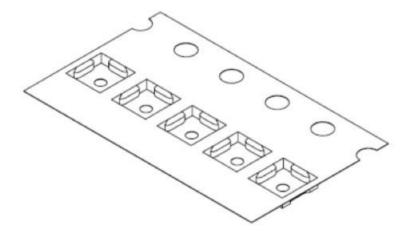

WLCSP devices are offered in 13" tape-and-reel (TNR) shipping configurations except 1000 units per reel smaller devices may use 7" tape-and-reel. Figure 2 shows a typical segment of carrier tape, including the pockets where the individual WLCSP devices would be placed and the sprocket holes for feeding the tape into automated assembly equipment. The devices are placed with the solder balls facing down and pin 1 orientation for all devices in the same location. Adhesive cover tape (not shown) is used to seal the devices in their pockets.

Figure 2.1. Carrier Tape

### 3. WLCSP PCB Layout and Considerations

WLCSP packages are similar to other BGA packages with regard to the PCBs the packages are to be mounted on. PCB layout design and breakout suggestions are outlined in PCB Layout Recommendations for BGA Packages (FPGA-TN-02024). For application-specific assembly guidance, consult the design guidelines of the assembly service provider.

### 4. WLCSP Solder Reflow and Rework

Assembly and rework parameters for WLCSP packages are similar to other BGA packages. Please refer to Solder Reflow Guide for Surface Mount Devices (FPGA-TN-02041), which outlines the reflow parameters for all of the various package styles offered, including WLCSP.

# **Technical Support Assistance**

Submit a technical support case through www.latticesemi.com/techsupport.

# **Revision History**

### Revision 1.1, June 2022

| Section                | Change Summary                                            |

|------------------------|-----------------------------------------------------------|

| All                    | Changed the document number from TN1242 to FPGA-TN-02312. |

|                        | Migrated the document to new template.                    |

| WLCSP Shipping Options | Added the option '7" tape-and-reel' for smaller devices.  |

#### Revision 1.0, June 2011

| Section | Change Summary  |

|---------|-----------------|

| All     | Initial release |

www.latticesemi.com