### ソニーセンサーSub-LVDSパラレル変換ブリッジ

## Sony IMX136/IMX104/IMX036 Sub-LVDSセンサー・インターフェイス

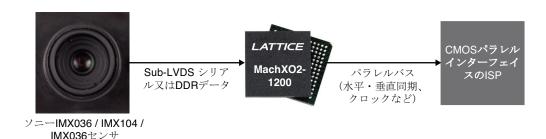

これまでは、簡素なCMOSパラレル・インターフェイスで全ての精細度(画素数)とフレームレートに対応してきました。ソニーが精細度1080Pまでに対応するIMX036センサを市場投入した際に、従来のインターフェイスではもはや帯域幅の要件を満たすことができませんでした。IMX036およびIMX104センサのより広い帯域幅というニーズに対応するために、ソニーはパラレルDDR Sub-LVDSインターフェイスを活用しています。IMX036では10/12ビットパラレルのSub-LVDS DDRインターフェイスが用いられています。

# パラレルSub-LVDSからパラレル・センサインターフェイス変換ブリッジの必要性

殆どのISP(Image Signal Processing、画像信号処理)デバイスは伝統的なCMOSパラレル・センサインターフェイスに対応していますが、通常それらはシリアルSub-LVDSやDDRに対応するインターフェイスがありません。したがってSub-LVDSシリアルデータやDDRパラレル形式を

CMOSパラレル形式に変換するブリッジデバイスが必要です。不揮発性デバイスのMachXO2™-1200やLattice-XP2™-5は、効率的で費用対効果に優れたパラレルSub-LVDSのブリッジ・ソリューションを提供します。

### 主要機能

- 完全な参照デザイン

- 10/12ビットバス幅のパラレルセンサ出力をエミュレートする設計

- Sony IMX036とTI DM814X IPカメラで検証済み

- シリアルSub-LVDSやパラレルDDRデータとインターフェイス

- Sub-LVDS同期コマンドを有効な信号に変換

- 省スペース型8×8mm 132ボールcsBGA封止のブリッジ デバイス。TQFPパッケージも用意

- 外付けPROMは不要

- パラレルインターフェイスは1.8V、2.5Vまたは3.3V LVCMOSレベルのSub-LVDS DDRデータに設定可能

#### Sub-LVDSからパラレル・センサインターフェイス変換ブリッジのブロック図 CLK \_\_\_ PLL CLK\_DIV CLK\_OUT 10-12 DATA\_OUT 2-12 Sub-LVDS DDR Vertical シリパラ変換と 同期コード検 データ SDRへの同期化 出と生成 Horizontal

www.latticesemi.com/sensorbridge で無償の参照デザインをダウンロードしてください

#### アプリケーションサポート

1-800-LATTICE (528-8423) +1-503-268-8001 techsupport@latticesemi.com www.latticesemi.co.jp

Copyright © 2012ラティスセミコンダクター株式会社 Lattice Semiconductor、L (stylized) Lattice Semiconductor Corp.、Lattice (design)およびLatticeXP2およびMachXO2はアメリカ合衆国、またその他の国におけるLattice Semiconductor Corporationの登録商標か商標のいずれかです。本カタログで用いられているその他の製品名は、識別目的のためであり、それぞれ各会社の登録商標であり得ます。