# LatticeECP3 SERDES/PCS

使用指南

2012 年 8 月 技术说明 TN1176

## 概述

LatticeECP3™ FPGA系列结合了高性能FPGA结构、高性能I/O和多达16个通道带有相应的物理编码子层(Physical Coding Sublayer, PCS)逻辑的嵌入式 SERDES。 PCS 逻辑可配置用于支持很多业界标准的、高速串行数据传输协议。

PCS 逻辑的每个通道包含专用的发送和接收 SERDES,可用于高达 3.2 Gbps 的高速、全双工串行数据传输。每个通道的 PCS 逻辑可通过配置来支持一系列常用的数据协议,包括 GbE、XAUI、SONET/SDH、PCI Express、SRIO、CPRI、OBSAI、SD-SDI、HD-SDI 和 3G-SDI。此外,基于协议的逻辑可以在许多配置中被完全或部分绕过,从而使用户在设计自己的高速数据接口时拥有更大的灵活性。

PCS 还提供旁路模式(bypass mode),允许使用 8 位或 10 位接口将 SERDES 直接连接到 FPGA 逻辑。每个 SERDES 引脚还可以独立实施直流耦合并且允许在同一个 SERDES 引脚上同时支持高速和低速工作,适用于如串 行数字视频等应用。

# 特性

- 多达 16 个通道的高速 SERDES

- 150 Mbps 至 3.2 Gbps 用于通用 8b10b, 10 位 SERDES 和 8 位 SERDES 模式。参见表 8-1。

- 所有其他的协议, 230 Mbps 至 3.2 Gbps/ 通道

- 3.2 Gbps 工作时,功耗低至 110mW/通道

- 适用于小尺寸背板工作的接收均衡和发送预加重

- 支持 PCI Express、千兆以太网 (1GbE 和 SGMII)、 XAUI 以及多种其他标准

- 支持用户定义的通用 8b10b 模式

- 适用于低速输入(视频应用)的带外(Out-of-band,OOB)信号接口

- 多种时钟速率支持

- 每个 PCS quad 独立的参考时钟,便于在一个器件内处理多种协议速率

- 全功能嵌入式物理编码子层 (PCS) 逻辑, 支持业界标准协议

- 每个器件支持多达 16 个通道的全双工数据传输

- 单芯片支持多种协议

- 支持通用的基于 8b10b 的数据包协议

- SERDES only 模式允许 8 位或 10 位接口直接连接到 FPGA 逻辑

- 兼容多种协议的时钟容限补偿 (Clock Tolerance Compensation, CTC) 逻辑

- 对参考时钟和接收数据速率之间的频率差异进行补偿

- 允许用户定义的 1、2或4字节长度的跳跃模式

- 集成了回环模式 (Loopback mode), 用于系统调试

- 用于系统调试的三种回环模式

### LatticeECP2M™ 所没有的 SERDES/PCS 的新特性

- 在一个 SERDES quad 中支持多种协议 / 标准。这些标准需支持如表 8-1 中所列标准的全速或半速标称频率。配置 灵活性不应成为支持不同混合的协议和标准的障碍。多协议组中支持 PCI Express、千兆以太网、 SGMII 和串行 RapidIO 模式。

- 支持兼容 XAUI 的功能并将 SERDES 的最高性能扩展至 3.2 Gbps。

Lattice Semiconductor Corp.2012 版权所有 © 所有莱迪思的商标、注册商标、图案和标识符均在 www.latticesemi.com/legal 网站上列出。所有其它品牌或产品名称均为其所有者的商标或注册商标。此处的参数规格和信息可能会更改,恕不另行通知。中文翻译文档仅为您提供方便。莱迪思将尽力为您提供准确的中文翻译文档,但鉴于翻译的难度,译文可能会与英文文档存在一些微小差别,其准确性也难以保证。请参考英文源文件,获取最新、最准确的信息。所有的翻译文档中的信息均以英文源文件为准。

- 支持 SONET/SDH OC-3/STM-1、OC-12/STM-4 和 OC-48/STM-16 速率。

- 增加了对于 SD-SDI、 HD-SDI 和 3G-SDI 的每个 RX 和 TX DIV11 的支持。多速 SDI 支持。

# 本技术说明的使用

莱迪思的 ispLEVER 设计工具支持所有的 PCS 模式。大多数模式都是专为特定行业的标准数据协议应用而设计。其他模式则适用于更通用的目的,让设计人员能对他们自己的应用设置进行定义。ispLEVER设计工具允许用户在自己的设计中为每个 quad 定义工作模式。本技术说明介绍的 SERDES 和 PCS 的所有模式都得到 ispLEVER 软件的支持。如果您正在使用 Lattice Diamond™ 设计软件,请参见附录 D。

本文档提供了嵌入式 SERDES 和相关 PCS 逻辑的所有功能的全部说明。<u>LatticeECP3 系列数据手册</u>提供了嵌入式 SERDES 的电气特性和时序特性。本文档 PCS 章节提供了 PCS 逻辑的工作情况。附录给出了可通过 SCI 总线访问的有关 SERDES 和 PCS 逻辑的所有状态和控制寄存器列表。<u>LatticeECP3 系列数据手册</u>的引脚布局信息章节给出了封装的引脚布局信息。

# 支持的标准

表 8-1 中列出了支持的标准。

表 8-1. SERDES 支持的标准

| 标准                                                                                 | 数据速率<br>(Mbps)                                                  | 系统参考时钟<br>(MHz)                                                | FPGA 时钟<br>(MHz)                     | 通用/链接宽度的<br>数量 | 编码类型     |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------|----------------|----------|

| PCI Express 1.1                                                                    | 2500                                                            | 100                                                            | 250                                  | x1, x2, x4     | 8b10b    |

|                                                                                    | 1250                                                            | 125                                                            | 125                                  | x1             | 8b10b    |

| 千兆以太网, SGMII                                                                       | 2500                                                            | 125                                                            | 250                                  | x1             | 8b10b    |

|                                                                                    | 3125                                                            | 156.25                                                         | 156.25                               | x1             | 8b10b    |

| XAUI                                                                               | 3125                                                            | 156.25                                                         | 156.25                               | x4             | 8b10b    |

| 串行 RapidIO Type I,<br>串行 RapidIO Type II,<br>串行 RapidIO Type III                   | 1250,<br>2500,<br>3125                                          | 125,<br>125,<br>156.25                                         | 125,<br>250,<br>156.25               | x1, x4         | 8b10b    |

| OBSAI-1,<br>OBSAI-2,<br>OBSAI-3,<br>OBSAI-4                                        | 768,<br>1536,<br>2304,<br>3072                                  | 76.8,<br>76.8, 153.6,<br>115.2,<br>153.6                       | 76.8,<br>153.6,<br>230.4,<br>153.6   | x1             | 8b10b    |

| CPRI-1,<br>CPRI-2,<br>CPRI-3,<br>CPRI-4                                            | 614.4,<br>1228.8,<br>2457.6,<br>3072.0                          | 61.44,<br>61.44, 122.88,<br>122.88,<br>153.6                   | 61.44,<br>122.88,<br>122.88<br>153.6 | x1             | 8b10b    |

| SD-SDI<br>259M, 344M)                                                              | 143 <sup>1</sup> ,<br>177 <sup>1</sup> ,<br>270,<br>360,<br>540 | 14.3 <sup>1</sup> ,<br>17.7 <sup>1</sup> ,<br>27,<br>36,<br>54 | 143,<br>177,<br>27,<br>36,<br>54     | x1             | NRZI/ 扰码 |

| HD-SDI<br>292M)                                                                    | 1483.5,<br>1485                                                 | 74.175, 148.35,<br>74.25, 148.50                               | 74.175, 148.35,<br>74.25, 148.5      | x1             | NRZI/ 扰码 |

| 3G-SDI<br>424M)                                                                    | 2967,<br>2970                                                   | 148.35,<br>148.5                                               | 148.35,<br>148.5                     | x1             | NRZI/ 扰码 |

| SONET STS-3 <sup>2</sup><br>SONET STS-12 <sup>2</sup><br>SONET STS-48 <sup>2</sup> | 155.52<br>622.08<br>2488                                        | 15.552<br>62.208<br>248.8                                      | 15.552<br>62.208<br>248.8            | x1             | N/A      |

| 10 位 SERDES                                                                        | 150 - 3125                                                      | 15 - 312.5                                                     | 15 - 312.5                           | x1, x2, x3, x4 | N/A      |

表 8-1. SERDES 支持的标准 (续)

| 标准        | 数据速率<br>(Mbps) | 系统参考时钟<br>(MHz) | FPGA 时钟<br>(MHz) | 通用 / 链接宽度的<br>数量 | 编码类型  |

|-----------|----------------|-----------------|------------------|------------------|-------|

| 8位 SERDES | 150 - 3125     | 15 - 312.5      | 15 - 312.5       | x1, x2, x3, x4   | N/A   |

| 通用 8b10b  | 150 - 3125     | 15 - 312.5      | 15 - 312.5       | x1, x2, x3, x4   | 8b10b |

<sup>1.</sup> 对于较低速率而言,可以绕过 SERDES,将信号可直接传入 FPGA 内核。

## 架构概述

quad 中的 SERDES/PCS 模块包含逻辑用于 4 个独立的全双工数据通道。

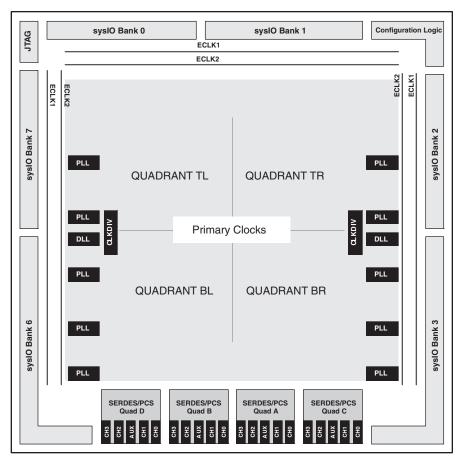

图 8-1 展示了 LatticeECP3-150 FPGA 中 SERDES/PCS quad 的布局 (其他器件有较少的 quad)。

### 图 8-1. LatticeECP3-150 框图

表 8-2 展示了 LatticeECP3 系列中每款器件可用的 SERDES/PCS quad 数量。

<sup>2. 8</sup> 位 SERDES 模式支持 SONET 协议。请参考本文档的 SONET 章节,了解更多详细信息。

#### 表 8-2. 每款 LatticeECP3 器件的 SERDES/PCS Quad 数量

| 封装            | ECP3-17 | ECP3-35 | ECP3-70 | ECP3-95 | ECP3-150 |

|---------------|---------|---------|---------|---------|----------|

| 256 球型 ftBGA  | 1       | 1       | _       | _       | _        |

| 328 球型 csBGA  | 2 通道 1  | _       | _       | _       | _        |

| 484 球型 ftBGA  | 1       | 1       | 1       | 1       |          |

| 672 球型 ftBGA  | _       | 1       | 2       | 2       | 2        |

| 1156 球型 ftBGA | _       | _       | 3       | 3       | 4        |

#### 1. Channel 0 和 3 可用。

每个 quad 可通过编程使用几种基于协议的模式中的一种。每个 quad 需要自己的参考时钟,可通过封装引脚连接到外部时钟源或连接到 FPGA 内部逻辑的时钟源。

每个 quad 可根据所选的支持标称频率的协议进行编程,并可选用每个通道的全速或半速选项。例如,可以在同一个 quad 中使用 PCI Express x1@2.5Gbps 和千兆以太网通道,在千兆以太网通道中使用半速选项。如果一个 quad 与非 PCI Express 通道共享一个 PCI Express x1 通道,请确保这个 quad 的参考时钟兼容这个 quad 内的所有协议。例如:PCI Express 扩频参考时钟与大多数千兆以太网应用不兼容。

因为每个 quad 都有自己的参考时钟,在同一块芯片上不同的 quad 可支持不同标准。这一特性使得 LatticeECP3 系列器件成为桥接不同标准的理想器件。

PCS quad 并不仅限用于业界标准协议。每个 quad (以及一个 quad 内的每个通道)可编程用于许多用户定义的数据操作模式。例如,字对齐和时钟容限补偿可通过编程用于用户自定义操作。

### PCS Quad 和通道

器件上的每个 quad 支持多达 4 个全双工数据通道。根据不同应用,可以使用一个 quad 内的一至四个通道。在一个给定的 quad 中,用户可以为每个通道分别设置许多选项。

图 8-1 展示了带有四个 PCS quad 的器件示例,包含了总共 16 个 PCS 通道。

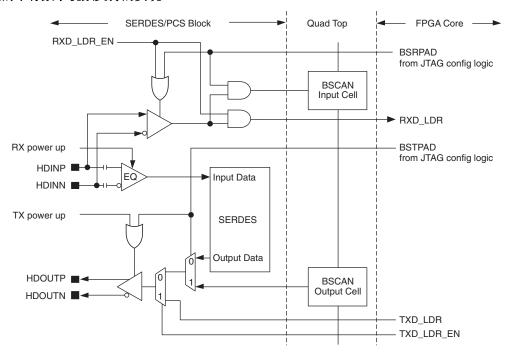

### 每个通道的 SERDES/PCS 和 FPGA 接口端口

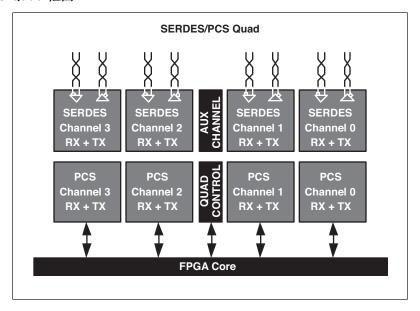

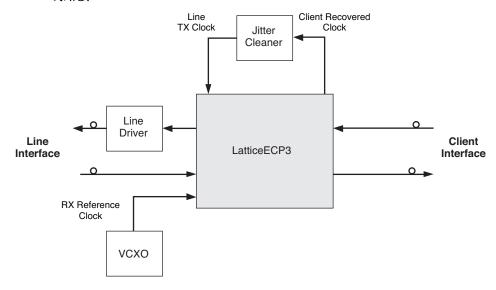

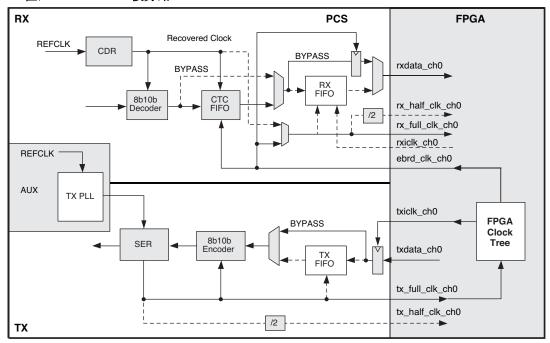

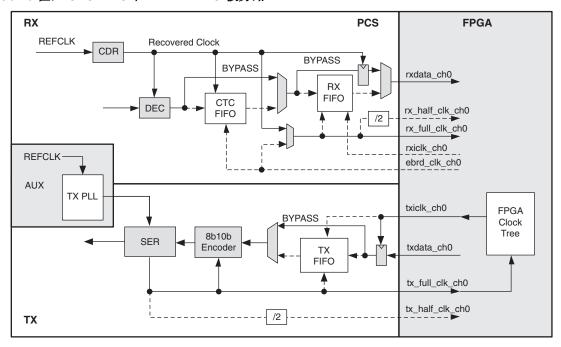

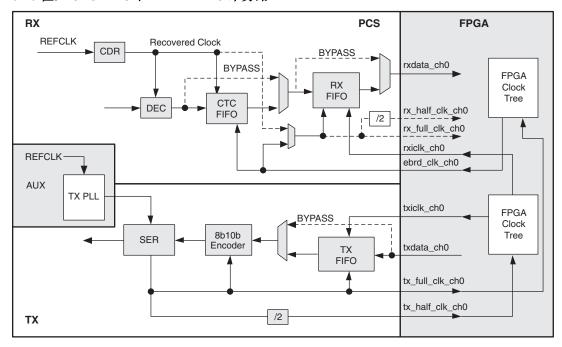

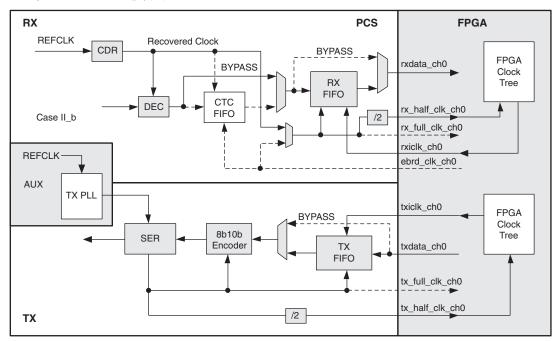

所有 PCS quad,无论所选的模式,都在封装引脚上有相同的外部高速串行接口。然而,每个 PCS 模式都有其唯一与 FPGA 逻辑作接口的输入 / 输出端口列表,这些端口是与 quad 所选协议相适应的。本文档提供了每个模式下该 quad 的输入 / 输出信号的详细说明。图 8-2 展示了一个简化的 SERDES/PCS quad。

#### 图 8-2. SERDES/PCS Quad 框图

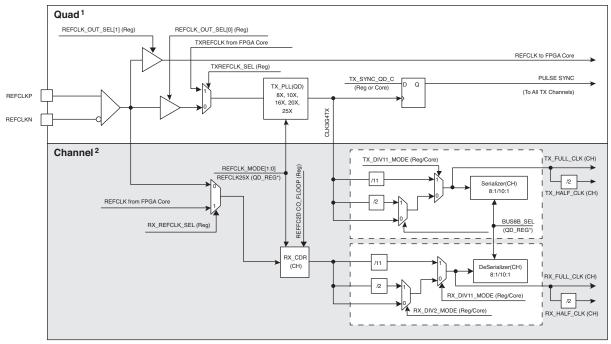

## 详细的通道框图

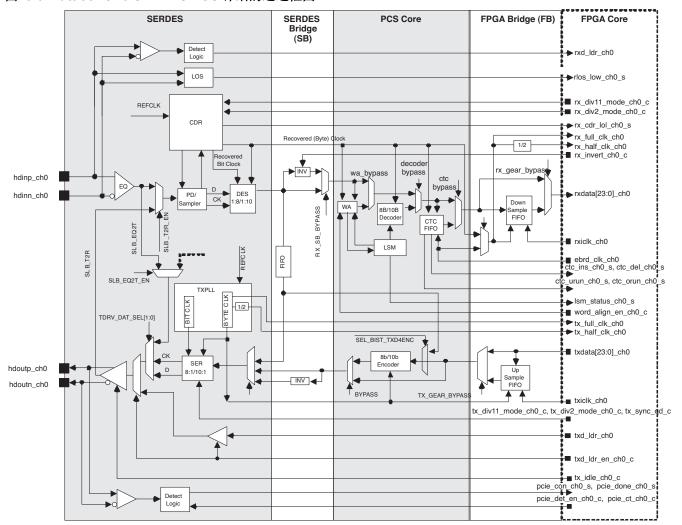

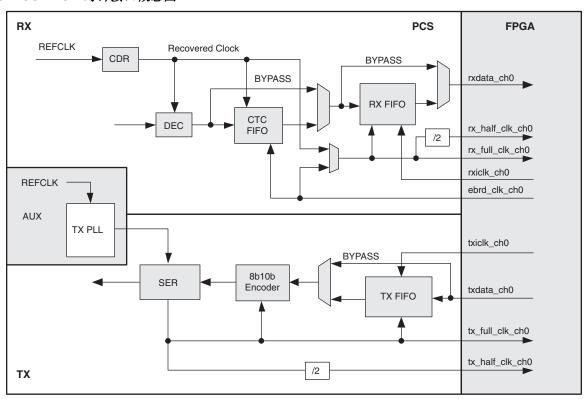

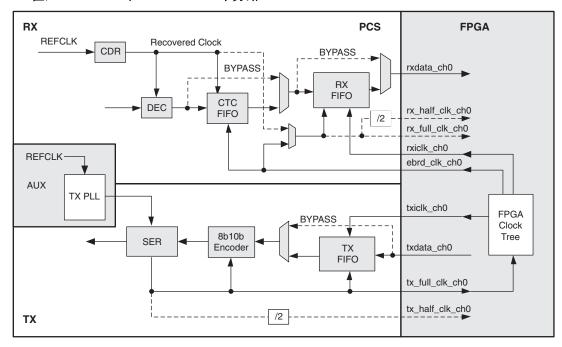

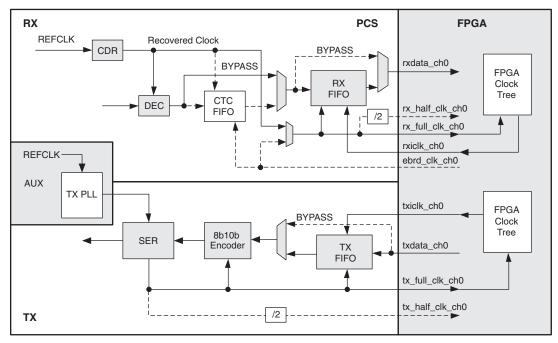

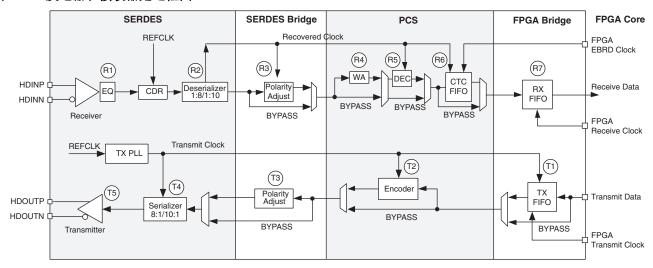

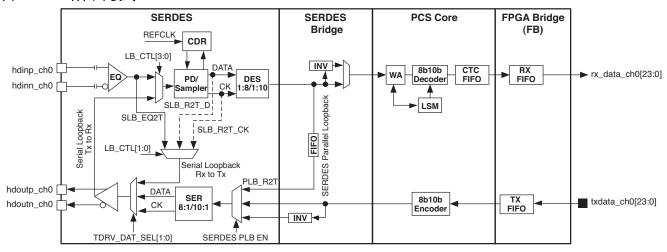

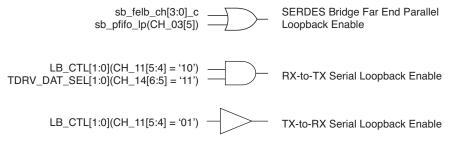

图 8-3 是 LatticeECP3 SERDES/PCS 的单通道主要功能的详细框图说明。该图展示了对 FPGA 中的用户逻辑来说可视的所有主要模块和主要控制和状态信号。该图还展示了通道中的主要子模块——SERDES、SERDES 桥、PCS内核以及 FPGA 桥。

图 8-3. LatticeECP3 SERDES/PCS 详细的通道框图

### 时钟和复位

一个 PCS quad 提供每个通道锁定的参考时钟和每个通道恢复的接收时钟,连到 FPGA 逻辑接口。每个 PCS quad 为主和次 FPGA 时钟走线提供时钟。PCS/FPGA 接口还为每个 quad 的四个通道提供来自 FPGA 逻辑的发送和接收时钟端口。

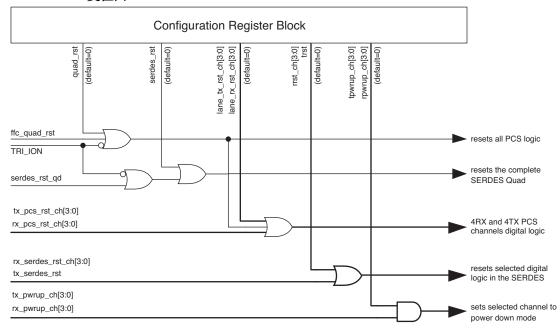

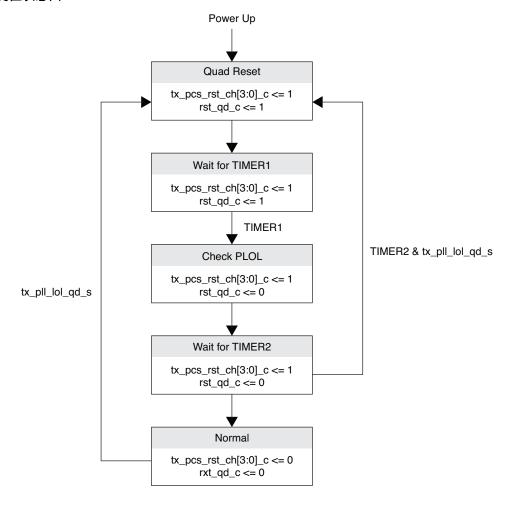

每个 quad 有复位输入来强制 quad 内的 SERDES 和 PCS 逻辑或仅 SERDES 复位。此外,还为每个通道的发送和接收提供专用于 PCS 逻辑的独立复位。

### 发送数据总线

在 PCS 块中,发送数据通道的信号是从 FPGA 到 FPGA 桥,数据宽度可调整为 2:1 进入内部 PCS 数据通道,具有 8 位数据宽度(外加控制 / 状态信号)。在 1:1 模式下,PCI Express x1 接口的最高速率是 250 MHz。在 2:1 gearing (如 16 位宽数据通道)模式下,可能的速率为 156.25 MHz(XAUI 4x 通道模式)。SERDES 和 PCS 将支持数据速率高达 3.2 Gbps 的数据,对应接口速率为 160 MHz(2:1 gearing 情况下)。

## 接收数据总线

接收路径的信号是从 PCS 块的 FPGA 桥到 FPGA。数据路径可调整(gearing)为 2:1 至数据宽度为 8 位的内部 PCS 数据路径。FPGA 接口的数据总线宽度为 16 位宽。可通过软件的寄存器位禁用 2:1 gearing 功能,这样的话,总线宽度减半(8 位宽)。当数据调整为 2:1,低位(rxdata[9:0])对应先接收的字,高位(rxdata[19:10])对应第二个接收的字。如果数据没有调整为 2:1,低位(rxdata[9:0])为有效位,并且高位不使用。表 8-3 说明了每个协议模式下数据总线的使用。

### 表 8-3. 模式使用的数据总线

| 数据总线 PCS<br>单元名称⁴ | G8B10B       | CPRI               | OBSAI                | PCI Express      | SRIO         | 千兆以太网                         | XAUI       | 8位<br>SERDES | 10 位<br>SERDES | SDI  |  |

|-------------------|--------------|--------------------|----------------------|------------------|--------------|-------------------------------|------------|--------------|----------------|------|--|

| FF_TX_D_0_0       |              |                    |                      |                  | txdata_ch(   | )[0]                          |            | •            |                | •    |  |

| FF_TX_D_0_1       |              |                    |                      |                  | txdata_ch(   | )[1]                          |            |              |                |      |  |

| FF_TX_D_0_2       |              | txdata_ch0[2]      |                      |                  |              |                               |            |              |                |      |  |

| FF_TX_D_0_3       |              | txdata_ch0[3]      |                      |                  |              |                               |            |              |                |      |  |

| FF_TX_D_0_4       |              | txdata_ch0[4]      |                      |                  |              |                               |            |              |                |      |  |

| FF_TX_D_0_5       |              |                    |                      |                  | txdata_ch(   | )[5]                          |            |              |                |      |  |

| FF_TX_D_0_6       |              |                    |                      |                  | txdata_ch(   | )[6]                          |            |              |                |      |  |

| FF_TX_D_0_7       |              |                    |                      |                  | txdata_ch(   | )[7]                          |            |              |                |      |  |

| FF_TX_D_0_8       |              |                    |                      | tx_k_ch0[0]      |              |                               | txc_ch0[0] | GND          | txdata_ch0     | [8]  |  |

| FF_TX_D_0_9       | tx_fc        | rce_dis            | p_ch0[0]             | 1                |              | GND                           |            |              | txdata_ch0     | [9]  |  |

| FF_TX_D_0_10      | tx_c         | disp_sel           | _ch0[0] <sup>1</sup> |                  | GND          | xmit_ch0[0] <sup>2</sup>      |            | GND          |                |      |  |

| FF_TX_D_0_11      | GND          |                    |                      | pci_ei_en_ch0[0] | GND          | tx_disp_correct_ch0[0]        |            | GND          |                |      |  |

| FF_TX_D_0_12      |              |                    |                      | tx               | data_ch0[8]  | •                             | •          |              | txdata_ch0[    | [10] |  |

| FF_TX_D_0_13      |              |                    |                      | tx               | data_ch0[9]  |                               |            |              | txdata_ch0     | [11] |  |

| FF_TX_D_0_14      |              |                    |                      | tx               | data_ch0[10] |                               |            |              | txdata_ch0[    | [12] |  |

| FF_TX_D_0_15      |              |                    |                      | tx               | data_ch0[11] |                               |            |              | txdata_ch0[    | [13] |  |

| FF_TX_D_0_16      |              |                    |                      | tx               | data_ch0[12] |                               |            |              | txdata_ch0[    | [14] |  |

| FF_TX_D_0_17      |              | txdata_ch0[13]     |                      |                  |              |                               |            |              |                | [15] |  |

| FF_TX_D_0_18      |              | txdata_ch0[14]     |                      |                  |              |                               |            |              |                | [16] |  |

| FF_TX_D_0_19      |              |                    |                      | tx               | data_ch0[15] |                               |            |              | txdata_ch0[    | [17] |  |

| FF_TX_D_0_20      |              |                    |                      | tx_k_ch0[1]      |              |                               | txc_ch0[1] | GND          | txdata_ch0[    | [18] |  |

| FF_TX_D_0_21      | tx_fc        | rce_dis            | p_ch0[1]             | 1                |              | GND                           |            |              | txdata_ch0[    | [19] |  |

| FF_TX_D_0_22      | tx_c         | disp_sel           | _ch0[1] <sup>1</sup> |                  | GND          | xmit_ch0[1] <sup>2</sup>      |            | GND          |                |      |  |

| FF_TX_D_0_23      | GND          |                    |                      | pci_ei_en_ch0[1] | GND          | tx_disp_correct_ch0[1]        |            | GND          |                |      |  |

| FF_RX_D_0_0       |              |                    |                      |                  | rxdata_ch(   | 0[0]                          | •          |              |                |      |  |

| FF_RX_D_0_1       |              |                    |                      |                  | rxdata_ch(   | )[1]                          |            |              |                |      |  |

| FF_RX_D_0_2       |              |                    |                      |                  | rxdata_ch(   | )[2]                          |            |              |                |      |  |

| FF_RX_D_0_3       |              |                    |                      |                  | rxdata_ch(   | )[3]                          |            |              |                |      |  |

| FF_RX_D_0_4       |              |                    |                      |                  | rxdata_ch(   | 0[4]                          |            |              |                |      |  |

| FF_RX_D_0_5       |              |                    |                      |                  | rxdata_ch(   | )[5]                          |            |              |                |      |  |

| FF_RX_D_0_6       |              |                    |                      |                  | rxdata_ch(   | )[6]                          |            |              |                |      |  |

| FF_RX_D_0_7       |              |                    |                      |                  | rxdata_ch(   | )[7]                          |            |              |                |      |  |

| FF_RX_D_0_8       |              |                    |                      | rx_k_ch0[0]      |              |                               | rxc_ch0[0] | NC           | rxdata_ch0     | [8]  |  |

| FF_RX_D_0_9       | rx_disp_err_ | ch0[0]             |                      | rxstatus0_ch0[0] | r            | x_disp_err_ch0[0]             | •          | NC           | rxdata_ch0     | [9]  |  |

| FF_RX_D_0_10      | rx_cv_err_c  | h0[0] <sup>3</sup> |                      | rxstatus0_ch0[1] |              | rx_cv_err_ch0[0] <sup>3</sup> |            |              | NC             |      |  |

| FF_RX_D_0_11      | NC           |                    |                      | rxstatus0_ch0[2] |              | N                             | IC         |              |                |      |  |

| FF_RX_D_0_12      |              |                    |                      | n                | data_ch0[8]  |                               |            |              | rxdata_ch0[    | [10] |  |

| FF_RX_D_0_13      |              | rxdata_ch0[9]      |                      |                  |              |                               |            |              | rxdata_ch0     | [11] |  |

| FF_RX_D_0_14      |              | rxdata_ch0[10]     |                      |                  |              |                               |            |              | rxdata_ch0[    | [12] |  |

| FF_RX_D_0_15      |              |                    |                      | rx               | data_ch0[11] |                               |            |              | rxdata_ch0[    | [13] |  |

| FF_RX_D_0_16      |              |                    |                      | rx               | data_ch0[12] |                               |            |              | rxdata_ch0[    | [14] |  |

| FF_RX_D_0_17      |              |                    |                      | rx               | data_ch0[13] |                               |            |              | rxdata_ch0[    | [15] |  |

| FF_RX_D_0_18      |              |                    |                      | rx               | data_ch0[14] |                               |            |              | rxdata_ch0[    | [16] |  |

| FF_RX_D_0_19      |              |                    |                      | rx               | data_ch0[15] |                               |            |              | rxdata_ch0[    | [17] |  |

### 表 8-3. 模式使用的数据总线 (续)

| 数据总线 PCS<br>单元名称 <sup>4</sup> | G8B10B       | CPRI   | OBSAI | PCI Express      | SRIO | 千兆以太网             | XAUI       | 8位<br>SERDES | 10 位<br>SERDES | SDI |

|-------------------------------|--------------|--------|-------|------------------|------|-------------------|------------|--------------|----------------|-----|

| FF_RX_D_0_20                  |              |        |       | rx_k_ch0[1]      |      |                   | rxc_ch0[1] | NC           | rxdata_ch0[1   | 18] |

| FF_RX_D_0_21                  | rx_disp_err_ | ch0[1] |       | rxstatus1_ch0[0] | r    | x_disp_err_ch0[1] |            | NC           | rxdata_ch0[1   | 19] |

| FF_RX_D_0_22                  | rx_cv_err_cl | ո0[1]³ |       | rxstatus1_ch0[1] |      | rx_cv_err_ch0[1]3 |            |              | NC             |     |

| FF_RX_D_0_23                  | NC           |        |       | rxstatus1_ch0[2] |      | N                 | IC         |              |                |     |

- 1. force\_disp 信号将强制相关数据字的位 [7:0] 在列上的不一致,而(disparity)值由 tx\_disp\_sel 信号来选择。如果 disp\_sel 是 1, 10 位编码将为 " 当前 RD+" 列(即 positive disparity)。如果 tx\_disp\_sel 为 0, 10 位编码将为 " 当前 RD-" 列(即 negative disparity)。

- 2. 莱迪思千兆以太网 PCS IP 核可提供一个自协商的状态机,生成信号 xmit。它用于与千兆以太网硬逻辑空闲状态机进行交互。

- 3. 当出现编码违例,数据包 PCS 8b10b 解码器将使用 d=hex EE 和 K=1 (K=1 且 d=EE 不在 8b10b 编码空间内)替代解码器的输出。

- 4. FF\_TX\_D\_0\_0: FPGA 结构发送数据总线 Channel 0 Bit 0。

## 特定模式控制 / 状态信号说明

表 8-4 说明了特定模式下的控制 / 状态信号。

### 表 8-4. 控制信号及其功能

| 信号名称                    | 说明                                                                   |

|-------------------------|----------------------------------------------------------------------|

| 发送控制信号                  |                                                                      |

| tx_k_ch[3:0]            | 每个通道,高电平有效控制字符指示。                                                    |

| tx_force_disp_ch[3:0]   | 每个通道,高电平有效,命令 PCS 接受来自 disp_sel_ch(0-3) FPGA 接口输入的不一致 (disparity) 值。 |

| tx_disp_sel_ch[3:0]     | 每个通道, FPGA 逻辑提供的不一致 (disparity) 值。当 force_disp_ch(0-3) 为高电平时有效。      |

| tx_correct_disp_ch[3:0] | 当有效时,通过调整 8b10b 编码器以取 negative disparity 状态开始来更正 (disparity) 指示符。    |

| 接收状态信号                  |                                                                      |

| rx_k_ch[3:0]            | 每个通道,高有效控制字符指示。                                                      |

| rx_disp_err_ch[3:0]     | 每个通道, PCS 发出的高有效信号,用以指示相应数据检测到的 (disparity) 错误。                      |

| rx_cv_err_ch[3:0]       | 每个通道,编码违例信号,用以指示相应数据检测到的错误。                                          |

### 控制

每个模式下有其各自的一套控制信号,允许从 FPGA 逻辑直接控制各种 PCS 功能。通常,这些控制输入的每个信号 复制写入相应的控制寄存器的一个或多个位中。

{signal}\_c 是从 FPGA 内核到 FPGA 桥的控制信号。所有控制信号均在 SERDES/PCS 内异步使用。

### 状态

每个模式下有其各自的一套状态或报警信号,通过 FPGA 逻辑进行监控。通常,这些状态输出都对应于特定状态寄存的一个或多个位。 Diamond 设计工具给了用户将这些端口输出到 PCS FPGA 接口的选择。

{signal}\_s 是从 FPGA 桥到 FPGA 内核的状态信号。来自 SERDES/PCS 的所有状态信号都是异步的。他们都必须在 FPGA 设计使用这些信号之前在时钟域进行同步。

请参考本文档的特定模式控制/状态信号章节,了解有关控制和状态信号的详细信息。

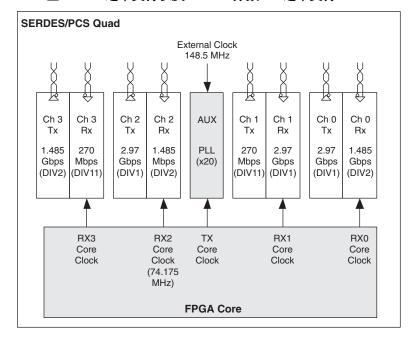

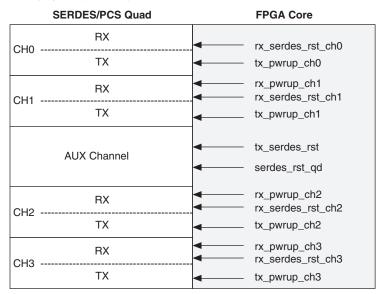

#### SERDES/PCS

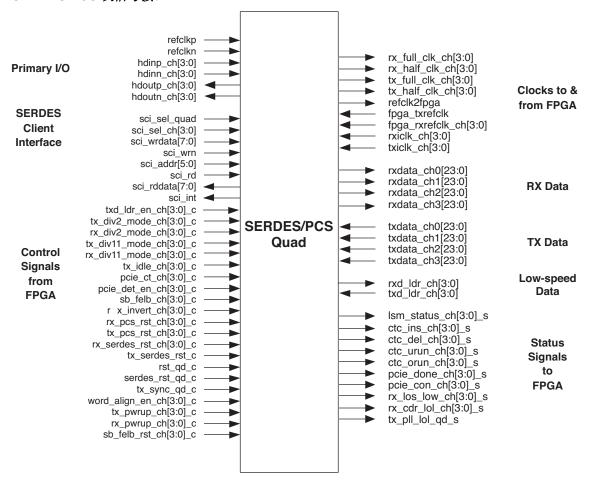

quad 包含 4 个通道,每个通道都有 RX 和 TX 电路,以及一个包含 TX PLL 的辅助通道。主差分参考时钟引脚或 FPGA 内核都可以提供 TX PLL 的参考时钟。quad SERDES/PCS 宏为 4 条数据通道执行串行化或解串功能。此外, SERDES/PCS 块的 TxPLL 为 FPGA 逻辑提供系统时钟。quad 还在每个 TX 和 RX 电路上独立支持全数据速率和半数据速率模式。框图级图如图 8-4 所示。

图 8-4. SERDES/PCS 块信号接口

# I/O 说明

表 8-5 列出了所有(至 / 从)PCS quad 的默认和可选择的输入和输出。用户可使用 IPexpress™ GUI 选择可选的端口用于 PCS quad。

表 8-5. SERDES\_PCS I/O 说明

| 信号名称                  | I/O        | 类型   | 说明                                                                                         |

|-----------------------|------------|------|--------------------------------------------------------------------------------------------|

| 主 I/O、SERDES Quad     | l          |      |                                                                                            |

| hdinp_ch0             | I          | 通道   | 高速 CML 输入、正极、 channel 0                                                                    |

| hdinn_ch0             | I          | 通道   | 高速 CML 输入、负极、 channel 0                                                                    |

| hdinp_ch1             | I          | 通道   | 高速 CML 输入、正极、 channel 1                                                                    |

| hdinn_ch1             | I          | 通道   | 高速 CML 输入、负极、 channel 1                                                                    |

| hdinp_ch2             | I          | 通道   | 高速 CML 输入、正极、 channel 2                                                                    |

| hdinn_ch2             | I          | 通道   | 高速 CML 输入、负极、 channel 2                                                                    |

| hdinp_ch3             | I          | 通道   | 高速 CML 输入、正极、 channel 3                                                                    |

| hdinn_ch3             | I          | 通道   | 高速 CML 输入、负极、 channel 3                                                                    |

| hdoutp_ch0            | 0          | 通道   | 高速 CML 输入、正极、 channel 0                                                                    |

| hdoutn_ch0            | 0          | 通道   | 高速 CML 输出、负极、 channel 0                                                                    |

| hdoutp_ch1            | 0          | 通道   | 高速 CML 输入、正极、 channel 1                                                                    |

| hdoutn_ch1            | 0          | 通道   | 高速 CML 输出、负极、 channel 1                                                                    |

| hdoutp_ch2            | 0          | 通道   | 高速 CML 输入、正极、 channel 2                                                                    |

| hdoutn_ch2            | 0          | 通道   | 高速 CML 输出、负极、 channel 2                                                                    |

| hdoutp_ch3            | 0          | 通道   | 高速 CML 输入、正极、 channel 3                                                                    |

| hdoutn_ch3            | 0          | 通道   | 高速 CML 输出、负极、 channel 3                                                                    |

| refclkp               | I          | Quad | 参考时钟输入、正极、专用 CML 输入                                                                        |

| refclkn               | I          | Quad | 参考时钟输入、负极、专用 CML 输入                                                                        |

| 接收/发送数据总线 (参见表        | 8-3 和 8-4, |      | <del>-</del>                                                                               |

| rxdata_ch0[23:0]      | 0          | 通道   | 用于 channel 0 接收路径的数据信号                                                                     |

| rxdata_ch1[23:0]      | 0          | 通道   | 用于 channel 1 接收路径的数据信号                                                                     |

| rxdata_ch2[23:0]      | 0          | 通道   | 用于 channel 2 接收路径的数据信号                                                                     |

| rxdata_ch3[23:0]      | 0          | 通道   | 用于 channel 3 接收路径的数据信号                                                                     |

| txdata_ch0[23:0]      | I          | 通道   | 用于 channel 0 发送路径的数据信号                                                                     |

| txdata_ch1[23:0]      | I          | 通道   | 用于 channel 1 发送路径的数据信号                                                                     |

| txdata_ch2[23:0]      | I          | 通道   | 用于 channel 2 发送路径的数据信号                                                                     |

| txdata_ch3[23:0]      | I          | 通道   | 用于 channel 3 发送路径的数据信号                                                                     |

| 控制信号                  |            |      |                                                                                            |

| tx_idle_ch[3:0] _c    | I          | 通道   | 通过 SERDES 发送器发出控制传输的电气空闲信号。<br>1 = 命令 SERDES 发送器输出电气空闲信号<br>0 = 正常操作                       |

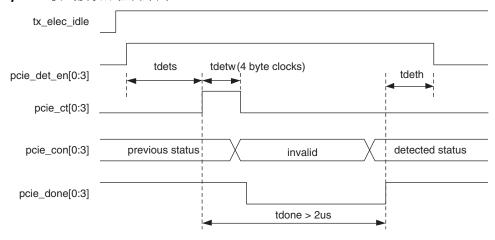

| pcie_det_en_ch[3:0]_c | I          | 通道   | FPGA 逻辑(用户逻辑)通知 SERDES 块,它将申请用于 PCI Express 接收器检测工作。<br>1 = 使能 PCI Express 接收器检测, 0 = 正常操作 |

| pcie_ct_ch[3:0]_c     | I          | 通道   | 1 = 申请发送器进行远端接收器检测<br>0 = 正常数据操作                                                           |

| rx_invert_ch[3:0]_c   | I          | 通道   | 控制接收数据求反。<br>1 = 数据取反, 0 = 无需数据取反                                                          |

# 表 8-5. SERDES\_PCS I/O 说明(续)

| 信号名称                     | I/O | 类型   | 说明                                                          |

|--------------------------|-----|------|-------------------------------------------------------------|

| word_align_en_ch[3:0]_c  | I   | 通道   | 控制 comma 字符 $1 = 使能 comma 对齐功能, 0 = 锁定字对齐位置为当前位置$           |

| sb_felb_ch[3:0]_c        | I   | 通道   | SERDES 桥接并行回环         1 = 使能回环从 RX 至 TX, 0 = 正常数据工作         |

| sb_felb_rst_ch[3:0]_c    | I   | 通道   | SERDES 桥接并行回环 FIFO 清除<br>1 = 复位回环 FIFO, 0 = 正常回环操作          |

| tx_sync_qd_c             | I   | Quad | 串行器复位<br>跳变(Transition) = 复位,不变(Level) = 正常工作               |

| rx_div2_mode_ch[3:0]_c   | I   | 通道   | 接收器速率模式选择 (半速 / 全速)<br>1 = 半速, 0 = 全速                       |

| tx_div2_mode_ch[3:0]_c   | I   | 通道   | 发送器速率模式选择 (半速 / 全速)<br>1 = 半速, 0 = 全速                       |

| rx_div11_mode_ch[3:0]_c  | I   | 通道   | 接收器速率模式选择 (Div11/ 全速)<br>1 = Div11, 0 = 全速                  |

| tx_div11_mode_ch[3:0]_c  | I   | 通道   | 发送器速率模式选择 (Div11/ 全速)<br>1 = Div11, 0 = 全速                  |

| txd_ldr_en_ch{3:0]_c     | Ι   | 通道   | 使能低数据速率 TX 串行路径<br>1 = 使能, 0 = 禁用                           |

| 复位信号                     |     |      |                                                             |

| rx_pcs_rst_ch[3:0]_c     | I   | 通道   | 高电平有效,异步输入。仅在 PCS 中复位单独的接收通道逻辑。                             |

| tx_pcs_rst_ch[3:0]_c     | I   | 通道   | 高电平有效,异步输入。仅在 PCS 中复位单独的发送通道逻辑。                             |

| rx_serdes_rst_ch[3:0]_c  | I   | 通道   | 高电平有效。在 SERDES 接收通道中复位选择的数字逻辑。                              |

| tx_serdes_rst_c          | I   | Quad | 高电平有效。在所有 SERDES 发送通道中复位选择的数字逻辑。                            |

| rst_qd_c                 | I   | Quad | 高电平有效,异步输入。复位所有 SERDES 通道,包括辅助通道和 PCS。                      |

| serdes_rst_qd_c          | I   | Quad | 高电平有效,异步输入至 SERDES quad。复位所有 SERDES 通道,包括 Quad 通道但非 PCS 逻辑。 |

| tx_pwrup_ch[3:0]_c       | I   | 通道   | 1=高电平有效,发送通道上电后。0=发送通道断电。                                   |

| rx_pwrup_ch[3:0]_c       | I   | 通道   | 1=高电平有效,接收通道上电后。0=接收通道断电。.                                  |

| 状态信号                     |     |      |                                                             |

| pcie_done_ch[0:3]_s      | 0   | 通道   | 1 = 远端接收器检测完成<br>0 = 远端接收器检测未完成                             |

| pcie_con_ch[3:0]_s       | 0   | 通道   | 远端接收器检测结果。<br>1 = 检测到远端接收器<br>0 = 未检测到远端接收器                 |

| rx_los_low_ch[3:0]_s     | 0   | 通道   | 每个通道的信号丢失(LO 阈值范围)检测。                                       |

| lsm_status_ch[3:0]_s     | 0   | 通道   | 1 = 数据通道已与 comma 字符同步<br>0 = 数据通道未找到 comma 字符               |

| ctc_urrun_ch[3:0]_s      | 0   | 通道   | 1 = 接收时钟补偿器 FIFO 欠载运行错误<br>0 = 无 FFIFO 错误                   |

| ctc_orun_ch[3:0]_s       | 0   | 通道   | 1 = 接收时钟补偿器 FIFO 过载错误<br>0 = 无 FIFO 错误                      |

| rx_cdr_lol_ch[3:0]_s     | 0   | 通道   | 1 = 接收 CDR 锁定丢失<br>0 = 保持锁定                                 |

| tx_pll_lol_qd_s          | 0   | Quad | 1 = 发送 PLL 锁定丢失<br>0 = 保持锁定                                 |

| ctc_ins_ch[3:0]_s        | 0   | 通道   | 1 = CTC 添加的字符 SKIP                                          |

| ctc_del_ch[3:0]_s        | 0   | 通道   | 1 = CTC 删除的字符 SKIP                                          |

| rx_cdr_trained_ch[3:0]_s | 0   | 通道   | 1 = 说明 CDR_TRAIN_DIV 路径已经训练了 CDR                            |

## 表 8-5. SERDES\_PCS I/O 说明(续)

| 信号名称                          | I/O     | 类型   | 说明                                                                                                                                                 |

|-------------------------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| FPGA 接口时钟                     |         |      |                                                                                                                                                    |

| rx_full_clk_ch[3:0]           | 0       | 通道   | 接收通道恢复时钟。在用户模式下,时钟源总是通道的恢复时钟。对于 10 GbE 等标准,支持时钟补偿,时钟源是相应发送通道的系统时钟。对于 PCS 旁路模式,它也是发送系统时钟,因此要求 raw 模式实际上通过 8b10b 模式下 8b10b 解码器禁止(10 位或 20 位数据通道)来实现。 |

| rx_half_clk_ch[3:0]           | 0       | 通道   | 接收通道恢复半速时钟。在 2:1 gearing 模式下,输出除以 2。                                                                                                               |

| tx_full_clk_ch[3:0]           | 0       | 通道   | TX PLL 全速时钟。仅 tx_full_clk_ch0 可直接驱动主时钟网络。所有tx_full_clk_ch[3:0] 信号可以通过使用 USE SECONDARY 时钟参数驱动次时钟网络。 <sup>3</sup>                                    |

| tx_half_clk_ch[3:0]           | 0       | 通道   | TX PLL 半速时钟。仅 tx_half_clk_ch0 可直接驱动主时钟网络。所有tx_half_clk_ch[3:0] 信号可以通过使用 USE SECONDARY 时钟参数驱动次时钟网络。 <sup>3</sup>                                    |

| refclk2fpga                   | 0       | Quad | 参考时钟至 FPGA 内核。选择该时钟后,只要参考时钟有效就一直保持有效,即使当 quad 为掉电模式。                                                                                               |

| fpga_rxrefclk_ch[3:0]         | I       | Quad | 来自 FPGA 逻辑的 RX 参考时钟,用于 CDR PLL                                                                                                                     |

| fpga_txrefclk                 | I       | Quad | 来自 FPGA 逻辑的 TX 参考时钟,用于 TX SERDES PLL                                                                                                               |

| ebrd_clk_ch[3:0] <sup>2</sup> | I       | 通道   | 来自 FPGA 的接收通道时钟输入,用于 CTC FIFO 读。                                                                                                                   |

| rxiclk_ch[3:0]                | I       | 通道   | 来自 FPGA 的接收通道时钟输入。用于使用与参考和 / 或接收参考时钟同步的时钟来为 RX FPGA Interface FIFO 提供时钟。                                                                           |

| txiclk_ch[3:0]                | I       | 通道   | 来自 FPGA 的发送通道时钟输入。每个通道来自 FPGA 发送的时钟输入。使用与参考时钟同步的时钟来为 TX FPGA Interface FIFO 提供时钟。在使用 CTC 时,还使用与参考时钟同步的时钟来为 RX FPGA Interface FIFO 提供时钟。            |

| 低速接收/发送数据和 SERDI              | ES 客户端接 | 口信号  |                                                                                                                                                    |

| rxd_ldr_ch[3:0]               | 0       | 通道   | 单端串行低数据速率输出 (RX)至 FPGA 内核。                                                                                                                         |

| txd_ldr_ch[3:0]               | 1       | 通道   | 来自 FPGA 内核的单端串行低数据速率输入 (TX)。                                                                                                                       |

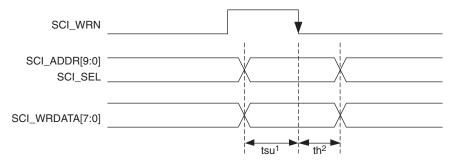

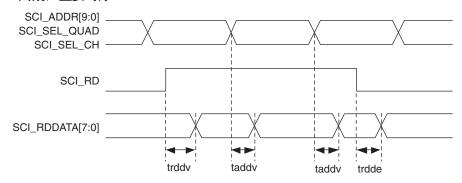

| sci_wrdata[7:0]               | I       | _    | 写数据输入。                                                                                                                                             |

| sci_wrn                       | 1       | _    | 写输入选通信号。                                                                                                                                           |

| sci_sel_quad                  | I       | _    | 选择 quad 寄存器。                                                                                                                                       |

| sci_sel_ch[3:0]               | 1       |      | 选择通道寄存器。                                                                                                                                           |

| sci_addr[5:0]                 | ı       | _    | 地址总线输入。                                                                                                                                            |

| sci_rd                        | I       | _    | 读数据选择。                                                                                                                                             |

| sci_rddata[7:0]               | 0       |      | 读数据输出。                                                                                                                                             |

| sci_int                       | 0       | _    | 中断输出。                                                                                                                                              |

- 1. 配置时, hdoutp 和 hdoutn 都拉高至 VCCOB。

- 2. wrapper 模块端口列表不提供该时钟。根据 CTC 模式,软件自动分配时钟。参见 FPGA 接口时钟使用章节,了解更多详细信息。

- 3. 通用布线用于访问次时钟网络。用户可能得到一个 PAR 警告,但是在大多数应用中这个延迟小到可以被忽略。使用时序参数并查看追踪报告,确保没有时序冲突。

## SERDES/PCS 功能说明

LatticeECP3 器件有 1 到 4 个嵌入式 SERDES/PCS 逻辑 quad。每个 quad 依次支持 4 个独立的全双工数据通道。单通道可支持一个数据链路,每个 quad 最多可支持四个这样的通道。

嵌入式 SERDES CDR PLL 和 TX PLL 支持的数据速率覆盖各种行业标准协议。

参见图 8-3 了解下面所列的每项内容。

#### • SERDES

- 均衡器

- CDR (时钟和数据恢复)

- 解串器

- 预加重

- 串行器

- 两种串行回环模式, TX 至 RX 或 RX 至 TX

#### • SERDES 桥 (SB)

- 反相器 —— 根据 PCI Express 的要求对接收数据取反。

- SERDES 桥并行回环

### • PCS 核

- 字对齐

- 8b10b 解码器

- 8b10b 编码器

- 链路状态机

- 时钟容限补偿

#### • FPGA 桥 (FB)

- 下采样 FIFO

- 上采样 FIFO

### **SERDES**

### 均衡器

随着数字传输的数据速率超过 Gbps 数量级,与频率相关的衰减导致接收信号受到严重的码间干扰,因而必须在数据收发器中使用一个均衡器来正确恢复数据。提供 6 个档位的频率范围: Mid\_Low, Mid\_Med, Mid\_High, Long\_Low, Long\_Med, Long\_High。

### 预加重

预加重是指一个系统过程,旨在相对于其它频率分量,增强某些频率的信号分量。目的就是尽量减少衰减差异这一现象所造成的不利影响,从而改善整体信号的信噪比。用户可以选择高达80%预加重。

### 参考时钟的使用

SERDES quad 包含 4 个带有 RX 和 TX 电路的通道,还有一个包含 TX PLL 的辅助通道。 TX PLL 的参考时钟可由 主差分参考时钟引脚或相邻 quad 的参考时钟或 FPGA 内核提供。此外,SERDES 块中的 PLL 提供了输出时钟,可用于作为系统时钟来驱动 FPGA。

RX 的参考时钟可由 TX PLL 的参考时钟或 FPGA 内核提供。FPGA 内核为 TX PLL 和 RX 提供的参考时钟可能来自于不同的时钟源。

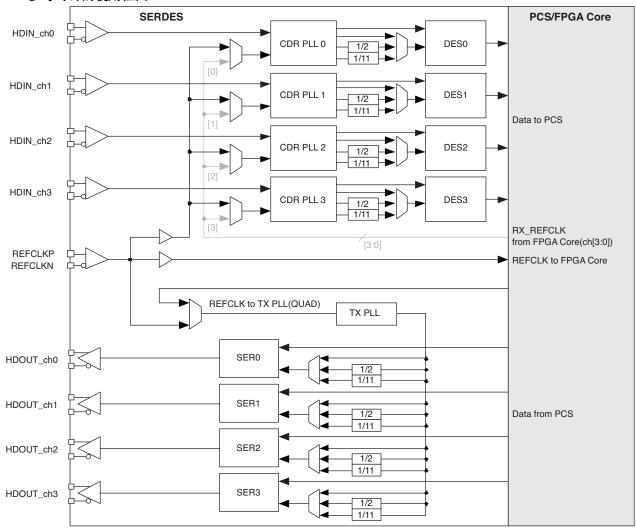

## SERDES 时钟架构

图 8-5 显示了整个 SERDES 时钟架构。这个图分成 2 部分,Quad 和通道。为简洁起见,每条通道仅显示一条。此外,不同的模块的各个控制位如下图所示。这些可能是基于 quad 的控制寄存器位或基于通道的控制寄存器位。在某些情况下,它可以是基于通道控制端口的。有些是寄存器和控制端口两者的结合。使用这两种模式可实现某些特定功能特性的动态控制。

### 图 8-5. SERDES 时钟架构

- 1. All control bits are quad based.

- 2. All control bits are channel based, except as indicated (\*).

- 3. These clocks are user-transparent.

时钟架构的主要部件包括:

- 每个 RX 和每个 TX 分频器 (DIV) 模式 ——DIV2, DIV11

- 多个 quad REFCLK 连接

- 使用 FPGA 的 tx\_sync\_qd\_c 信号的多通道发送同步

- · OOB 低数据速率应用支持

### 速率模式

每个通道的 TX 可独立编程以下面某种速率运行:

- FULL RATE

- HALF\_RATE (DIV2)

- DIV11

RX也可以每通道使用一个独立的参考时钟,使发送器和接收器在完全不同的速率下运行。

这里有一点很重要,请注意 PLL VCO 是未受影响的,它支持该协议的最高速率。该协议所需的所有分频速率都可以

通过对分频器多路开关选择进行适当的编程得到。由于 PLL 无需重新编程,从而实现了非常快速的数据速率转换。这对于许多应用来说是很有价值的。

注: LatticeECP3 PCS 不能在运行时进行速率改变。简单地改变 refclk 速率不会使 SERDES 在新的速率范围下工作。你需要重新对 SERDES 进行编程,并且这仅可能通过使用一个新的位流来实现。

TX PLL 和 4 个 CDR PLL 通常以相同频率工作,该频率为参考时钟频率的若干倍。表 8-6 显示了各种可能的时钟速率模式。列出的位时钟为参考时钟频率的倍数。

#### 表 8-6. TXPLL 和 RX CDRPLL 支持的模式

| 参考时钟模式 | refclkPmode (Quad) | Bus_width | 位时钟 (全速)    | 位时钟(div2,div11)             |

|--------|--------------------|-----------|-------------|-----------------------------|

| 20x    | 0                  | 10        | Refclk x 20 | Refclk x 10                 |

| 16x    | 0                  | 8         | Refclk x 16 | Refclk x 8                  |

| 10x    | 1                  | 10        | Refclk x 10 | Refclk x 5                  |

| 8x     | 1                  | 8         | Refclk x 8  | Refclk x 4                  |

| 25x    | _                  | 8         | Refclk x 25 | Refclk x 12.5               |

| 25x    | _                  | 10        | Refclk x 25 | Refclk x 12.5               |

| 20x    | 0                  | 10        | Refclk x 20 | Refclk x 20/11 <sup>1</sup> |

<sup>1.</sup> DIV11 模式。

### 来自 FPGA 内核的参考时钟

如图 8-5 中所述,Tx 参考时钟可由 FPGA 内核提供。在这种情况下,FPGA 资源将时钟信号传给 SERDES 所引起的额外的抖动将传递给发送数据,就具体情况而言,可能会违反Tx抖动特性规范。当使用一个来自FPGA的SERDES Tx 参考时钟时需要加以注意。

### 图 8-6. 参考时钟的使用框图

# 全速、 Div 2 和 Div 11 数据速率

每个 TX 串行器和 RX 解串器根据协议可分为全数据速率和 div2 速率或 div11 速率,在每个通道的每个方向上允许不同的数据速率。请参见图 8-6,了解更多信息。

如图 8-7 所示,四个通道可以进行不同的配置。

### 图 8-7. IPexpress GUI 的全速和半速示例

本示例中的实际数据速率和 FPGA 接口时钟速率如表 8-7 所示。 IPexpress GUI 将在本文档的后续章节中讨论。

### 表 8-7. 时钟速率示例

| 通道        | 数据速率     | 参考时钟<br>倍频器 | 数据速率<br>模式        | 计算的参考<br>时钟速率 | FPGA 接口数<br>据总线宽度   | FPGA 接口时钟速率 | tx_full_clk | tx_half_clk |

|-----------|----------|-------------|-------------------|---------------|---------------------|-------------|-------------|-------------|

| Channel 0 | 1 Gbps   | 10 x        | FULL              | 100 MHz       | 8 (10) <sup>3</sup> | 100 MHz     | 100 MHz     | 50 MHz      |

| Channel 1 | 500 Mbps | 10 x        | DIV2              | 100 MHz       | 8 (10)              | 50 MHz      | 50 MHz      | 25 MHz      |

| Channel 2 | 1 Gbps   | 10 x        | FULL              | 100 MHz       | 16 (20)             | 50 MHz      | 100 MHz     | 50 MHz      |

| Channel 3 | 500 Mbps | 10 x        | DIV2 <sup>2</sup> | 100 MHz       | 16 (20)             | 25 MHz      | 50 MHz      | 25 MHz      |

- 1. 阴影单元格中的时钟用作每个模式下的 FPGA 接口时钟。

- 2. 在 DIV2 模式下, tx\_full\_clk 调整为半速。 tx\_half\_clk 仅用于 16 位总线接口。

- 3. 10 位 SERDES only 模式或 SDI 模式。

### 全速和半速(DIV2)之间的动态开关

本章节说明了如何在全速和半速 (DIV2) 之间进行动态的开关控制。

两种速率模式控制信号通过或门,如图 8-8 所示。

### 图 8-8. 速率模式控制信号

tx\_div2\_mode\_chx\_c 是 FPGA 结构发送给 TX 的输入控制信号。

rx\_div2\_mode\_chx\_c 是 FPGA 结构发送给 RX 的输入控制信号。

Rate Mode Tx(CH 14[1]) 是针对 TX 路径的控制寄存器位。

Rate Mode Rx(CH 15[1]) 是针对 RX 路径的控制寄存器位。

在 rx 线上, pcs\_rst 需在开关切换后发出。

在tx线上,换为新速率时无需复位。

### 参考时钟源

### refclkp, refclkn

专用 CML 输入。除非使用其他的时钟源,这是 rx 和 tx 首选的时钟源。时钟信号可能是 CML、 LVDS 或 LVPECL。请参见 TN1114C,莱迪思 SERDES 的电气建议,例如接口电路。

#### fpga\_txrefclk, fpga\_rxrefclk

来自 FPGA 逻辑的参考时钟。主时钟引脚(PCLK)应作为 FPGA 的时钟输入引脚。时钟信号可能是 CML、LVDS、LVPECL 或单端。

#### **FPGA PLL**

当 FPGA PLL 用作参考时钟,连到 PLL 的参考时钟应分配给一个专用的 PLL 输入引脚。在更高的数据速率情况下, FPGA PLL 输出抖动可能会不能满足系统特性。不推荐在抖动敏感的应用中使用一个 FPGA PLL。

### 扩频时钟 (SSC) 支持

链路两端的端口必须一直以两者之间低于 600pm 的速率差异传输数据。这个规定允许比特率时钟源有 +/- 300ppm 容限。必须遵守最小的时钟周期。首选的方法是调整扩展技术,不允许超过调制的额定频率。数据速率可在 0%至 - 0.5%的额定频率范围内进行调制。调制率在不超过 30KHz 到 33KHz 的范围内。根据 +/- 300ppm 的容限,这里要求,当数据使用 SSC 调制时,两个端口需要相同的比特率时钟。

在 PCI Express 应用中,根复合体(root complex)是负责扩频参考时钟,然后端点 (endpoint)基本上使用相同的时钟,通过 TX 返回频谱。因此,不需要单独的 RXREFCLK。主要应用是在插件卡上。插件卡无须使用来自连接器的 REFCLK,但必须接收和发送与 PCI Express 连接器 REFCLK 相同的 SSC。

虽然 LatticeECP3 架构允许在一个 quad 中混合 PCI Express 通道和千兆以太网、串行 RapidIO 或 SGMII 通道,使用 PCI Express SSC 作为发送参考时钟将会导致违反千兆以太网、串行 RapidIO 和 SGMII 发送抖动参数的规定。

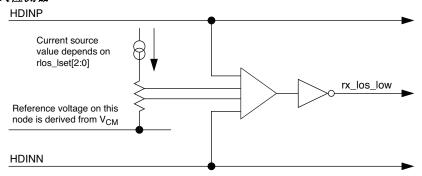

### 信号丢失

每个通道包含一个可编程的信号丢失检测器,如图 8-9 所示。

信号丢失阈值由可编程电流源的值决定。电流源值使用rlos\_lset[2:0] 控制位来选择。阈值检测的结果通过rx\_los\_low 状态信号标示给 FPGA。

#### 图 8-9. 信号丢失检测器

Note: rx\_los\_low shows that a signal has been detected for data rates above 1 Gbps with a maximum CID (Consecutive Identical Digits) of 7 bits (i.e., a minimum input signal transition density as is sent by 8b10b).

rx\_los\_low is supported with a default setting of rlos\_lset[2:0] = 2, except in PCI Express mode and SDI mode. In PCI Express mode, 2 and 3 are supported.

In SDI mode, it is recommended to use the carrier detect output signal (/CD) from the external SDI cable equalizer.

### 表 8-8. 信号丢失检测器的响应时间

| 说明                                 | 最小值 | 典型值 | 最大值 | 单位 |

|------------------------------------|-----|-----|-----|----|

| 检测到信号丢失所需的时间 (rx_los_low 从 0 变为 1) | _   | 8   | 10  | ns |

| 检测到信号出现所需的时间 (rx_los_low 从 1 变为 0) | _   | 8   | 10  | ns |

### 失锁

发送 PLL 和单独通道 CDR 都有数字的基于计数器的失锁检测器。如果发送 PLL 失锁,发出 PLL 失锁信号,并且将一直发出该信号,直到 PLL 重新获得锁定。如果 CDR 失锁,该通道将发出失锁信号并锁定参考时钟,使 CDR 中的 VCO 重新开始训练。完成后,通道的失锁信号释放, CDR 转回锁定传进来的信号。 CDR 将继续锁定数据,或返回再次失锁状态,这样的话将重复再训练周期。有关 CDR 失锁的详细信息,请参阅本文档中的 SERDES/PCS 复位章节。

### 表 8-9. 锁丢失检测器的响应时间

| 说明                                            | 最小值 | 典型值 | 最大值 | 单位 |

|-----------------------------------------------|-----|-----|-----|----|

| 检测到回路失锁所需的时间 (tx_pll_lol, rx_cdr_lol, 0 变为 1) | _   | 200 | 500 | us |

| 检测到回路锁定所需的时间 (tx_pll_lol, rx_cdr_lol, 1 变为 0) | _   | 200 | 500 | us |

### TX 通道间偏移

控制信号 tx\_sync\_qd\_c 复位所有有效的 TX 通道,从 bit 0 开始串行化。大多数多通道协议标准要求确保 TX 通道间偏移在一个确定的规定值范围内。

TX 串行器的复位通常是由于 tx\_sync\_qd\_c 信号跳变或 PLL 锁定丢失时刻而产生的。

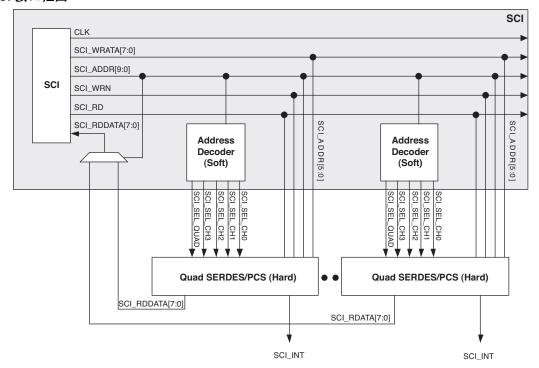

### SERDES PCS 配置设置

LatticeECP3 PCS 可配置用于各种应用。使用 IPexpress 模块生成器工具选择设置,允许用户选择 PCS 的模式和特性选项。选项选择保存在自动配置文件中,之后位流生成器可以用它来将用户选择写入位流。更改 PCS 选项选择时,推荐用户重新运行 IPexpress,产生一个新的 PCS 模块,并创建一个新的自动配置文件。在运行位流生成器之前,一些选项可通过手动编辑自动配置文件来进行更改。配置之后, PCS 选项可通过可选的 SERDES 客户端接口总线写入 PCS 寄存器来进行动态修改。SERDES 客户接口允许 SERDES/PCS quad 通过寄存器来进行控制,以不同于原来的配置存储器单元。可通过 SCI 访问的控制和状态寄存器表请参见附录 A。

## 自动配置文件

每个 PCS 模式的初始寄存器设置可通过使用 IPexpress 中的自动配置功能实现。模块生成器提供了一个自动配置文件,包含了所选模式下 quad 和通道寄存器的设置。可参考这个文件来进行前端仿真,还可以集成到位流中。当一个自动配置文件集成到位流中,那么在配置过程中,所有的 quad 和通道寄存器将根据自动配置文件定义的值进行设置。如果在工作时,用户需要更改控制寄存器或监控状态寄存器,那么设计中必须包含 SCI。

### 发送数据

PCS quad 发送数据路径的每通道包含一个8b10b编码器和串行器。

### 8b10b 编码器

该模块实现了一个 8b10b 编码器,符合 IEEE 802.3ae-2002 1000BASE-X 规范标准。编码器根据规范实现 8 位到 10 位的代码转换,并且同时遵守所规定的运行(running disparity)规则。 8b10b 编码器可通过在每个通道上将 CHx 8B10B 属性设置为 "BYPASS" 来将其旁路,其中 x 是通道编号。

#### 串行器

8b10b 编码数据进行了并到串转换并且通过嵌入式 SERDES 进行片外传送。

### 接收数据

PCS quad 接收数据路径的每个通道包含以下子模块:解串行器、字对齐、8b10b解码器、可选的链路状态机以及可选的接收时钟容限补偿(CTC)FIFO。

#### 解串行器

数据是在传至片上到嵌入式 SERDES 的过程中从串行变为并行的。

#### 字对齐 (字节边界检测)

这个模块执行 comma 这一字符检测和对齐操作。接收逻辑使用逗号 (comma) 字符来对传入数据流进行 10 位字符的字对齐。逗号 (comma) 的描述可以查阅 802.3.2002 1000BASE-X 规范的 36.2.4.9 章节,以及 10GBASE-X 规范 48.2.6.3 章节的图 48-7。

字对齐模块支持大量可编程选项:

- 字对齐控制由嵌入式链路状态机(LSM)或 FPGA 控制实现。除了 8b10b 数据包模式外,还支持 8 位 SERDES Only、10 位 SERDES Only 以及 SDI 模式。

- 可以设置两种可编程字对齐字符(通常一个用于 positive disparity,一个用于 negative disparity)以及一个可编程的每位掩码寄存器用于对齐比较。对齐字符和掩码寄存器可按每个 quad 来设置。对于许多协议来说,字对齐字符可设为 "XX00000011"(jhgfiedcba 位用于 positive disparity comma 字符对应代码组 K28.1、 K28.5 和 K28.7)以及 "XX01111100"(jhgfiedcba 位用于 negative disparity comma 字符对应代码组 K28.1、 K28.5 和 K28.7)。但是,用户也可定义任意 10 位模式。

- 第一个对齐的字符由分配给属性 COMMA A的 10位数值所定义。该值适用于 PCS quad 中的所有通道。

- 第二个对齐的字符由分配给属性 COMMA\_B 的 10 位数值所定义。该值适用于 PCS quad 中的所有通道。

• 掩码寄存器定义了要比较哪个字对齐位 (掩码寄存器中值为 '1'的位表示需要检查字对齐字符寄存器中的相应位)。掩码寄存器由 COMMA\_M 属性的 10 位值决定。此值适用于 PCS quad 中的所有通道。当属性 CHx\_RXWA (字对齐)设置为 "ENABLED",并且 CHx\_ILSM (内部链路状态机)设置为 "ENABLED",某个基于协议的链路状态机的工作将控制字对齐。若欲了解更多有关基于协议的链路状态机的工作的信息,请参见下面特定协议的链路状态机章节。

### 8b10b 解码器

8b10b 解码器实现了一个 8b10b 解码器操作,符合 IEEE 802.3-2002 参数规范标准。解码器根据规范实现 10 位到 8位的代码转换,并且同时遵守所规定的运行差异规则。当检测到代码违例时,接收数据 rxdata 设为 0xEE, rx\_k\_chn 设为 '1'。

## 外部链路状态机选项

当属性 CHx\_ILSM (内部链路状态机)设为 "DISABLED",并且 CHx\_RXWA (字对齐)设为 "ENABLED",控制信号 word\_align\_en\_ch(0-3)用于使能字对齐。这个信号应当由 FPGA 结构中实现的 FPGA 外部链接状态机产生。当word\_align\_en\_ch(0-3)\_c 为高电平时,字对齐将锁定对齐位并保持锁定状态。它将停止输入数据与用户定义的字对齐字符的比较,并保持当前第一次比较成功的 COMMA\_A 或 COMMA\_B 的对齐状态。如果需要重新对齐,触发word\_align\_en\_ch(0-3)\_c 信号由低电平变为高电平。字对齐将重新锁定下一次符合用户定义的字对齐字符的输入。如果需要,word\_align\_en\_ch(0-3)\_c 可通过 PCS quad 外部实现的链路状态机控制,仅在特定条件下允许对字对齐进行更改。

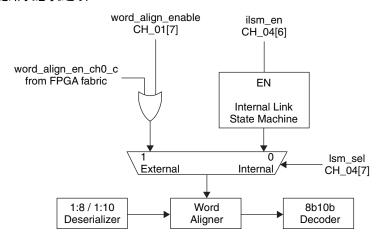

图 8-10 说明了链路状态机选项。

#### 图 8-10. PCS 字对齐和链路状态机选项

当选择了一个链路状态机并在某一通道使能后,一旦链路同步成功,该通道的 lsm\_status\_ch(0-3)\_s 状态信号将变为高电平。

## 千兆以太网模式下的 Idle 信号插入

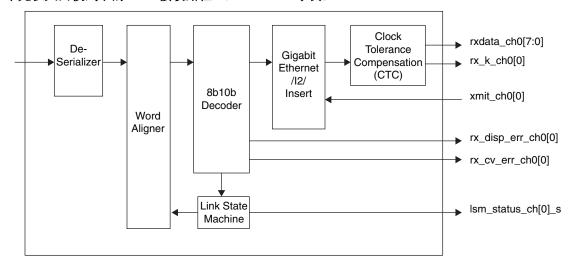

PCS 设为千兆以太网模式,将 /l2/ 信号插入接收数据流用以自动协商。千兆以太网自动协商以软逻辑方式执行。该功能以每2048个时钟周期插入连续的8个/l2/有序集。/l2/插入由输入到PCS的xmit\_ch(0-3)信号来控制,xmit\_ch(0-3)信号由自动协商软逻辑来驱动。图 8-11 说明了当 PCS 设为千兆以太网模式时,接收逻辑的一个通道(此示例中的 channel 0),并说明了这些控制 / 状态信号。

图 8-11. 千兆以太网模式下的 PCS 接收路径 (Channel 0 示例)

## 时钟容限补偿

时钟容限补偿(CTC)模块执行恢复的接收时钟和锁定的参考时钟之间的时钟速率调整。时钟补偿是通过在预先定义的位置插入或删除数据字节来实现的,并且同时保证不会造成数据包丢失。16字节的CTC FIFO 用于在两个时钟域之间传输数据,并且将在LatticeECP3 SERDES 规定的最大 ppm 容限范围内允许时钟差异。(请参见 LatticeECP3 系列数据手册中的直流和开关特性章节)。

在通道属性 CHx\_CTC 设为 "ENABLED" 时,该通道就使能了时钟容限补偿模块。当通道属性 CHx\_CTC 设为 "DISABLED" 时, CTC 就被旁路。

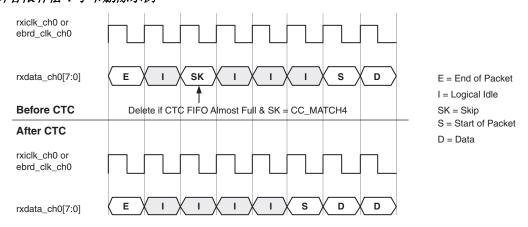

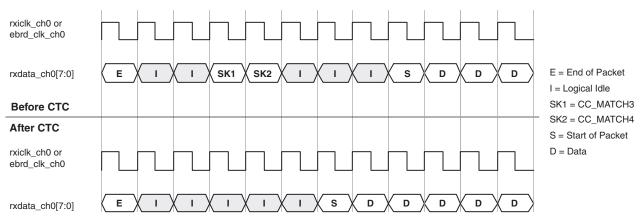

1字节删除的图示说明如图 8-12 所示。

图 8-12. 时钟容限补偿 1 字节删除示例

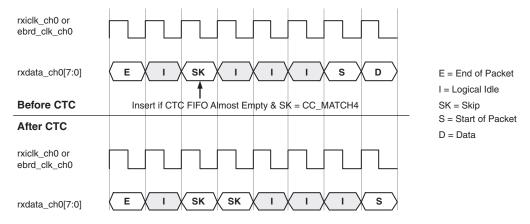

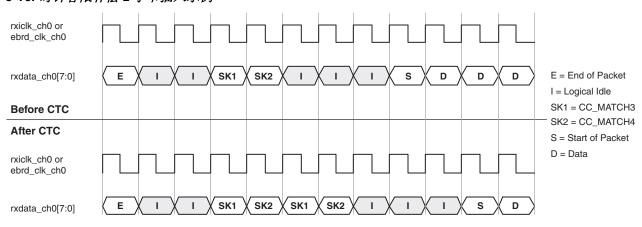

1字节插入的图示说明如图 8-13 所示。

### 图 8-13. 时钟容限补偿 1 字节插入示例

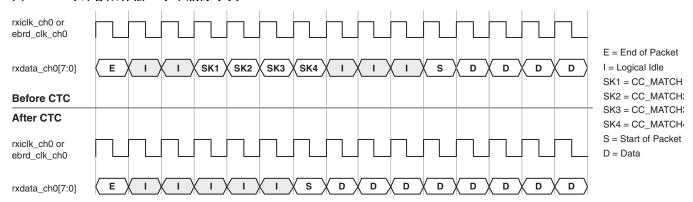

2字节删除的图示说明如图 8-14 所示。

### 图 8-14. 时钟容限补偿 2 字节删除示例

2字节插入的图示说明如图 8-15 所示。

### 图 8-15. 时钟容限补偿 2 字节插入示例

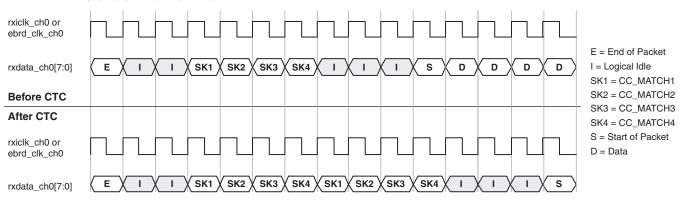

4字节删除的图示说明如图 8-16 所示。

#### 图 8-16. 时钟容限补偿 4 字节删除示例

4字节插入的图示说明如图 8-17 所示。

#### 图 8-17. 时钟容限补偿 4 字节插入示例

当使用 CTC 时,针对不同的应用,对时钟补偿必须做以下适当的设置:

- 使用 CC\_MATCH\_MODE 属性设置插入 / 删除模式长度。该属性设置了在执行插入和删除之前, CTC 所比较的 跳过字节(skip byte)的数目。 CC\_MATCH\_MODE 的值为 "1"(1 字节插入 / 删除)、"2"(2 字节插入 / 删除)以及 "4"(4 字节插入 / 删除)。最小的数据包间间隙也必须根据目标应用适当地进行设置。数据包间间隙通过属性 CC\_MIN\_IPG 来指定。 CC\_MIN\_IPG 的允许值为 "0"、"1"、"2" 和 "3"。跳过字符删除后允许的最小数据包间间隙按照表 8-10 中这些属性的设置来执行。

- 跳过字节或定序集必须按照所选的CC\_MATCH\_MODE进行设置。对于4字节插入/删除(CC\_MATCH\_MODE = "4"),第一个字节必须分配给属性 CC\_MATCH1,第二个字节必须分配给属性 CC\_MATCH2,第三个字节必须分配给属性 CC\_MATCH3,并且第四个字节必须分配给属性 CC\_MATCH4。所有的都为 10 位二进制值。

#### 例如:

如果 4 字节跳过定序集设置为 /K28.5/D21.4/D21.5/D21.5,那么 "CC\_MATCH1" 应设为 "0110111100", "CC\_MATCH2" = "0010010101", "CC\_MATCH3" = "0010110101" 并且 "CC\_MATCH4" = "0010110101"。

对于 2 字节插入 / 删除 (CC\_MATCH\_MODE = "2"),第一个字节必须分配给属性 CC\_MATCH3,并且第二个字节必须分配给属性 CC\_MATCH4。

对于 1 字节插入 / 删除 (CC MATCH MODE = "1"), 跳过字节必须分配给属性 CC MATCH4。

- 时钟补偿 FIFO 的高位水印和低位水印必须根据所使用的协议进行适当的设置。设置值的范围可从 0 至 15, 并且高位水印必须设置比低位水印更高的值(两者不可设为相同的值)。高位水印值通过给属性 CCHMARK 一个值来设置。 CCHMARK 的允许值以十六进制表示,从 "0" 到 "F"。低位水印值通过给属性 CCLMARK 一个值来设置。 CCLMARK 的允许值以十六进制表示,从 "0" 到 "F"。

- 当通过 ispLEVER 模块生成器生成 PCS 模块时,如果选择了 "Error Status Ports",根据 PCS/FPGA 接口的 cc overrun ch(0-3),可以对每个通道上的时钟补偿 FIFO 过载进行监测。

- 当通过 ispLEVER 模块生成器生成 PCS 模块时,如果选择了 "Error Status Ports",根据 PCS/FPGA 接口的 cc underrun ch(0-3),可以对每个通道上的时钟补偿 FIFO 欠载进行监测。

### 计算最小的数据包间间隙

表 8-10 显示了数据包间间隙的用户自定义值(由 CC\_MIN\_IPG 属性定义)和确保的最小数据包间字节数之间的关系,这个最小数据包间字节数是指,从 PCS 跳过字符删除后的最小数据包间字节数。表中将数据包间间隙显示为一个乘数。数据包间最小字节数等于每次插入 / 删除的字节数乘以表中所列的乘数。例如,如果每次插入 / 删除的字节数为 4(CC\_MATCH\_MODE 设为 "4"),并且最小的数据包间间隙属性 CC\_MIN\_IPG 设为 "2",那么最小的数据包间间隙等于 4(CC\_MATCH\_MODE = "4")乘以 3(表 8-10 中 CC\_MIN\_IPG = "2")或 12 字节。PCS 不会执行跳过字符删除,直到最小的数据包间字节数通过 CTC。

### 表 8-10. 最小的数据包间间隙乘数

| CC_MIN_IPG | 插入/删除<br>乘数 |

|------------|-------------|

| 0          | 1x          |

| 1          | 2x          |

| 2          | 3x          |

| 3          | 4x          |

请注意带有 TW 后缀的 LatticeECP3-150EA 器件系列的 CTC 支持: 对于初始版本的带有 TW 后缀的 LatticeECP3-150EA 器件是不支持 PCS 中 CTC 的。CTC 功能可以被旁路,并在软 IP 中实现。目前莱迪思提供的许多 IP 核是以软逻辑形式实现 CTC 逻辑。

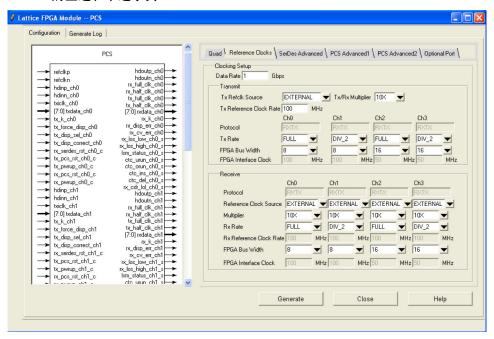

### 使用 Diamond 中的 IPexpress

IPexpress 是用以创建和配置 SERDES 和PCS 块的。设计师们使用图形用户界面来为特定 quad 或通道选择 SERDES 协议标准。IPexpress 从这个图形用户界面获得输入并产生配置文件(.txt 文件)和 HDL 网表。 HDL 模型用于仿真和综合流程。配置文件包含属性层映射信息。这个文件是仿真和 ispLEVER bitgen 程序的输入。强烈推荐设计师们在 IPexpress 中进行更改和更新,然后重新生成配置文件。在一些例外情况下,用户可以修改配置文件。

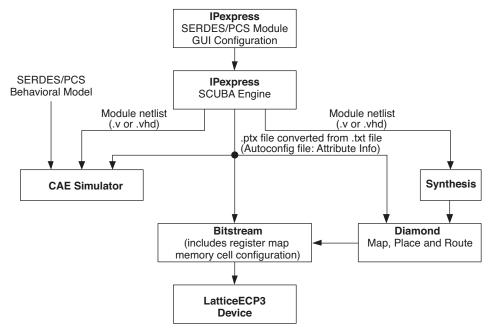

图 8-18 显示了当使用 IPexpress 为 SERDES 协议标准生成 SERDES/PCS 块时的工具流程。

## 图 8-18. SERDES\_PCS Diamond 用户流程

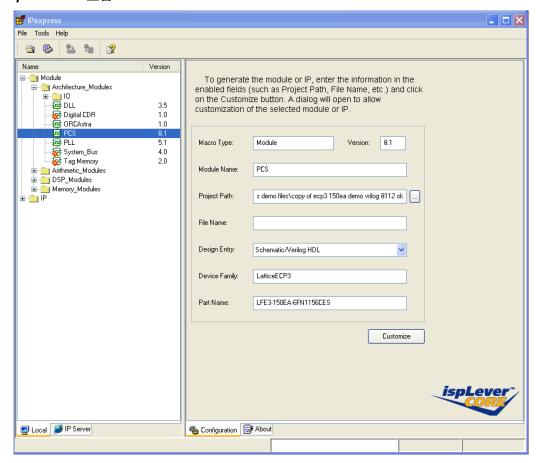

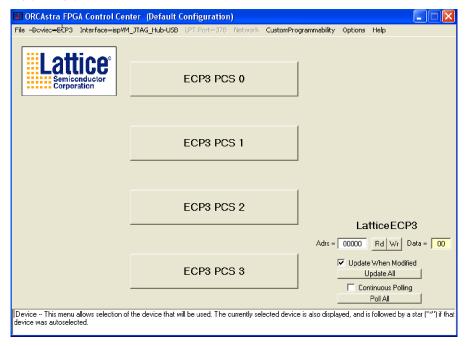

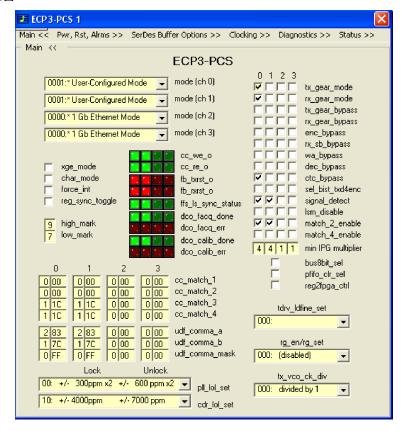

# IPexpress 中的 PCS 模块生成器

图 8-19 显示了在 IPexpress 图形用户界面中选择 PCS 时的主窗口。

### 图 8-19. IPexpress PCS 主窗口

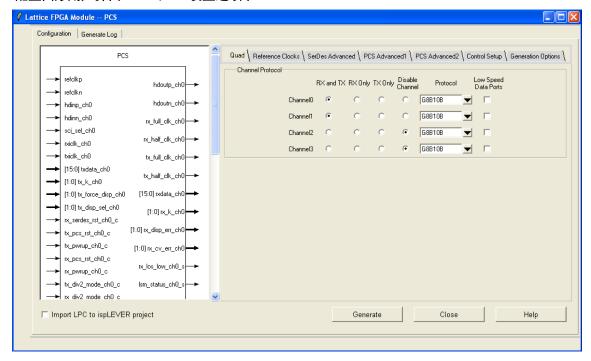

#### Quad 设置选项卡

图 8-20 显示了当输入了文件名并且在主窗口中勾选了 Customize 按钮后, Quad 设置选项卡窗口。在这个窗口中首先必须要求输入的是要为每个通道选择一种协议模式。每个通道可以配置为 'RX and TX'、'RX Only'、'TX Only'、'Disabled'或'Low Speed Data Port'。

### 图 8-20. 配置图形用户界面 ——Quad 设置选项卡

表 8-11. SERDES PCS 图形用户界面属性——Quad 选项卡设置

| 图形用户界面内容                     | 属性名称         | 属性范围                                                                   | 默认值      |

|------------------------------|--------------|------------------------------------------------------------------------|----------|

| Channel Protocol             | CHx_MODE     | RX and TX, RX Only, TX Only                                            | DISABLED |

| Disable Channel <sup>1</sup> | CHx_MODE     | ENABLE, DISABLE                                                        | DISABLED |

| Protocol                     | CHx_PROTOCOL | GIGE, SGMII, XAUI, SRIO, PCIE, SDI, G8B10B, 10BSER, 8BSER, CPRI, OBSAI | G8B10B   |

| Low Speed Data Port          |              |                                                                        | DISABLED |

1. 对于 328-ball csBGA 封装的 LatticeECP3-17EA 器件,仅 channel 0 和 3 可用。

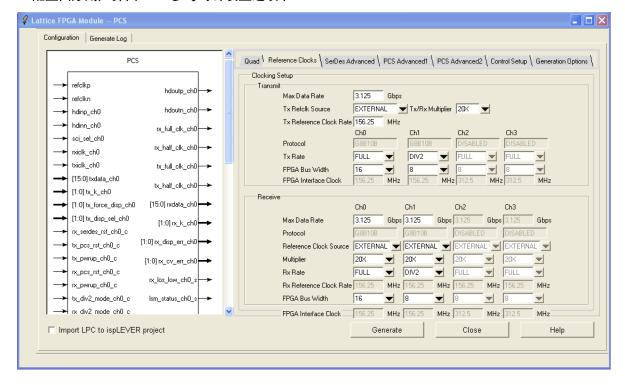

### 参考时钟设置选项卡

在该选项卡中,选择 TX 和 RX 参考时钟源的属性。用户可以选择 EXTERNAL 或 INTERNAL 参考时钟。此外,还有一个工具来提供所需要的时钟速率以及用于特定数据速率的乘法器设置。除此之外,对于给定的数据总线宽度,工具提供通道到内核接口所需的时钟速率。

#### 图 8-21. 配置图形用户界面—— 参考时钟设置选项卡

## 表 8-12. SERDES\_PCS 图形用户界面属性 —— 参考时钟设置选项卡

| 图形用户界面内容                    | 属性名称                      | 范围                     | 默认值<br>(图形用户界面) | 默认值<br>(属性) |  |  |

|-----------------------------|---------------------------|------------------------|-----------------|-------------|--|--|

| Transmit                    | Transmit                  |                        |                 |             |  |  |

| Max. Data Rate <sup>1</sup> | N/A                       | 0.23 至 3.2 Gbps        | 2.5 Gbps        | N/A         |  |  |

| TX Refclk Source            | PLL_SRC                   | INTERNAL, EXTERNAL     | INTERNAL        | REFCLK_INT  |  |  |

| TX/RX Multiplier            | REFCK_MULT                | 8X, 10X, 16X, 20X, 25X | 根据协议            |             |  |  |

| TX Reference clock Rate     | #REFCLK_RATE <sup>2</sup> |                        | 根据协议            |             |  |  |

| Protocol                    | 用户无法访问。仅供参考。              |                        |                 |             |  |  |

| TX Rate                     | CHx_TX_DATA_RATE          | FULL, DIV2, DIV11      | FULL            | FULL        |  |  |

| FPGA Bus Width              | CHs_TX_DATA_WIDTH         | 8, 10, 16, 20          | 根据协议            |             |  |  |

| FPGA Interface Clock        | #CH0_TX_FICLK_RATE        |                        |                 |             |  |  |

| Receive                     |                           |                        |                 |             |  |  |

| Max. Data Rate <sup>1</sup> | N/A                       | 0.23 至 3.2 Gbps        | 2.5 Gbps        | N/A         |  |  |

| Protocol                    | 用户无法访问。仅供参考。              |                        |                 |             |  |  |

| Refclk Source               | CHx_CDR_SRC               | INTERNAL, EXTERNAL     | INTERNAL        | REFCLK_INT  |  |  |

| Multiplier                  | 用户无法访问。仅供参考。              |                        |                 |             |  |  |

| RX Rate                     | CHx_RX_DATA_RATE          | FULL, DIV2, DIV11      | FULL            | FULL        |  |  |

| RX Reference Clock Rate     | #CH0_RXREFCLK_RAT<br>E    |                        |                 |             |  |  |

| FPGA Bus Width              | CHx_RX_DATA_WIDTH         | 8, 10, 16, 20          | 根据协议            |             |  |  |

| FPGA Interface Clock        | #CH0_RX_FICLK_RATE        |                        |                 |             |  |  |

<sup>1.</sup> 速率并不反映在自动配置文件中。相反, DATARATE RANGE 是为特定数据速率所指定的,如 :150 Mbps ≤ LOWLOW ≤ 230 Mbps, 230 Mbps < LOW ≤ 450 Mbps, 450 Mbps < MEDLOW ≤ 0.9 Gbps, 0.9 Gbps < MED ≤ 1.8 Gbps, 1.8 Gbps < MEDHIGH ≤ 2.55 Gbps, 2.55 Gbps < HIGH ≤ 3.2Gbps。

<sup>2. &#</sup>x27;#' 后面的属性表示仅供参考。这些属性也包括在自动配置文件中,以便参考。

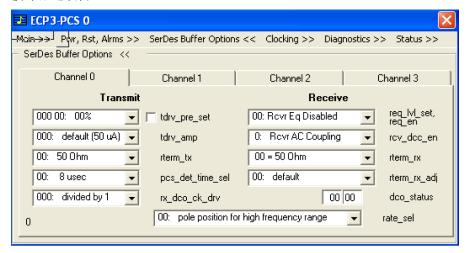

#### SERDES 高级设置

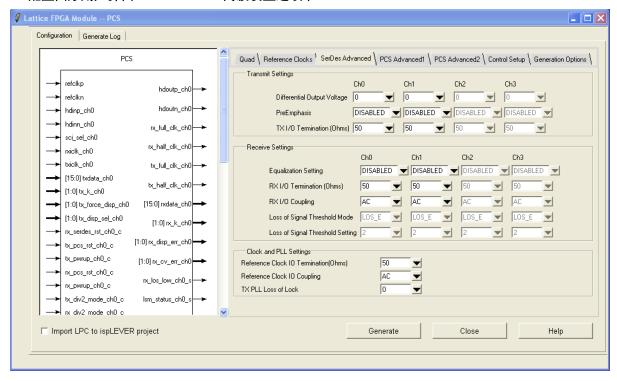

该选项卡是用于访问发送和接收 SERDES 的所有 4 个通道的高级属性的。选择发送属性,如: PreEmphasis、Termination、Differential Output Voltage。选择接收属性,如: Equalization、Termination、I/O Coupling。还可以选择发送 SERDES 时钟和 PLL 的属性。

## 图 8-22. 配置图形用户界面——SERDES 高级设置选项卡

### 表 8-13. SERDES PCS 图形用户界面属性——SERDES 高级设置选项卡

| 图形用户界面内容                                                   | 属性名称                  | 值                                                                                                                                                                                       | 默认值              |

|------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Differential Output Voltage                                | CHx_TDRV <sup>8</sup> | -4 (640mV) <sup>5</sup> , -3 (780mV), -2 (870mV), -1 (920mV), 0 (1040mV:default), 1 (1130mV) <sup>6</sup> , 2 (1260mV) <sup>7</sup> , 3 (1350mV) <sup>7</sup> , 4 (1440mV) <sup>7</sup> | 0                |

| PreEmphasis                                                | CHx_TX_PRE            | Disabled, 0 (0%), 1 (5%), 2 (12%), 3 (18%), 4 (25%), 5 (33%), 6 (40%), 7 (48%)                                                                                                          | DISABLED         |

| TX I/O Termination (Ohms) <sup>3</sup>                     | CHx_RTERM_TX          | 50, 75, 5K                                                                                                                                                                              | 50               |

| Equalization <sup>1</sup>                                  | CHx_RX_EQ             | Disabled, Mid_Low, Mid_Med, Mid_High, Long_Low, Long_Med, Long_High                                                                                                                     | DISABLED         |

| RX I/O Termination (Ohms) <sup>3</sup>                     | CHx_RTERM_RX          | 50, 60, 75, High                                                                                                                                                                        | 50               |

| RX I/O Coupling                                            | CHx_RX_DCC            | AC, DC                                                                                                                                                                                  | AC <sup>2</sup>  |

| Loss of Signal Threshold                                   | CHx_LOS_THRESHOLD_LO  | 2 (+15%),3 (+25%)                                                                                                                                                                       | 2 <sup>4</sup>   |

| TX PLL Reference Clock I/O Termination (Ohms) <sup>3</sup> | PLL_TERM              | 50, 2K                                                                                                                                                                                  | 50               |

| TX PLL Reference Clock I/O Coupling                        | PLL_DCC               | AC, DC                                                                                                                                                                                  | AC <sup>10</sup> |

| PLL Loss of Lock                                           | PLL_LOL_SET           | 0: +/- 1350ppm x2 <sup>9</sup><br>1: +/- 2400ppm x2<br>2: +/- 6800ppm<br>3: +/- 400ppm                                                                                                  | 0                |

- 1. 参见表 8-106 了解详细信息。

- 2. 内部片上 AC 耦合电容的典型值是 5 pF。

- 3. 端接电阻及它们的使用:

#### RX I/O 端接:

- -50: 除了 SMTPE, 目前所有的协议都使用一个 50 欧姆的端接电阻。

- -60: 以供灵活选择。

- 75: SMPTE 使用一个 75 欧姆的端接电阻。

- HIGH: 不使用 Rx 时的默认值。

#### TX I/O 端接:

- -50:除了 SMTPE,目前所有的协议都使用一个 50 欧姆的端接电阻。

- 75: SMPTE 使用一个 75 欧姆的端接电阻。

- 5K 如 PCI Express 电气空闲和 PCI Express RX 检测。用户不需要为 RX 检测设置该端接值。请参见 PCI Express 接收器检测章节。 TX PLL 端接:

- 50: 如果印刷电路板上没有 50 欧姆的端接电阻。

- 2K: 如果印刷电路板上有 50 欧姆的端接电阻。

- 4. PCS 配置,对于除 PCI Express 外的所有协议,图形用户界面仅支持值 2。对于 PCI Express,值 2 和值 3 都支持。

- 5. TDRV\_AMP\_BOOST(CH\_13[3]) 设为 1,以实现该信号幅度。

- 6. 该设置是 PCI Express 的默认设置。使用 PCI Express 协议时,推荐使用该默认设置。因而 IPexpress 图形用户界面中 TDRV 下拉窗口是不可更改的,显示为灰色。其他设置可仍然通过编辑 autoconfig 文件 (.txt 文件) 中的 CHn TDRV 属性来使用。

- 7. 这些设置中的 VCCOB 必须为 1.5V。

- 8. 这些值为典型值。对于整个频率范围内大约有 +/-20% 的裕度。请参见表 8-105 中 CHn\_TDRV 行,了解详细信息。

- 9. 'x2' 为内部 LOL 计数器中成功的 ppm 双倍计数。

- 10. 推荐在大多数应用中使用交流耦合。直流耦合应当仅与外部交流耦合电容结合使用。

#### PCS 位置的指定

用户可以通过约束文件 (.lpf) 来指定其希望的 PCS quad 位置。使用约束 "locate"。语法示例如下所示。

LOCATE COMP "pcs inst name" SITE "PCSB" ;

Quad 名称 位置名称

Quad A PCSA

Quad B PCSB

Quad C PCSC

Quad D PCSD

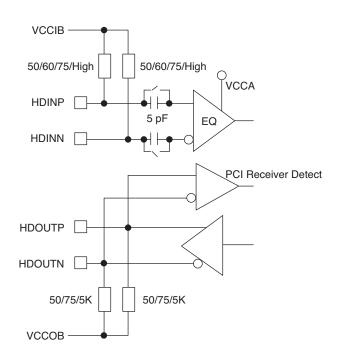

高速 I/O 端接拓扑结构如图 8-23 所示。

### 图 8-23. 高速 I/O 端接

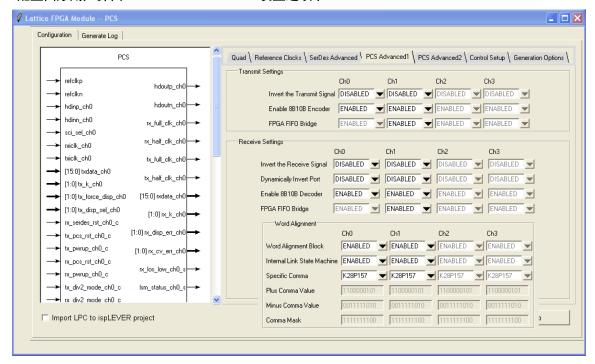

### PCS Advanced1 设置

通过此选项卡可访问所有四个通道的发送和接收PCS的高级属性。每个TX和RX通道的极性和工作模式(如8b10b)可以独立进行选择。此外,字对齐值也可以选择,如 comma 值、 comma 掩码和 comma 对齐。

## 图 8-24. 配置图形用户界面 ——PCS Advanced1 设置选项卡

### 表 8-14. SERDES/PCS 图形用户界面 ——PCS Advanced1 设置选项卡

| 图              | 形用户界面内容                    | 属性名称                     | 默认值        |

|----------------|----------------------------|--------------------------|------------|

| Transmitter    | Invert the Transmit Signal | CHx_TX_SB                | DISABLED   |

|                | Enable 8b10b Encoder       | CHx_TX_8B10B             | 根据协议       |

|                | FPGA FIFO Bridge           | CHx_TX_FIFO              | 根据协议       |

| Receiver       | Invert the Receive Signal  | CHx_RX_SB                | DISABLED   |

|                | Dynamically Invert Port    | N/A                      | DISABLED   |

|                | Enable 8b10b Decoder       | CHx_RX_8B10B             | 根据协议       |

|                | FPGA FIFO Bridge           | CHx_RX_FIFO              | 根据协议       |

| Word Alignment | Word Alignment Block       | CHx_RXWA                 | 根据协议       |

|                | Internal Link              | CHx_ILSM                 | 根据协议       |

|                | Specific Comma             | #CHx_SCOMMA              | 根据协议       |

|                | Plus Comma Value           | CHx_COMMA_A <sup>1</sup> | 1100000101 |

|                | Minus Comma Value          | CHx_COMMA_B              | 0011111010 |

|                | Comma Mask                 | CHx_COMMA_M              | 根据协议2      |

<sup>1.</sup> 根据定义,COMMA\_A 和 COMM\_B 是带有 positive 和 negative running disparity 的一组 8b10b 编码控制字符。用户必须提供符合协议的适当的 IDLE 序列来获得链接状态机同步。例如,1 GbE 协议需要 K28.5+D5.6 或 D16.2 用作 IDLE (字对齐和同步状态机)。默认值使用小端字节序格式。

<sup>2.</sup> 在大多数应用中, K28.5 用作逗号字符。默认的掩码值是 11111111111 。在 G8B10B 模式可以使用任意逗号字符, 因此掩码是 1111111100, 以检测所有的三种逗号字符, K28.1、28.5、28.7。

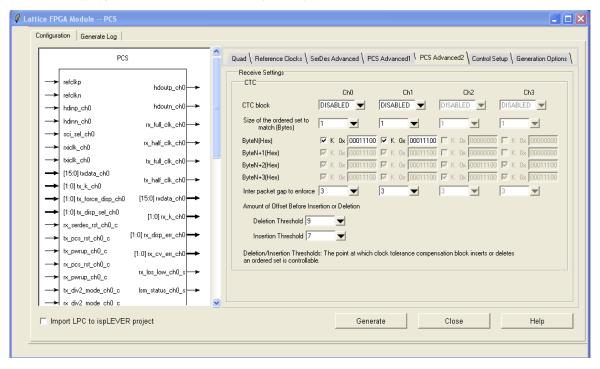

#### PCS Advanced2 设置

该选项卡用于为时钟容限补偿模块设置值。

### 图 8-25. 配置图形用户界面 ——PCS Advanced2 设置选项卡

### 表 8-15. SERDES/PCS 图形用户界面 ——PCS Advanced2 设置选项卡

| 图形用户界面内容            | 属性名称              | 默认值   |

|---------------------|-------------------|-------|

| CTC block           | CHx_CTC           | 根据协议1 |

| Size of ordered set | CHx_CC_MATCH_MODE | 根据协议  |

| Byte N              | CHx_CC_MATCH1     | 根据协议  |

| Byte N+1            | CHx_CC_MATCH2     | 根据协议  |

| Byte N+2            | CHx_CC_MATCH3     | 根据协议  |

| Byte N+3            | CHx_CC_MATCH4     | 根据协议  |

| Inter-packet gap    | CHx_CC_MIN_IPG    | 根据协议  |

| Deletion threshold  | CCHMARK           | 9     |

| Insertion threshold | CCLMARK           | 7     |

1. 始终禁止: XAUI、SDI、CPRI、OBSAI、10 位 SERDES 以及 8 位 SERDES。 始终使能: 串行 RapidIO。

所有其他模式:默认为禁止。在 IP 中提供大多数 CTC 功能。

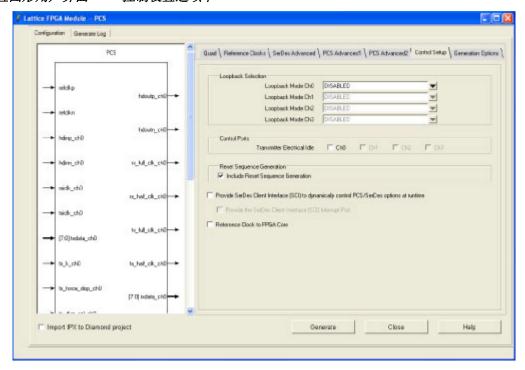

#### 控制设置

该选项卡是用于选择 SCI 接口和其他调试和控制选项的。此外,用户可以使能 SCI、错误报告、PLL quarter 时钟以及回环功能。

### 图 8-26. 配置图形用户界面—— 控制设置选项卡

表 8-16. 选项卡 5, SERDES\_PCS 图形用户界面属性 —— 控制设置选项卡

| 图形用户界面内容                                           | 属性名称                                                                                                                                | 默认值                   |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Loopback Mode (Ch0, Ch1, Ch2, Ch3)                 | DISABLED Loopback serial data after equalizer Loopback serial data after transmit driver Loopback parallel data after de_serializer | DISABLED <sup>1</sup> |

| Transmitter Electrical Idle                        | signal tx_idle_ch0_c is provided                                                                                                    | DISABLED              |

| Include Reset Sequence Generation <sup>2</sup>     | Include the TX and RX Reset Sequence                                                                                                | ENABLED               |

| Provide SERDES Client Interface                    | N/A                                                                                                                                 |                       |

| Provide the SERDES Client Interface Interrupt Port | INT_ALL                                                                                                                             | DISABLED              |

| Reference Clock to FPGA core                       | QD_REFCK2CORE                                                                                                                       | DISABLED              |

注: ispLEVER 8.0 中不支持复位序列发生器。

#### FPGA 核和复位序列的参考时钟

复位序列在复位状态机中使用参考时钟。

如果 Tx Refclk 时钟源选择 "Internal", 复位状态机使用内部参考时钟。

如果 Tx Refclk 时钟源选择 "External",复位状态机使用 Reference Clock to FPGA Core 信号,对用户而言该信号可见(控制寄存器位 QD\_0A[1] 置 1)。仅当选择了 "Reference Clock to FPGA Core" 时, REFCLK2FPGA 信号将包括在 wrapper 模块中。

<sup>1.</sup> 当回环模式在默认状态 (禁用)时,用户可以在 HDL 模块中使用两个 SERDES 桥并行回环控制信号 (sb\_felb\_ch[3:0]\_c 和 sb\_felb\_rst\_ch[3:0]\_c),动态打开和关闭回环模式。如果不使用回环模式,这些信号应连接到地。

<sup>2.</sup> 本文档的 SERDES/PCS 复位章节说明了复位序列产生。

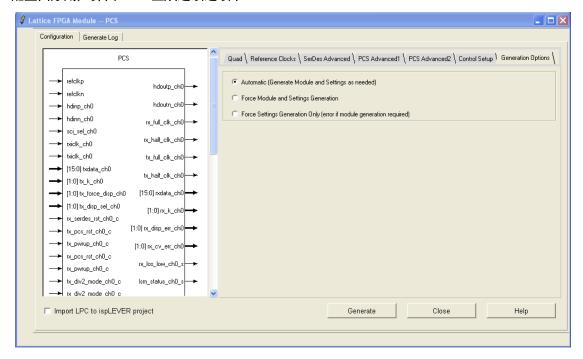

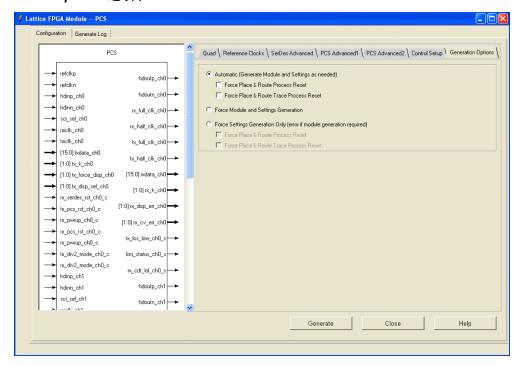

#### 生成选项

该选项卡为用户提供了选择 PCS 模块生成输出文件的选项。

#### 图 8-27. 配置图形用户界面—— 生成选项选项卡

当第一次将之前在旧的 Diamond 版本中创建的项目移植到最新的版本中时,强烈推荐在最新的版本中重新生成 PCS 模块,即使不需要做任何配置上的更改。这将确保使用最新的原始库文件。如果不这样做的话,设计可能在后续流程中失败,或者通过流程但是会在板上显示无法预计的错误。

当在现有的项目中重新生成 PCS 模块时,通常 HDL 文件保持不变,并且仅配置文件需要重新生成。在这种情况下,用户可以运行 "Generate Bitstream Data" 和 "Force One Level" 选项以节省编译时间。

- Automatic——选择该方式时,IPexpress将仅生成必须的文件。这可以包括 HDL 和 TXT 文件或仅 TXT 文件。这是默认设置。

- Force Module and Settings Generation——选择该方式时,将生成HDL和TXT文件。这将使项目导航器的处理过程强制复位到综合。

- Force Settings Generation Only——选择该方式时,将仅生成 TXT 文件。如果 HDL 生成是必需的,那么将会提供错误信息。

- 流程定义 —— 生成选项在两种模块处理流程的工作是不同的。

- HDL 源代码处理流程:项目导航器中的 HDL 文件 现有的 LPC 文件可以从 IPexpress 中打开,用以重新生成。在这种情况下,通过图形用户界面设置的复位点 将成为新的开始点。因而,当用户双击一个处理过程或者运行 "Force One Level"选项时,它将从复位点 开始运行。

- LPC 源代码处理流程:项目导航器中的 LPC 文件 打开 LPC 文件并重新生成 PCS 模块将重新复位整个处理过程,无论 HDL 模块是否重新生成。

在这两种情况下,处理过程窗口中的勾选记号将保持不变,但是一旦用户开始处理过程就会立即进行更新该过程的勾选记号状态。

#### 配置文件说明

IPexpress 生成了这个文件,包含属性级映射信息。仿真模型以及位流生成的过程都是用这个文件来自动将 PCSD quad 初始化为 IPexpress 中所选的模式。

配置文件使用"txt"作为文件类型扩展名。

下面是一个配置文件示例。

- # This file is used by the simulation model as well as the bitstream

- # generation process to automatically initialize the PCSD quad to the mode

- # selected in the IPexpress. This file is expected to be modified by the

- # end user to adjust the PCSD quad to the final design requirements.

| DEVICE NA | ME "LE | E3 - 9 | 5 | $\mathbf{E''}$ |

|-----------|--------|--------|---|----------------|

|-----------|--------|--------|---|----------------|

CHO MODE "RXTX" CH1 MODE "DISABLED" CH2 MODE "DISABLED" CH3\_MODE "DISABLED" "HIGH" TX DATARATE RANGE

PLL SRC "REFCLK EXT"

"10X" REFCK MULT #REFCLK RATE 250.0

"G8B10B" "RXTX" CHO PROTOCOL CH0 LDR CHO\_RX\_DATARATE\_RANGE "HIGH" CHO\_TX\_DATA\_RATE "FULL"

CHO\_TX\_DATA\_WIDTH "8"

CHO\_TX\_FIFO "DISABLED"

CHO\_CDR\_SRC "REFCLK\_EXT"

#CHO\_TX\_FICLK\_RATE 250.0

CHO\_RX\_DATA\_RATE "FULL"

CHO\_RX\_DATA\_WIDTH """ CHO RX DATA WIDTH

CHO RX FIFO "DISABLED" #CHO RX FICLK RATE 250.0 "O" CH0 TDRV

CHO TX PRE "DISABLED"

"50*"* CHO RTERM TX

"DISABLED" CHO RX EQ

**"**50**"** CHO RTERM RX "AC" CHO RX DCC

CH0\_LOS\_THRESHOLD\_LO "2"

CH0\_TX\_SB "DISABLED" "ENABLED" CHO TX 8B10B CHO RX SB "DISABLED" "ENABLED" "ENABLED" CHO RX 8B10B CHO RXWA "ENABLED"

"111111111" CH0 ILSM #CH0 SCOMMA CHO COMMA A "1100000101" "0011111010"

"1111111100" CHO COMMA B CHO COMMA M CHO\_CTC "ENABLED"

CHO CC MATCH MODE

CHO CC MATCH1 "0000000000"

| CH0_CC_MATCH2  | "0000000000" |

|----------------|--------------|

| CHO_CC_MIN_IPG | "3"          |

|                |              |

| CH0_SSLB       | "DISABLED"   |

| CH0_SPLBPORTS  | "DISABLED"   |

| CH0_PCSLBPORTS | "DISABLED"   |

| PLL_TERM       | "50"         |

| PLL_DCC        | "AC"         |

| PLL_LOL_SET    | "0"          |

| CCHMARK        | "9"          |

| CCLMARK        | "7"          |

| INT_ALL        | "DISABLED"   |

| QD_REFCK2CORE  | "ENABLED"    |

# 8 位和 10 位 SERDES-Only 模式

本章节说明了 SERDES/PCS 模块的两种工作模式, 8 位 SERDES-Only 和 10 位 SERDES-Only。这些模式都是专为需要访问高速 I/O 接口,并且无需 LatticeECP3 PCS 逻辑提供的基于协议的操作的应用而设计的。

#### 发送路径

• 串行器: 8 位或 10 位并行数据转换为串行数据。

#### 接收路径

- 解串行器: 串行数据转换为 8 位或 10 位并行数据。

- 用户定义的对齐模式下的可选字对齐。

# 通用 8b10b 模式

SERDES/PCS 块的通用 8b10b 模式是专用于需要 8b10b 编码 / 解码应用,并且无需额外特定协议的数据操作而设计的。 LatticeECP3 SERDES/PCS 块可支持通用 8b10b 应用,高达 3.2 Gbps/ 通道。在通用 8b10b 模式下,字对齐器可以由嵌入式 PCS 链路状态机(LSM)控制。

当选择并使能了嵌入式链路状态机时,一旦链接同步成功, lsm status ch[3:0] s 状态信号将变为高电平。

为了该模式下的链接同步,8b10b模式下SERDES通道接收器输入(hdinp\_ch[0-3]/hdinn\_ch[0-3])需要满足以下条件:

- 串行数据需要周期性的使用 8b10b 编码的逗号字符。需要周期性的使用是因为一旦没有同步,LSM 可以重新与逗号字符同步。逗号字符应该对应"特定逗号"值,如图 8-24 所示。例如,当特定逗号值设为 K28P157,串行链路上的逗号值应该为 K28.1 (k=1, Data=0x3C)、K28.5 (k=1, Data=0xBC) 或 K28.1 (k=1, Data=0xFC) 中任意一个的 8b10b 编码值。注意:通常 K28.5 是最常用的。

- 逗号字符后要紧跟一个数据字符

- 后一个逗号字符要在前一个逗号字符后的偶数个周期上出现

#### 其他信息:

- 需要大约四个有效的逗号 / 数据对, LSM 才能达到链路同步

- 四个连续错误(非法的 8b10b 编码字符、编码违例、不一致(disparity)错误、两个逗号间非偶数个时钟周期)可引发 LSM 未锁定

- CDR 失锁条件将导致 LSM 未锁定,大量的代码违例和不一致错误也将导致 LSM 未锁定

- 当使用内部复位序列状态机, CDR 失锁 (rx\_cdr\_lol\_ch[3:0]\_s) 或信号丢失 (rx\_los\_low\_ch[3:0]\_s) 条件,将导致 RX 复位序列状态机复位 SERDES 以及 LSM 未锁定

下面的两个例子说明了两个**逗号**之间有效和无效的偶数时钟周期边界的差别 (注: **C =** *逗号, D = 数据*)。

有效 (偶数) 逗号边界:

| 字时钟周期 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

|-------|---|---|---|---|---|---|---|---|---|---|----|----|

| 字符    | С | D | С | D | С | D | D | D | D | D | С  | D  |

无效 (奇数) 逗号边界:

| 字时钟周期 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

|-------|---|---|---|---|---|---|---|---|---|---|----|----|----|

| 字符    | С | D | С | D | С | D | D | D | D | С | D  | С  | D  |

在上面无效 (奇数) 逗号边界的例子中,逗号字符出现在周期 9 和 11,因而是无效的,因为它们不是在前一个逗号字符后的偶数个周期上出现。

此外,LSM 可以被禁用,字对齐器可由 FPGA 结构的 word\_align\_en\_ch[3:0]\_c 输入引脚控制。参见第 21 页 "外部 链路状态机选项"和第 33 页 "PCS Advanced1 设置",了解更多信息。

#### 发送路径

- 串行器

- 8b10b 编码器

## 接收路径

- 解串行器

- 根据用户定义的字对齐字符或来自嵌入式 GbE 链路状态机的字符进行字对齐

- 8b10b 解码

- 时钟容限补偿 (可选)

# 千兆位以太网和 SGMII 模式下的 Lattice ECP3 PCS

LatticeECP3 SERDES/PCS 块的千兆位以太网模式支持全面兼容,从串行 I/O 到 IEEE 802.3-2002 1000 BASE-X 千兆位以太网标准的 GMII/SGMII 接口。

#### 发送路径

- 串行器

- 8b10b 编码器

#### 接收路径

- 解串行器

- 基于 IEEE 802.3-2002 1000 BASE-X 定义的对齐字符的字对齐。

- 8b10b 解码

- 千兆以太网链路状态机符合图 36-9 中 (同步状态机, 1000BASE-X)的 IEEE 802.3-2002 标准,仅一点例外。图 36-9 要求接收 4 个连续正确的代码组,以使 LSM 从 SYNC\_ACQUIRED\_{N} (N=2,3,4) 变为 SYNC\_ACQUIRED\_{N-1}。而现在实际的 LSM 实现要求 5 个连续正确的代码组来触发转换。

- 千兆以太网载波检测: IEEE 802.3-2002 (1000BASE-X) 的 36.2.5.1.4 章节定义了 carrier\_detect 功能。在千兆以太网模式下,此功能不包含在 PCS 中,并且 carrier\_detect 信号不会提供给 FPGA 结构。

- 时钟容限补偿逻辑能处理时钟域的差异。

#### 千兆以太网(1000BASE-X) Idle 插入

这对于时钟补偿和自动协商来说是必需的。自动协商是由 FPGA 逻辑实现的。莱迪思千兆以太网 PCS IP 核提供自动协商,下面将详细讨论。

Idle 模式插入对于时钟补偿和自动协商来说是必需的。自动协商是由 FPGA 逻辑实现的。该模块在自动协商过程中,自动在接收数据流中插入 /I2/ 符号。在自动协商时,链路的另一端将不断发送 /C1/ 和 /C2/ 序列集。时钟补偿器不会删除这些序列集,因为它被配置为仅插入 / 删除 /I2/ 序列集。为了防止时钟补偿器的过载 / 欠载,必须周期性地插入/I2/ 序列集,为时钟补偿器提供插入 / 删除机会。

在执行自动协商时,该模块将每隔 2048 个时钟周期插入连续的 8 个 /I2/ 的序列集(每个占两个字节)。由于此模块在 8b10b 解码器后面,此操作将不会引入任何运行不一致(running disparity)的错误。这些 /I2/ 序列集不会传入 FPGA 接收接口,因为在自动协商过程中,GMII 接口由 RX 状态机驱动为 IDLE。一旦自动协商完成后,禁止 /I2/ 插入,以防止破坏任何接收到的数据。

请注意,该状态机只在自动协商时有效。自动协商状态机和 GbE 接收状态机在软逻辑中实现。该状态机由自动协商状态机的信号 xmit\_ch 决定。这个信号是在 TX 数据总线上提供。虽然这个信号是相对静态的 (尤其是在自动协商后),它包含在 TX 数据总线中。

#### 表 8-17. GbE IDLE 状态机控制和状态信号

| 模块信号         | 方向 | 说明                |

|--------------|----|-------------------|

| xmit_ch[3:0] | In | 来自 FPGA 逻辑自动协商状态机 |

#### 千兆以太网 Idle 插入和 correct\_disp\_ch[3:0] 信号的使用

correct\_disp\_ch[3:0] 信号用于 PCS 的发送端,以确保数据包间间隙在 negative disparity 状态下开始。请注意,在以太网帧最后,发送器的当前 disparity 状态可以是 positive 或者 negative,根据以太网帧的大小和数据内容决定。

然而,从 PCS 的 FPGA 软逻辑端,PCS 发送器目前的 disparity 状态是未知的。这就是 correct\_disp\_ch[3:0] 信号的作用。如果一旦进入一个数据包间间隙,发出 correct\_disp\_ch[3:0] 信号一个时钟周期,当目前是 positive disparity时,将强制 PCS 发送器在发送数据流中插入一个 IDLE1 序列集。但是,如果目前是 negative disparity,则不对发送数据流做任何改变。

从 PCS 的 FPGA 软逻辑端,数据包间间隙为不断发送的 IDLE2 序列集如下: tx\_k\_ch=1, txdata= 0xBC tx\_k\_ch=0, txdata=0x50。

请注意,在 PCS 通道中, IDLE2 意味着目前的 disparity 状态将被保留。 IDLE1 意味着目前的 disparity 状态应当翻转。那么,就有可能可以确保数据包间间隙以 negative disparity 状态开始。如果在数据包间间隙前的 disparity 状态为 negative,那么数据包间间隙将不断发送 IDLE2。如果在数据包间间隙段前的 disparity 状态为 positive,那么将发送一个 IDLE 后面跟连续的 IDLE2。

在 PCS 的 FPGA 软逻辑端,数据包间间隙总是将 IDLE2 输入 PCS。当第一次出现数据包间间隙时,将发出一个时钟周期的 correct\_disp\_ch[3:0] 信号,k\_cntrl=0,data=0x50。如果需要的话,PCS 将会把这个 IDLE2 转换为 IDLE1。在余下的数据包间间隙, IDLE2 应输入 PCS 并且 correct\_disparity\_chx 信号应保持无效。

例如,如果发送连续的512字节以太网帧和512字节/I/,可以观察到:

- 在第一个数据包间间隙,可以看到所有的 negative disparity /l2/ (K28.5(-) D16.2(+))

- 在下一个数据包间间隙,周期以 positive disparity /l1/(K28.5 (+), D5.6 (+/- 相同 ))开始,然后所有剩下的序列都是 negative disparity /l2/

- 在下一个数据包间间隙,可以看到所有的 negative disparity /I2/

- 在下一个数据包间间隙,周期以 positive disparity /l1/(K28.5 (+), D5.6 (+/- 相同 ))开始,然后所有剩下的序列都是 negative disparity /l2/

编码器模块支持许多可编程选项。它们是:

- 按每个字强制 negative 或 positive disparity

- 直接从 FIFO 桥输入数据 —— 外部的多路复用器

- 根据运行差异 (running disparity) (100BASE-X 和 FC) 改变编码字

- 软件寄存器控制的旁路模式

# XAUI 模式

使用莱迪思 XAUI IP 核, SERDES/PCS 块的 XAUI 模式支持全面兼容,从串行 I/O 到 IEEE 802.3-2002 XAUI 标准的 XGMII 接口。 XAUI 模式支持 10 千兆以太网。

#### 发送路径

- 串行器

- 发送状态机根据 IEEE 802.3ae-2002 规范,将 XGMII idle 转化为相应的 ||A||、||K||、||R|| 字符。

- 8b10b 编码

#### 接收路径

- 解串行器

- 基于 IEEE 802.3-2002 定义的对齐字符的字对齐。

- 8b10b 解码

- XAUI 链路状态机符合图 48-7—IEEE 802.3ae-2002 标准的 PCS 同步状态图, 仅有一点例外。图 48-7 要求接收 4 个连续正确的代码组, 以使 LSM 从 SYNC\_ACQUIRED\_{N} (N=2,3,4) 变为 SYNC\_ACQUIRED\_{N-1}。而现在实际的 LSM 实现要求 5 个连续正确的代码组来触发转换。

- PCS 中的时钟容限补偿逻辑在 XAUI 模式下是禁止的。MCA (Multi-Channel Alignment, 多通道对齐) 及 CTC 是在 XAUI IP 核中实现的。

- x4 多通道对齐应当在 FPGA 内核逻辑中实现。

# PCI Express 版本 1.1 (2.5Gpbs) 模式下的 LatticeECP3 PCS

SERDES/PCS 块的 PCI Express 模式支持 x1、 x2 和 x4 PCI Express 应用。

## 发送路径

- 串行器

- 8b10b 编码

- 接收器检测

- 电气空闲状态

## 接收路径

- 解串行器

- 基于 Sync 编码的字对齐

- 8b10b解码

- 链路同步状态机功能包括了在 IEEE 802.3ae-2002 10GBASE-X 规范下的 PCS 同步状态机(图 48-7)中定义的操作。

- x2 或 x4 PCI Express 操作,可用一个 PCS quad 设为 PCI Express 模式。

- 时钟容限补偿逻辑能处理时钟域的差异。

- x2 或 x4 多通道对齐应当在 FPGA 内核逻辑中实现。

表 8-18 说明了 PCI Express 模式下的特定端口。

## 表 8-18. PCI Express 模式特定端口

| 信号                    | 方向  | 类别 | 说明                                                                                                  |

|-----------------------|-----|----|-----------------------------------------------------------------------------------------------------|

| pcie_done_ch[3:0]_s   | Out | 通道 | 1 = 远端接收器检测完毕<br>0 = 远端接收器正在检测                                                                      |

| pcie_con_ch[3:0]_s    | Out | 通道 | 远端接收器检测的结果。<br>1 = 检测到远端接收器<br>0 = 未检测到远端接收器                                                        |

| pcie_det_en_ch[3:0]_c | In  | 通道 | FPGA 逻辑 (用户逻辑) 通知 SERDES 块, 它要申请一次 PCI Express 接收器<br>检测操作。<br>1 = 使能 PCI Express 接收器检测<br>0 = 正常工作 |

| pcie_ct_ch[3:0]_c     | In  | 通道 | 1 = 申请发送器进行远端接收器检测<br>0 = 正常工作                                                                      |

| rxstatus[2:0]         | Out | 通道 | 每个通道 PCI Express 接收状态端口。 RxStatus# 是接收数据路径的一种编码状态。如果在 16 位数据总线模式下是 2 位宽。                            |

状态信号 rxstatus 是接收数据路径的编码状态。编码如下所示。

#### 表 8-19. rxstatus 编码

| rxs | tatus[2 | 2:0] | 说明                                | 优先级 |

|-----|---------|------|-----------------------------------|-----|

| 0   | 0       | 0    | 接收到的数据正常                          | 8   |

| 0   | 0       | 1    | CTC 插入 1 个字节                      | 7   |

| 0   | 1       | 0    | CTC 删除 1 个字节                      | 6   |

| 0   | 1       | 1    | 检测到接收器 (pcie_done, pcie_con)      | 1   |

| 1   | 0       | 0    | 8b10b 解码错误 (编码违例 ——rx_cv_err)     | 2   |

| 1   | 0       | 1    | CTC FIFO 上溢 (ctc_orun)            | 3   |

| 1   | 1       | 0    | CTC FIFO 下溢 (ctc_urun)            | 4   |

| 1   | 1       | 1    | 接收不一致 (disparity)错误 (rx_disp_err) | 5   |

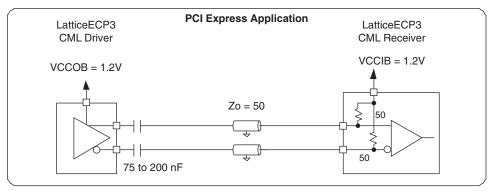

## PCI Express 端接

在电气层,PCI Express 采用了两根单向的低压差分信号对,每个通道速率为 2.5Gbps。发送和接收是独立的差分对,每个通道总共有 4 根数据线。通过带有可编程均衡器的输入接收器和带有可编程预加重的输出发送器优化了链路。PCI Express 规范要求差分线路必须在接收端使用共模端接。每条链路要求在远端 (接收器)使用一个端接电阻。使用的标称电阻值为 100 欧姆。这是通过使用如图 8-28 所示的 CML 输入的嵌入式端接特性实现的。该规范要求在链路的发送端使用交流耦合电容(CTX)。这消除了发送和接收器件之间潜在的共模偏置的不匹配。莱迪思 CML输出必须外加该电容。

## PCI Express L2 状态

对于 PCI Express L2 状态,rx\_pwrup\_c 信号不应该变为无效,从而使 rx 通道掉电。这将强制 rx 端接为高阻状态,并不允许远端检测到接收器。而应该使用 rx\_pcs\_rst\_c 信号将通道保持在复位状态来节省功耗。

## 图 8-28. PCI Express 接口图

## 表 8-20. 差分 PCI Express 规范

| 信号          | 参数         | 最小值 | 正常值 | 最大值 | 单位  | 说明                                                                                                                | 位置 |

|-------------|------------|-----|-----|-----|-----|-------------------------------------------------------------------------------------------------------------------|----|

| ZTX-DIFF-DC | 直流差分 TX 阻抗 | 80  | 100 | 120 | Ohm | TX 直流差分模式低阻抗。 ZTX-DIFF-DC 是发送器的小信号阻抗,在直流工作点上测得,等于当 TX 在驱动静态逻辑信号 1 或者 0 时,在 D+ 和 D- 之间连接一个 100 欧姆电阻。               | 内部 |

| ZRX-DIFF-DC | 直流差分输入阻抗   | 80  | 100 | 120 | Ohm | 所有 LTSSM 状态下的 RX 直流差分模式阻抗。当发送从 Fundamental Reset变为 Detect 时,(LTSSM 的初始状态),在满足一个端口上所有未配置的线路上的接收器端接值之前,需要 5 ms转换时间。 | 内部 |

| СТХ         | 交流耦合电容     | 75  |     | 200 | nF  | 所有的发送器都是交流耦合的。传输介<br>质或者发送元件本身都需要交流耦合。                                                                            | 外部 |

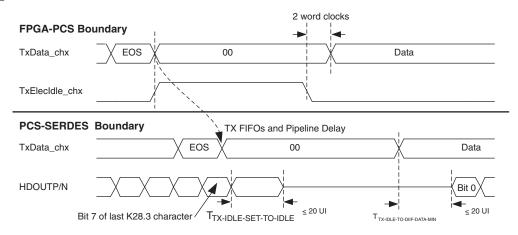

#### PCI Express Electrical Idle 发送

Electrical Idle 是一个稳定状态,发送器 P 和 N 电压都保持在相同的恒定值(即,Electrical Idle 差分峰值输出电压,VTX-IDLE-DIFFp,在 0 和 20mV 之间)。 Electrical Idle 主要用于节省功耗和非激活状态。

根据 PCI Express 基本规范,在发送器进入 Electrical Idle 之前,通常必须发送 Electrical Idle 序列 (EIOS),一个 K28.5(COM)之后有三个 K28.3(IDL)。在发送完 Electrical Idle 序列的最后一个符号后,发送器必须在一个 TTX-IDLE-SET-TO-IDLE 规定的小于 20UI 时间内进入有效的 Electrical Idle 状态。

要做到这一点,FPGA 内核逻辑至 PCS 的 Electrical Idle Enable(tx\_idle\_chx\_c)随每个发送数据一起发送。该信号以类似于流水线的方式发送到 PCS-SERDES 边界。对于所有有效数据来说,该信号为 LOW。为初始化 Electrical Idle,在它发出最后一个 K28.5(IDL)字符后的这个时钟,FPGA 逻辑将该信号变为 HIGH。因为当信号以流水线方式发送到 PCS-SERDES 边界,发送数据和该信号之间的关系和在 FPGA-PCS 边界上的完全相同。

在 PCS-SERDES 边界,Electrical Idle Enable 信号处于上升边沿的 14UI 后,发送最后一个字符 K28.3(IDL)的最后一位(bit7)。在 16UI(<20UI)后,发送差分缓冲器实现了 Electrical Idle 状态。

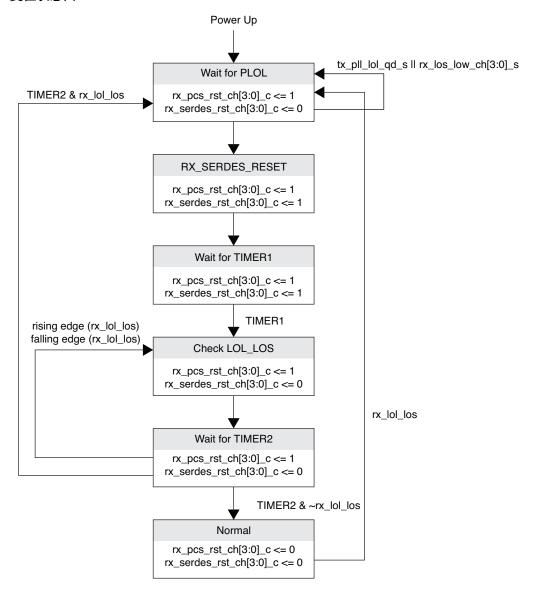

#### 图 8-29. 发送 Electrical Idle