# 運用 PLD 降低消費性應用的成本與功耗

萊迪思半導體白皮書 2010年11月

萊迪思半導體

5555 Northeast Moore Ct. Hillsboro, Oregon97124USA Telephone: (503) 268-8000

www.latticesemi.com

### 簡介

爲了在緊縮的銷售時間內支援持續演變的市場標準,業界逐漸廣泛採用可編程邏輯元件(PLD)來開發各式各樣的消費性應用產品。發展特殊應用 IC(ASIC)與特定應用標準產品(ASSP)往往須付出高昂的非重複性工程費用,而 PLD 則屬市場上流通的標準型零件,其可運用彈性的軟體工具來針對各種不同應用自行客製化。不同於 ASIC 與 ASSP 的是,PLD 不需冗長的前置作業:它們的功能可針對產品需求的改變而隨時變更。在諸如掌上型裝置在內的許多市場中,PLD 因爲能提供新的產品架構而廣獲採納,因客戶將能藉此降低功耗、採用新的封裝選項、以及獲得更低的單位成本。

### 消費性應用- 趨勢與挑戰

#### 降低成本

根據市調機構 iSuppli 預測,消費性電子產品在 2010 年的銷售營收達到 2590 億美元的規模,同時結束之前持續了好幾年的市場衰退期。在這波走強的成長期中,未來數年的營收將持續攀升,2011 年將成長 6.7%,2012 年則預計成長7%。營收的成長力量來自於各種量產產品的銷售,包括藍光 DVD 播放機、液晶電視、視訊轉換器、數位相機、智慧型手機、以及 GPS 導航機等。有鑑於此,業者著手研發新設備以滿足新興市場的各種需求,透過大幅降低的成本爲消費者帶來更多的價值與功能。因此,設計人員亦面臨持續不斷的壓力,他們被要求必須推出更低成本的產品,同時達到更高的系統整合度。

### 持續降低的耗電預算

對於各種消費性產品的研發人員而言,不斷降低靜態功耗是一項長久持續的挑戰。對於各種使用電池供電的產品而言,如智慧型手機、GPS 導航機、行動運算、以及數位相機等,更長的電池續航力一直是最重要的差異化特色之一。即使是使用插座供電的電子產品,由於設計人員必須遵循最新的能源之星(EnergyStar)以

及歐盟的 EC Code of Conduct 電力消耗規範,使得低功耗也逐漸成為一項重要因素。

#### 持續縮短的產品生命週期

消費性電子市場持續快速演進,最佳證明就是不斷推陳出新的新標準,以提升消費性電子產品的品質與平價化。目前市場的兩大趨勢-有線與無線裝置的寬頻存取,以及媒體與資料的匯流-正驅動著業界發展這些新標準。

製造商們面臨著沉重的競爭壓力,因此競相搶先推出與眾不同的差異化產品。然而,成功的產品很快就會吸引對手模仿,導致價格迅速滑落。爲搶得市場先機,消費性產品製造商被迫持續改良其產品或支援各項新技術。由於這些因素,使得消費性產品的生命週期大幅縮短。

### PLD 在消費產品的應用

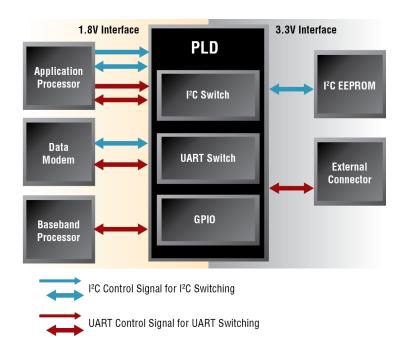

改良式的架構協助降低功耗、新封裝造就更小的產品尺寸、更低的單位成本加上更高的產品差異化,這些因素都促使著 PLD 更廣泛地用於消費性產品中。在許多消費性產品中,PLD 能提供先進的匯流排介面與橋接功能,因而延伸了現有應用處理器或 CPU 的應用範疇。這些匯流排介面與橋接功能通常不具極高效能的要求。圖 1 顯示這類應用的範例。

圖 1: 在手機中採用 PLD

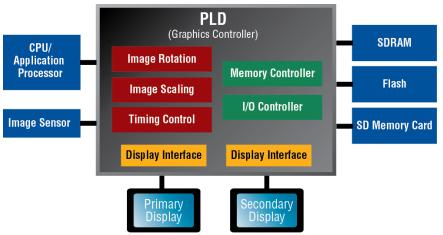

PLD 亦經常用來建置人機介面控制器、螢幕控制器、外部記憶體介面控制器、以及脈衝調變控制器。表 2 列舉出消費產品市場中常見的 PLD 應用。有時業者會結合兩種或更多的功能來支援特殊的需求; 圖 2 顯示其中一種應用。

| PLD 功能     | 應用實例                                                                              |  |

|------------|-----------------------------------------------------------------------------------|--|

| 人機介面控制器    | 鍵盤矩陣解碼器、數位觸控螢幕控制、岔斷管理器                                                            |  |

| 螢幕控制器      | 影像旋轉、影像縮放、液晶螢幕控制、顯示介面多工/<br>解多工                                                   |  |

| 外部記憶體介面控制器 | Secure Digital (SD)、Compact Flash (CF)、Memory Stick 等記憶卡以及 DDR/DDR2/LPDDR 記憶體的控制器 |  |

| 脈衝調變控制器    | 液晶螢幕背光控制、步進馬達控制                                                                   |  |

| 匯流排介面連結與橋接 | I <sup>2</sup> C、SPI、UART、I <sup>2</sup> S、USB、以及 SDIO 等介面                        |  |

表 1: 消費應用中常見的 PLD 功能

圖 2: PLD 在數位相機的應用實例

如同高階 FPGA,低密度 PLD 如今擁有許多先進的 I/O 介面,包括支援各種 I/O 標準、多重 I/O 插槽、以及多種電壓。這些功能特性讓 PLD 能用在 ASIC/ASSP、記憶體、處理器、以及其它元件之間建置互連邏輯,這些元件通常 採用不同的電壓與 I/O 標準。

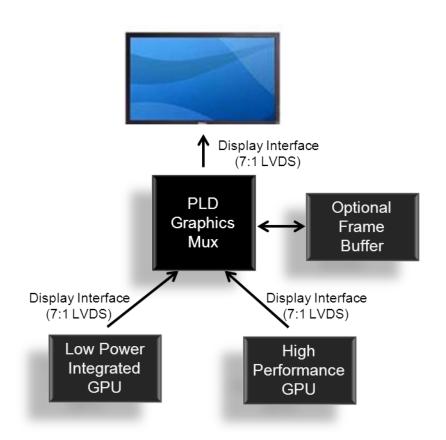

如圖 3 所示,繪圖多工器適合用來說明低成本、低密度的 PLD 如何執行先進的互連邏輯。筆記型電腦與可攜式電源管理的最新趨勢,是採用英特爾的 Switchable Graphics 計畫。Graphics Multiplexer 根據應用需求,選擇採用一款繪圖控制器。該公司選擇低功耗整合式 GPU 來支援包括文書處理、收發電子郵件、以及瀏覽網站等日常應用。高效能的獨立 GPU 用來處理高效能應用,例如遊戲、編輯影片、以及播放 HD 影片等。對於低擺幅差動 I/O 標準、以及內建齒輪箱與鎖相迴路,讓 PLD 能夠連結繪圖處理器,建置各種智慧型多工演算法,以盡量減少或消除切換時的視覺瑕疵,並直接驅動液晶螢幕。

圖 3: PLD 建構的繪圖多工器

萊迪思的 MachXO2 PLD 系列元件適合支援上述消費應用所採用的功能。結合最佳化的查表(LUT)架構及 65 奈米嵌入式快閃製程技術,MachXO2 元件為各種消費性產品設計提供了高度彈性的"多功能合一"(Do-it- All)解決方案。

#### 運用 MachXO2 元件降低成本

#### 受銲盤限制的設計

根據歷史經驗,就對於價格敏感的量產型應用而言,PLD並不是成本最低的解決方案。但隨著 ASIC 與 PLD 開始受到銲盤限制,這種情況也出現了變化。在受 銲盤限制的設計中,晶粒尺吋僅由所需的 I/O 銲墊數量來決定,而不是由核心中邏 輯元件 的數量決定。價格最終取決於晶粒尺吋 - 當元件開始受銲盤限制時,客製 化與可編程產品設計之間的價差就會縮小。MachXO2 元件一開始就設計成受銲盤 限制。I/O 銲墊依照元件密度的高低,配置成兩個或三個交錯式 I/O 環路,在一定的 I/O 數量下盡量縮小晶粒的尺吋。

#### 低成本封裝

MachXO2 元件提供各種無鹵素的低成本封裝。現有的封裝選項包括低成本BGA與TQFP,還有各式先進晶圓級晶片封裝及微型化晶片級封裝。BGA 封裝包括最少訊號繞線層的版本,其能降低整體封裝成本。這些封裝讓所有 I/O 與電源供應連結能置於兩到三層的 PCB 線路中,如此一來便不需使用埋入式或盲孔與雷射導孔等更高成本的製造技巧。MachXO2 封裝上的 I/O 配置,讓業者能在同一種封裝進行密度移植。這使得業者可透過設計變更來利用相同的機板,藉此運用更大或更小的 MachXO2 元件。

#### 功能整合

設計人員經常面臨的兩難處境,是一方面要支援高階功能,同時還得降低總成本。獨立式元件會增加成本、機板空間、以及系統的整體耗電預算。獨立式元件還會衍生機板可靠度降低的問題。這些因素,促使著消費性應用開始追求更高的功能整合度。

MachXO2 元件支援高階的系統整合,其包括單晶片解決方案,不需要外部組態記憶體、外部使用者快閃記憶體、或是 EEPROM 與震盪器等元件,因此可進一步降低機板空間、元件數量及整體系統成本。

圖 4 所示為一款 MachXO2 元件,其於內部整合了獨立邏輯元件,例如 I/O 擴充器、電壓值與匯流排橋接轉譯器、穩壓器、時脈來源、以及組態元件,所有元件均整合於單一晶片中。

#### 圖 4: MachXO2 功能整合

#### 整合外部非揮發記憶體

MachXO2 元件最多內含 256Kbits 的嵌入式快閃記憶體。這個晶片內使用者快閃記憶體(UFM)讓 MachXO2 元件能整合外部非揮發記憶體,並能用在各種應用,包括儲存一部分的組態映像、儲存 PROM 資料、或是作爲通用型使用者快閃記憶體。

#### 減少振盪器數量

MachXO2 元件內含一內部振盪器,額定精準度達+/- 5%,其可作爲設計的時脈來源,因此不需外部振盪器。

## 硬型化 SPI、I2C 以及計時器/計數器

SPI 與  $I^2C$  控制器與計時器/計數器是消費性產品最常見的功能。研發業者通常會把 SPI 或  $I^2C$  匯流排擴充功能建置在 PLD 內。計時器/計數器亦經常用來產生狀態訊號。所有 MachXO2 元件均將這些常用功能硬型化成內部搭載的硬體元件,透過硬型化的  $I^2C$ 、SPI、以及計時器/計數器功能,研發業者可在其設計中節省最高達 600 個 LUT 並建置額外的邏輯功能。表 2 顯示針對各種常見控制功能採用硬型化元件所省下的邏輯元件。

| 功能                          | 使用 PLD 時需要的<br>LUT 數量 | 使用 MachXO2 元件時<br>需要的 LUT 數量 |

|-----------------------------|-----------------------|------------------------------|

| SPI Master 控制端              | 115                   | 0                            |

| I <sup>2</sup> C Master 控制端 | 234                   | 0                            |

| 計時器/計數器                     | 50-80                 | 0                            |

表 2: 運用硬型化 I<sup>2</sup>C、SPI、與計時器/計數器功能時所省下的邏輯元件

### 運用 MachXO2 元件降低耗電預算

#### 靜態與動態功耗

PLD 的整體功耗是兩個主要元素的總和: 亦即靜態功耗與動態功耗。靜態功耗主要來自元件中電晶體的漏電流。漏電流是"漏出"的微小電流,包括源極(source)至汲極(drain),或是閘極氧化層,即使當電晶體的邏輯運算功能處在關閉狀態時,仍可能會有漏電的情況。動態功耗是在核心或元件 I/O 進行切換時所消耗的電力,因此與頻率及使用者皆有關連。

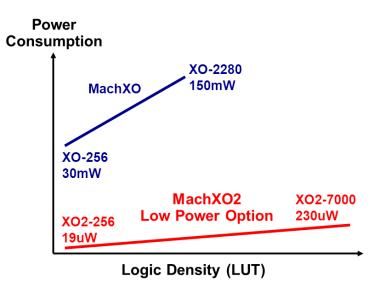

圖 5: 比較 MachXO2 與 MachXO PLD 的靜態功耗

由於動態功耗取決於切換時的節點數量,因此和設計的手法更密切相關。研發人員可採用各種技巧來降低動態功耗。例如,選擇在時脈樹的來源啟動時脈而不是在每個端點,即可減少系統中的時脈切換。I/O 亦對動態功耗有極大的影響。除採用 LVTTL/LVCMOS 等低電壓標準與更低的 I/O 電壓有助於降低功耗外,運用更低擺幅的差動訊號亦有助於降低動態功耗。MachXO2 元件提供許多架構功能來降低動態功耗,例如功耗控制器、I/O 插槽控制器、支援動態時脈、power guard 閘控、以及可編程低振幅差動訊號等。

### 非揮發性達到更低的功耗

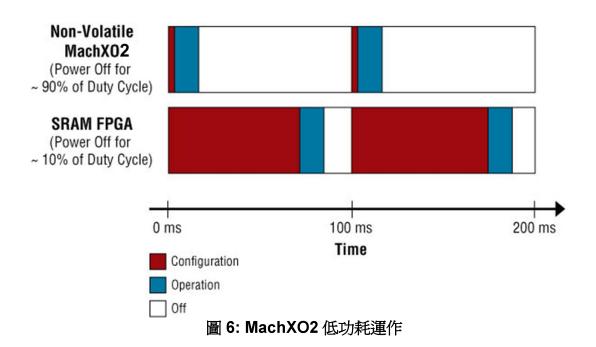

除了靜態與動態功耗外,還有一項功耗元件與湧浪電流以及組態有關。亦即在 PLD/FPGA進入使用者模式之前,當啟動電源與設定時的功耗。其消耗的電力和 進入使用者模式所耗費的時間成正比。機板設計人員在判斷功耗需求時,必須考量 這個額外的功耗。許多消費性產品的設計造成 FPGA或 PLD 會經常啟動/關閉。這 種系統行爲由於經常進行啟動/關閉導致耗電增加。基於本身的特性(像是內含晶片 內部組態記憶體的 PLD), MachXO2 元件可在數微秒內自行完成設定,因此可將 湧浪與設定時的功耗減至最低。圖 6 為 MachXO2 PLD 與 SRAM 型 FPGA 兩種元 件在進入使用者模式所需的時間比較圖。

### 運用免費設計工具加速創新

研發業者可運用 Lattice Diamond v1.1 軟體,立即著手採用 MachXO2 元件進行設計,這款軟體可至 Lattice 網站免費下載。此外,他們也可運用免費的ispLEVER® v8.1 SP1 Starter 軟體,搭配從 Lattice 網站下載的預先安裝控制套件。

針對消費應用進行最佳化的全方位參考設計套件,可至萊迪思網站免費下載。 其中收錄了(請列出消費性參考設計 list a few consumer ref designs)。參考設計方 案的原始碼,包括 HDL 與韌體在內,可根據應用的需求自行修改。欲得知有關參考設計方案的詳細資訊,請參閱 <a href="http://www.latticesemi.com/ip">http://www.latticesemi.com/ip</a>

### 結論

對於在消費產品中建置功能而言,PLD是一種理想的選擇,因爲其能克服ASIC與ASSP的各種限制,而提供一個低成本、低功耗、彈性化的解決方案。MachXO2 PLD系列元件專爲低成本、低功耗的消費應用量身打造,爲研發業者提供更低成本、更低功耗、更高的系統整合度、以及小巧的尺寸。此外,MachXO2元件內含許多硬型化的常見功能,包括使用者快閃記憶體(UFM)、I<sup>2</sup>C、SPI、以及計時器/計數器等,均是消費性應用常見的功能。