This document provides a brief introduction and instructions to install and demonstrate the HDR-60 Video Camera Development Kit on Windows 7/Vista/XP/2000. Additional documentation can be downloaded at www.latticesemi.com/hdr60. The HDR-60 Base Board User's Guide and NanoVesta Head Board User's Guide are also available for download from the Lattice web site.

## Check Kit Contents

The HDR-60 Video Camera Development Kit contains the following items:

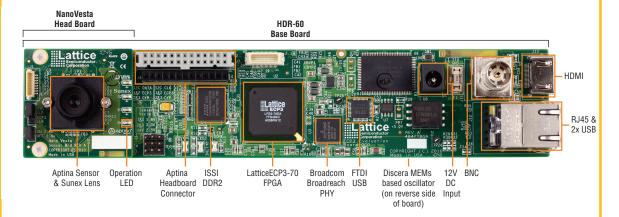

- HDR-60 Base Board with LatticeECP3™ FPGA pre-loaded with Image Signal Processing (ISP) Demo

- NanoVesta Head Board with Aptina sensor and Sunex lens

- · Two USB cables

- HDMI cable with HDMI-to-DVI adapter

- 12V AC adapter power supply

- QuickSTART Guide

HDR-60 Video Camera Development Kit

Note: Static electricity can shorten the lifespan of electronic components. Please handle the kit components carefully.

The Aptina head board connector is provided only for use with Aptina DevWare software (not included). If you plan to use Aptina DevWare software, please visit www.aptina.com or contact your local Aptina representative.

The lower USB connector is used to run the Aptina DevWare software. The upper USB connector utilizes the FTDI USB device for programming different designs into the LatticeECP3-70 device.

Programming the LatticeECP3 device requires Lattice ispVM™ System software version 17.9 or later. ispVM System software can be downloaded from the Lattice web site at www.latticesemi.com/ispvm.

## Run the Demonstration

To power the HDR-60 Base Board:

- Connect the NanoVesta Head Board to the HDR-60 Base Board if it is not already connected. The two connectors permit mating only in one orientation, so no misconnection is possible.

- Connect the external power supply to the power connector on the HDR-60 Base Board.

The LatticeECP3-70 device's Flash is preprogrammed to load a default demo that will appear on the monitor. Running the preloaded demonstration does not require connecting the provided USB cables to a PC.

After the AC adapter is plugged in and the HDMI cable is connected, the HDR-60 Base Board loads the LatticeECP3 with the preconfigured demo file. LED D4 will blink, indicating that the device has loaded correctly.

The preloaded demo file in the LatticeECP3 incorporates an Image Signal Processing (ISP) pipeline with HDR and displays a split screen on the monitor. On your right side as you look at the monitor is the effect of the ISP pipeline and on your left side is the unprocessed image. You may need to rotate the lens holder for better focus. Here are some actions you can perform to see the ISP pipeline's capabilities:

- Auto Exposure Cover the lens with your finger and then uncover it quickly. The picture will instantly reappear with no settling time, bloom or washout. This demonstrates fast auto exposure.

- HDR Point the lens to a light source. Note that while the light source is visible, the rest of the image

is not blacked out. See the difference between the processed and unprocessed images on the split

screen.

- Auto White Balance Cover the lens for 5 seconds or more. Remove your finger and see that the

image is tinted. Wait a few seconds while the ISP reads the histograms generated by its internal

statistics block and automatically adjusts the image to natural colors. This demonstrates high-quality

auto white balance.

## Done!

Congratulations! You have successfully demonstrated the HDR-60 Video Camera Development Kit. Please refer to the *HDR-60 Base Board User's Guide* and *NanoVesta Head Board User's Guide* for board schematics, board descriptions and signal usage information.

See the HDR-60 Video Camera Development Kit web page at www.latticesemi.com/hdr60 for schematic design files in OrCAD Capture format, layout design files in Allegro format, photoplot files for all layers in Gerber format and BOM files in Excel format.

## **Technical Support**

1-800-LATTICE(528-8423)

+1-503-268-8001

techsupport@latticesemi.com

Copyright © 2012 Lattice Semiconductor Corporation. Lattice Semiconductor, L (stylized) Lattice Semiconductor Corp., Lattice (design), ispVM and LatticeECP3 are either registered trademarks or trademarks of Lattice Semiconductor Corporation in the United States and/or other countries. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.