# ispMACH 4000ZE

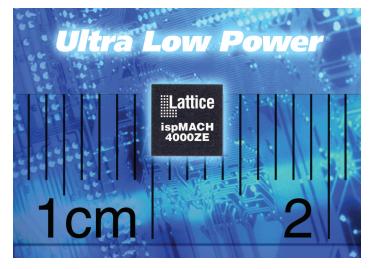

# 低コスト、小型パッケージ、超低消費電力

第二世代のispMACH 4000ZEは、低消費電力で多量生産の携帯アプリケーションに理想的です。ispMACH 4000ZEは  $10\,\mu$  A程度のスタンバイ電流を実現しました。コスト的に最適化しつつも機能の豊富なispMACH 4000ZEデバイスは、省スペースの超小型パッケージucBGAとcsBGAで提供されます。極めて低いシステム電力の実現を可能にするパワーガードなどの新しい機能を備えるとともに、ユーザ用オンチップ発振器とタイマを含むシステム機能を集積しています。

ispMACH 4000ZEデバイスは実証済みの $E^2$ CMOS®プロセステクノロジで製造され、1.8Vのコア電圧を用い、3.3Vと 2.5V、および1.8Vの広範囲なI/0規格に対応します。さらにLVCMOS3.3やLVTTL、またはPCIインターフェイスを使用することで、ispMACH 4000ZEデバイスは5V耐性のI/0にも対応します。

ispMACH 4000ZEファミリには民生用と産業用の温度グレードに対応するバージョンを用意しており、同一パッケージ間では従来のゼロパワーCPLD ispMACH 4000Zファミリとピン互換です。

新しいispMACH 4000ZEファミリは、ラティスの使いやすくて強力なispLEVER® Classicデザインソフトウェア、並びに広く採用されているサードパーティ・ツールに対応しています。

#### パワーガード

パワーガードは、未使用の入力ピンを選択的にディセーブルすることによって、システムのスタンバイ時電流を減らします。本機能はI/Oピンと入力バッファ間のマルチプレクサと、デバイス内部の関連する回路をイネーブルすることで実現します。ブロック内の全I/Oピンがイネーブル信号(Block Input Enable; BIE)信号を共有します。「ブロック」数はデバイス規模に依存し、デバイスあたり2~16です。ブロック内のI/OピンはいずれもBIE信号を無視するように設定できます。イネーブルするかディセーブルするかの機能はピン単位に設定できます。

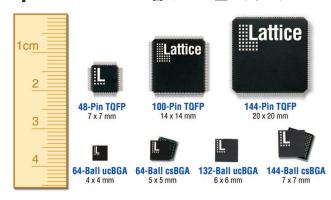

## ispMACH 4000ZE 省スペース型パッケージ

パッケージは実際のサイズで示されています。寸法はパッケージ本体のサイズです。

## 主要な機能と特長

- 超低消費電力

- 10 μ A-typ. の低いスタンバイ電流

- 低ダイナミック電力用の1.8Vコア電圧

- V<sub>CC</sub> は1.6Vまで動作

- ピン単位のプルアップ、プルダウン、またはバスキーパ制御

- 複数のイネーブル信号があるパワーガード

- 極めて小さい実装面積

- 4x4mm (64ボールucBGA) の省スペース小型パッケージ

- 容易なシステム集積

- LVCMOS I/Oは3.3V、2.5V、1.8Vまたは1.5V動作

- LVCMOS3.3、LVTTL、およびPCIインターフェイスによる5V耐性I/0

- 活線挿抜に対応

- オープンドレイン出力のオプション

- プログラマブルな出力スルーレート

- 3.3V PCI互換

- 高速セットアップパスのあるI/0ピン

- 入力ヒステリシス

- IEEE1149.1バウンダリスキャン・テスト対応

- IEEE1532 ISC準拠

- ユーザ用のオンチップ発振器とタイマ

- 高性能

- 4.4nsのピン間遅延

- 260MHzのシステム性能

- 多彩なラインアップ

- マクロセル数は32~256

- 複数の温度グレードをサポート

- 民生用グレード: ジャンクション温度0~90℃

- 産業用グレード: ジャンクション温度 -40~105℃

- 環境に優しい素材

- RoHS準拠の無鉛パッケージ

- ハロゲンフリーの材質

### ispMACH 4000ZEデバイス選択ガイド

| パラメータ                                | 4032ZE          | 4064ZE  | 4128ZE  | 4256ZE   |

|--------------------------------------|-----------------|---------|---------|----------|

| マクロセルセル数                             | 32              | 64      | 128     | 256      |

| t <sub>PD</sub> (ns)                 | 4.4             | 4.7     | 5.8     | 5.8      |

| t <sub>CO</sub> (ns)                 | 3.0             | 3.2     | 3.8     | 3.8      |

| t <sub>S</sub> (ns)                  | 2.2             | 2.5     | 2.9     | 2.9      |

| f <sub>MAX</sub> (MHz)               | 260             | 241     | 200     | 200      |

| V <sub>CC</sub> (Volts)              | 1.8             | 1.8     | 1.8     | 1.8      |

| スタンバイ電流 (Typ.)                       | 10              | 11      | 12      | 13       |

| パッケージ <sup>1</sup>                   | I/O+ <b>入</b> 力 |         |         |          |

| 48-ピン TQFP (7 x 7 mm)                | 32 + 4          | 32 + 4  |         |          |

| 64-ボール csBGA (5 x 5 mm, 0.5 mm ピッチ)  | 32 + 4          | 48 + 4  |         |          |

| 64-ボール ucBGA (4 x 4 mm, 0.4 mm ピッチ)  |                 | 48 + 4  |         |          |

| 100-ピン TQFP (14 x 14 mm)             |                 | 64 + 10 | 64 + 10 | 64 + 10  |

| 132-ボール ucBGA (6 x 6 mm, 0.4 mm ピッチ) |                 |         | 96 + 4  |          |

|                                      |                 |         |         |          |

| 144-ボール csBGA (7 x 7 mm, 0.5 mm ピッチ) |                 | 64 + 10 | 96 + 4  | 108 + 14 |

1. 無鉛品のみ

#### ピン単位の制御

ispMACH 4000ZEはピン単位で以下のオプションに対応し ます。

- ・プルアップ

- ・プルダウン

- ・バスキーパ

- プル処理なし

これらのオプションは節電状態時に、バスメンテナンスにおいて、より大きな柔軟性をもたらします。

# 入力ヒステリシス

ispMACH 4000ZEデバイスでは、各入力ピンに常時オンのヒステリシスがあります。この新機能は3.3Vと2.5V入力ピンに改善された耐ノイズ特性を実現します。

#### オンチップ発振器とタイマ

内蔵発振器は、ウォッチドッグタイマやデジタル・グリッチ除去回路、制御用ステートマシンなど種々の管理用途のために用意されています。節電の目的のために、発振器はデフォルトではオフです。

## ispMACH 4000ZE ピコ開発キット

ispMACH 4000ZEピコ開発キットは、電池駆動の携帯アプリケーションという想定でispMACH 4000ZE CPLDを評価する一助となる機能を搭載しています。ラティスからの無償の参照設計を使用すれば、1

申間程度でユーザ独自のデザインを構築できます。詳細はwww. latticesemi.com/4000ze-pico-kit をご確認下さい。

# ispMACH 4000ZEアプリケーション

- テレマティックス

- ■スマートフォン

- ■ポケットベル

- 携帯クレジットカード/ デビットカード・リーダ

- GPS

- 薄型ディスプレイ

- 電卓

- 業務用無線機

- 工業用計測機器

- デジタルカメラ

- デジタルビデオレコーダ

- 家庭用オーディオ機器

- ■携帯用医療機器

- 車載アプリケーション

- ■携帯バーコードスキャナ

- どんなCPLD用途でも!!

#### 参照設計ポートフォリオ

ラティスはCPLDアプリケーションをターゲットにした参照設計(RD)の拡張ポートフォリオを用意しています。これらのデザインはispMACH 4000ZEアーキテクチャに最適化されており、I2CやSPIなどの広く採用されている接続機能が含まれています。ラティスのウェブサイトから参照設計、ソースコード、およびドキュメントを無料でダウンロードすることができます。詳しくはwww.latticesemi.com/ipをご確認ください。

# ispLEVER Classic設計ツール

ラティスのispLEVER ClassicソフトウェアはispMACH 4000ZEファミリ用の包括的な設計環境です。ツールはデザイン入力、論理合成、フィッティング、シミュレーション、プロジェクト管理、デバイスプログラミング、およびその他の必要なものをすべて含んでいます。論理合成とシミュレーションツールも含まれています。www.latticesemi.comからispLEVER Classicをダウンロードしてください。

#### アプリケーションサポート techsupport@latticesemi.com

techsupport@latticesemi.com www.latticesemi.co.jp