## 実用的な低消費電力CPLDデザイン

ラティスセミコンダクター・ホワイトペーパー

2009年8月

ラティスセミコンダクター

5555 Northeast Moore Ct. Hillsboro, Oregon 97124 USA Telephone: (503) 268-8000 www.latticesemi.com

#### はじめに

今日の携帯用製品開発にかかわる技術者は誰でも、消費電力を最少にすることが設計における絶対要件であることを知っています。しかし、システムのバッテリ寿命を最大に延ばすことができる微妙ながらも重要なことは、一般にベテラン技術者のみが理解しています。このホワイトペーパーは、これら成熟した専門家が組み込み設計のI/Oサブシステムから最後の余分な微少電力を搾り取るために、どのように超低消費電力CPLDを用いるかに焦点を合わせます。

まず、組み込み設計において消費電力、PCBスペース、およびBOMコストを減らすために、CPLDが通常どのように用いられるかを再検証することから始めます。次に、デバイス自体を慎重に選択するだけでなく、バスメンテナンス機構も適切に選ぶことによって、スタンバイモードでCPLDの消費電力を最少にする方法を確かめます。動作中の電力削減の検討対象としては、選択的ロジックゲーティングや「スマート」I/O設計、或いは高精度な供給電源電圧の管理などの技法を含むでしょう。

#### CPLD ~ 組み込み技術者の先進性

CPLDは、進化の著しいアプリケーションにおいて特にグルーロジックによく採用されています。その低コスト、小型サイズ、そして低消費電力の特性は、どのような携帯用製品の設計にとっても素晴らしい選択肢となります。これら携帯機器アプリケーションでは、なるべく長い時間プロセッサを低消費電力のスリープモードにすることができるように、CPLDは一般的にロジック機能の統合やホストプロセッサのI/O拡張、および重要な入力の監視などの目的に用いられます。

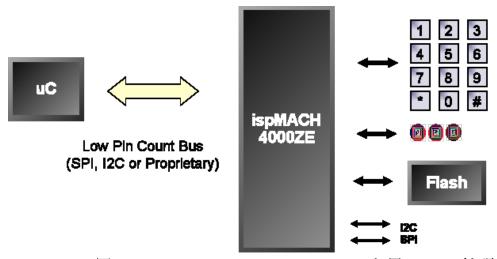

I/O拡張デバイスとして用いる場合、ispMACH 4000ZE (図1)のようなCPLDは簡易な組み込みプロセッサに対して、表示やボタン、あるいはLED、シリアルまたはパラレルI/Oやストレージ・インターフェイスなどに対応するために必要な信号線とアドレス機能を付加します。とくにスマートフォン、GPSシステム、工業用リモートセンサ、およびデジタル・ビデオカメラのなどの設計おいては、より専門化したチップセットと汎用プロセッサ間のグルーとしてCPLDが頻繁に用いられます。

図1 ラティスispMACH 4000ZE CPLDを用いるI/O拡張

#### スタンバイ電力の基礎

CPLDの消費電力削減方法を習得することにおける第一歩は、デバイスがその通常動作時とスタンバイ(またはスタティック)時の両ステートでどのように振る舞うかを理解することです。多くのCPLDはスタンバイ状態でほとんどの時間を費やすため、まず最初にこのしばしば誤解されているモードについてより詳しく見ていきます。

デバイスに電源が供給されていて内部ロジックにクロックが与えられていない時、CPLDはスタンバイ状態にあると呼ばれます。この状態でもリーク電流とバイアス電流が存在するため、CPLDは(実際に動作している時よりは大幅に少ないですが)ある程度の電力を消費しています。リーク電流は温度、動作電圧、および製造プロセスの関数として変動します。

他方バイアス電流は、デバイスのロジック機能が用いられるかどうかにかかわらず、内部オシレータやI/Oラインのプルアップ/ダウン、またその他の必ず使用される部分で消費されます。バイアス電流は、リーク電流と異なり温度や電圧範囲にわたって比較的安定していますが、適切なデバイスのコンフィグレーションでこれらを制御することができます。

# 動作条件が影響するリーク電流〜仕様書を賢く解釈して管理

CPLDのリーク電流は主としてそれがどう作られているかによって決定されるので、第一歩はベンダが発行する候補部品のデータシート上で提供される仕様を綿密に調べることです。しかし、単に消費電力が最も低いと宣伝されている部品を購入するということは、それが実設計において意図したように動作することを保証する訳ではありません。経験豊富な設計者は、そのアプリケーション固有の特質に基づいて、"typical"と"maximum"電流値の実際の関係を理解するには何らかの"翻訳"をする必要があることを知っています(図2)。多くのアプリケーションでは、データシートに記載されているいわゆるTypical値が、実際にCPLDが引き込むであろう電流に関して非常に役に立つ近似値を与えます。とは言え、設計に対して見積もり値と実際の電力消費が比較的近いことを確実にするために、幾つかのポイントを確認をしなければなりません。

#### **Supply Current**

| Symbol                       | Parameter                      | Condition                                | Min. | Тур. | Max. | Units |

|------------------------------|--------------------------------|------------------------------------------|------|------|------|-------|

| ispMACH 4032ZE               |                                |                                          |      |      |      |       |

| ICC <sup>1, 2, 3, 5, 6</sup> | Operating Power Supply Current | Vcc = 1.8V, T <sub>A</sub> = 25°C        | _    | 50   | _    | μΑ    |

|                              |                                | Vcc = 1.9V, T <sub>A</sub> = 0 to 70°C   | _    | 58   | _    | μΑ    |

|                              |                                | Vcc = 1.9V, T <sub>A</sub> = -40 to 85°C | _    | 60   | _    | μΑ    |

| ICC <sup>4, 5, 6</sup>       | Standby Power Supply Current   | Vcc = 1.8V, T <sub>A</sub> = 25°C        | _    | 10   | _    | μΑ    |

|                              |                                | Vcc = 1.9V, T <sub>A</sub> = 0 to 70°C   | _    | 13   | 25   | μΑ    |

|                              |                                | Vcc = 1.9V, T <sub>A</sub> = -40 to 85°C | _    | 15   | 40   | μΑ    |

| ispMACH 4064ZE               |                                |                                          |      |      |      |       |

| ICC <sup>1, 2, 3, 5, 6</sup> | Operating Power Supply Current | Vcc = 1.8V, T <sub>A</sub> = 25°C        | _    | 80   | _    | μΑ    |

|                              |                                | Vcc = 1.9V, T <sub>A</sub> = 0 to 70°C   | _    | 89   | _    | μΑ    |

|                              |                                | Vcc = 1.9V, T <sub>A</sub> = -40 to 85°C | _    | 92   | _    | μΑ    |

| ICC <sup>4, 5, 6</sup>       | Standby Power Supply Current   | Vcc = 1.8V, T <sub>A</sub> = 25°C        | _    | 11   | _    | μΑ    |

|                              |                                | Vcc = 1.9V, T <sub>A</sub> = 0 to 70°C   | _    | 15   | 30   | μΑ    |

|                              |                                | Vcc = 1.9V, T <sub>A</sub> = -40 to 85°C | _    | 18   | 50   | μΑ    |

- 1. Frequency = 1.0 MHz.

- 2. Device configured with 16-bit counters.

- 3.  $I_{\text{CC}}$  varies with specific device configuration and operating frequency.

- 4.  $V_{CCO} = 3.6 \text{V}, V_{IN} = 0 \text{V}$  or  $V_{CCO}$ , bus maintenance turned off.  $V_{IN}$  above  $V_{CCO}$  will add transient current above the specified standby  $I_{CC}$ .

- 5. Includes V<sub>CCO</sub> current without output loading.

- 6. This operating supply current is with the internal oscillator disabled. Enabling the internal oscillator adds approximately 15µA typical current plus additional current from any logic it drives.

#### 図2供給電流仕様

最初に考える事の一つは、システムの総許容電力のうち、CPLDが何パーセントを負うかということです。それが5%~10%程度のわずかな割合であれば、ワーストケースの条件でも総合的な消費電力に対しては比較的小さな変化しかもたらさない結果となります。CPLDが総許容電力の20%かそれ以上を意味するのであれば、設計としての公称スタンバイ電流値は、データシートに記載されている最大電流に近いと考えるべきです。またシステム上のCPLD(およびその他のデバイス)の数を考慮するべきです。あるボード上のデバイス数が増加するに従って、

それらを合算した消費電力がTypical電流値の合計に近くなる確率も大きくなります。さらに、ワーストケースの電力レベルになる部品が幾つか搭載されていた場合どうなるかという、潜在的な影響を考慮する必要があります。より大きい電力消費は単純に動作寿命を短くしないかどうか、或いは火災の危険性をはらまないか、などです。

図2で注意深くデータシートを調べると、スタンバイ電力が動作温度とVcc(供給電圧)によって異なることに気がつきます。それは温度が上昇するのに従ってCPLDのリーク電流が増加する傾向があるためです。実際に、デバイスを適切に冷却しておくことは、スタンバイ消費電力を改善します。リーク電流はVccにより強く依存するため、供給電圧を可能な限り低く保つことによって、さらに電力を大きく節約できます。本ペーパーの後半で動作時電力の管理を扱う際に、注意深く管理された供給電圧がさらに大きいダイナミック電力の減少をもたらすことを再検証します。

#### バイアス電流を飼いならす

これまでは適切なデバイスを選ぶことによってCPLDリーク電流を制御しましたので、次はバイアス電流をトリムする作業にエンジニアリング・スキルを割り当てる番です。これらのバイアス電流を管理するために用いられる技法は、およそ2種類の作業になります:

- 1、CPLDのスタンバイ・コンフィグレーションが、プルアップ/ダウン、又はそれが接続された他のデバイスで用いられているバスメンテナンス技法と競合しないことを確認する

- 2、(オシレータなどの)内部の機能を、それらが必要に応じてオンするようにダイナミックに制御する(設計のスタンバイ時間をもう少し長くするために、使用するCPLDによってはこれはかなり良い方法かもしれません)

#### バスメンテナンスの競合回避

多くの設計において組み込みホストプロセッサは、バスやI/Oラインの必要なロジックレベルを維持するために、それ自身のバスメンテナンス機構を用いることができます。従って、CPLDをスタンバイモードにする準備のために唯一しさなければならないことは、アクティブなバス管理機能がディセーブルされることの確認です。スタンバイのあいだ、他のアプリケーションではバスを管理しなければならないCPLDの代わりに、バス上のどこか他にあるアクティブ・プルアップやプルダウン回路を使用できます。

しかしCPLDが何もする必要がないということは、なくても良いと言うことを意味するわけではありません。信号線をドライブしているのが単独デバイスである

ことを確かめるために時間をかけることは重要な作業です。というのは、単一ピン上の論理的競合が、チップ全体で公称アイドル電流10uAの電力レベルから2~15倍に増える結果となり得るためです。

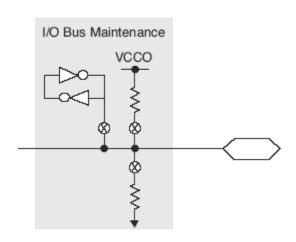

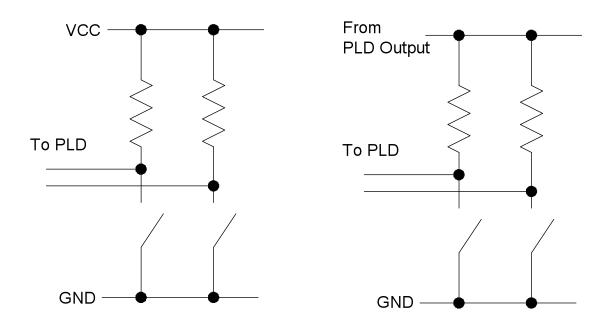

ホストのバスメンテナンス・メカニズムが利用できない状況では、プルアップ/ダウンや、ほとんどの近代的なCPLDで利用できるバスホールド機能を利用するべきです。このクラスにおけるほとんどのデバイスのように、ラティスispMACH 4000ZE CPLDのI/Oピンは選択可能なプルアップとプルダウン抵抗を備えており、スタンバイ状態の間、適切なロジックレベルを与えるために用いることができます(図3)。また、4000ZEシリーズは節電バスキーパ(バスホールドとしても知られる)機能を備えています。これは弱いアクティブなドライバ回路で、簡素な抵抗よりはるかに少ない電力を消費するだけで、アクティブHighかLowのどちらかに設定することができます。注意:バスキーパ機能が電力を顕著に節約する一方で、確かにそれが信号線上のアクティブな唯一のデバイスであることに注意しなければなりません。さもなくば大きい電流を流すリスクをとることになります。

図3 CPLDバスメンテナンス・オプション

#### ダイナミック電力の管理

設計者が関心を持つ必要があるダイナミック電力には、二つのタイプがあります。一方は実際に動作をしている際にCPLD内部を動作させるために必要な電力、他方は、CPLD入力部の動作用電力です。後者に対する電力管理のストラテジには、特定の時点で必要がない入力部をトグルしないようにするとか、または可能であればそれらを完全にオフにすることが含まれます。

#### 高精度の供給電源管理

CPLDのロジックの多くの部分は継続的に使用され、有意な少しの期間もディセーブルすることができない可能性が高いですが、実際に取り得る最低の供給電圧を用いることによって、まだある程度の電力削減を達成することができます。消費電力は電圧の二乗関数で表されるので、1%精度のスイッチングレギュレータに投資してCPLDの許容動作電圧範囲の低いところに下げて回路を動作させることで、かなりの電力を節約することを可能にします。例えば、公称1.8V動作電圧のCPLDが1.65Vで動作するなら、およそ30%少ない電力消費で済みます。しかも、これはVccを低くすることで減少するリーク電流を考慮せずにです。

#### 選択的ロジック・ゲーティング

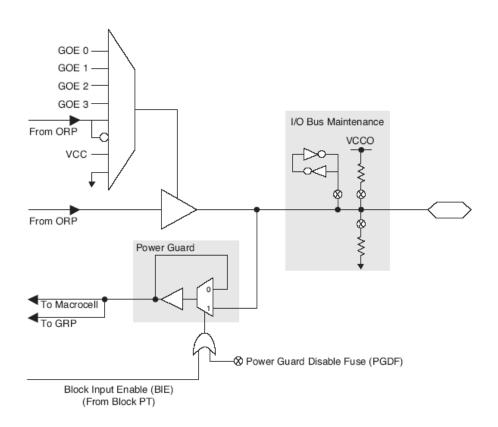

このクラスのほとんどのCPLDのように、ispMACH 4000ZEにはラティスが「パワーガード」と呼ぶ機能があり、ロジックが動作する必要がないときに、それらに接続されている入力を個別にディセーブルするために用いることができます。デバイスのブロック入力イネーブル(Block Input Enable)信号をホストプロセッサや外部ロジック、又はCPLDの他の部分から用いることができ、CPLDロジックの選択したブロックにクロックが供給されるのを防ぐことができます(図4)。例えばCPLDの一部がデコーダ回路として用いられているなら、ホストプロセッサはその機能が用いられているときのみイネーブルし、それ以外の期間は休止状態にしておくことができます。

図4パワーガード回路

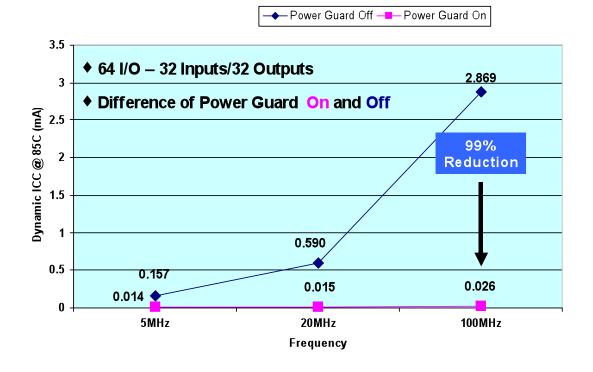

アプリケーションによっては、ラティスのパワーガードか他の技法を用いて選択されたCPLD入力ピンへのクロッキングをディセーブルすることで、ダイナミック消費電力を劇的に減少させることができます。これはロジック信号のクロック周波数がおよそ30MHzを超える場合特に当てはまります。図5は選択的ロジック・クロッキング技法で実現することが可能な、潜在的な電力削減について図示しています。

#### ispMACH 4064ZE-TN100 Power Guard Advantage

図5パワーガード省エネ

#### 低消費電力のためのI/O設計

既に記述された技法を用いることに加えて、抜け目のない技術者にとってほとんどのプロジェクトで微少なuWを節約するさならる機会があります。ただし、多くのデザインの中に潜む小さい「エネルギー吸血鬼」をよく探すことを厭わないと思っていればですが。解りやすい一つの例は、CPLDの入力ラインに取り付けられたスイッチとリレーに検出電圧を供給するために遍在しているプルアップ抵抗です(図6)。使用しているCPLD出力や他の制御信号に、それらを読み込む時のみ検出電圧を供給することによって、設計者は検出ラインがグランド電位になるときに起こる、小さいながらも定常的に流れる電流を排除することができます。

DIP Switch Sense -- Option A

DIP Switch Sense -- Option B

図6パッシブとアクティブに電源を供給するスイッチ検出信号

#### その他の秘訣

- リーク電流を避けるためにCPLDのJTAGインターフェイスピンをフローティングに構成する

- VCCO I/O電源をVCCより高く保つ(電圧が近いほど電流を多く引き込みます)

- 可能な限り遅いスルーレートI/Oを用いる

### まとめ

ほとんどのCPLDベースの設計には、バッテリから静かに電力を消費している間にも「エネルギに飢えた吸血鬼」が潜むことができる、幾つかの暗い片隅が多少含まれています。幸いこれら幾つかの重要な原則を注意深く適用することで、このやっかい物の寄生を終わらせることができます。

- CPLDと他の部品を選ぶとき、そのスタティックとダイナミックな消費電力の両方の位置づけ関して充分に注意を払います。それらは供給電圧、温度、および動作周波数に従って変動します。

- "min"と"max"および"typical"各消費電力仕様が、どのように設計に影響するかを解釈することにも等しい注意を払います。

- スタンバイ時の構成がそれが接続された他のデバイスと競合しないことと共に、いかなる不要な内部機能もディセーブルすることを確実にして、CPLDのバイアス電流を最少にします。

- 必要な期間だけCPLDの各部にクロックを供給することによって、ダイナミック電力を管理します。ラティスのパワーガード機能は、選択的に特定入力へのクロッキングをディセーブルする簡易な方法を提供しますが、それが利用できない場合でも他の技法があります。

- 高精度の供給電源管理を用いることで、ロジックをドライブするための電圧 を実際に採用し得る限り低くすることで、追加のダイナミック電力削減を実 現することができます。

- I/O接続で、不要な電力を奪いとるプルアップ/ダウン抵抗が削除できないか、 或いは必要なときのみ選択的に電源を供給できないかチェックします。

これらの「道具」を慎重に次のプロジェクトに適用するなら、最も見えにくい 「電力吸血鬼」さえあなたの徹底的な管理から逃れることはできません。そし て最終製品はそれに値する長寿命を享受するでしょう。

###