# 实用的低功耗CPLD设计技术

莱迪思公司公司白皮书

2009年8月

Lattice Semiconductor

5555 Northeast Moore Ct.

Hillsboro, Oregon 97124 USA

Telephone: (503) 268-8000

www.latticesemi.com

## 引言

从事便携式或手持产品设计的工程师都明白对于如今的设计,最大限度地降低功耗是必不可少的要求。但是,只有经验丰富的工程师理解尽可能地延长系统的电池寿命的那些微妙但又重要的细节。本文中我们将重点放在这些经验丰富的专家是如何使用超低功耗的复杂可编程逻辑器件(CPLD),并从他们的嵌入式设计中的I/O子系统节省每个微瓦的方法。

我们首先来了解在嵌入式设计中如何降低CPLD的功耗、电路板的面积和元器件成本。下一步,我们将看到在待机模式下如何尽量降低CPLD的功耗,不仅要仔细地选择器件,而且还要选择一个合适的总线驻留方案。器件工作期间,我们对节省功耗的探讨将包括选择逻辑门、智能I/O设计和精密的电源电压管理技术。

## CPLD -嵌入式工程师青睐的器件

尽管在最先进的新兴应用中它们特别受欢迎, CPLD的成本低,体积小和低功耗 的特性使他们成为几乎所有的手持式或便携式设计的首选。在这些应用中,它们常 用来整合逻辑功能,扩展主处理器的I/O功能和监控关键的输入,从而使处理器有 更多的时间处于低功耗睡眠模式。

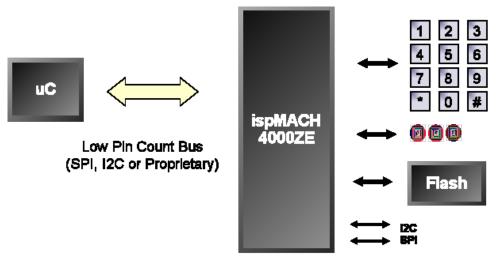

用作I/O的扩展器件时,像ispMACH 4000ZE这样的CPLD器件(图1 )给予简单的嵌入式处理器额外的信号线和处理功能,他们能够支持显示器、按钮、发光二极管,串行或并行I / O ,或存储接口。设计人员还经常利用它们作为设计中通用处理器和更多的专业芯片组之间的缓冲,还能用于其他的应用,如智能手机、GPS系统,远程工业传感器和数码摄像机。

图 1 用Lattice ispMACH 4000ZE CPLD扩展I/O

# 待机功耗的基本知识

掌握CPLD功耗的第一步是了解器件在工作时的情况和待机(也称为静态)时的状态。由于许多CPLD在大部分时间是处于待机状态,我们首先会仔细考察这个经常被误解的模式。

加电压至器件输入部分,但其内部逻辑还没有被时钟控制,此时CPLD是处于待机 状态。在此状态下,因为它的泄漏和偏置电流(虽然大大低于实际的操作), CPLD仍然有一些功耗。泄漏电流随温度、工作电压和制造工艺而变化。

负载产生了可编程逻辑器件内的偏置电流,如内部振荡器、I/O的上拉/下拉电路和其他固定开销,而不管器件的逻辑功能是否正在使用。与泄漏电流不一样,在一定的温度和电压范围内偏置电流是相对稳定的,它们可以用合适的内部配置所控制。

## 用明智的方法管理泄漏电流

由于可编程逻辑器件的泄漏电流主要取决于它是怎样制造的,第一步就是要密切关注候选器件制造商提供的数据手册的规范。只是简单地购买广告所述的低功耗器件并不能保证如你期望设计中达到的指标完全一样。经验丰富的设计师明白寻找"典型"和"最大"电流之间的实际关系需要根据具体的应用(图2)做出解释。在许多应用中,数据手册中列出的所谓典型电流中提供了一个非常有用的CPLD汲取电流的近似值。然而,有几个问题需要加以探讨,以确保对设计的估计和实际功耗保持相对接近。

# **Supply Current**

| Symbol                       | Parameter                      | Condition                                       | Min. | Тур. | Max. | Units |

|------------------------------|--------------------------------|-------------------------------------------------|------|------|------|-------|

| ispMACH 4                    | 032ZE                          |                                                 |      | •    | •    |       |

| ICC <sup>1, 2, 3, 5, 6</sup> | Operating Power Supply Current | Vcc = 1.8V, T <sub>A</sub> = 25°C               | _    | 50   | _    | μΑ    |

|                              |                                | $Vcc = 1.9V, T_A = 0 \text{ to } 70^{\circ}C$   | _    | 58   | _    | μΑ    |

|                              |                                | $Vcc = 1.9V, T_A = -40 \text{ to } 85^{\circ}C$ | _    | 60   | _    | μA    |

| ICC <sup>4, 5, 6</sup>       | Standby Power Supply Current   | Vcc = 1.8V, T <sub>A</sub> = 25°C               | _    | 10   | _    | μA    |

|                              |                                | $Vcc = 1.9V, T_A = 0 \text{ to } 70^{\circ}C$   | _    | 13   | 25   | μΑ    |

|                              |                                | $Vcc = 1.9V, T_A = -40 \text{ to } 85^{\circ}C$ | _    | 15   | 40   | μΑ    |

| ispMACH 4                    | 064ZE                          | ,                                               |      |      |      |       |

| ICC <sup>1, 2, 3, 5, 6</sup> |                                | Vcc = 1.8V, T <sub>A</sub> = 25°C               | _    | 80   | _    | μA    |

|                              | Operating Power Supply Current | $Vcc = 1.9V, T_A = 0 \text{ to } 70^{\circ}C$   | _    | 89   | _    | μΑ    |

|                              |                                | $Vcc = 1.9V, T_A = -40 \text{ to } 85^{\circ}C$ | _    | 92   | _    | μA    |

| ICC <sup>4, 5, 6</sup>       | Standby Power Supply Current   | Vcc = 1.8V, T <sub>A</sub> = 25°C               | _    | 11   | _    | μA    |

|                              |                                | $Vcc = 1.9V, T_A = 0 \text{ to } 70^{\circ}C$   | _    | 15   | 30   | μΑ    |

|                              |                                | $Vcc = 1.9V, T_A = -40 \text{ to } 85^{\circ}C$ | I —  | 18   | 50   | μA    |

- 1. Frequency = 1.0 MHz.

- 2. Device configured with 16-bit counters.

- 3.  $I_{CC}$  varies with specific device configuration and operating frequency.

- 4.  $V_{CCO} = 3.6V$ ,  $V_{IN} = 0V$  or  $V_{CCO}$ , bus maintenance turned off.  $V_{IN}$  above  $V_{CCO}$  will add transient current above the specified standby  $I_{CC}$ .

- Includes V<sub>CCO</sub> current without output loading.

- 6. This operating supply current is with the internal oscillator disabled. Enabling the internal oscillator adds approximately 15µA typical current plus additional current from any logic it drives.

#### 图 2 供给电流规范

首先需要考虑的事项是CPLD占整个系统功耗的比例。如果这是一小部分,比如说 5 % -10 %,即使最坏的情况将引起整个功耗有相对较小的变化。如果CPLD需 要20 %或以上的功耗预算,也许是开始根据额定待机电流考虑偏置设计的时候 了,额定待机电流接近数据手册中列出的最大电流。您还应该考虑设计中CPLD (以及其他器件)的数量。由于电路板上元器件数量的增加,总功耗接近总的典型 额定电流的概率也随之增加。最后,如果您的产品以驱动它至最坏情况的功耗级别 为目标,那么您需要考虑潜在影响:较高的功耗会缩短产品的寿命吗?它是否会成为火灾的隐患?

如果您仔细察看图2中的数据,你可能注意到,待机功耗还根据工作温度和Vcc(电源电压)而变化。这是因为CPLD的漏电流会随温度升高而增加。事实上,使您的设计完美将改善其待机功耗。由于漏电流与Vcc密切相关,保持电源电压尽可能的低可以节省更多的功耗。由于仔细的电源电压管理能够节省更多的动态功耗,在涉及运作功耗管理时,我们会对这个方面进行探讨。

#### 设置偏置电流

通过选择合适的器件,你控制了CPLD的泄漏电流,现在到了运用你的工程技能调整偏置电流的时候了。用来管理这些偏置电流的技术大致分为两种类型:

- 1 -确保CPLD的待机配置不与上拉/下拉或相关的其他器件所用的总线驻留技术相冲突。

- 2 -动态控制内部功能塊(如振荡器),使他们只开启所需要的部分。取决于所使用的CPLD,这是增加更多的待机时间到设计中的好方法。

#### 并行驻留101方案

在许多设计中,嵌入式主处理器可以使用自己的总线驻留方案,以保持在总线或I/O上所需的逻辑电平,所以你只须为CPLD的待机模式做准备,确保其激活总线的管理功能被禁用。在其他应用中,总线上其他地方的上拉或下拉电路也可以缓解在待机期间CPLD必须管理总线的情况。

但是,不需要CPLD做任何事情并不意味着你也不需要做任何事情。花些时间验证 只有一个设备驱动总线是一个重要的任务,因为单个引脚上的逻辑冲突可导致待机 功耗为整个芯片标称值10 uA 闲置功耗的2-15倍。

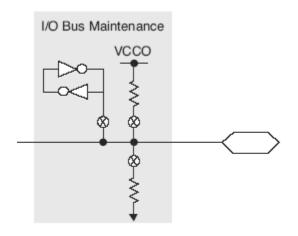

在主总线驻留机制无法使用情况下,可以使用上拉/下拉,以及在大多数现代的 CPLD中拥有的总线保持功能。如同大多数同类器件,莱迪思的ispMACH 4000ZE CPLD的I/O引脚都配备了可选的上拉和下拉电阻,在待机状态(图3)可提供合适的逻辑电平。4000ZE系列还配备了节省功耗的总线保持功能(也称为总线保持): 一种弱激活驱动电路可设置为激活或零,同时产生比简单的电阻器消耗小得多的功

耗。一点忠告:虽然总线保持功能可大大节省功耗,但必须肯定它是唯一的在线有源器件,否则会有吸入大电流的风险。

# 图3 CPLD的总线管理选择

# 动态功耗管理

设计人员需要关注两种类型的动态功耗。运行功耗预算的第一部分是CPLD需要实际工作时的那部分。管理策略的其他部分涉及关掉输入至此刻不需要的CPLD的部分,阻止它们切换,或在可能的情况下将它们全部关闭。

# 精密的电源管理

虽然CPLD逻辑的许多部分很可能被连续使用,在有意义的时间段内不能禁用,因此使用低电源电压仍然可以节省功耗。由于功耗是电压平方的函数,用1 %的精确开关稳压器,可让设计运行于CPLD工作范围的下限,您可以节省相当多的功耗。例如,如果一个标称值为1.8V的CPLD工作在1.65V,它大约少消耗30 %的功耗-这还不包括在较低Vcc的情况下泄漏电流的减少。

# 选择逻辑门

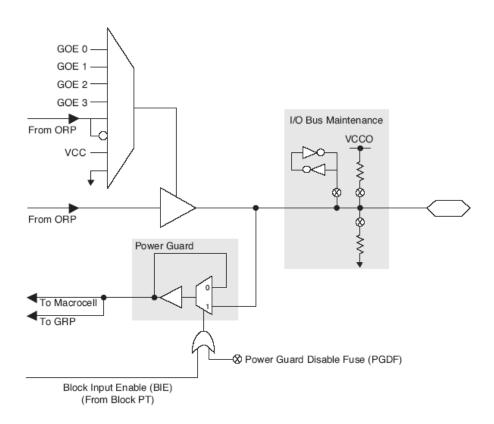

如同大多数的CPLD,ispMACH 4000ZE有一个功能(莱迪思称为"Power Guard" 功耗卫士),当它们不需要相关的逻辑时,可禁用单独的输入。主机处理器、其他的外部逻辑,或CPLD的其他部分可以使用器件的块输入使能线,以保持CPLD的逻辑选定的块被时钟控制(图4 )。例如,如果CPLD的某个部分被用作解码器电路,只有该功能正在使用时,主处理器可以使它能工作,使之能够在其余的时间保持休眠状态。

图 4 Power Guard电路

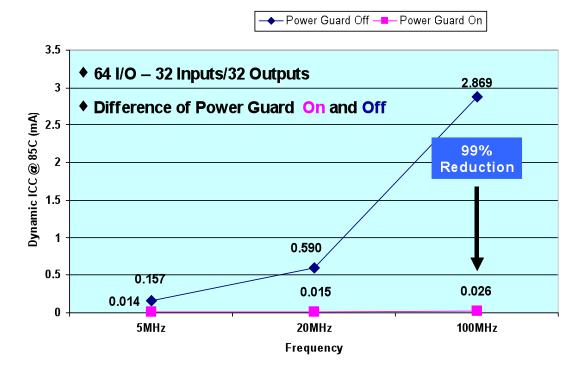

取决于实际的应用,使用Lattice的Power Guard或其他方法来禁用时钟至选定的 CPLD的输入引脚,这样可以大大降低动态功耗。尤其是如果逻辑信号的时钟频率 超过30兆赫时,这些方法特别有用。图5说明了可以用选择逻辑时钟技术实现潜在的节省功耗的方法。

#### ispMACH 4064ZE-TN100 Power Guard Advantage

图5 Power Guard 节省的功耗

## 针对低功耗的I/O设计

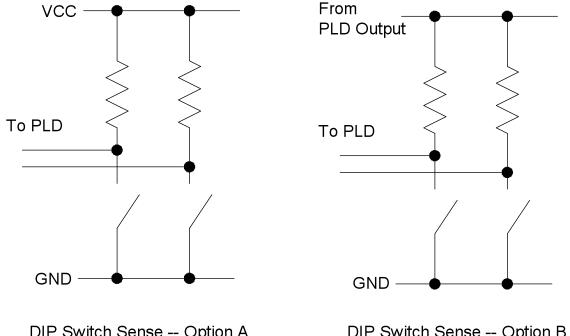

除了使用已经阐述的技术,目前大部分项目给予精明的工程师更多节省多余的微瓦功耗的机会—如果他们愿意关注潜伏在许多设计中的微小能源汲取部分。一个好的例子是无处不在的为开关提供读出电压的上拉电阻,以及连接到CPLD的输入线(图6)。通过使用CPLD的输出,或其他控制线至电源电压到读出线,只有当他们被读取时,并且读出线接地时,设计人员方可去除这个小而稳定的电流。

DIP Switch Sense -- Option A

DIP Switch Sense -- Option B

图 6 无源和有源功率开关读出线

### 其他提示

- •配置可编程逻辑器件的JTAG接口引脚为浮动状态,以避免漏电流。

- •保持VCCO的I / O电平高于VCC。越接近这个电压,吸收的电流越多。

- •在可能的情况下,使用转换率慢的I/O。

#### 结论

大多数基于CPLD设计至少包括一些未引起注意的角落,在这些地方潜伏着耗能大 户,他们悄悄地汲取电池的能量。幸运的是,认真实施一些重要的原则可以制止这 些讨厌的寄生部分:

- 当选择CPLD和其他元件时,注意其静态和动态功耗等级:他们随供电电压、 温度和工作频率而变化。

- 同样要注意"最小"、"最大"和"典型"功耗指标,它们将影响你的设计。

- 尽量减少CPLD的偏置电流,确保其待机配置不与其他与之相连的器件相冲 突, 关闭任何不必要的内部功能。

- 管理动态功耗,只给当前CPLD需要的部分加时钟。莱迪思的Power Guard功能 提供一个简单的方法来选择关闭时钟至专门的输入,如果无法使用的话,还有 其他的技术可用。

- 使用精确的电源控制驱动逻辑,可实现节省额外的动态功耗,使用尽可能低的 电源电压。

- 检查I/O的连接,看看是否有不必要的可去除的加载的汲取功耗的上拉/下拉电阻,或只在需要时才选择加载电阻。

如果你仔细地将这些工具应用到下一个项目,设计中就不会有隐藏的汲取功耗的大户,你的产品将会有很长的寿命。

###