## 在下一代無線網路中的 FPGA

# **萊迪思半導體公司白皮書** 2010年3月

Lattice Semiconductor 5555 Northeast Moore Ct. Hillsboro, Oregon 97124 USA Telephone: (503) 268-8000 www.latticesemi.com

#### 引言

除了語音連接之外,數位蜂窩無線網路,如 GSM 和增強的 GSM-EDGE 現在可以提供更高的資料傳輸速率,理論上可達 384kbps 的限制。第三代移動網路,例如 CDMA2000 和 WCDMA 或 UMTS (Universal Mobile Telecommunications Standards) 和 TD - SCDMA (中國標準)目前正在全球範圍內部署。這些系統提供的服務,如視頻流媒體,互聯網流覽和使用稱爲高速分組接入(HSPA)的技術,在理論上他們可以提供下行速率高達14.4Mbps。

未來基礎設施的發展,泛稱為 4G 系統專注於以很低的成本提供更高的速度和更強的功能。在這一發展的前沿有兩種技術:3GPP LTE(3rd Generation Partnership Program,長期的演進)用於蜂窩/移動技術,通常簡寫為 LTE,以及針對寬頻無線接入的 WiMAX。WiMAX 已經贏得了早期進入市場的支持,但一些漫遊和基站之間的切換問題依然存在。主要的蜂窩網路運營商支援 LTE,將其作爲未來的選擇技術。這兩個 4G 標準使用基於OFDM(正交頻分調製)的通用無线介面標準,以及 MIMO(Multiple Input Multiple Output)天線網路。這些先進的技術能夠使信號從更高的雜訊閱值中恢復出來,這對廣泛的區域覆蓋是基本的。

這些複雜且有時相互競爭的技術的實際結果是要求設備供應商能夠支援多種空中介面標準,以及需要進行更複雜的基帶處理。同時,這些系統必須能夠提供靈活性,以適應發展規劃,以便滿足未來所需的增加帶寬的要求。他們必須採用降低成本的方式,也爲了滿足人們對綠色環保要求的關注,即要求有更低的功率預算。

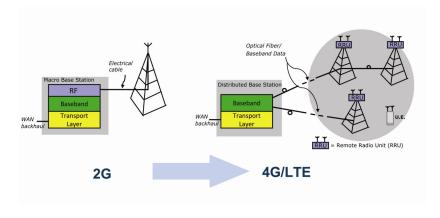

在第二代基站系統中,巨集基站通常位於天線的下面,RF 功率放大器緊靠基帶和前置放大器。該主要系統的發展之一是用於分散式基站。在這些系統中,基帶處理獨立於射頻功率部分。從架構上而言,從巨集 站移動到分散式基站系統(圖 1),可以大大降低系統成本。在其他要求中,巨集基站與天線的距離必須在 150 米之內,在電纜中會有 50%的RF 功率損失。設備更新和維護的成本很高。更好的解決辦法是採用分散式"遠端無線"網路,基帶部分相距很遠,有射頻功率放大器的遠端射頻單元(RRU)可直接安裝在天線杆上。通過光纖和標準介面如 CPRI(通用公共無線介面)或 OBSAI(開放式基站架構計畫),RRU 單元可以鏈結到基帶。

圖 1 - 基站網路的演進

#### 在無線基礎設施中的 FPGA

可編程技術的特點是能夠跟隨基站設計的演進,因爲通常設計在規範被完全批准之前就開始了。基站需要大量的 ASIC 器件,FPGA 通常被用作介面和"粘合 "邏輯:能夠快速修正設計錯誤,或支援專門的 DSP 器件的功能。隨著無線標準的演變,基站的複雜性也相應大大增加。FPGA 也在不斷發生變化,其性能和邏輯密度大大增加。工程師開始將FPGA 用於更複雜的功能,例如數位降變頻(DDC)和數位升變頻(DUC)。針對在基站設計中的這些功能,FPGA 提供的靈活性意味著現在 FPGA 成爲設計過程中的重要部件。現在 Lattice ECP3 FPGA 擁有許多特性,如多個嵌入式 DSP 塊,嵌入式記憶體和SERDES 功能。這些功能與無線系統的不斷發展的需求緊密相關,因此他們成爲設計工程師所選擇的器件。 FPGA 的靈活性使工程師能夠快速修改設計,而不必等待使用另一個 ASIC 而再重新設計電路板,從而加快了產品的上市時間。

#### 遠端無線單元/頭。

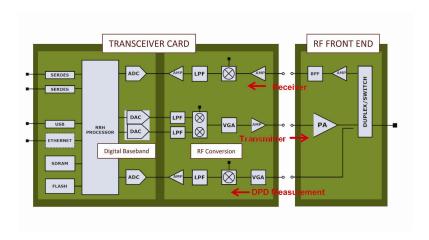

RRU 功能包括一個具有數位信號處理功能的收發器卡、射頻轉換、包含功率放大器、雙工器和 LNA(Low Noise Amplifier 低雜訊放大器)的射頻前端。收發器卡的設計往往是寬頻的,在無線標準和工作頻帶之間有 80-90%之間的元器件通用性。一個典型的單元如圖 2 所示。

圖 2 - 典型的收發器卡的設計

FPGA的可重構特性允許 SDR(軟體無線電)技術支援多種無線標準,例如 WCDMA、WiMAX,以及通用基帶的 LTE。對於 MIMO 天線系統,該單元必須爲每根天線提供一個發射器和接收器對。

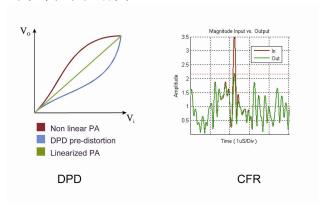

下一代網路將比目前部署的網路運行的頻率高得多,通常會超過 2 GHz。他們還需要提供更高的資料傳輸率。主要的 RRU 設計問題是功耗和射頻功率放大器(Power Amplifier 功率放大器)的成本。大信號峰值對平均功率比(PAPR)要求功率放大器傳送少見的更大功率。雖然這種情況很少發生,設計必須實現這個功能,這將轉化爲更高的成本。射頻電晶體在大功率時呈現了非線性,造成信號失真和帶外發射。大信號峰值對平均功率比和在 4G 系統中的非線性這二者的共同影響可能導致功率放大器將只運行在其總輸出功率的 20-30%,整個效率只有 10-15%。而與之相比,GSM 功率放大器的運行可達到 100%利用率和高達 70%效率。對這個問題的解決辦法是在最後的功率放大器前預先處理這個信號,這種方式最終導致放大的射頻信號有最佳的性能。在這一過程中可以使用兩種方法;波峰抑制迴路(CFR)和數位預失真(DPD)。

波峰抑制迴路工作原理是智慧地限制功率放大器輸入的最大波形振幅,因此產生峰值輸出功率。這有效地降低了這個信號的 PAPR,同時保持所需信號的精確度和頻譜特性。在低功耗或微型基站情況下,如 WiMAX 或 Picocell,可以使用它而無需 DPD。

另一方面,DPD 能夠使功率放大器線性化,通過應用一種使輸入信號失真的方式,這種方式考慮了功率放大器的傳輸特性,因此使任何信號失真無效,這是功率放大器的特性所導致的。在射頻輸出功率大於 1-2 瓦的大功率系統中,它通常與 CFR 相結合。這些技術

的效果如圖3所示。

圖 3 DPD 和 CFR 技術的效果

在 RRU 中使用 CFR 和 DPD 技術可以讓系統工程師使用比採用其他技術更低成本的功率放大器。這兩種方法都需要大量的 DSP 處理功能,以實現行必要的演算法。最重要的是,他們還需要某種具有一定的可適性,因爲他們需要適應功率放大器傳輸特性的任何變化,這可能發生在溫度和時間變化的情況。

RRU 內遠端無線處理器的合併是對這個問題的解決方案之一。傳統上 ASIC 被廣泛用於蜂窩基站的設計,但是他們的設計週期長,高固定成本和不靈活,他們不適合仍在不斷發展的市場。對這個問題,分立的 DSP 處理器似乎是另一個解決方案,但分析表明,在多種標準的基站實現方面,它們也有局限性。另一方面,具有嵌入式 DSP 單元、SerDes功能和軟處理器的 FPGA 在一個可重構的晶片中提供所有的功能。這個器件就是萊迪思半導體公司的 ECP3。對任何帶有 SERDES 功能的 FPGA 器件而言,這個 FPGA 具有業界最低的功耗和價格。該系列產品提供遵守 XAUI 抖動標準的多協議 3.2G SERDES、DDR1/2/3 記憶體介面、功能強大的 DSP 功能和高密度的片上記憶體,與帶有 SERDES功能的 FPGA 相比,所有這些功能只有競爭產品的一半功耗和一半價格。

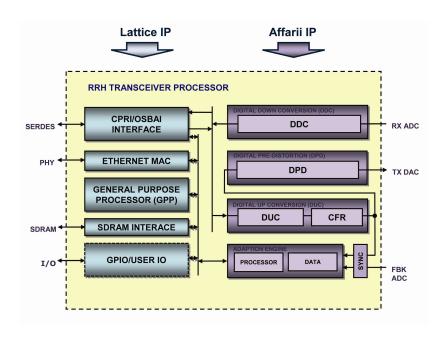

而選擇 FPGA 時需要認真考慮,以滿足系統的物理和性能參數要求,獲得實現 RRU 的關鍵功能的 IP 核對整個系統的解決方案而言是至關重要的。作為 IP 合作夥伴計畫的一部分,萊迪思公司與擁有豐富蜂窩無線系統經驗的 Affarii 公司一起致力於該項工作。 Lattice ECP3 FPGA 與 Affarii 的 IP 結合在一起提供了一個靈活的平臺,可以在 FPGA 架構中組合構建 RRU 所需的所有 IP 模組。

圖 4 RRU 處理器

針對發送和接收,RRU處理器的功能是多工和調製這個信號資料到射頻載波。圖 4 展示了萊迪思的 IP 和 Affarii 提供的 IP。這些塊已用不同的顏色加以區別。

針對不同的具體應用,可以對 CFR 配置進行優化。最高載波配置的類比可以決定精確的參數。在設計工具和文檔中提供了標準的系統配置。對於用戶自己的應用,用戶還可以創建自定義的配置,使用 IP 模型和有 IP 核的仿真環境。將 CFR IP 放置在 LFE-70E FPGA中進行佈局和佈線,表 1a 展示了資源利用率。

通過針對功率放大器的特性來確定 DPD 工作的配置是最好的方法。DPD 核本身支援診斷介面,以提供現場或測試源的資料分析。使用這個工具,可以實現放大器的非線性複雜特性,因此可以針對 DPD 決定最好的配置。因為它測量即時的放大器參數,這個過程還可以突出顯示在設計放大器時所需作出的改進。表 1b 展示了將 DPD 放置在 Lattice LFE-70E 中進行佈局和佈線所需的資源。

| CFR Place & Routed: LFE3-70E-FPBGA484-8 |      |     |        |     |      |     |  |  |

|-----------------------------------------|------|-----|--------|-----|------|-----|--|--|

| STANDARD                                | MODE | СН  | SLICES | EBR | MULT | MHz |  |  |

| LTE, WIMAX                              | SYM  | 1-2 | 8K     | 22  | 22   | 213 |  |  |

| LTE, WCDMA                              | ASYM | 1-4 | 14K    | 48  | 69   | 209 |  |  |

| DPD Place & Routed: LFE3-70E-FPBGA484-8 |     |     |        |     |      |     |  |  |  |  |

|-----------------------------------------|-----|-----|--------|-----|------|-----|--|--|--|--|

| COMPONENT                               | DPD | EQU | SLICES | EBR | MULT | MHz |  |  |  |  |

| PREDISTORTION<br>FILTER                 | 4   | 9   | 4K     | 5   | 39   | 182 |  |  |  |  |

表 1b

該 Affarii IP 不僅包括了 CFR 和 DPD 功能,而且還有 DUC,DDC 和匹配引擎的功能,這是基站結構的重要組成部分。

由萊迪思提供的主要 IP 塊是 CPRI 和 OBSAI:這些是使用 FPGA 中帶有的嵌入式 SERDES 功能的高速介面。這些介面連接遠端基帶至 RRU。乙太網 MAC 提供監測和控制系統的功能。設計師也可以選擇使用 LatticeMico32 軟處理器,用於 RRH 通用處理和控制,以便減少元件的數量和節省成本。用先進的記憶體介面和通用 I / O (GPIO)介面可以完成該系統。

### 總結

FPGA 現在已發展成爲高度集成的器件,可以包括嵌入式 ASIC 類型的功能,提供增強的介面功能。軟核微處理器功能加上 DSP 處理器和嵌入式記憶體意味著在基站設計中使用的 FPGA 將用一個可重構晶片提供功能核。可編程器件提供的優點將使產品能夠更快地進入市場,靈活地適應新的和不斷發展的具有成本效益的標準。

###