## 차세대 무선 네트워크에서의 FPGA

# A Lattice Semiconductor White Paper 2010년 3월

래티스 반도체 주식회사 5555 Northeast Moore Ct. Hillsboro, Oregon 97124 USA Telephone: (503) 268-8000

www.latticesemi.com

### 소개

음성통신 연결에 GSM과 향상된 GSM-EDGE와 같은 디지털 셀룰러 무선 네트워크는 (이론상) 최대 384Kbps까지 데이터 속도를 추가적으로 제공할 수 있습니다. CDMA2000과 WCDMA 혹은 UMTS(범용 이동 통신 표준), TD-SCDMA(중국에 한함)와 같은 제 3세대 모바일 네트워크가 현재 전 세계적으로 보급되고 있습니다. 이러한

시스템은 고속 패킷 접속(HSPA)이라 불리는 기술을 이용하여 비디오 스트리밍, 인터넷 브라우징과 같은 서비스를 제공하며, 이론적인 하향 속도는 최대 14.4Mbps까지 제공이 가능합니다.

4G 시스템이라 불리는 미래 인프라 개발은 저비용으로 더 높은 속도와 높은 용량 제공에 초점을 맞추고 있습니다. 이 개발의 최전선에는 두 가지 기술이 있습니다:

셀룰러/모바일 기술을 위한 3GPP LTE(3rd Generation Partnership Program, Long Term Evolution)가 있고, 광대역 무선 액세스를 위한 LTE와 WiMAX가 있습니다. WiMAX는 액세스 시장에서 초기 선점 위치에 있지만, 기지국간에 로밍과 스위칭에 관한 몇 가지 문제가 남아있습니다. 주요 셀룰러 네트워크 운용자는 미래의 기술로서 LTE를 지원하고 있습니다. 각 4G 표준은 OFDM(Orthogonal Frequency Division Modulation)과

MIMO(Multiple Input Multiple Output)안테나 네트워크를 기반으로 무선 인터페이스를 이용하고 있습니다. 이런 진화된 기술들로 인하여 넓은 지역을 커버하기 위해 필수적으로 필요한 높은 노이즈 임계치 범위에서의 신호 복구가 가능해졌습니다.

이러한 복잡한 네트워크와 경쟁 기술에 있어서 장비 제조업체는 복잡한 베이스 밴드 처리뿐만 아니라 여러 개의 무선 인터페이스 표준을 지원해야 할 필요성이 있습니다. 동시에, 이러한 시스템들은 증가되고 있는 대역폭을 향후에 수용할 수 있는 유연성을 갖추어야 합니다. 그것들은 또한 녹색 환경 부분을 고려하여 낮은 전원 소비와 저렴한 비용을 갖추어 완성되어야 합니다.

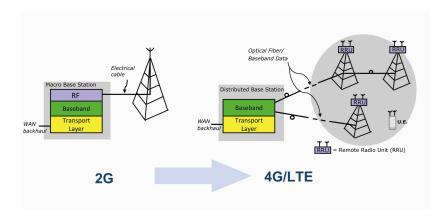

일반적으로 제2세대 마이크로 기지국은 물리적으로 RF파워를 갖춘 안테나가 있는 베이스밴드와 프리-앰프 가까이에 위치합니다. 주요 시스템 개발은 분산 기지국을 이용하는 것입니다. 이러한 시스템에서 베이스밴드 처리는 RF 파워부분과

분리되어있습니다. 구조적으로 마이크로 기지국 시스템으로부터 분산된 기지국 시스템(그림1)으로의 변화를 줌으로써 시스템 가격을 절감할 수 있습니다. 기타 요구 사항 중에서, 마이크로 기지국은 안테나와 150m이내에 위치해야 하며, RF 파워의 50%는 케이블에서 손실될 수 있습니다. 장비 업그레이드와 유지보수에는 비용이 듭니다. 더 나은 솔루션으로는 분산 "원격 라디오" 네트워크가 있는데, 이는 베이스 밴드가 원격지에 위치되고, RF파워 앰프를 포함하고 있는 RRU(Remote Radio Unit)는 마스터 안테나에 직접 장착될 수 있습니다. RRU 유닛은 광섬유와 CPRI(Common Public Radio Interface) 혹은 OBSAI(Open Basestation Architecture Initiative)와 같은 표준 인터페이스를 통하여 베이스밴드에 연결될 수 있습니다.

그림 1 - 기지국 네트워크의 진화

### 무선 인프라에서의 FPGA

규격은 완전한 비준을 받기도 전에 종종 실행되기 때문에, 기지국 디자인의 진화는 프로그래밍을 통하여 운용되는 것이 특징입니다. 기지국은 ASIC디바이스가 가장 많이 적용되는 부분입니다, 그리고 FPGA는 디자인 버그에 대한 신속한 수정 혹은 특정 DSP 디바이스지원을 위한 인터페이스와 "글루로직"으로서 사용되었습니다. 무선 표준 진화에 따라, 기지국의 복잡성 역시 증가되었습니다. FPGA 역시 성능과 로직 밀도를 높이는 진화 과정에 있습니다. 엔지니어는 디지털다운 컨버전(DDC)과 디지털 업 컨버전 (DUC)과 같은 더욱 복잡한 기능들을 사용하기 시작했습니다. 기지국 디자인에 있어서 이러한 기능구현을 위한 FPGA의 유연성은 FPGA가 핵심 요소가 되었음을 의미합니다.

LatticeECP3제품과 같은 FPGA는 오늘날 여러 임베디드 DSP블럭, 임베디드 메모리, SERDES 기능과 같은 많은 기능들을 포함하고 있습니다. 이러한 기능들은 무선 시스템의 진화에 필요한 부분과 관련이 되었으며, 디자인 엔지니어들이 선택할 수 있는 계기가 되었습니다. FPGA의 유연성은 엔지니어들이 ASIC 재설계에 대한 기다림 없이, 신속히 변화에 맞추어 디자인 구현을 할 수 있도록 합니다.

#### Remote Radio Unit/Head. (원격 라디오 유닛/헤드)

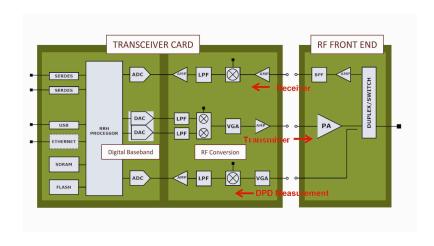

RRU 기능은 디지털 신호 처리와 RF 전환 및 RF 프런트 엔드 어셈블리 전력 증폭기, 양방향 및 LNA (낮은 잡음 증폭기)를 갖춘 송수신기 카드로 구성되어있습니다. 송수신 카드 디자인은 종종 무선 표준 및 운영 밴드 사이 80~90% 구성 요소를 폭넓게 공용하고 있습니다. 전형적인 장치는 그림 2에 표시됩니다.

그림 2 - 전형적인 트랜시버 카드 디자인

재구성이 가능한 FPGA의 이용으로 인하여 SDR(소프트웨어로 정의된 라디오)기술을 적용하여 WCDMA,WiMAX와 LTE와 같은 여러 무선 표준을 하나의 일반적인 베이스 밴드로서 지원할 수 있게 되었습니다. MIMO안테나 시스템을 위해, 유닛은 각 안테나에 대해서 송/수신기 한 쌍을 반드시 제공하여야 합니다.

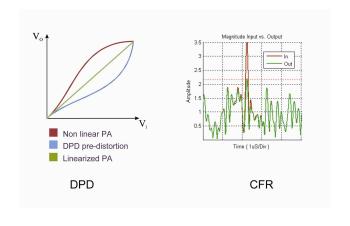

차세대 네트워크는 현재 보통 2GHz를 초과한 높은 주파수에서 동작할 것입니다. 그것들은 또한 더 높은 데이터 전송율을 제공할 것입니다. 주요 RRU디자인 이슈는 전력 소모와 RF PA(Power Amplifier)의 가격입니다. 평균전력비율(PARR)에 높은 신호 피크는 PA가 높은 전력 레벨을 송신하도록 요구합니다. 그러나, 이러한 발생은 디자인에서 반드시 허용되어야 하지만, 이는 높은 비용이 발생되는 원인이기도 합니다. RF 트랜지스터 역시 높은 전력 레벨에서 비-선형성을 보여 주고 있고, 결과적으로 신호 왜곡과 밴드 이탈이 발생됩니다. 4G시스템에서 높은 PARR과 결합된 효과 및 비선형성은 PA가 전체 효율의 10~15%로, 잠재적인 출력 전력 능력의 20~30%로 동작되도록 합니다. 이러한 문제의 해결은 증폭된 RF신호 결과가 최적의 성능을 도출할수 있도록 최종적인 PA전에 신호를 미리 제어 하는 것입니다. 이러한 과정에는 Crest Factor Reduction (CFR)과 Digital Pre-distortion (DPD)방식 두 가지가 있습니다.

CFR(Crest Factor Reduction)은 PA의 입력에 최대 파형 진폭을 지능적으로 제한하면서 동작하는 것을 말하며, 그럼으로써 출력 파워 피크치를 도출할 수 있습니다. 이것은 요구된 신호의 정확성과 스텍트럴 규격을 유지하면서도 신호 PAPR을 감소시키는 효과가 있습니다. WiMAX혹은 Picocell과 같은 저전력 마이크로 기지국에서는 DPD없이도 이용될 수 있습니다.

한편, DPD는 PA전달 특성을 고려한 방식으로 입력 신호에 왜곡을 적용함으로써 선형적인 PA를 만들 수 있는 것입니다. PA특성의 결과로서 신호 왜곡이 무력화 될 수 있으며, 1-2와트 이상의 고출력 시스템에서 CFR과 동시에 이용됩니다. 이러한 기술 효과는 그림3에서 보여지고 있습니다.

차세대 무선 네트워크에서의 FPGA

#### 그림 3 - DPD 효과와 CFR기술

RRU에서 CFR과 DPD의 사용은 시스템 엔지니어들이 훨씬 저가의 PA를 사용할 수 있도록 합니다. 각각의 기술들은 필요한 알고리즘을 구현하기 위해 많은 부분의 DSP 처리 능력을 요구합니다. 그것들은 온도와 시간 범위 초과부분에서 발생할지도 모를 PA전달 특성의 변화부분을 수용할 수 있는 적응능력이 요구됩니다.

RRU내에 원격 무선 프로세서의 결합은 이 문제에 대한 하나의 솔루션입니다. 전통적인 ASIC은 셀룰러 기지국 디자인에서 폭넓게 이용되어 왔습니다; 그러나 그들의 긴 디자인 주기와 고정된 고비용 및 비 융통성 때문에 여전히 혁신적인 시장에는 적절하지 못합니다. 개별 DSP프로세서는 이 문제를 위한 또 하나의 솔루션처럼 보일 수 있습니다만, 여러 표준 기지국 구현에는 너무도 많은 제한이 있는 것으로 분석 결과가 보여주고 있습니다. 한편, 임베디드 DSP셀, SERDES기능과 소프트 프로세서를 갖춘FPGA는 단일 리컨피규레이션 칩에서 요구되어지는 모든 기능을 수용할 수 있습니다. 이러한 디바이스에는 래티스 반도체의 ECP3가 있습니다. 이 FPGA는 SERDES를 갖춘 FPGA중에서 산업계 최저 전력 소모와 저가로서 제공되고 있습니다. 이 제품군은 XAUI 지터 규정을 만족하며 다양한 3.2G SERDES 프로토콜, DDR1/2/3 메모리 인터페이스, 강력한 DSP기능과 고 집적 온-칩 메모리를 제공하며, SERDES기능이 갖추어진 경쟁사 FPGA에 비해 전력 소모는 절반, 가격도 절반 정도의 경쟁력을 갖추고 있습니다.

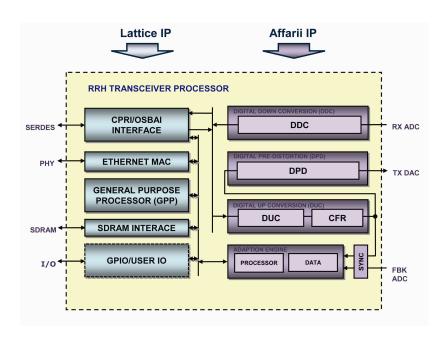

FPGA는 시스템의 물리적 성능변수의 충족부분을 충분히 고려하여 선택하는 반면에, 전체 시스템 솔루션을 위해 RRU의 기능측면에서는 이용 가능한 IP가 매우 중요합니다. IP파트너 프로그램 부분에서, 래티스는 셀룰러 라디오 시스템에 폭넓은 경험이 있는Affarii와 손을 잡고 있습니다. Affarii IP와 LatticeECP3 FPGA의 협력으로 각각의 회사가 FPGA내에 RRU를 구축하는데 필수적인 모든 IP블록을 조합할 수 있는 유연한 플랫폼을 제공할 수 있게 되었습니다.

그림 4 - RRU 프로세서

RRU프로세서는 송수신을 위해 RF캐리어로 신호 데이터의 다중화와 신호 변조에 대한 책임을 갖고 있습니다. 그림4는 래티스 IP와 Affarii에 의해 제공된 IP를 보여주고 있습니다. 블록은 색상별로 식별이 용이하게 해 놓았습니다.

CFR구성은 서로 다른 특정 애플리케이션을 위해 최적화 될 수 있습니다. 이러한 세밀한 변수는 최대 캐리어 구성의 시뮬레이션에 의해 결정될 수 있습니다. 표준 시스템 구성은 디자인 툴과 설명서에서 제공됩니다. 사용자는 IP모델과 IP코어에 적용된 시뮬레이션 환경을 이용하여 자체 애플리케이션을 위해 사용자의 구성을 생성해 볼 수도 있습니다. 표 1a는 LFE-70E FPGA에 CFR IP의 라우팅을 위한 리소스 사용을 보여주고 있습니다.

DPD동작의 구성은 타겟 PA의 특징에 의해 결정됩니다. DPD코어 자체는 테스트 소스혹은 실제 소스로부터 데이터의 분석을 제공하기 위해 진단 인터페이스를 지원합니다. 이러한 툴을 이용함으로써, 비선형 앰프의 상세한 특성이 수행될 수 있고, 그렇게함으로써 DPD를 위한 최적의 구성이 결정될 수 있습니다. 이 절차는 실시간 앰프의 변수때문에 앰프 디자인의 개선을 위해 필요한 부분이 될 수 있습니다. 표 1b는 DPD가래티스 LFE-70EP에서 라우팅되는데 필요한 리소스를 보여줍니다.

| CFR Place & Routed: LFE3-70E-FPBGA484-8 |      |     |        |     |      |     |  |  |  |

|-----------------------------------------|------|-----|--------|-----|------|-----|--|--|--|

| STANDARD                                | MODE | СН  | SLICES | EBR | MULT | MHz |  |  |  |

| LTE, WIMAX                              | SYM  | 1-2 | 8K     | 22  | 22   | 213 |  |  |  |

| CFR Place & Routed: LFE3-70E-FPBGA484-8 |       |     |        |     |      |     |  |  |  |

|-----------------------------------------|-------|-----|--------|-----|------|-----|--|--|--|

| BLOCK                                   | BW    | LEN | SLICES | EBR | MULT | MHz |  |  |  |

| DPD ENGINE                              | 20MHz | 9   | 4.5K   | 70  | 43   | 184 |  |  |  |

Table 1

Affarii의 IP는 CFR 및 DPD 기능뿐만 아니라 DUC, DDC 그리고 기지국 아키텍처의 필수 빌딩 블록인 응용 엔진 기능이 포함되어있습니다.

래티스에 의해 제공되는 주요 IP블록들은 CPRI와 OBSAI가 있습니다: FPGA에 포함된 임베디드 SERDES기능을 이용하는 고속의 인터페이스가 있는데, 이 인터페이스 는 RRU원격 기지국과 연결합니다. 이더넷 MAC은 시스템 제어와 감시 기능을 제공합니다. 디자이너는 또한 RRH 의 일반적인 처리, 부품의 수와 가격을 절감하기 위해 LatticeMico32소프트 프로세서의 적용을 선택할 수 있습니다. 향상된 메모리 인터페이스와 일반 목적의 I/O는 시스템을 완벽한 체계로 구성할 수 있도록 합니다.

### 요약

FPGA는 향상된 인터페이스 기능을 제공하는 임베디드 ASIC형태를 포함할 수 있는 고집적 디바이스로 성숙했습니다. 베이스 밴드 디자인에서 마이크로 프로세서 기능이통합된 DSP 프로세서 및 임베디드 메모리는 재구성이 가능한 단일 칩으로 핵심적인기능 제공을 의미합니다. 프로그래머블 디바이스에 의해 제공되는 장점들은 비용적인측면에서 효율적으로 새로운 표준에 유연성 있게 타임 투 마켓을 활성화 시킬 수있습니다.