1

# 實用的低功耗 CPLD 設計

Lattice Semiconductor 白皮書 2009年8月

Lattice Semiconductor

5555 Northeast Moore Ct.

Hillsboro, Oregon 97124 USA

Telephone: (503) 268-8000

www.latticesemi.com

# 背景

任何開發可攜式或掌上型產品的工程師都瞭解,在現今的設計工作中,儘可能降低功耗是一項絕對必要的任務。但是,只有老練的工程師能掌握許多細微但重要的門路,而能把系統的電池續航力提升到最高。在這篇白皮書中,我們將探討這些老手如何運用超低功耗的複雜可編程邏輯晶片(CPLD),從嵌入式設計中的各個I/O子系統中榨出最後一微瓦的電量。

首先,我們要檢視廣為業界所運用的CPLD如何在嵌入式設計中縮減功耗、電路板空間、以及零組件成本。接著,我們再研究如何降低在待機模式中的CPLD功耗,其方法包括審慎選擇元件,以及選擇適合的匯流排暫停機制。之後我們要研究運作模式下的省電方法,包括選擇邏輯閘、智慧型I/O設計、以及精準的供電電壓管理等技巧。

### CPLD-嵌入式產品工程師的優勢

雖然業界普遍瞭解應在新產品中運用最具優勢的方案,亦即利用CPLD在低成本、 微型化、以及低功耗等方面的特性,這些優點讓CPLD在掌上型或可攜式設計中成 為業界極為理想的選擇。在這些應用中,業者經常運用CPLD來整合各種邏輯功 能、擴充主處理器的I/O功能,以及監視關鍵的輸入訊號,並讓處理器能有更多時 間切換至低功耗的休眠模式。

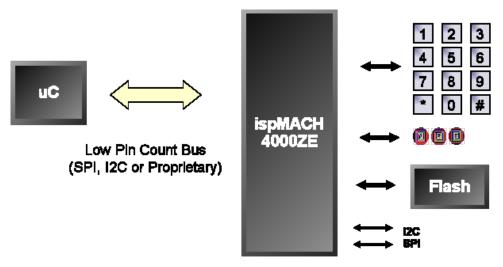

當CPLD作為I/O擴充元件時,類似ispMACH 4000ZE(如圖1所示)的元件便能為簡單的嵌入式處理器提供額外的訊號通道及各種定址功能,而讓處理器能支援顯示、按鈕、LED燈號、串列/並行I/O、或儲存介面。研發業者亦常運用CPLD作為分界點,其可用來區隔通用處理器及更專業的晶片組,應用領域包括智慧型手機、GPS衛星導航系統、工業遠端感測器、以及數位攝影機等。

圖1 – 運用Lattice的 ispMACH 4000ZE CPLD元件來進行I/O擴充

#### 待機功耗的基本概念

要徹底瞭解CPLD功耗,第一步得先瞭解元件在運作與待機(亦稱為靜態)狀態時的 行為。由於許多CPLD在大多數時間都是處於待機模式,因此就讓我們先仔細探討 這個經常被大家誤解的模式。

當CPLD元件的輸入端已導通電源,但其內部邏輯元件尚未設定時序時,此時 CPLD處在待機狀態。在這種狀態下,因CPLD有漏電與偏置電流(雖然遠低於實際 運作時的數值),因此仍會消耗一些電力。漏電流和許多影響因素之間呈函數關 係,包括溫度、運作電壓、以及製程等。

CPLD的偏置電流是由各種負載所產生的,例如內部共振器、I/O線路內的上拉/下 拉電路、以及其他固定的損耗資源,不論元件使用哪些邏輯功能,這些負載都會存 在。有別於漏電流的是,在溫度與電壓範圍內,偏置電流相對較為穩定,其可透過 適當的元件配置來加以控制。

### 明智判讀規格資料以有效管理漏電流

由於決定CPLD漏電流的主要因素是其製造方式,因此第一步就是仔細檢視製造商產品型錄中所載明的規格。但選購廠商宣稱功耗最低的元件,並不一定保證在你設計的產品中會達到與規格相符的性能。經驗老到的設計者都知道,想在"正常"與"最高"額定電流之間找出兩者的實際關係,需要費一番功夫參照其設計產品的規格,方能判斷出元件的實際性能(如圖2所示)。在許多應用中,產品型錄列出的所謂的正常電流,代表CPLD功耗的近似值,這是相當實用的參考數據。不過,我們還須澄清幾個問題,才能保證設計的預估值會相當趨近實際功耗。

#### **Supply Current**

| Symbol                       | Parameter                      | Condition                                       | Min. | Тур. | Max. | Units |

|------------------------------|--------------------------------|-------------------------------------------------|------|------|------|-------|

| ispMACH 4                    | 032ZE                          | ,                                               |      |      |      |       |

| ICC <sup>1, 2, 3, 5, 6</sup> | Operating Power Supply Current | Vcc = 1.8V, T <sub>A</sub> = 25°C               | _    | 50   | _    | μΑ    |

|                              |                                | Vcc = 1.9V, T <sub>A</sub> = 0 to 70°C          | _    | 58   | _    | μΑ    |

|                              |                                | $Vcc = 1.9V, T_A = -40 \text{ to } 85^{\circ}C$ | _    | 60   | _    | μΑ    |

| ICC <sup>4, 5, 6</sup>       | Standby Power Supply Current   | Vcc = 1.8V, T <sub>A</sub> = 25°C               | —    | 10   | _    | μΑ    |

|                              |                                | $Vcc = 1.9V, T_A = 0 \text{ to } 70^{\circ}C$   | _    | 13   | 25   | μA    |

|                              |                                | $Vcc = 1.9V, T_A = -40 \text{ to } 85^{\circ}C$ | _    | 15   | 40   | μΑ    |

| ispMACH 4                    | 064ZE                          |                                                 |      |      |      |       |

| ICC <sup>1, 2, 3, 5, 6</sup> | Operating Power Supply Current | Vcc = 1.8V, T <sub>A</sub> = 25°C               | _    | 80   | _    | μΑ    |

|                              |                                | Vcc = 1.9V, T <sub>A</sub> = 0 to 70°C          | _    | 89   | _    | μΑ    |

|                              |                                | $Vcc = 1.9V, T_A = -40 \text{ to } 85^{\circ}C$ | _    | 92   | _    | μA    |

| ICC <sup>4, 5, 6</sup>       | Standby Power Supply Current   | Vcc = 1.8V, T <sub>A</sub> = 25°C               | —    | 11   | _    | μA    |

|                              |                                | $Vcc = 1.9V, T_A = 0 \text{ to } 70^{\circ}C$   | _    | 15   | 30   | μA    |

|                              |                                | $Vcc = 1.9V, T_A = -40 \text{ to } 85^{\circ}C$ | _    | 18   | 50   | μA    |

- 1. Frequency = 1.0 MHz.

- 2. Device configured with 16-bit counters.

- 3.  $I_{\text{CC}}$  varies with specific device configuration and operating frequency.

- 4.  $V_{CCO} = 3.6V$ ,  $V_{IN} = 0V$  or  $V_{CCO}$ , bus maintenance turned off.  $V_{IN}$  above  $V_{CCO}$  will add transient current above the specified standby  $I_{CC}$ .

- 5. Includes V<sub>CCO</sub> current without output loading.

- This operating supply current is with the internal oscillator disabled. Enabling the internal oscillator adds approximately 15µA typical current plus additional current from any logic it drives.

#### 圖2-供應電流規格資料

首先要考慮的因素之一,就是CPLD在整個系統功耗預算中所佔的比重。若比重較低,如5%至10%,那麼即便出現最差的狀況,對於整體耗電量造成的影響還是不大。若CPLD在耗電預算佔的比重達20%、甚至更高,就應考慮根據額定待機電流來進行設計,這個額定值會更接近產品型錄所載明的最高電流。你也應考量在設計案中,所用到的CPLD(與其他元件)數量。機板上的元件數量增加,總耗電量也更可能接近其正常額定電流。最後,還應考量一旦產品內的元件發生最差狀況的功耗時,可能產生的潛在影響為何?更高的功耗是否只會縮短運作壽命,或者甚至會引發火災?

若仔細檢視圖2所示的產品型錄,你可能會發現待機耗電也會隨著運作溫度以及 Vcc(電源的電壓)的波動而改變。這是因為CPLD的漏電流會隨著溫度上升而增加。事實上,讓設計的產品保持在較低的溫度有助於降低待機模式的耗電。由於漏電流與Vcc之間的關係更密切,因此,盡可能壓低電壓能產生更顯著的省電效果。 謹慎控管供電電壓對節省動態功耗的成效更為顯著,而此部分我們會在操作電源管理的章節中再做介紹。

### 控管偏置電流

到目前為止,你已藉由選擇適當的元件,有效地控制了CPLD的漏電流,下一步,就是運用設計技巧來削減偏置電流。管理這些偏置電流的技巧大致分成兩種:

- 1 確保CPLD的待機組態不會與各種技巧相衝突,包括下拉/上拉或其他相連元件 所使用的匯流排暫停機制。

- 2 機動開閉內部功能 (如共振器),只在有需要用到時才開啟。若搭配適合的 CPLD,就能有效地進一步提升設計產品的待機時間。

### 分析同步暫停機制

在許多設計中,嵌入式主處理器可透過自身的匯流排暫存器機制,以在一個匯流排 或I/O線路上維持想要的邏輯階層。要準備讓CPLD切換到待機模式,你要做的就 只是確保其主動匯流排管理功能已經關閉。在另一種應用中,位在匯流排其他位置 的主動上拉或下拉電路,也能在待機狀態時讓CPLD不需管理匯流排。

但CPLD不必做任何事,並不代表你也無事可做。你得花時間檢查,確保只有一個元件在驅動整條電路,因為光是一個針腳的邏輯衝突,就會導致待機模式的耗電量比整個晶片的10uA額定待機電流值高出2至15倍。

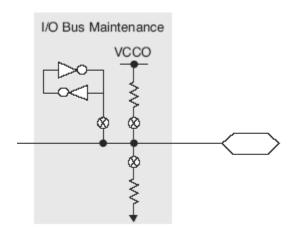

若沒有主匯流排暫停的機制時,就應運用大多數現代CPLD的上拉/下拉以及電位保持 (Bus Hold)功能。在同系列的大多數元件中,Lattice ispMACH 4000ZE CPLD

的I/O針腳都配備了可選擇的上拉與下拉暫存器,以在待機狀態下用來提供適當的 邏輯位準 (如圖3所示)。4000ZE系列元件還配備了一個省電Bus Keeper功能(亦稱 為Bus Hold),一個推力偏弱的主動驅動器電路,可設定在active one 或zero的狀態,其消耗之電力遠低於一個結構簡單的暫存器。*這裡要提醒的重點是*:儘管Bus Keeper功能可省下可觀的電力,但必須小心確保線路上只有作用中的元件,否則 就可能變成一個極大的電流吸收端(current sink)。

圖3-CPLD 匯流排的維護選項

# 管理動態功耗

設計師需要關心的動態功耗有兩種。第一種為運作狀態的功耗,這是在實際運作的 CPLD中各部分元件在運行時所需的電力。另一部分,則是針對CPLD中不需用到 的部分適時關閉其輸入端,若可能的話應儘可能關閉整個CPLD。

#### 精準的供電管理

雖然CPLD邏輯單元的許多部分可能會持續不斷地被使用,且在任何時段都無法被關閉,但你仍可儘可能使用較低的供電電壓,藉此省下一些電力。由於功耗是電壓平方的函數,因此讓開關式穩壓器的精準度提高1%的投資,就能把CPLD壓低到運作範圍的最低值,藉此節省可觀的電力。舉例而言,一個額定運作電壓為1.8伏

特的CPLD,當在1.65伏特的電壓運作時,功耗約可減少30%-這還沒算入在較低的Vcc時能減少漏電流的效益。

#### 選擇適合的邏輯閘控

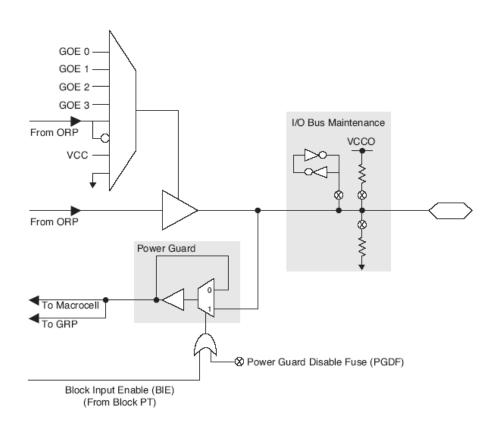

和同系列中多數CPLD一樣,ispMACH 4000ZE也有一項重要功能(Lattice稱之為 "Power Guard"),當連結的邏輯元件不會用到時,可用這個功能單獨關閉特定的輸入端。元件的Block Input Enable 線路可由主處理器、外部邏輯、或CPLD的其他部分來使用,讓選定的CPLD邏輯模塊不被設定時脈(如圖4所示)。例如,若CPLD的特定部分被當作一個解碼電路,主處理器可選擇僅在運作時才啟動它,其他時間則讓它保持在休眠狀態。

圖4 - Power Guard 保護電路

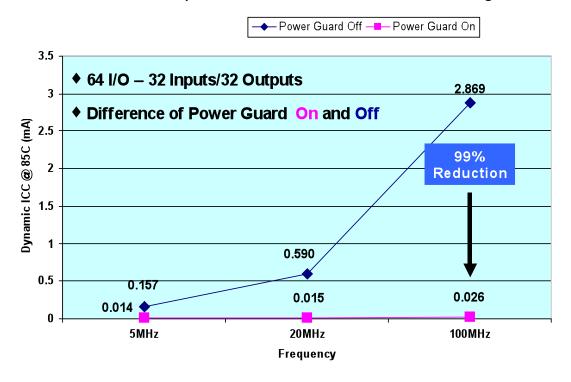

在適當的應用中,運用Lattice的Power Guard或其他技巧來關閉特定CPLD輸入針腳的時脈,可大幅降低動態功耗。若是邏輯訊號的時脈頻率超過30MHz,省電的效果更為顯著。圖5所示,為運用適當的邏輯時脈調整技巧而達到的省電效果。

#### ispMACH 4064ZE-TN100 Power Guard Advantage

圖5 - Power Guard 產牛的省電效果

# I/O設計協助降低功耗

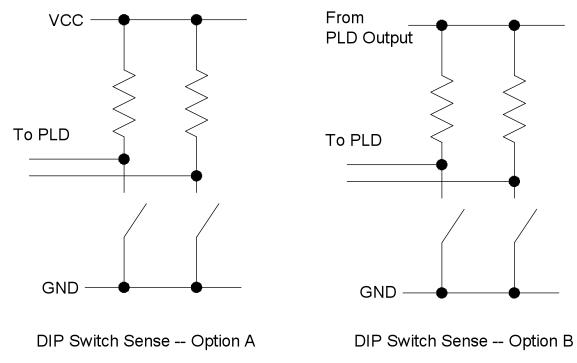

除了運用上述的技巧外,大多數設計案都會讓懂門道的工程師有額外的機會來省下一些電力 - 倘若他們願意仔細找出潛伏在設計案中許多吃電的部分。有個好例子是連結至CPLD輸入線路的開關與繼電器,上拉電阻能為它們提供一個感測電壓(如圖6所示)。運用CPLD的輸出端或一些其他控制線路,並僅在讀取時向感測線路導通電壓,當感測線路接地時,設計師將可藉此消除微小但持續的電流。

圖6-被動與主動供電的開關感測線路

# 其他技巧

- 把CPLD的JTAG介面針腳設定成浮動狀態,避免漏電流產生。

- 讓VCCO I/O電路維持在VCC之上。因為當電壓越接近時,消耗的電流就越多。

- 盡可能使用低迴轉率的I/O

# 結論

大多數採用CPLD的設計,或多或少都有一些黑暗的角落,其中潛伏著消耗大量電力的元件,默默耗損著電池的電力。幸運的是,如果小心運用本文中所提及的幾項重要原則,這些惱人的寄生蟲便能得以消弭:

- 在選擇**CPLD**與其他元件時,留意其寄生與動態功耗的額定值:這些數值會隨著 供電電壓、溫度、以及運作時脈等因素異動而改變。

- 小心判斷耗電規格中"最小"、"最大"、以及"正常"功耗數據會對設計案產生什麼樣的影響。

- 把CPLD的偏置電流壓到最低,確保其待機配置不會與其他相連元件相衝突, 並關閉所有不需要的內部功能。

- 僅針對CPLD中在運作時需要用到的部分啟動時脈,藉此控管動態功耗。 Lattice的Power Guard功能提供一個簡單的方法,能局部關閉特定輸入端的時 脈,若無法使用這種方法,也可使用其他技巧。

- 運用精準的電源控制方法,盡可能使用較低的供電電壓來驅動邏輯元件,藉此 進一步節省動態功耗。

- 檢查I/O連結,查看是否有任何不必要的上拉/下拉暫存器,關閉這些會耗電的 元件,或僅在有需要時才啟動這些元件。

若您在下一個設計案中小心運用這些工具,即使再隱密的吃電區塊,也將逃不出您的手掌心,您的產品也將能擁有更長的使用壽命。

###