# 在下一代无线网络中的FPGA

# 莱迪思半导体公司白皮书 2010年3月

Lattice Semiconductor 5555 Northeast Moore Ct. Hillsboro, Oregon 97124 USA Telephone: (503) 268-8000

www.latticesemi.com

## 引言

除了语音连接之外,数字蜂窝无线网络,如GSM和增强的GSM-EDGE现在可以提供更高的数据传输速率,理论上可达384kbps的限制。第三代移动网络,例如CDMA2000和WCDMA或UMTS(Universal Mobile Telecommunications Standards)和TD - SCDMA(中国标准)目前正在全球范围内部署。这些系统提供的服务,如视频流媒体,互联网浏览和使用称为高速分组接入(HSPA)的技术,在理论上他们可以提供下行速率高达14.4Mbps。

未来基础设施的发展,泛称为4G系统专注于以很低的成本提供更高的速度和更强的功能。在这一发展的前沿有两种技术: 3GPP LTE(3rd Generation Partnership Program,长期的演进)用于蜂窝/移动技术,通常简写为LTE,以及针对宽带无线接入的WiMAX。WiMAX已经赢得了早期进入市场的支持,但一些漫游和基站之间的切换问题依然存在。主要的蜂窝网络运营商支持LTE,将其作为未来的选择技术。这两个4G标准使用基于OFDM(正交频分调制)的通用空中接口标准,以及MIMO(Multiple Input Multiple Output)天线网络。这些先进的技术能够使信号从更高的噪声阈值中恢复出来,这对广泛的区域覆盖是基本的。

这些复杂且有时相互竞争的技术的实际结果是要求设备供应商能够支持多种空中接口标准,以及需要进行更复杂的基带处理。同时,这些系统必须能够提供灵活性,以适应发展规划,以便满足未来所需的增加带宽的要求。他们必须采用降低成本的方式,也为了满足人们对绿色环保要求的关注,即要求有更低的功率预算。

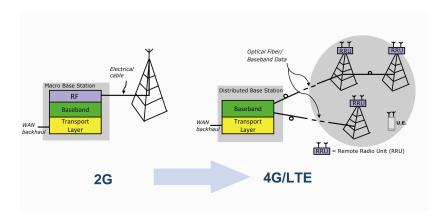

在第二代基站系统中,宏基站通常位于天线的下面,RF功率放大器紧靠基带和前置放大器。该主要系统的发展之一是用于分布式基站。在这些系统中,基带处理独立于射频功率部分。从架构上而言,从宏基站移动到分布式基站系统(图1),可以大大降低系统成本。在其他要求中,宏基站与天线的距离必须在150米之内,在电缆中会有50%的RF功率损失。设备更新和维护的成本很高。更好的解决办法是采用分布式"远程无线"网络,基带部分相距很远,有射频功率放大器的远程射频单元(RRU)可直接安装在天线杆上。通过光纤和标准接口如CPRI(通用公共无线接口)或OBSAI(开放式基站架构计划),RRU单元可以链接到基带。

图1-基站网络的演进

## 在无线基础设施中的FPGA

可编程技术的特点是能够跟随基站设计的演进,因为通常设计在规范被完全批准之前就开始了。基站需要大量的ASIC器件,FPGA通常被用作接口和"粘合"逻辑:能够快速修正设计错误,或支持专门的DSP器件的功能。随着无线标准的演变,基站的复杂性也相应大大增加。FPGA也在不断发生变化,其性能和逻辑密度大大增加。工程师开始将FPGA用于更复杂的功能,例如数字下变频(DDC)和数字上变频(DUC)。针对在基站设计中的这些功能,FPGA提供的灵活性意味着现在FPGA成为设计过程中的重要部件。现在LatticeECP3 FPGA拥有许多特性,如多个嵌入式DSP块,嵌入式存储器和SERDES功能。这些功能与无线系统的不断发展的需求紧密相关,因此他们成为设计工程师所选择的器件。FPGA的灵活性使工程师能够快速修改设计,而不必等待使用另一个ASIC而再重新设计电路板,从而加快了产品的上市时间。

#### 远程无线单元/头。

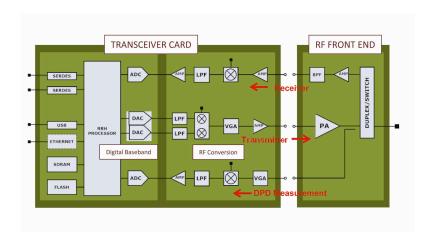

RRU功能包括一个具有数字信号处理功能的收发器卡、射频转换、包含功率放大器、双工器和LNA(Low Noise Amplifier低噪声放大器)的射频前端。收发器卡的设计往往是宽带的,在无线标准和工作频带之间有80-90%之间的元器件通用性。一个典型的单元如图 2所示。

图2-典型的收发器卡的设计

FPGA的可重构特性允许SDR(软件无线电)技术支持多种无线标准,例如WCDMA、WiMAX,以及通用基带的LTE。对于MIMO天线系统,该单元必须为每根天线提供一个发射器和接收器对。

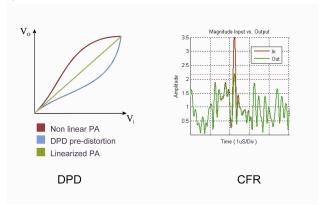

下一代网络将比目前部署的网络运行的频率高得多,通常会超过2 GHz。他们还需要提供更高的数据传输率。主要的RRU设计问题是功耗和射频功率放大器(Power Amplifier功率放大器)的成本。大信号峰值对平均功率比(PAPR)要求功率放大器传送少见的更大功率。虽然这种情况很少发生,设计必须实现这个功能,这将转化为更高的成本。射频晶体管在大功率时呈现了非线性,造成信号失真和带外发射。大信号峰值对平均功率比和在4G系统中的非线性这二者的共同影响可能导致功率放大器将只运行在其总输出功率的20-30%,整个效率只有10-15%。而与之相比,GSM功率放大器的运行可达到100%利用率和高达70%效率。对这个问题的解决办法是在最后的功率放大器前预先处理这个信号,这种方式最终导致放大的射频信号有最佳的性能。在这一过程中可以使用两种方法;振幅因子缩小(CFR)和数字预失真(DPD)。

波峰因子缩小工作原理是智能地限制功率放大器输入的最大波形振幅,因此产生峰值输出功率。这有效地降低了这个信号的PAPR,同时保持所需信号的精确度和频谱特性。在低功耗或微型基站情况下,如WiMAX或Picocell,可以使用它而无需DPD。

另一方面,DPD能够使功率放大器线性化,通过应用一种使输入信号失真的方式,这种方式考虑了功率放大器的传输特性,因此使任何信号失真无效,这是功率放大器的特性所导致的。在射频输出功率大于1-2瓦的大功率系统中,它通常与CFR相结合。这些技术的

## 效果如图3所示。

图3 DPD和CFR技术的效果

在RRU中使用CFR 和 DPD技术可以让系统工程师使用比采用其他技术更低成本的功率放大器。这两种方法都需要大量的DSP处理功能,以实现行必要的算法。最重要的是,他们还需要某种具有一定的可适性,因为他们需要适应功率放大器传输特性的任何变化,这可能发生在温度和时间变化的情况。

RRU内远程无线处理器的合并是对这个问题的解决方案之一。传统上ASIC被广泛用于蜂窝基站的设计,但是他们的设计周期长,高固定成本和不灵活,他们不适合仍在不断发展的市场。对这个问题,分立的DSP处理器似乎是另一个解决方案,但分析表明,在多种标准的基站实现方面,它们也有局限性。另一方面,具有嵌入式DSP单元、SerDes功能和软处理器的FPGA在一个可重构的芯片中提供所有的功能。这个器件就是莱迪思半导体公司的ECP3。对任何带有SERDES功能的FPGA器件而言,这个FPGA具有业界最低的功耗和价格。该系列产品提供遵守XAUI抖动标准的多协议3.2G SERDES、DDR1/2/3存储器接口、功能强大的DSP功能和高密度的片上存储器,与带有SERDES功能的FPGA相比,所有这些功能只有竞争产品的一半功耗和一半价格。

而选择FPGA时需要认真考虑,以满足系统的物理和性能参数要求,获得实现RRU的关键功能的IP核对整个系统的解决方案而言是至关重要的。作为IP合作伙伴计划的一部分,莱迪思公司与拥有丰富蜂窝无线系统经验的Affarii公司一起致力于该项工作。

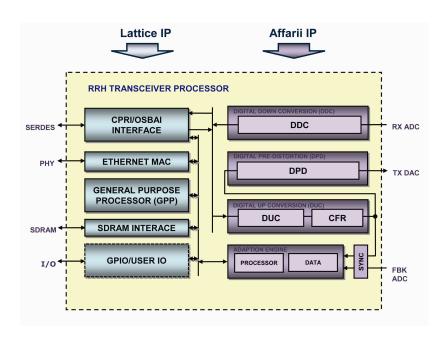

LatticeECP3FPGA 与Affarii的IP结合在一起提供了一个灵活的平台,可以在FPGA架构中组合构建RRU所需的所有IP模块。

图4 RRU处理器

针对发送和接收,RRU处理器的功能是多路复用和调制这个信号数据到射频载波。图4展示了莱迪思的IP和Affarii提供的IP。这些块已用不同的颜色加以区别。

针对不同的具体应用,可以对CFR配置进行优化。最高载波配置的模拟可以决定精确的参数。在设计工具和文档中提供了标准的系统配置。对于用户自己的应用,用户还可以创建自定义的配置,使用IP模型和有IP核的仿真环境。将CFR IP放置在LFE-70E FPGA中进行布局和布线,表1a展示了资源利用率。

通过针对功率放大器的特性来确定DPD工作的配置是最好的方法。DPD核本身支持诊断接口,以提供现场或测试源的数据分析。使用这个工具,可以实现放大器的非线性复杂特性,因此可以针对DPD决定最好的配置。因为它测量实时的放大器参数,这个过程还可以突出显示在设计放大器时所需作出的改进。表1b展示了将DPD放置在Lattice LFE-70EP中进行布局和布线所需的资源。

| CFR Place & Routed: LFE3-70E-FPBGA484-8 |      |     |        |     |      |     |  |  |

|-----------------------------------------|------|-----|--------|-----|------|-----|--|--|

| STANDARD                                | MODE | СН  | SLICES | EBR | MULT | MHz |  |  |

| LTE, WIMAX                              | SYM  | 1-2 | 8K     | 22  | 22   | 213 |  |  |

| LTE, WCDMA                              | ASYM | 1-4 | 14K    | 48  | 69   | 209 |  |  |

表1a

| DPD Place & Routed: LFE3-70E-FPBGA484-8 |     |     |        |     |      |     |  |  |  |

|-----------------------------------------|-----|-----|--------|-----|------|-----|--|--|--|

| COMPONENT                               | DPD | EQU | SLICES | EBR | MULT | MHz |  |  |  |

| PREDISTORTION<br>FILTER                 | 4   | 9   | 4K     | 5   | 39   | 182 |  |  |  |

表1b

该Affarii IP不仅包括了CFR和DPD功能,而且还有DUC,DDC和匹配引擎的功能,这是基站结构的重要组成部分。

由莱迪思提供的主要IP块是CPRI和OBSAI: 这些是使用FPGA中带有的嵌入式SERDES 功能的高速接口。这些接口连接远程基带至RRU。以太网MAC提供监测和控制系统的功能。设计师也可以选择使用LatticeMico32软处理器,用于RRH通用处理和控制,以便减少元件的数量和节省成本。用先进的存储器接口和通用I/O(GPIO)接口可以完成该系统。

# 总结

FPGA现在已发展成为高度集成的器件,可以包括嵌入式ASIC类型的功能,提供增强的接口功能。软微处理器功能加上DSP处理器和嵌入式存储器意味着在基站设计中使用的 FPGA将用一个可重构芯片提供功能核。可编程器件提供的优点将使产品能够更快地进入市场,灵活地适应新的和不断发展的具有成本效益的标准。

###