# 莱迪思 SERDES 的电气建议

2012 年 9 月 技术说明 TN1114

## 引言

LatticeECP3、LatticeECP2 / M 和 LatticeSC / M SERDES 集成了高速差分电流模式逻辑 (CML)的输入和输出缓冲器,在开关速度方面拥有明显的优势,同时提供更好的抗噪声能力并且节省功耗。电流模式设计的其它优点包括减少电压摆幅,因为电源电流是恒定的,从而大大抑制了电源的噪声。

CML 差分接收器和驱动器整合了各种可编程特性,并能接口至其他的 CML 和非 CML 逻辑信号。片外信号接口设计和特点是本文的重点。讨论了有 LVDS 和 LVPECL 的外部高速器件,以及由于高数据速率所需的器件之间的传输线互连的详细接口要求。还讨论了有关印刷电路板的实际问题。如需了解更详细的有关印刷电路板的建议,请参阅TN1033 一 高速印刷电路板的设计考虑。本文中采用了额定电阻和电容值,在每个应用中最佳值会有所不同。提供的带有接口实例的 HSPICE 模型便于用户在实际应用中进行调整。

## CML 缓冲器概述

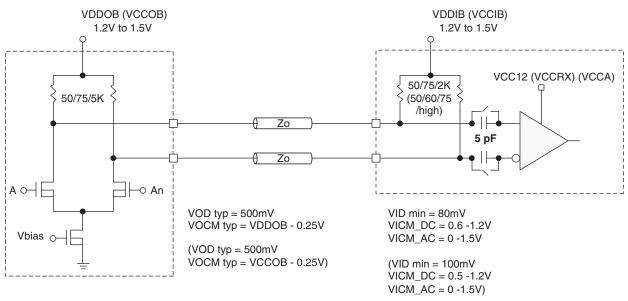

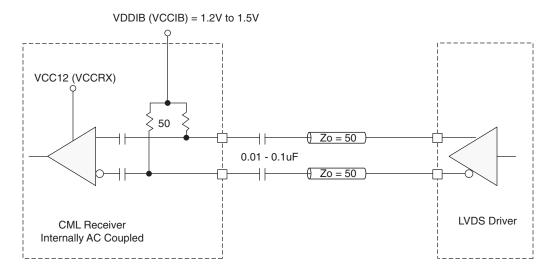

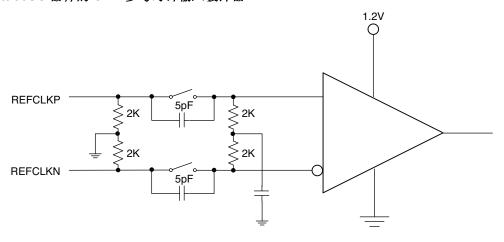

CML 缓冲器被用作 SERDES PCS 的通用接口。提供内部的输入和输出终端匹配,以简化电路板级的接口,CML 接收器里拥有交流耦合电容。串行输入和输出缓冲器的简化原理图如图 1 所示。终端匹配电阻和交流耦合电容内部接至缓冲器。

#### 图 1. LatticeECP3、LatticeECP2 / M 和 LatticeSC / M 的 CML 输入和输出缓冲结构

Note: Signal or parameter names and values in parenthesis are for Lattice ECP2M and Lattice ECP3.

#### SERDES 的电源

通常莱迪思基于 SERDES 的 FPGA 器件有许多相似之处。但也有一些差别需要加以注意和理解。理解 LatticeSC、LatticeECP2M 和 LatticeECP3 器件之间的电源定义时,这是非常重要。这些差异列于表 1。

#### 表 1. SERDES 的电源

| LatticeSC SERDES<br>电源 | LatticeECP2M SERDES<br>电源 | LatticeECP3<br>电源   | 额定值            | 说明              | 电源容限  |

|------------------------|---------------------------|---------------------|----------------|-----------------|-------|

| VDDIB[0-3]             | VCCIB[0-3]                | VCCIB[0:3]          | 1.2V 至 1.5V    | CML 输入终端电源      | +/-5% |

| VDDOB[0-3]             | VCCOB[0-3]                | VCCOB[0:3]          | 1.2V 至 1.5V    | CML 输出终端电源      | +/-5% |

| VDDAX25                | VCCAUX33                  | VCCAUX <sup>2</sup> | 2.5V/3.3V/3.3V | CML I/O 控制逻辑电源  | +/-5% |

| VCC12 <sup>1</sup>     | VCCP/VCCRX/VCCTX          | VCCA                | 1.2V           | SERDES/PLL 模拟电源 | +/-5% |

- 1. 内部 1.2V 的电源电压用于配置逻辑和 FPGA 的 PLL、SERDES PLL 电源电压和 SERDES 模拟电源电压。

- 2. 对于 LatticeECP3, 这个电压与 FPGA 的 VCCAUX 共享。

对每个 CML 输入和输出缓冲器,SERDES 设计提供了各自独立的最后级 Rx 和 Tx 电源节点。对于 LatticeSC 标示为 VDDIB 和 VDDOB;对于 LatticeECP2M 和 LatticeECP3 标示为 VCCIB 和 VCCOB,这些是相同的。这使得接收器输入终端匹配电阻(50 欧姆、75 欧姆、2K 欧姆)和发送器输出终端匹配电阻(50 欧姆、75 欧姆、5k 欧姆)偏置于不同的电平,内部核电压 VCC 电压是独立的。根据各种设计要求, Rx 终端匹配电阻 (电阻连接到 VCCIB)值可以变化。

对于 SERDES 的模拟电路模块,莱迪思器件使用了几个电源。不论在应用中是否使用该通道,所有的模拟电源引脚必须连接到一个电压源上。未使用的通道可以内部断电,以便节省功耗。在印刷电路板上应隔离模拟电压,提供干静,无噪声的电源。对于 LatticeSCM 器件,这个电源被定义为 VCC12,为 SERDES 块内提供模拟电压。器件内的 VCC12 给模拟电路供电,由 SERDES 和 PLL 共享。对于 LatticeECP2M,这些电源是 VCCP,VCCRX 和 VCCTX,应该连接在一起,象 VCC12 一样处理。LatticeECP3 还包括电压 VCCA,也类似于 VCC12,应该做同样的处理。

设计人员往往忽略一个非常严格的要求,隔离由数字元件产生的噪声。对 SERDES 器件的敏感的模拟部分必须提供一个低噪声电源。由于电源电压变化产生的噪声的变化会耦合到芯片的模拟部分,可能会在器件的敏感级产生不希望的电压波动。

有好几个电源与器件中的 SERDES/PCS 部分有关。根据设计需要,要对这些电压进行处理。如前所述,在 1.2V 的印刷电路板的电源上,模拟电源需要与其他的噪声相隔离。除了 VDDIB(VCCIB)和 VDDOB(VCCOB)引脚,不管设计的情况如何,所有专用 SERDES 的电压引脚必须连接。VDDIB(VCCIB)和 VDDOB(VCCOB)用于向输入和输出终端匹配供电,用于匹配传输线。对于在设计中所使用的通道,这些电源需要连接。在只使用 Rx 部分的情况下,无论 Tx 部分是否使用,建议将相关的 VDDOB(VCCOB)连接到相应的电源。这种方法为通道隔绝了噪声。类似地,如果仅 Tx 部分使用,相应的 VDDIB(VCCIB)必须连接。同样,在设计中未使用特别通道,HDIN 和HDOUT 引脚可以不连接。

在印刷电路板上电源分配不能完全旁路的实例中,设计者可能想使用几个不同的有源器件,例如电压调节器,以作为对这些电源的去耦步骤。通过一个单独的电感或"扼流圈"来为各级提供直流电源,也能有效地旁路到地,这样就能不使用有源元件达到相同的结果。在这些无源滤波器网络方案中,对各级之间的任何出错信号或噪声,扼流圈提供了一个高阻抗路径,同时对直流电源提供一个非常低的阻抗路径。这一技术适用于对 RX 和 TX 终端电源(VCCIB/VDDIB/VCCOB/VDDOB)供电。

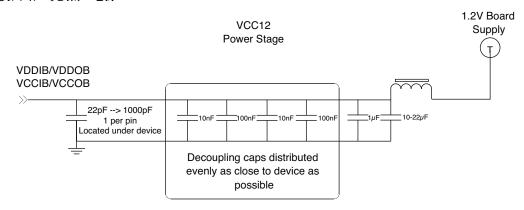

图 2 展示了将 SERDES 模拟电源与源于印刷电路板数字噪声相隔离的方法。这种技术应该用于电路板上的 VDDIB / VDDOB (对 LatticeSC), VCCP / VCCIB / VCCOB (对 LatticeECP2M 和 LatticeECP3) 电源。

#### 图 2. 无源滤波网络"无噪声电源"

Note: The use of Passive-Filter Networks is not recommended for low-impedance power supplies such as VCC Core.

- · 高 "Q " 最小电感去耦合电容

- 表面贴装或陶瓷电容片是最好的。并行使用几种容量的电容,如 1ufd, 0.1ufd, 0.01ufd 等, 其原因是与其电感相关的每个电容将有自己的串联谐振频率。因此,最好是有一个宽范围的电容值,在有效频率范围内提供全面的低电源阻抗。

- 使用高 "Q" 低 "R" 铁氧体磁环

- 铁氧体不利的一面是电感随电流或通量的变化而变化。在大电流情况下,它会处于饱和状态。但是,选择正确的电感器时,理解交流和直流电流的要求是很重要的。可选择 Murata 的 BLM41PG471SN1L 磁环。

同时应该探讨电源分配系统的其他选择,以便了解电源的噪声和电压纹波的来源。使用前面提到的无源滤波器技术是一个良好的开端,采用后置滤波器以处理电源所产生的纹波。该滤波器器必须充分衰减主开关电源的低频谐波,因此理解后置滤波器需要什么截止频率是很重要的事。具体的建议是构建一个 LC 无源网络,截止频率低于主频率 10 倍程。通常情况下,可以很容易衰减电源产生的高频噪声。通常用额外的陶瓷去耦合电容器来实现,放置在后置滤波器之后,如图 2 所示。

在莱迪思 FPGA 系统中,使用线性稳压器和开关稳压器有各自的优点和缺点。根据系统的要求,任何一个都可能是合适的选择。输入电压低于或远远大于所需的输出时,要求多个输出时,必须保持低功耗时,开关稳压器是一种较好的选择。开关稳压器比低压差线性稳压器(LDO)更有效是没有争议的。开关稳压器有 90%的效率,而 LDO 只有 36%。但开关稳压器不一定能满足所有的设计关键需求。开关稳压器有以下好处:

- 高效率 (降低了电源的要求和散热的要求)

- 能够处理更高的功率密度

- 单个或多个输出电压,大于或小于输入电压。

它们有以下缺点:

- 更大的输出噪声/纹波,尤其是在开关频率

- 更慢的瞬态恢复时间

开关稳压器非常适合给 FPGA 核及 I/O 电源供电,在进行电路板电源设计时,大功率要求是一个要素。高效率减少热量和线性稳压器所表现的功耗问题。然而,对使用敏感的模拟电源,由开关稳压器产生的有限纹波是不可取的。使用后置的电源滤波器网络可以衰减不要的纹波。通常,输出的附加噪声是处于开关频率。如果这个频率是低于SERDES 或 PLL 的带宽,这将直接影响相关元件的抖动。否则,它将被滤除。对于 SERDES 的连接,被传送到的接收器也将滤除开关稳压器所产生的低频抖动。

一般来说,当输入电压比输出高几伏,但不接近调节器的压降电压时,以及当负载电流小于 3A 时,线性稳压器是一个更好的选择。线性稳压器有以下好处:

- 简单和小电路板的应用

- 低输出纹波电压

- 出色的线路和负载调节

- 对负载或线路变化响应时间快

- 低电磁干扰 (EMI)

它们有以下缺点:

- 低效率,特别是高输入电压

- 如果需要散热的话,要求有大的空间

这种类型的调节是专门为针对 SERDES 器件的 PLL 和 SERDES 使用的无噪声模拟电源而设计的。这些稳压器有更好的噪声性能和更快的瞬态响应。它们提供了良好的噪声抑制,不产生波纹。在为 FPGA 模拟电路提供低功耗的环境下工作良好。使用线性稳压器构建的无噪声电源满足了 FPGA 模拟部分所需的电源要求。**莱迪思强烈推荐使用线性稳压器为模拟 SERDES 供电。**

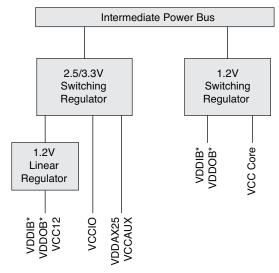

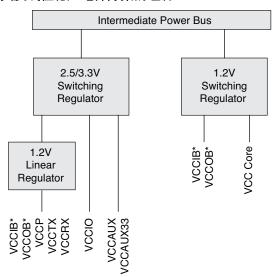

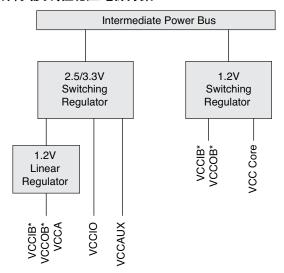

#### 图 3. 针对 Lattice SC、开关及线性稳压电源方案的组合

\*VDDIB and VDDOB should be passively filtered from either 1.2V supply.

#### 图 4. 针对 Lattice ECP2M、开关及线性稳压电源方案的组合

\*VCCIB and VCCOB should be passively filtered from either 1.2V supply.

#### 图 5. 针对 LatticeECP3,组合开关及线性稳压电源方案

\*VCCIB and VCCOB should be passively filtered from either 1.2V supply.

线性稳压器与开关稳压器的结合使用是一种减少电路板漏电流的方法。这个例子如图 3 所示。在这个设计中,开关稳压器提供了正确的电平,同时用线性稳压器滤除了开关噪声。请注意,需要正确的电源去耦和滤波。当它们驱动所设计的负载时,开关稳压器是最有效的。但是,输出电压的负载不是过重的情况下,需要保持开关稳压器开关所需的电流变得更加困难。在这些情况下,线性稳压器更加有效。将不同稳压器结合在一起是很有用的,有利于满足需要多个电源分配的高性能 FPGA 设计的要求。这一策略将同时满足 FPGA 系统的功率和性能要求。

## 通用 FPGA 的建议

若要正确使用嵌入式 SERDES 单元的话,对低噪声模拟电源网络是有严格要求的。由于电源电压的变化,噪声可以耦合到器件的其它非 SERDES 的模拟部分。这对理解基于 FPGA 内部结构的锁相环是很重要。这些 PLL 也应遵循 所提及的为 SERDES 电源所提供的无噪声电源的各项建议。

#### 表 2. 每个器件的 PLL 电源

| 器件           | FPGA PLL<br>电源 | 静态电源<br>电压 (标称值) |

|--------------|----------------|------------------|

| LatticeSC    | VCC12          | 1.2V             |

| LatticeECP2M | VCCPLL_[L:R]   | 1.2V             |

| LatticeECP3  | VCCPLL_[L:R]   | 3.3V             |

## 印刷电路板设计注意事项

许多现有的文件提供了指导意见,以避免基于 SERDES 和高速 I/O 设计的印刷电路板设计所易犯的错误。但仍然有几个基本问题通常会被误解或忽视。FPGA 的同时开关输出(SSO)的相互作用会产生许多系统级的问题,导致整个 SERDES 性能的退化。

莱迪思 FPGA 的 I/O 能构建许多复杂的系统。这些丰富而灵活的 FPGA I/O 包括许多速度和信号接口功能,如驱动器强度和终端匹配选项。SSO 成为噪声源是由于多个 I/O 引脚在同时开关。这些变化电流无意中感应了电压,影响到器件的其他敏感级。LatticeSC 器件中采用了许多创新方法来克服特定器件和封装对 SSO 和封装内串扰的敏感性。大多数情况下,通过最小化返回路径的总电感可以纠正这种情况,类似于已在莱迪思封装设计所做的那样。设计印刷电路板时需要小心地使用各种技术,尽可能减少与印刷电路板有关的串扰和由 SSO 导致的系统性能衰退。

与印刷电路板相关的 SERDES 串扰的主要原因与 FPGA 的输出有关,这些输出与敏感的 SERDES 电源相毗邻。在电路板布局时需要谨慎对待这些电源,以确保对 FPGA 输出产生的开关噪声进行抑制。已经提供了一些准则,要对这些敏感的电源构建经滤波的无噪声电源,但仍需要合理的印刷电路板布局,确保噪声不会渗透到这些模拟电源。虽然器件的封装中已经减少了耦合,几乎没有交叉串扰,印刷电路板 BGA 区域的过孔可能会导致大量的噪声,它们来自与相邻 SERDES 数据的 I/O 引脚、参考时钟、电源引脚以及其它关键的 I/O,如时钟信号引脚。

许多印刷电路板设计包括会引起 FPGA 的 I/O 至模拟电源引脚的交叉耦合的相邻布局。由过孔至过孔的耦合而产生的噪声可能会导致噪声影响模拟电源。噪声产生的串扰主要是源于 SSO 引脚,可能影响电源和绕过印刷电路板上的电源滤波。印刷电路板上的耦合噪声可能会导致 SERDES 的性能显著降低。启用 SERDES 的幅度增强模式 (amplitude boost mode)通常会改善SERDES的Rx和Tx部分的抗噪声能力,特别是在速率高于2.7Gbps的情况下。

系统设计人员可以通过实现差分信号传输标准来缓和这个问题,FPGA 发送和接收信号时采用差分信号而不是用单端缓冲器。如果必须使用单端信号时,当靠近模拟电源时,印刷电路板设计必须注重过孔和信号的放置,避免单端总线的布线接近高速 SERDES 信道。对于静态控制信号或低驱动强度的信号,慢摆率信号和有限的电容负载的信号(终端匹配信号也改进了这种情况),更好的做法是使用更接近 SERDES 数据、参考时钟的 I/O 引脚,和模拟信号电源引脚。对每一种 LatticeSC 封装,如果可能的话,为此目的所建议避免的引脚展示在表 3 之中。对于 LatticeECP2/M 器件,请参阅 TN1159,LatticeECP2/M 引脚分配的建议。TN1189,LatticeECP3 硬件检查列表有针对 LatticeECP3 器件相似的建议。

| <b>寿</b> ? | LatticaSC | 印刷电路板产生串扰的I/O | 21脚   |

|------------|-----------|---------------|-------|

| X 3.       | LatticeSC | 印刷电路拟广生单切的I/U | 51100 |

| 器件              | 封装         | 封装类型      | 产生串扰的 I/O 引脚 <sup>1</sup>                                                 |

|-----------------|------------|-----------|---------------------------------------------------------------------------|

| SC15            | 256-fpBGA  | Wire-bond | E7                                                                        |

| SC15/SC25       | 900-fpBGA  | Wire-bond | F22 <sup>2</sup>                                                          |

| SC25/SC40       | 1020-fpBGA | Flip Chip | D2, E2, F2, D31, E31, F31                                                 |

| SC40/SC80/SC115 | 1152-fpBGA | Flip Chip | D2, D33, F14, F21, G14, G21,H13, H14, H21, H22                            |

| SC80/SC115      | 1704-fpBGA | Flip Chip | F27, G1, G2, G3, J17, J18, G40, G41, G42, K18, M9, N9, N10, N33, N34, M34 |

- 1. 对模拟电源, I/O 引脚是潜在的印刷电路板耦合噪声源,应遵循建议。

- 2. F22 是一种双功能引脚。当使用 SPI 闪存, F22 用作 SPI 闪存片选的源,不应该连接到"软地"。

最好的情况是用"软地"驱动这些信号。连接激活的输出缓冲器和驱动一个低电平信号构建有效的"软地"。这个引脚应该连接到印刷电路板的接地平面。这个连接可作为返回路经,帮助构建更多的抗噪声性能。列出了在电路板上可能会影响模拟电源的引脚,以及毗邻高速 SERDES 数据引脚的引脚,这些引脚可能在印刷电路板上产生耦合。其他建议如下:

- 不要使用 SERDES 的电源连接作为走线。最好使用平面或非常宽的总线结构,并且与高速信号不在相邻层,用相邻接地层屏蔽他们。

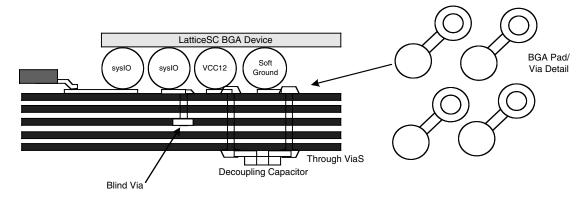

- 对于连接到 I/O 而言,盲孔优于通孔。这限制了过孔之间耦合的量。如果需要通孔,直接放置高频去耦电容在器件的下方,邻近 VCC12 电源的过孔。

- 在单端 I/O 和模拟电源之间保持最大的距离。在电路板上很靠近的情况下,印刷电路板叠层中始终保持模拟电源和单端走线垂直分离是最佳的。

#### 图 6. 针对 LatticeSC 的印刷电路板过孔层叠的详细情况

在图 6 中, I/O 信号路径和通过 VCC12 过孔之间区域的互感造成了耦合。盲孔和短过孔能使电容耦合效应最小化。遵循使这种影响最小的建议减少了耦合。不同封装中,靠近 VCC12 引脚的 I/O 引脚是不同的,封装的变化也影响抗噪声性能。有关这些位置的问题是由于远离引脚,或走线从器件引脚引出所采取的方法。确定远离器件的 BGA 区域的最佳走线是至关重要的,能使电路板上的耦合噪声影响最小。

#### SERDES 电源印刷电路板布线的最佳实践方法

- 如果可能,不要使用直接邻近模拟电源引脚的特殊 I/O。

- 当走线从器件引出时, 布线也应远离模拟电源过孔。

- 对于屏蔽来自模拟电源引脚连接的任何走线,这是最实际的方法。可以将电源和地平面置于模拟电源布线的上层和下层(接地面首选),以及在同层采用地屏蔽布线。

- 小心相同层的屏蔽,不要造成边缘耦合的问题。通常需要有 3W 的间距,以防止边缘耦合。

- 考虑保留无噪声的 SERDES 电源连接在尽可能与接近器件那一边的电源层上,通过接地层屏蔽。

- 高速 I/O 信号应避开,不靠近模拟电源的信号层。

- 应当在完成所有 SERDES 和模拟电源布线之后,再对高速 I / O 信号布线。如果无噪声电源的过孔都是盲孔,这种限制可以放宽,只要无噪声的电源平面尽可能接近电路板的器件一边。

#### 对 LatticeSC 特别要考虑降低 Tx 抖动,提升抖动容差

对于 wire-bond 封装,在毗邻 SERDES 通道的 I/O bank 中,在任何速度的情况下,限制单端输出同时开关的数量是一个好的方法。对于 256-fpBGA, 这是 I/O Bank #1; 对于 900-fpBGA 封装, 这些为 I/OBank #1、#2、#7。 SERDES 速率增加时,应当优先考虑这个方法。

wire-bond 封装中,SERDES 速度超过 3.2Gbps 时,Bank #1 中应该限制单端输出至配置信号(针对 900-fpBGA,包括最多 8 位 MPI 的接口连接)。对于 Bank #2 和 #7, 900-fpBGA 中单端输出数目应限制为 8 或更少。

对于 256-fpBGA 封装,将 Bank #1 用作:

- 差分 I / O 或静态配置和控制信号

- 单端输入

- 如有必要,可使用单端输出信号,但应该限制驱动电流为 4mA,并且使能 slewlim 模式。

对于 900-fpBGA 封装,将 Bank #1, #2 和 #7 用于:

- MPI 的引脚 (仅 8 位)

- 差分 I/O 或静态配置和控制信号

- 单端输入

- 如有必要,可使用单端输出信号,但应该限制驱动电流为 4mA,并且使能 slewlim 模式。

在倒装芯片封装中限制单端输出的数目并不那么重要。然而,限制输出的数量、降低驱动强度,使能摆率限制模式和减少 Bank #1, #2 和 #7 中的容性负载将对改善 SERDES 的性能有较小的影响。 SERDES 速度大于 3.2Gbps 时这种影响明显。

## SERDES 的外部接口

用户理解高速串行 SERDES I/O 的接口参数非常重要。对于成功整合至一个系统,需要正确解释参数。信号互连的性能,可靠性和完整性是与这些特点和变化限制紧密相关的。本节试图总结和讨论关键的串行缓冲接口参数。正确指定缓冲器 I/O 是一个复杂的过程。采用的方法包括进行大量的 SPICE 仿真和实验室测量。

本节所阐述的所有互联电路应该使用 50 欧姆传输线的匹配长度对。每个都应提供线的特性阻抗终端匹配,提供最大的信号带宽。对电路板和背板应用,行业标准 50 欧姆提供最大的兼容性,很适合目前的印刷电路板互连技术。这也与 100 欧姆平衡传输线接口一致,这正在成为流行的高带宽屏蔽双绞线连接。然而,为便于集成到 75 欧姆阻抗特性系统,如视频应用,对莱迪思的 SERDES 器件进行了优化,能直接端接 50 欧姆和 75 欧姆应用。

#### DC 耦合

对 SERDES 高速串行缓冲器进行了优化,能够与外部至其他类似的缓冲器进行接口。对于一些接口,莱迪思 SERDES 缓冲器的直接互连不需要在印刷电路板上有外部器件或元件。例如在同一电路板或系统板中,接口有同样 的地电位,直流耦合直接连接,无需任何耦合电容。直流耦合的优点包括简化电路板设计和没有直流漂移的问题。在 所有的数据编码流中,这也是有用的,包括 SONET 和 NRZ 数据应用。在需要宽带的系统或使用直流非平衡编码技术的场合,可以利用直流耦合的优点。

#### 交流耦合

在一些高速应用中,首选交流耦合有各种原因。莱迪思 CML 接收器集成了交流耦合电容。当互连不同的物理层时,交流耦合用来改变共模电平。电容去除了信号的直流分量(共模电压),而通过交流分量或电压变化。在图 1 中接至 RxTerm 的电阻代表了内部偏置结构,用于在交流耦合电容线端设置共模电压。偏置结构是接收器内部偏置的一部分,或是外部电阻上拉和 / 或下拉网络。互连至其它厂商的非 CML 缓冲器是可能的,但需要增加一些无源元件。在高速串行数据传输时,交流耦合产生基线漂移,因为它是非直流平衡。ANSI 光纤通道的 8B/10B 编码数据是直流平衡信号的实例。

针对交流耦合,添加外部电容(Cext)需要注意一些问题。设计者应选择系统所要求的电容。使与交流耦合网络低频截止频率有关的模式决定的抖动最小化是很重要的。当含有长字符串的相同 1 或相同 0 的 NRZ 数据加到这一高通滤波器时,会发生电压跌落,造成在低频率有模式决定的抖动(PDJ)。

使用片外电容(Cext)时,可以使用内部交流耦合或直流耦合模式。对于交流耦合模式,当以串联方式连接 Cext 至内部交流耦合 5pF 电容(典型值)时,建议 Cext>100 倍 +/- 5% 的容差。必需有片外 AC 耦合时,推荐的电容值如表 4 所示。

#### 表 4. 片外交流耦合电容器

| 类型            | Min. | Max. | 单位 |

|---------------|------|------|----|

| 8b/10b (XAUI) | 4.7  | _    | nF |

| SONET         | 22   | _    | nF |

| PCI-Express   | 75   | 200  | nF |

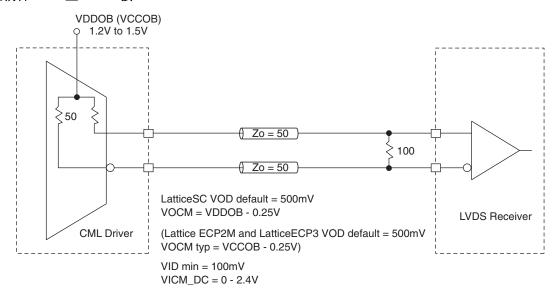

#### LVDS 的器件接口

象 CML 一样的 LVDS 是为低电压差分信号点对点传输而设计的。许多商业的 LVDS 器件提供内部的 100 欧姆输入终端匹配。它们通常用于 100 欧姆特性阻抗传输线连接。规定了标准 LVDS 约 3 mA 信号电流,转换为约 600 mVp-p(差分)额定电压信号。低功耗 LVDS 提供了约 2 mA 信号电流。LVDS 输入和输出参数如表 5 所示,如 LVDS 标准中的规范。

#### 表 5. LVDS 的规范

| 符号    | 参数        | 条件                      | Min  | Max  | 单位   |

|-------|-----------|-------------------------|------|------|------|

| 驱动器规范 |           | <u> </u>                | •    |      | •    |

| VOH   | 输出电压高电平   | Rload (diff) = 100 ohms | _    | 1475 | mV   |

| VOL   | 输出电压低电平   | Rload (diff) = 100 ohms | 925  | _    | mV   |

| VOD   | 输出差分电压    | Rload (diff) = 100 ohms | 250  | 400  | mV   |

| Ro    | 输出阻抗,单端   | Vcm = 1.0V to 1.4V      | 40   | 140  | Ohms |

| 接收器规范 |           | ·                       |      |      |      |

| Vi    | 输入电压范围    |                         | 0    | 2400 | mV   |

| Vidth | 输入差分阈值    |                         | -100 | +100 | mV   |

| Vhyst | 输入差分迟滞    |                         | 25   | _    | mV   |

| Rin   | 接收器差分输入阻抗 |                         | 90   | 110  | Ohms |

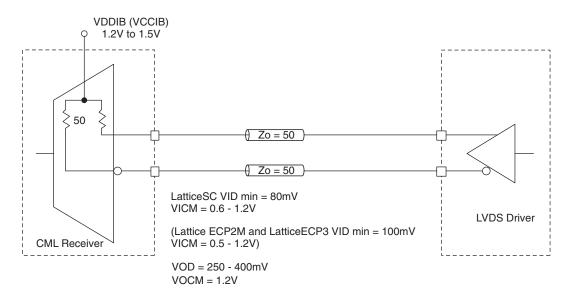

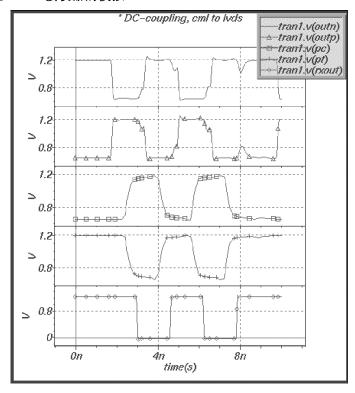

在常见的 LVDS 接收器里,通常在 P 和 N 输入端之间需要有 100 欧姆的内部或外部的输入差分终端匹配电阻。相对于地而言,这个终端电阻通常是浮动的。在 SERDES CML 接收器中,差分输入终端电阻有中心抽头,交流耦合至地,或悬空。VDDIB 也可以连接到电源,相当于输出缓冲器正常工作所需的共模电平。在常见的 LVDS 至 CML 应用中,许多应用中可以使用一个简单的直接接口。在此应用中,莱迪思 CML 输出驱动器和输入接收器都在内部端接50 欧姆。图 7 说明了与莱迪思 CML 缓冲器与商业 LVDS 输入和输出缓冲器之间所推荐的接口。由于利用了内部 CML的特性,此接口无需外部元件。接口的模拟结果绘制在图 8 中。

#### 图7. 直流耦合 CML 至 LVDS 接口

#### 图 8. 莱迪思 CML 驱动器至 LVDS 接收器的模拟

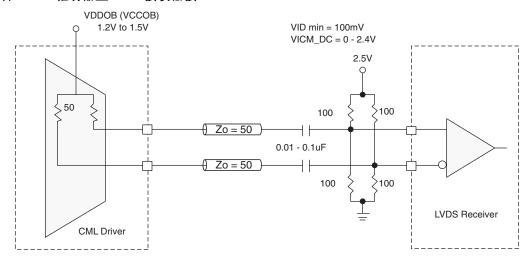

更高共模噪声的容差可用其他交流耦合 LVDS 驱动器至 SERDES 接收器的连接来实现。这个方案如图 9 所示。这将增加接收器对共模输入噪声电压的容差,并对共模,系统和地噪声提供更高的容差范围。

#### 图 9. 交流耦合 LVDS 驱动器至 CML 接收器接口

## LVPECL 器件接口

LVPECL 是一个信号线对的差分 I/O 标准,需要每个通道有一对信号线。通常用于远距离电气传输。差分传输方式比单端传输方式不容易受到共模噪声的影响。LVPECL 标准需要外部终端电阻,以减少信号的反射。差分对的标准电压摆幅约为 850mV,典型的 LVPECL VCC 为 3.3 V。

表 6. 典型的 LVPECL 规范

| 符号       | 参数          | 条件                       | Min        | Max        | 单位    |

|----------|-------------|--------------------------|------------|------------|-------|

| Voh      | 输出电压高电平     | 端接 50 欧姆的输出至 Vcco - 2.0V | 2215       | 2420       | mV    |

| Vol      | 输出电压低电平     | 端接 50 欧姆的输出至 Vcco - 2.0V | 1470       | 1680       | mV    |

| Vod      | 输出差分电压      | 端接 50 欧姆的输出至 Vcco - 2.0V | 535        | 950        | mV    |

| Ro       | 输出阻抗, 单端    | Vcm =1.0V 至 1.4V         | 3          | 10         | Ohms  |

| Vi       | 输入电压范围, 共模  | < 500mVp-p > 500mVp-p    | 1.1<br>1.3 | 3.1<br>3.1 | V     |

| Vin-diff | 输入电压范围,差分模式 |                          | 200        | >2000      | mVp-p |

| lih      | 输入大电流       |                          |            | -150       | μA    |

| lil      | 输入小电流       |                          | -600 - μA  |            |       |

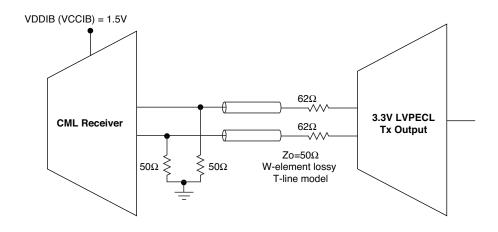

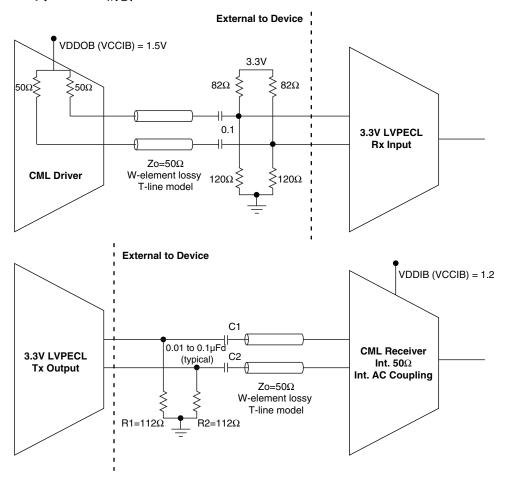

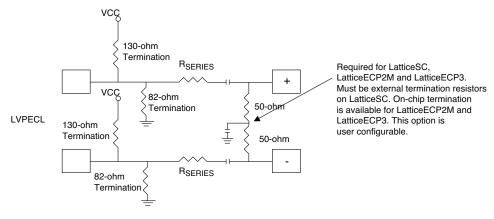

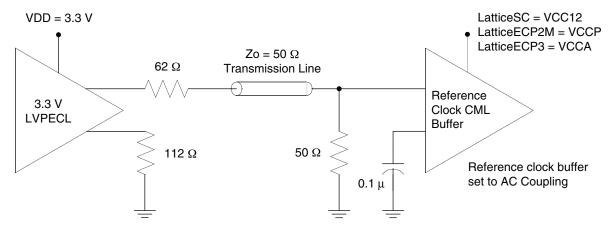

图 10 中的电路外部元件最少,并提供了直流信号耦合。在 LVPECL 输入使用与 SERDES VCCOB / VDDOB 电源相同的电平,偏置两个 50 欧姆的端接电阻,表示终端匹配了用于互连的传输线。这里首选 1.5V 的较高 VCCOB / VDDOB 值,以便更好地匹配信号电压。模拟的结果如图 11 所示。

LVPECL 驱动器输出偏置电流流过串联的 62 欧姆电阻和 SERDES 输入内部的 50 欧姆终端电阻。这种配置提供了合适的 SERDES 接收器所需接口的电压偏移和衰减。它还提供了用于互连的匹配传输线终端阻抗。

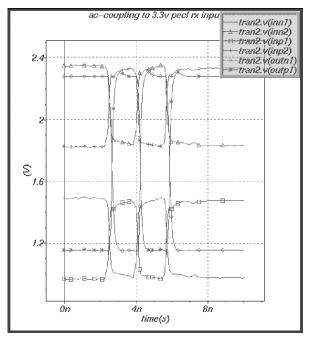

交流耦合解决方案的应用如图 11 所示。在这种情况下允许 LVPECL Rx 端有更高的终端阻抗,而不会造成信号失真。图 12 展示了模拟结果。

#### 图 10. 直流耦合 LVPECL 到 CML 的接口

图 11. 交流耦合 CML 到 LVPECL 的接口

图 12. 交流耦合 CML 到 LVPECL 的模拟

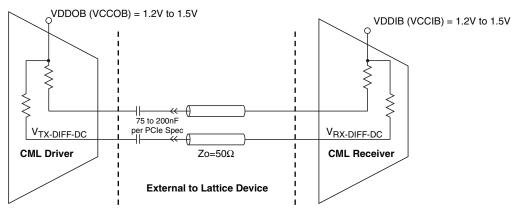

### PCI Express 器件接口

就电平而言,PCI Express 采用了两个单向的低电压差分信号(LVDS)对,每个通道的传输速率为 2.5Gbps。发送和接收是分开的差分对,每个通道共有 4 根数据线。莱迪思 CML 缓冲器能够很好地与 LVDS 接口,从而能够互连至 PCI Express 总线。可编程的均衡输入接收器和可编程的预加重输出发送器能够优化链接。PCI Express 规范要求差分线必须在接收端是共模终端。每一个链路需要在远(接收器)端有终端电阻。使用的额定电阻值为 100 欧姆。这是通过利用如图 14 所示的 CML 输入嵌入式终端匹配电阻的特性来达到的。该规范要求交流耦合电容器(CTX)在链路的发送方。这消除了发送和接收器件之间潜在的共模偏置的不匹配。该电容必须添加至莱迪思CML输出的外部。

#### 表 7. 差分 PCI Express 规范

| 符号                      | 参数         | Min. | Nom. | Max. | 单位 | 注释                                                                                            | 位置                |

|-------------------------|------------|------|------|------|----|-----------------------------------------------------------------------------------------------|-------------------|

| Z <sub>TX-DIFF-DC</sub> | 直流差分 TX 阻抗 | 80   | 100  | 120  | 欧姆 | TX 直流差分模式低阻抗。 ZTX-DIFF-DC 是在直流工作点测量到的发送器的小信号电阻,相当于 D+和 D-间连接了 100 欧姆的电阻,而 TX 驱动静态逻辑 1 或逻辑 0。  | 芯片内部              |

| Z <sub>RX-DIFF-DC</sub> | 直流差分输入阻抗   | 80   | 100  | 120  | 欧姆 | 在所有 LTSSM 情况下,RX 直流差分模式阻抗。传输从基本复位到检测时,(LTSSM 的初始状态),所有端口的未配置的通道上,在接收器终端阻抗满足之前,必须满足 5ms 的过渡时间。 | 芯片内部              |

| C <sub>TX</sub>         | 交流耦合电容     | 75   |      | 200  | nF | 所有的发送器应是交流耦合。要么在<br>传输媒介或者要么发送元件本身要求<br>交流耦合。                                                 | 外部至莱<br>迪思的器<br>件 |

#### 图 13. PCI Express 应用终端

## 接口至参考时钟 CML 缓冲器

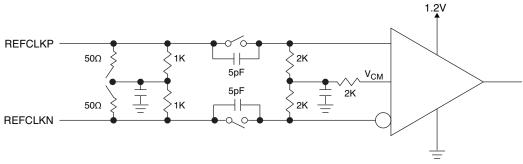

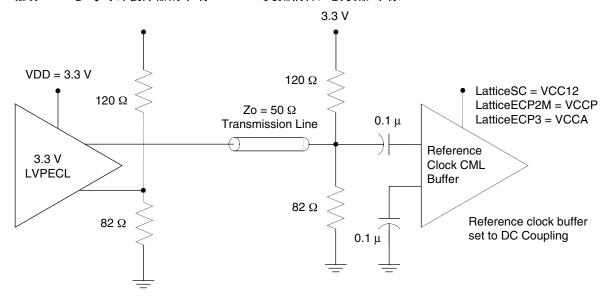

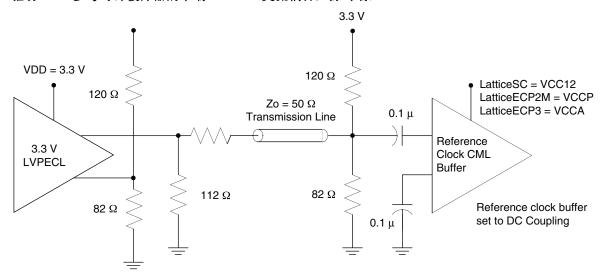

有些应用程序可能需要参考时钟接口。至 LVPECL 的接口需要外部元件,如以下一些图所示。这些都是针对驱动 CML 的差分 LVPECL、驱动 CML 的单端 PECL (直流耦合),以及驱动 CML 的单端 LPECL (在接收端或源终端进行交流耦合)推荐的配置。最好的做法是使用对地的两个中心抽头的 50 欧姆电阻。

#### 图 14. 针对 LatticeSC 器件的 CML 参考时钟输入缓冲器

#### 图 15. 针对 LatticeECP2M 器件和 LatticeECP3 器件的 CML 参考时钟输入缓冲器

Note: DC coupling is only recommended when using an external AC coupling capacitor.

#### 图 16. 外部交流耦合的参考时钟缓冲器——LVPECL 时钟驱动器

- 1. 150-ohm (or similar) pull-down can typically be substituted in place of a 130/82-ohm Thevenin divider.

2. R<sub>SERIES</sub> varies based on LVPECL driver characteristics.

3. Reference clock options LatticeECP2M/LatticeECP3: 50-ohm termination, DC-coupling; LatticeSCM: Hi-Z termination, DC-coupling.

- Refer to the specific device data sheet for DC specifications.

#### 图 17. 驱动 CML 参考时钟缓冲器的单端 PECL (直流耦合)

图 18. 驱动 CML 参考时钟缓冲器的单端 PECL (交流耦合,接收器终端)

图 19. 驱动 CML 参考时钟缓冲器的单端 PECL (交流耦合,源终端)

使用 900-BGA wire-bonded 封装的 LatticeSC 器件时,要考虑几个特殊的情况。当通过探测器件引脚来观察时,可能会发现至参考时钟输入的输入路径电气性能的质量并不如我们所期望的。由于 900 BGA 封装所固有的时钟路径的寄生效应,造成了这些信号的缺陷。在内部参考时钟输入缓冲器本身,这些反射是不明显的。HSPICE 模型可供用户进行评估和验证。

# 仿真使用的详细资料

接口电路的模拟仿真是设计过程中非常有用的一部分。简单的接口可以使用 CML 缓冲器的 HSPICE 模型来仿真,这些模型可从莱迪思获取。在 SERDES 和互联器件之间,可以提供长度匹配的两个 50 欧姆理想传输线,表示为印刷电路板的走线。正如本文所述,在驱动 SERDES 缓冲器的仿真中,采用了随机的 622 Mbps 的数字信号模式,通过模拟预测可以得到信号电压波形。器件封装的寄生单元可包括在内。其他参数和假设条件是标称的集成电路工艺参数,额定电源电压和室温。

## 结论

本文讨论了莱迪思 SERDES 器件的通用终端和接口互连。还讨论了电流模式逻辑(CML)输入和输出缓冲器结构的使用,用其他 CML 和非 CML 器件的接口功能。莱迪思 SERDES 器件提供了各种输入和输出终端匹配电阻,从而减少了外部元件。

## 参考文献

- LatticeSC/M 系列数据手册

- LatticeSC/M 系列 flexiPCS 数据手册

- LatticeECP2/M 系列数据手册

- LatticeECP3 系列数据手册

- TN1033, 高速印刷电路板的设计考虑

- TN1124, LatticeECP2M SERDES/PCS 使用指南

- TN1176, LatticeECP3 SERDES/PCS 使用指南

- TN1159, <u>LatticeECP2/M 引脚分配的建议</u>

- TN1189, LatticeECP3 硬件清单

- ispLEVER® 软件文档

## 技术支持

热线电话: +86-21-52989090

电子邮件: techsupport-asia@latticesemi.com

网站: www.latticesemi.com.cn

# 修订历史

| 日期       | 版本   | 变更摘要                                                           |  |

|----------|------|----------------------------------------------------------------|--|

| 2006年7月  | 01.0 | 最初的版本。                                                         |  |

| 2006年12月 | 01.1 | 新增讨论有关开关稳压器和线性稳压器的文本部分。                                        |  |

|          |      | 更新的 PCI Express 的应用终端图。                                        |  |

| 2007年4月  | 01.2 | 新增对 LatticeSC 印制电路板布局的建议。                                      |  |

| 2007年6月  | 01.3 | 对 LatticeSC 和 LatticeECP2M SERDES 的电源表加脚注 1。                   |  |

| 2007年7月  | 01.4 | 更新接口至参考时钟 CML 缓冲器部分。                                           |  |

| 2008年1月  | 01.5 | 更新接口至参考时钟 CML 缓冲器部分。                                           |  |

| 2008年1月  | 01.6 | 更新的 PCI Express 器件接口部分。                                        |  |

| 2008年6月  | 01.7 | 对 LatticeSC 印刷电路板产生串扰的 I/O 引脚表加脚注。                             |  |

|          |      | 对 TN1159 LatticeECP2 / M 引脚分配加参考信息。                            |  |

|          |      | 更新差分 LVPECL 驱动 CML 参考时钟缓冲器 (DC) 图,在 (图 13 说明 CML 缓冲器)之后添加了新的图。 |  |

| 2008年8月  | 01.8 | 按照数据手册纠正 LatticeECP2 / M 的参数名称和值。                              |  |

| 2008年11月 | 01.9 | 对无源滤波网络"无噪声电源"示例图添加了注释。                                        |  |

|          |      | 对 LatticeSCM 和 LatticeECP2M 的 CML 参考时钟输入缓冲器添加了新的图。             |  |

| 2008年12月 | 02.0 | 更新了 LatticeECP2M VCOM 的典型值范围。                                  |  |

| 2009年2月  | 02.1 | 对 LatticeECP3 FPGA 系列添加了支持。                                    |  |

| 2009年4月  | 02.2 | 对 LatticeECP2M 和 LatticeECP 3 器件图更新了 CML 参考时钟输入缓冲器。            |  |

| 2009年6月  | 02.3 | 更新了有内部直流耦合的参考时钟缓冲器图。                                           |  |

|          |      | 更新了有内部交流耦合的参考时钟缓冲器图。                                           |  |

| 2009年11月 | 02.4 | 添加了 REFCLK 直流耦合的建议。                                            |  |

| 2010年2月  | 02.5 | 对电源图和 LVPECL 端接方法做了更新。                                         |  |

| 2011年6月  | 02.6 | 更新了有内部直流耦合的参考时钟缓冲器图。                                           |  |

|          |      | 删除了直流耦合图 (CML 到 LVPECL)。                                       |  |

| 2012年8月  | 02.7 | 更新文档,加入了新的公司标志。                                                |  |

|          |      | 更新了有外部交流耦合的参考时钟缓冲器图。                                           |  |

| 2012年9月  | 02.8 | 添加了仅 Rx 或仅 Tx 时的电源 (VCCIB/OB) 的使用建议。                           |  |

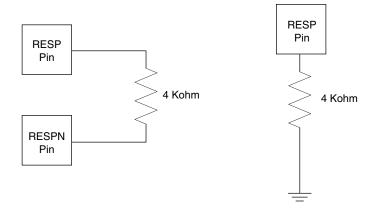

## 附录 A. LatticeSC 器件

外部校准电阻连接在 RESP 引脚和 RESPN 之间,对一些没有专门 RESPN 引脚的封装,这个电阻连接在 RESPN 引脚与电路板的地之间。器件的上面各角上都需要这个电阻,因此对每个器件最多需要两个电阻。外部电阻值为 4.02K 欧姆,这是对精度为±1%的电阻的 "EIA E96 series" 行业标准。该电路还需要内部核电压 VCC,生成如图 20 所示的 VBIAS。

#### 图 20. RESP 连接