# 검증된 시스템-온-칩 디자인을 통한 PLD개발의 가속화

A Lattice Semiconductor White Paper 2010년 3월

래티스 반도체 주식회사

5555 Northeast Moore Ct. Hillsboro, Oregon 97124 USA

Telephone: (503) 268-8000

www.latticesemi.com

## 서론

콘트롤 애플리케이션에 적용되는 보통의 프로그래머블 로직 디바이스(PLD)는 내부 온 칩 버스를 통해 마이크로콘트롤러와 여러 온 칩/오프 칩과 상호 연결되어 구성된다. 비록 각 인터페이스는 비교적 간단하지만, 이들 모든 상호 연결을 구성하고 디버깅하는 일은 많은 시간이 소비되고 어려움이 될 수 있다. 그래서 개발 과정을 가속화 시킬 수 있도록 미리 설계된 프로세서-기반의 개발 보드를 사용하는 디자이너가 점차 늘고 있다.

이런 접근방식은 여러 장점이 있다. 첫 번째, 여러 IP를 사용하는 것과 선택된 IP와 온-칩 버스간의 차이를 새로이 설계 할 필요가 없다. 두 번째, 온-칩 버스에 다양한 IP를 일일이 수동으로 연결 할 필요가 없다. 해당 문서 후미에서 논의 될, 대략 1000룩-업-테이블(LUTs)의 작은 디자인 설계 일지라도, 이는 탑-레벨 연결을 위해 대략 300라인의 Verilog코드를 필요로 한다. 세 번째, 하드웨어 기능 구현을 위한 시간을 아주 빠르게 줄일 수 있다. 하드웨어의 기본 기능 구현과 중요한 모든 인터페이스 디버깅을 수 일 내에 끝내는 것이 가능하다. 디자인이 안정화된 시점에선 인터페이스의 추가 또는 삭제는 좀더 간단하게 이루어진다. 그리고, 수정으로 인해 인터페이스에 문제가 발생하면, 이전의 알고 있는 버전으로 쉽게 이동할 수 있다.

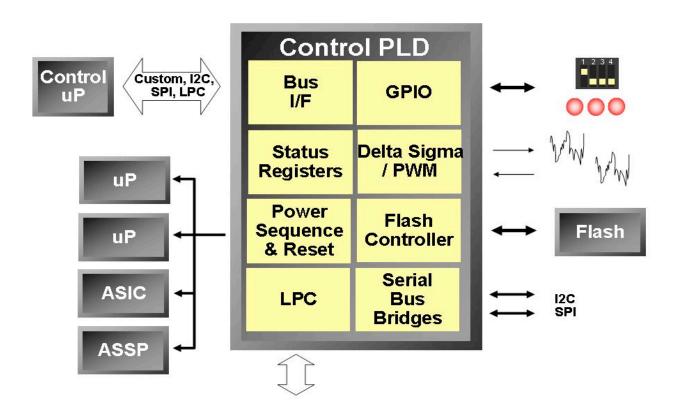

# 전형적인 개발 보드

디자이너들이 미리 설계된 시스템으로 개발을 시작하도록 한 후 최종 시스템으로 디자인을 전송하기 전에 프로토타입 구축을 위해 수정하는 개발환경의 한 예가 Lattice의 MachXO Mini개발 보드이다. 이는 많은 애플리케이션에 적합하기는 하지만, 자주 사용되는 비휘발성 PLD와 함께 작은 콘트롤 애플리케이션을 위해 맞추어져 있다. 그림 1은 콘트롤 플레인 애플리케이션에 수행하는 PLD에서 구현되는 전형적인 기능을 나타낸 것이다.

Figure 1 - Typical Control Plane Functions Implemented in PLDs

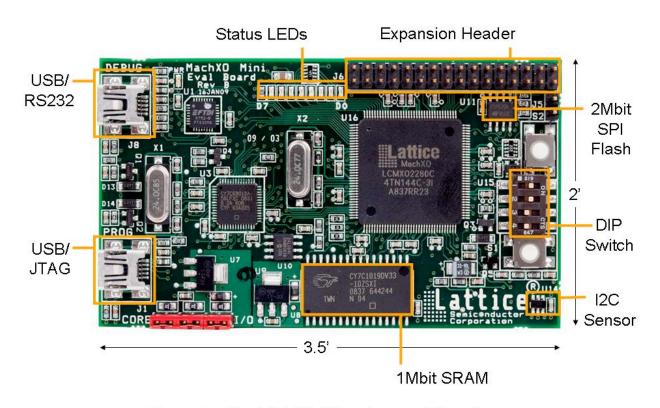

Mini 개발 보드의 중앙에는 로직 구현을 위해 2280LUTs를 제공하는 비휘발성, 플래쉬기반의 MachXO 2280이 있다. 그림 2는 MachXO Mini개발 보드 및 주요 인터페이스에대해 보여주고 있다. 해당 보드는 다섯 가지의 주요 기능을 제공한다.

- LED, 헤더, DIP스위치와 푸쉬 버튼 스위치를 통해 GPIO와 상태 표시기가 제공된다.

- SPI 플래쉬 메모리와 I2C온도 센서 제공을 통한, 보통의 시리얼 인터페이스를 지원한다.

- SRAM메모리는 별도의 스크래치-패드 메모리를 제공한다.

- 디버깅을 위한 USB의 RS232를 제공한다.

- 디바이스 프로그래밍을 위한 인터페이스로서 USB의 JTAG을 제공한다.

USB를 통한RS232와 JTAG 인터페이스는 개발 과정에서 아주 중요하다. 미니 "B" 타입의 USB커넥터는 케이블을 통해 일반 개인 컴퓨터의 USB포트에 연결 될 수 있다. 안정적으로 드라이버가 로딩되어 있으면, USB를 통한 JTAG인터페이스를 통하여, Lattice ispVM소프트웨어에서 MachXO 디바이스를 프로그래밍 할 수 있다. 또한 USB RS232를 위한 드라이버를 로딩 후 에뮬레이션을 할 수 있다. 그리고 Linux와 Windows XP를 위한 최신 버전의 드라이버를 제공한다. 시리얼 포트는 간단하게 호스트 PC에 "COM"포트로 나타난다. 이 인터페이스는 온-칩 디자인을 위한 상태 정보 및 디버깅 정보를 호스트 프로세서에 전송하는 편리한 방법을 제공한다.

Figure 2 - MachXO Mini Development Board

## 미리 개발된 시스템-온-칩 디자인

Mini개발 보드를 통해, 빠른 개발을 가능하게 하는 것은 시스템-온-칩(SOC) 디자인이 미리-개발되고, 미리-로딩되어 컨트롤 플레인 기능을 구현하는 PLD 개발 초기에 제공될 수 있기 때문이다. 아래는 안정적으로 소프트웨어 툴과 드라이버가 호스트 PC 에 로딩됐다는 가정하에서, 개발 흐름과 이와 연관된 개발 시간을 보여준다:

- 1. 예상되는 하드웨어와 인터페이스 동작 검증. (보통 5분) *이 시점에서 설계자는 하드웨어에 대해 잘 알고 있다.*

- 2. ispVM프로그래밍 소프트웨어를 사용하여 FPGA 컨피규레이션 파일을 재로딩할 수 있는지에 대해 확인한다. (보통 5분)

- 3. ispLEVER소프트웨어를 사용하여 디자인을 컴파일하고 예상되는 결과로 동작되는지에 대해 확인한다. (보통 10분) 이 시점에서 설계자는 개발 초기의 여러 가지를 잘 알고 있다.

- 4. 디자인의 개선을 위해 첫 변경을 하게 되고, 새로운 컨피규레이션을 위해 재컴파일하고 로딩한다. (보통 60분, 실제 시간은 수정된 부분에 따라 다르다.)

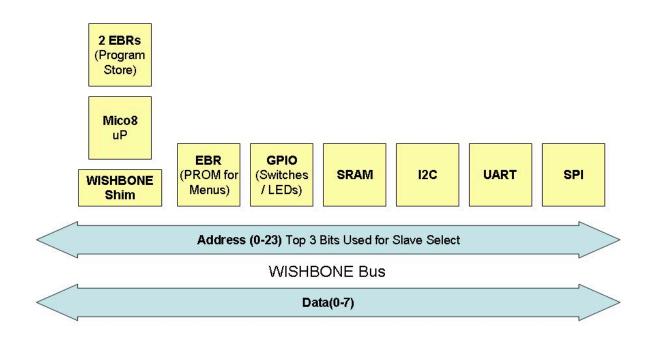

이런 개발 흐름에 따라, 초기 개발에서 수 시간을 줄일 수 있다. 그림 3에서는 SOC디자인 전반에 대해 보여준다. 아래 그림에서 볼 수 있는 것처럼, 디자인은 온-칩 버스를 통해 상호 연결된 마이크로프로세서와 여섯 개의 인터페이스로 구성되어 있다.

Figure 3 - MachXO Mini Board Pre-loaded SOC Design

해당 디자인의 중앙에는 온-칩 버스가 있다. 사용되는 WISHBONE표준은: SOC설계에 이상적인 구조로 오픈-소스 버스 표준이다. 이런 WISHBONE버스의 이점은 다음과 같다:

- WISHBONE 오픈 소스이며, FPGA 또는 ASIC에서 다양하게 사용될 수 있다.

- WISHBONE 인터페이스를 위한, 많은 수의 오픈 소스 IP가 있다.

- 간단하지만 복잡한 성능을 위한 유연함을 갖는다.

많은 콘트롤 플레인 PLD에서 요구되는 성능은 비교적 낮은 관계로, WISHBONE 버스는 마스터로 동작하는 마이크로프로세서와 함께 공유된 버스로 구현된다. 어드레스 버스는 슬레이브 선택 시그널 생성 전용 최고 3비트로 총 24비트이다.

LatticeMico8 (레퍼런스 디자인 RD1026)과 연관된 WISHBONE 어댑터(RD1043)는 디자인 코어를 형성하는 프로세서를 위해 사용된다. Mico8은 오픈 소스의 이점을 갖는다. 이는 임베디드 프로세서의 개발을 위해 종종 상당한 양의 코드를 개발해야 하기 때문에 아주 중요하다. LatticeMico8의 오픈 소스 본질은 임베디드 코드에 대한 투자를 보호하고, 다양한 FPGA패브릭 또는 ASIC에 구현될 수 있는 것을 의미한다.

Mico8은 8비트 데이터 패스, 18-비트 광범위한 명령과 16 또는 32개의 일반 목적의 레지스터를 가지고 있다. 외부 메모리는 op코드가 포함된 첫 8-비트 어드레스가 페이징 된다. 다른 16-비트 어드레스 버스는 R15와 R16레지스터를 제어할 수 있다. 프로그램 메모리는 512와 4096사이에서 설정 될 수 있다. 이 경우 최대 18비트의 1024지점까지 사용된다. 프로그램 메모리는 두 개의 임베디드 블록 램(EBR)에 저장되며, 이는 디바이스 초기 동작 시 요구되는 내용을 초기화 할 수 있다. 각 MachXO EBR은 9-비트의 1024워드까지 지원된다. Mico8은 대략 300LUTs를 사용한다.

Mico8을 위한 새로운 코드는 프로젝트 파일의 일부분으로 제공되는 어셈블리 리스팅의 변경으로 쉽게 생성될 수 있다. 수정된 코드는 LatticeMico8 툴을 통해 검증되고, 알맞은 HEX파일을 생성한다. 이 HEX파일은 ispLEVER 툴에서 프로그램 저장을 위해 적당하게 EBR들을 초기화 한다. Mico8툴은 또한 Lattice 웹사이트에서 다운로드 가능하고, 소스와 실행 가능한 형태로 오픈 되어 있다.

다른 EBR메모리는 WISHBONE버스에 연결되며, 이 EBR은 1024 8-비트워드로 구성된다. 또한 RS232인터페이스를 이용하여, Mico8에 의해 나타나는 다양한 메뉴를 볼 수 있다. SPI인터페이스는 Lattice의 SPI WISHBONE 콘트롤러 레퍼런스 디자인(RD1044)의 수정된 버전을 활용하고 있다. SPI인터페이스는 외부 2Mbit의 SPI 플래쉬 메모리와 WISHBONE 버스를 연결한다. SPI WISHBONE 콘트롤러는 필요한 경우, 최대 8개의 슬레이브를 제어하는데 사용 될 수 있다. 송수신 레지스터는 비록 8-비트 레지스터로 사용되지만, 1에서32-비트로 구성이 가능하다. 레지스터는 수신되는 데이터를 위해 더블-버퍼가 가능하고, 마이크로프로세서가 다른 버퍼를 확실히 하기 위해 인터럽트 요구를 처리하는 동안, 송신될 수 있다. 이 레퍼런스 디자인은 대략 113LUTs를 사용한다. I2C인터페이스는 WISHBONE버스 인터페이스 레퍼런스 디자인(RD1046)의 Lattice I2C마스터를 사용한다. 해당 디자인은 7또는 10-비트 어드레싱 모드와 8-비트 송수신 버퍼를 지원한다. I2C레퍼런스 디자인은 대략 234LUTs를 사용한다.

UART디자인은 Lattice WISHBONE UART 레퍼런스 디자인(RD1042)을 이용한다. 이는 범용적으로 독립된 NS16450 UART와 동일한 기능으로 구현되었다. 이 디자인은 대략 291LUT를 사용하며, 이는 간단한 WISHBONE 주변장치의 좋은 예라 할 수 있다.

# 결론

MachXO Mini개발 보드의 목표는 비휘발성의 작은 FPGA형태의 디자인을 위한 개발시간을 단축 시키는 것이다. 이를 달성하기 위해, 이 글에서 논의된 SOC디자인의 모든 정보를 Lattice웹사이트에서 단일 패키지로 다운로드가 가능하다. 자료 및 소스파일과 더불어, TransFR과 전력 소모 절감을 위한 슬립 모드 데모 그리고 SOC 디자인을 위한 완전한 ispLEVER프로젝트 또한 제공된다. 제공되는 정보는 프로젝트 파일과 함께디자인이 처음 컴파일 될 수 있도록 필요한 모든 프리퍼런스(preferences)와 컨스트레인트 (constraints)를 포함한다.

엔지니어 시스템에서 사용되는 콘트롤 PLD 설계 시간을 단축시키고 싶다면, 개발 시스템과 검증된 디자인을 살펴보길 바란다. 이는 엔지니어의 차기 개발 사이클을 단축시켜 줄 수 있을 것이다.

###