# 次世代ワイヤレス・ネットワークにおける FPGA

ラティスセミコンダクター・ホワイトペーパー 2010年3月

ラティスセミコンダクター

5555 Northeast Moore Ct. Hillsboro, Oregon 97124 USA Telephone: (503) 268-8000

www.latticesemi.com

#### はじめに

音声接続に加えて、GSM やその機能拡張である GSM-EDGE は現在、(理論上の)限界である 384Kbps まで増大したデータ速度を提供することができます。CDMA2000 やWCDMA、或いは UMTS (Universal Mobile Telecommunications Standards)や TD-SCDMA (中国のみ)などの第三世代モバイル・ネットワークは現在、世界中で展開されています。これらのシステムはストリーミング・ビデオやインターネット閲覧などのサービスを提供し、そして HSPA (High Speed Packet Access)と呼ばれる技法を用いることによって、理論上は 14.4Mbps までダウンリンク速度を達成することができます。

将来のインフラストラクチャは総称して 4G システムと呼ばれますが、その開発は大幅な低コストで、より高速かつ大容量の実現に焦点を合わせています。2つのテクノロジがその最先端にあります。即ち通常 LTE と呼ばれるセルラー/モバイル・テクノロジのための 3GPP LTE (3rd Generation Partnership Program、Long Term Evolution)と広帯域ワイヤレス・アクセスのための WiMAX です。WiMAX はアクセス市場で早期に相応の支持を勝ち取りましたが、ローミングと基地局間の切り替えに関する幾つかの課題が残っています。主要なセルラー・ネットワークの事業者は将来のテクノロジとしてLTE の選択を支持しています。これら 4G 規格は共に OFDM (Orthogonal Frequency Division Modulation)および MIMO (Multiple Input Multiple Output)アンテナネットワークに基づく共通のエアインターフェイス標準を用います。これら先進のテクニックにより、広域サービスでは避け得ない劣化した信号対雑音比の信号でも再生することが可能になります。

これらの複雑で、またしばしば競合するテクノロジの実質的影響は、機器ベンダがより 複雑なベースバンド処理と同様に複数のエアインターフェイス規格に対応する必要があ るということです。同時に、これらのシステムは将来必要となるであろう帯域幅の増加 に応じた拡張計画に対応するための柔軟性を提供できる必要があります。これらはコス トを低減し、そしてまた"グリーンな"環境要件を満たすためにより低消費電力でなければなりません。

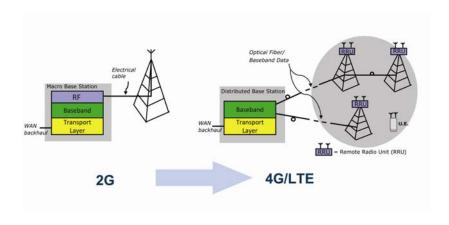

第二世代システムでは、通常マクロ基地局は物理的にベースバンドとプリアンプに近く、RF電力部を持つアンテナに配置されました。主要なシステム開発の一つが分散基地局の使用です。これらのシステムでは、ベースバンド処理部は RF電力部と分離されます。アーキテクチャ的にマクロ基地局システムから分散基地局システム(図 1)に移行することで、システムコストを顕著に節減することができます。マクロ基地局での他の要件の中には、アンテナと 150m 以内に配置しなければならないというものがあり、さもないと RF電力の 50%がケーブルで失われることになります。機器のアップグレードと保守に費用がかかる場合があります。より良いソリューションは分散「リモートラジオ」ネットワークです。そこでは、RF電力増幅器を含む RRU (Remote Radio Unit)をベースバンドと遠隔地に配置し、直接アンテナマストに取り付けることができます。CPRI (Common Public Radio Interface)や OBSAI (Open Basestation Architecture Initiative)などの標準インターフェースは、RRU ユニットを光ファイバでベースバンド部に接続することができます。

図1基地局ネットワークの進展

### 無線インフラストラクチャにおける FPGA

プログラマビリティは基地局設計が進展する過程に共通してみられる特性です。すなわち仕様が完全に批准される前に設計がしばしば開始されたためです。基地局は ASIC デバイスを多用した装置であり、そして FPGA はインターフェイスや「グルーロジック」としてしばしば用いられてきました。即ちデザインバグの対処のためや、専用DSP デバイスのサポート機能などとしてです。ワイヤレス標準が進化するにつれて、基地局の複雑さもそれに対応して増加しました。FPGA は革新的な変化を経ましたが、それは特にその性能とロジック規模の顕著な向上です。技術者は DDC (Digital Down Conversion)や DUC (Digital Up Conversion)などの、より複雑な機能に FPGA を用い始めました。基地局設計においてこれらの機能のために FPGA が提供する柔軟性は、FPGA が今や設計プロセスで主要な部品になったことを意味します。LatticeECP3 ファミリなどの FPGA は今日、複数の組み込み DSP ブロックや組み込みメモリ、および SERDES などの多くの機能を搭載しています。これらの機能が無線システムの発展に伴うニーズと相俟って、設計エンジニアにとって FPGA を選択すべき部品にしました。その柔軟性は、次の ASIC 修正を待つ必要なしに技術者が変更を直ちに実装することを可能にしたため、市場投入までの時間は加速されました。

## <u>リモート・ラジオ・ユニット/ヘッド(RRU)</u>

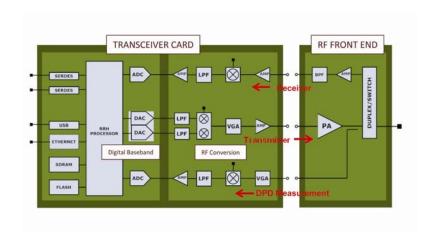

RRU機能はデジタル信号処理、RF変換、および電力増幅器、デュプレクサ、および LNA (Low Noise Amplifier)を包括する RF フロントエンド・アセンブリよりなるトランシーバーカードから成ります。トランシーバーカードの設計はしばしば広帯域で、各無線規格と動作帯域の間には、コンポーネントとして 80%~90%の共通性があります。 典型的なユニットを図 2 に示します。

図2典型的なトランシーバーカードの設計

SDR (ソフトウェア無線機)のテクニックでは再構成が可能であるために FPGA を使用することが、共通のベースバンドで WCDMA や WiMAX、或いは LTE などの複数の無線規格に対応することを可能にします。 MIMO アンテナシステムでは、ユニットは複数の送受信アンテナを提供しなければなりません。

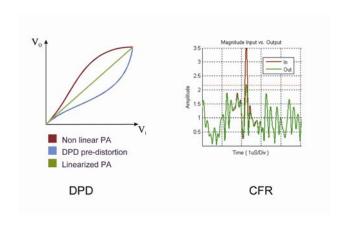

次世代ネットワークは現在展開されている 2GHz 以上の帯域よりも大幅に高い周波数で運用されるでしょう。またそれらは、大幅に速いレートのデータ伝送が必要でしょう。RRU 設計上の主要な懸案は RF PA (パワーアンプ)の消費電力とコストです。ピーク対平均電力比(PAPR)の大きい信号では、PA は比較的まれながら高い電力レベルを送信する必要があります。これが幾らまれにしか起こらないとは言え、設計としてはそれを考慮しなければならず、これはより高コスト化をもたらします。また、RF トランジスタは高電力レベルでは非線形性を示すため、信号ひずみと帯域外電力の増加という結果になります。PAPR が大きいことと非線形性が組み合わされる 4G システムでは、PA が定格出力電力の 20~30 %で動作し、トータル効率は 10~15%になる結果となり得ます。100%の使用率と最大 70%の効率で動作する GSM PA とよい比較です。この問題に対する解決策は、増幅された RF 信号が結果として最適の性能で得られるような方法で、PA 最終段の前の信号をあらかじめ調整することです。このプロセスで使われる 2

つの手法があります;即ち CFR (Crest Factor Reduction)と DPD (Digital Pre-distortion) です。

CFR は、知的に PA 入力に存在する最大波形の振幅を制限することによって、結果として生起するピーク出力電力を減らします。求められる信号精度とスペクトル特性を維持しながらも、実質的に信号 PAPR を低減させます。これは低消費電力時や WiMAX やピコセルなどのマイクロ基地局では DPD がなくても用いることができます。

他方 DPD は PA の伝達特性を考慮に入れて、入力信号にひずみを適用する方法によって PA に直線性を持たせます。その結果、PA の特性によって生成されるどのような信号ひずみも取り除きます。 DPD は通常、RF 出力電力が 1~2 ワットより大きいシステムで CFR と共に用いられます。これらテクニックの効果は図 3 で示されています。

図 3 DPD と CFR 技法の効果

RRUにおける CFR と DPD 技法の使用は、システムエンジニアが別の方法で必要とされるであろうより大幅に低コストの PA を用いることを可能にします。これら技法のいずれもが、アルゴリズムを実装するために顕著な量の DSP 処理能力を必要とします。また最も重要なことは、これらは何らかの形態の適応性を必要とすることです。すなわち温度変動や時間を経ることで起こるであろう PA 伝達特性のどのような変化にも対応する必要があります。

RRU 内にプロセッサを組み込むことは、この問題に対する一つの解決策です。セルラー基地局の設計では伝統的に ASIC が広く用いられてきました。しかしながらその長い設計サイクル、高い固定費、および柔軟性がないなど、まだ発展途上の市場には適しません。個別の DSP プロセッサはこの問題の別の解決策であるように思えるでしょうが、調査によれば複数規格対応の基地局を実装する際に限界があることが示されました。他方 FPGA では、組み込み DSP セルや SERDES、そしてソフトプロセッサによって必要な機能のすべてを単一の再構成可能チップに収容することができます。そのようなデバイスの一つがラティスセミコンダクターからの ECP3 です。この FPGA は業界のどの SERDES 搭載 FPGA デバイスよりも低い電力消費と価格を提供します。ファミリは XAUI ジッタ準拠の複数プロトコル対応 3.2G SERDES や、DDR 1/2/3 メモリインターフェイス、強力な DSP 機能、および大規模オンチップメモリを提供し、しかも競争他社の SERDES 搭載 FPGA より消費電力とコストがそれぞれ約半分です。

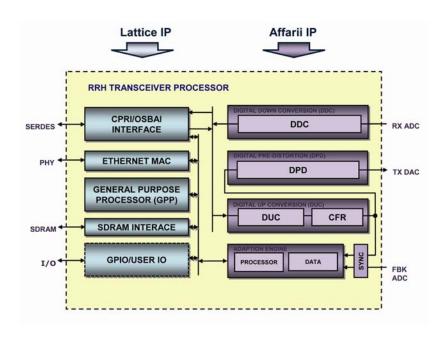

FPGA の選択は、システムの物理的な、そして性能パラメータを満たすために慎重に考慮される必要がありますが、トータルシステム・ソリューションとして RRU の機能に重要な IP が利用できることも重要です。IP パートナー・プログラムの一環として、ラティスはセルラー無線システムに幅広い経験がある会社である Affarii とチームを組みました。Affarii IP と Lattice ECP3 FPGA の組み合わせは、FPGA ファブリック内にRRU を構築するために必要なブロックすべての IP を組み合わせることができる、柔軟なプラットホームを両社が提供することを可能にします。

図 4 RRU プロセッサ

RRUプロセッサでは、送受信のために RF キャリアに信号データを多重化し、変調します。図 4 はラティスと Affarii によって提供される IP を表します。各ブロックは識別を容易にするために色分けされています。

特定の異なるアプリケーションのために CFR の構成を最適化することができます。厳密なパラメータは最大キャリアの構成に対するシミュレーションで決定することができます。標準システムでの構成はデザインツールとドキュメントで提供されます。またユーザは、特定用途のために IP コアと共に提供する IP モデルとシミュレーション環境を用いることで、カスタム構成を生成することもできます。表 1 の上部に CFR IP をLFE-70E FPGA に配置配線した場合の使用リソースを示します。

DPD 動作のための構成は、意図する PA の特性評価を元に最良になるように決定されます。 DPD コア自体には、実環境やテストソースからデータ解析をするための診断インターフェイスがあります。このツールを用いてアンプの非線形性に対する詳細な特性評価を実施することができ、したがって DPD の最適構成を決定することができます。

またリアルタイムでアンプパラメータを測定するため、この手順はアンプ設計時に改善が必要な点を把握することもできます。表 1 下部は DPD を LFE-70EP FPGA に配置配線した場合の使用リソースを示します。

| ci it i lace e | Routed:   | LFE3- | 70E-FPE | 3GA48 | 4-8         |     |

|----------------|-----------|-------|---------|-------|-------------|-----|

| STANDARD       | MODE      | СН    | SLICES  | EBR   | MULT        | MHz |

| LTE, WIMAX     | SYM       | 1-2   | 8K      | 22    | 22          | 213 |

|                | '         |       |         |       |             |     |

| CFR Place &    | k Routed: | LFE3- | 70E-FPE | 3GA48 | 4-8<br>MULT | MHz |

表1

Affarii IP は CFR と DPD 機能だけでなく、DUC/DDC と基地局アーキテクチャで不可欠のビルディングブロックである適応エンジン機能も含みます。

ラティスにより提供される主要な IP ブロックは CPRI と OBSAI です。これらは FPGA に含まれる組み込み SERDES 機能を用いる高速インターフェイスです。これらインターフェイスが遠隔ベースバンドを RRU にリンクします。イーサネット MAC はモニターと制御システム機能を備えます。設計者はまた部品点数とコストを節約するために、RRH の汎用処理と制御に LatticeMico32 ソフトプロセッサを用いることを選択するかもしれません。先進のメモリインターフェイスと汎用 I/O(GPIO)でシステムは完成します。

# まとめ

FPGA はいま高集積度のデバイスに成熟し、性能・機能的に向上したインターフェイスを提供する組み込み ASIC タイプの機能を集積することもできました。FPGA の使用に

よりマイクロプロセッサ機能と組み合わされた DSP プロセッサと組み込みメモリは、 基地局設計において単一の再構成可能なデバイスでコア機能を提供する手段を与えます。 プログラマブル・デバイスによって提供される利点は、新しくて発展途上の標準に対応 する柔軟性を持ちながら、高いコスト効果で市場投入期間のより短縮化を可能にするで しょう。

###