# MachXO 系列

## 针对低密度应用进行优化

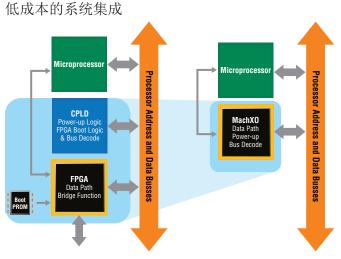

非易失无限可重构可编程逻辑器件(PLD)MachX0™系列是专为传统上使用CPLD或低密度FPGA实现的应用而设计的。将优化的查找表(LUT)结构与低成本的嵌入式闪存处理工艺结合在一起,即时启动,易于使用的MachX0器件是针对低密度应用的最通用的,非易失可编程逻辑器件。

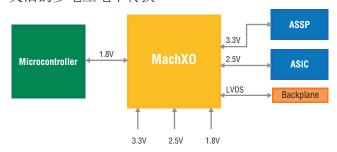

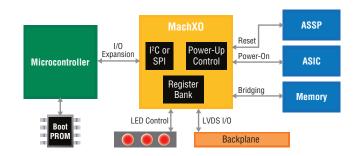

通过提供嵌入式存储器、内置锁相环,灵活的多电压高性能的LVDS I/0、远程现场升级(TransFR™技术)和低功耗的睡眠模式,MachX0可编程逻辑器件系列有效地提升了系统的集成度,所有这些功能都整合在单片器件之中。

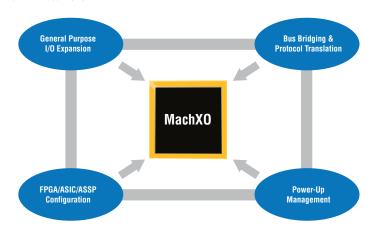

MachXO PLD专门为广泛的低密度应用而设计,包括通用I/O的扩展、控制,总线桥接和电源管理功能,MachXO PLD系列适用于各种终端市场,如消费电子、汽车、通讯、计算机,工业和医疗设备。

### 广泛的应用

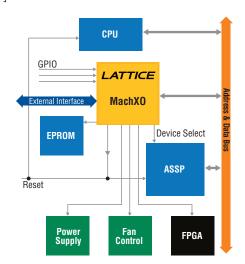

#### 应用实例

#### 主要特性和优点

- 非易失性,无限可重构

- 即时启动,上电时间低于1毫秒

- 单芯片, 无需外部配置存储器

- 优异的设计安全性, 无法截取位流

- 3.5ns引脚至引脚的性能

- TransFR技术使得能够方便地进行现场升级

- 灵活的LUT结构

- 256到2280个 LUT4

- · 具有多种封装选择的73至271个I/0

- 支持密度迁移

- 嵌入式和分布式存储器

- · 高达27.6千位的sysMEM™嵌入式RAM块

- · 包含专用的FIFO控制逻辑

- 高达7.7千位的分布式RAM

- 灵活的I/0缓冲器

- 可编程sysI0™缓冲器支持各种接口:

- LVCMOS 3.3/2.5/1.8/1.5/1.2

- LVTTL

- PCI\*

- LVDS\*, Bus-LVDS\*, LVPECL\*, RSDS\*

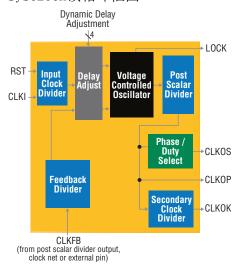

- sysCLOCK™锁相环

- 每个器件多达两个模拟锁相环

- 时钟倍频, 分频和相移

- 睡眠模式降低待机功耗至< 100 μ A

- 系统级支持

- IEEE标准1149.1边界扫描

- 板上的20MHz振荡器用于配置和用户逻辑

- 器件工作于3.3V、2.5V、1.8V或1.2V的电源电压

- 器件适用宽的温度范围

- 商业: 0至85℃ (TJCOM)

- 工业: -40至100℃ (TJIND)

- 符合AEC Q100: -40至125℃ (TJAUTO)

- \* 仅MachX01200和2280器件

# MachXO架构

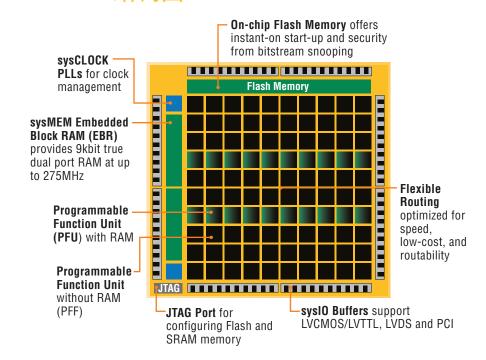

#### 架构概述

MachXO可编程逻辑器件为传统上用CPLD或低密度FPGA实现的应用提供了一个低成本,灵活的选择。器件基于一种极其有效的架构,MachXO可编程逻辑器件提供出色的引脚对引脚的性能,支持高速的I/O、嵌入式RAM块,以及sysCLOCK锁相环。

可供选择节省面积的符合RoHS的封装,MachXO PLD可用于广泛的面积受限的应用。

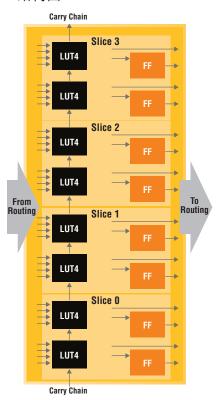

#### PFU结构图

## MachXO结构图

#### sysMEM配置选择

| 单口       | 双口       | 准双口      | FIFO     |

|----------|----------|----------|----------|

| 8192 x 1 | 8192 x 1 | 8192 x 1 | 8192 x 1 |

| 4096 x 2 | 4096 x 2 | 4096 x 2 | 4096 x 2 |

| 2048 x 4 | 2048 x 4 | 2048 x 4 | 2048 x 4 |

| 1024 x 9 | 1024 x 9 | 1024 x 9 | 1024 x 9 |

| 512 x 18 | 512 x 18 | 512 x 18 | 512 x 18 |

| 256 x 36 | -        | 256 x 36 | 256 x 36 |

#### MachX0电压选择

#### sysI0缓冲支持高带宽的I/0标准

- LVCMOS / LVTTL

- Hotsocketing功能

- 可编程转换率

- 可编程驱动强度

- 可编程上拉、下拉,总线友好

- 可编程漏极开路

- 可编程施密特单元

- PCI, LVDS, LVPECL, Bus-LVDS, RSDS

### sysCLOCK锁相环框图

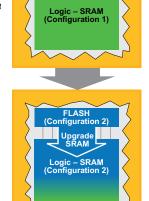

#### 易于现场更新

MachXO可编程逻辑器件支持莱迪思的专用透明的现场重新配置(TransFR)技术。 TransFR技术使得能够在现场更新逻辑,而 无需中断系统的运行。

Step 1 Program Flash in background while logic functions

Step 2 Precisely control

JTAG.

I/Os and initiate Flash to SRAM transfer through

FLASH

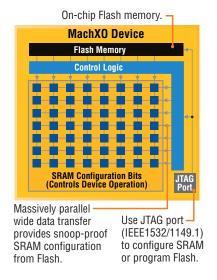

#### MachXO配置

MachXO可编程逻辑器件同时采用闪存和SRAM的技术,在一个低成本的器件上提供"即时启动"功能。上电时,在不到1毫秒的时间内,配置数据从闪存传送到SRAM单元。可从JTAG端口对SRAM和闪存编程。通过莱迪思的独特TransFR技术,这种SRAM和闪存的组合能够方便地进行现场更新。 MachXO PLD拥有一个防止回读的安全方案,通过使用内部的闪存,莱迪思消除了窥探位流的可能性。

### MachXO休眠模式下功耗减少100倍!

| 特性                | 普通模式     | 关闭                | 睡眠模式               |

|-------------------|----------|-------------------|--------------------|

| SLEEPN引脚          | 高        | Х                 | 低                  |

| 静止I <sub>cc</sub> | 典型值<10mA | 0                 | 典型值<100 μ A        |

| 电源                | 正常范围     | 0                 | 正常范围               |

| 逻辑操作              | 用户定义     | 不工作               | 不工作                |

| I/O操作             | 用户定义     | 三态<br>( <1mA漏电流 ) | 三态<br>(<10 µ A漏电流) |

## MachXO应用实例

#### 灵活的多电压电平转换

#### 上电和控制

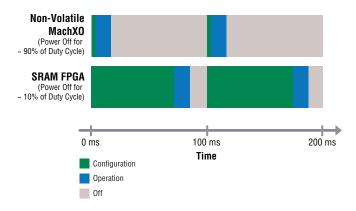

#### 低功耗循环工作

#### 免费、易于使用的莱迪思软件

Lattice Diamond®设计软件为MachXO架构和其他器件系列提供了全面的设计环境。Diamond具有设计探索、易于使用、改进的设计流程,以及许多其他的增强功能。Diamond使得用户能够更快、更方便地完成设计,并获得比以往更好的结果。

#### 评估和开发电路板

莱迪思提供了一些评估和开发板,从而提供一个完整的且易于使用的平台来评估MachXO的性能,也有助于定制设计的开发。

#### 参考设计组合

针对低密度应用,莱迪思提供了IP核扩展产品系列和参考设计。对MachXO的结构进行了优化,其中包括流行的协议和连接标准,如I2C、SPI,UART和PCI标准。可从莱迪思的网站免费下载参考设计,源代码和文档。欲了解更多的信息,请访问www.latticesemi.com/IP.

#### MachX0迷你开发套件

使用MachXO迷你开发套件,能够在几分钟 内测试I2C、SPI、UART,SRAM接口,以及 8位LatticeMico8™微控制器。在不到不到 1小时的时间内用莱迪思的免费参考设计构 建自己的设计。欲了解更多信息,请访问 www.latticesemi.com/machxo-mini.

#### MachX0控制开发套件

使用MachXO控制开发套件测试电路板的诊断功能,包括与Power Manager II POWR1014A和8位

LatticeMico8 微控制器一起使用的基于温度监测的风扇转速控制,完整的电源监控和复位分配。测试这些功能只需几分钟,使用莱迪思的免费参考设计在不到一个小时内构建立你

自己的设计。欲了解更多的信息,请访问

www.latticesemi.com/machxo-control-kit.

#### 器件选型指南

| 价 [T. 22] 11 [F] |                   |                   |                   |                   |  |  |  |

|------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|--|--|--|

| 参数                                                   | LCMX0256          | LCMXO640          | LCMX01200         | LCMX02280         |  |  |  |

| LUT                                                  | 256               | 640               | 1200              | 2280              |  |  |  |

| 分布式RAM(Kbit)                                         | 2                 | 6.1               | 6.4               | 7.7               |  |  |  |

| 嵌入式RAM块——EBR(Kbit)                                   | -                 | _                 | 9.2               | 27.6              |  |  |  |

| EBR块的数量                                              | -                 | _                 | 1                 | 3                 |  |  |  |

| V <sub>cc</sub> 电压(V)选择                              | 1.2V或1.8/2.5/3.3V | 1.2V或1.8/2.5/3.3V | 1.2V或1.8/2.5/3.3V | 1.2V或1.8/2.5/3.3V |  |  |  |

| PLL的数量                                               | -                 | _                 | 1                 | 2                 |  |  |  |

| I/O Bank的数量                                          | 2                 | 4                 | 8                 | 8                 |  |  |  |

| 最多I/O数量                                              | 78                | 159               | 211               | 271               |  |  |  |

| 最多的LVDS对*                                            | -                 | _                 | 27                | 33                |  |  |  |

| 封装和I/O组合                                             |                   |                   |                   |                   |  |  |  |

| 100引脚TQFP (14 x 14 mm)**                             | 78                | 74                | 73                | 73                |  |  |  |

| 144引脚TQFP (20 x 20 mm)                               |                   | 113               | 113               | 113               |  |  |  |

| 100球型csBGA (8 x 8 mm)                                | 78                | 74                |                   |                   |  |  |  |

| 132球型csBGA (8 x 8 mm)                                |                   | 101               | 101               | 101               |  |  |  |

| 256球型caBGA (14 x 14 mm)                              |                   | 159               | 211               | 211               |  |  |  |

| 256球型ftBGA (17 x 17 mm)                              |                   | 159               | 211               | 211               |  |  |  |

| 324球型ftBGA (19 x 19 mm)                              |                   |                   |                   | 271               |  |  |  |

<sup>\*</sup> LVDS输出的数量可以通过使用外部电阻进行模拟后增加。

#### 应用支持

1-800-LATTICE (528-8423) (503) 268-8001

techsupport@latticesemi.com

Lattice Semiconductor Corporation 2013版权⑤。Lattice Semiconductor、L(设计图案)Lattice Semiconductor Corporation、Lattice(设计)、ispLEVER、ispVM、LatticeMico8、MachXO、sysCLOCK、sysIO、sysMEM,和 TransFR及特定的产品名称均为莱迪思半导体公司或其在美国和/或其它国家的子公司的注册商标或商标。本出版物中提到的其它产品名称仅作识别目的,它们可能是其各自所有公司的商标。

2013年1月 订购编号: I0176HC

<sup>\*\*</sup>使用100引脚TQFP封装的设计不能从LCMXO640迁移到1200。