# LatticeXP2 sysCONFIG 使用ガイド

## はじめに

LatticeXP2<sup>™</sup> FPGAにはSRAMセルと共にフラッシュセルを用いてメモリが構築されており、パワーアップ時やユーザがデバイスを更新したい時はいつでも、コンフィグレーション・メモリに自動的にロードすることができるようになっています。"インスタントオン"機能に加えて、オンチップ・フラッシュメモリはコンフィグレーション・ビットストリームが外部に出ないことによって、設計のセキュリティが増大します。一方で、SRAMベースFPGAの使いやすさと再プログラム性を維持します。

LatticeXP2はさらなるセキュリティとして、フラッシュメモリの内容を保護するために暗号化キーの使用をサポートします。またLatticeXP2は、フラッシュメモリが消去されたり、再プログラムされる事から守るために、ワンタイム・プログラム(OTP)機能の使用もサポートします。

外部デバイスは不要ですが、LatticeXP2は複数の外部コンフィグレーション・モードをサポートします。利用できる外部コンフィグレーション・モードは以下の通りです。ンフィグレーション・モードは以下の通りです。

- ・スレーブSPI

- ・マスタSPI

- ・ ispJTAG TM (1149.1インターフェイス)

このガイドはLatticeXP2で利用できるすべてのコンフィグレーション・オプションをカバーします。

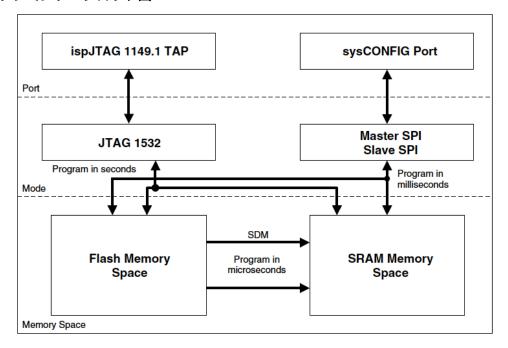

# プログラミング概要

LatticeXP2は2種類のメモリ、SRAMおよびフラッシュを含んでいます(図14-1を参照)。SRAMは本質的には回路の接続を定義する"ヒューズ"で、FPGAコンフィグレーション情報を保持します。フラッシュはコンフィギュレーション・データ用に不揮発性の内部記憶領域を提供します。

またLatticeXP2は、タグ(Tag)メモリ及びユーザ用フラッシュメモリとして使用される付加的なフラッシュメモリ領域を含んでいます。タグメモリはいわゆるスクラッチパッド(メモ書き用)メモリで、ユーザが極めて重要なデータや、ボードのシリアル番号、改版情報、識別パターンのプログラム、またはその他情報の格納のために利用できます。ユーザ・フラッシュメモリは、ユーザが望む場合にはEBR RAMモジュールの内容をバックアップするために利用できます。本ドキュメントの後ろのセクションでこれらの機能についてさらに詳細に議論します。

SRAMは、JTAGを用いるか、外部マスタSPIポート、またはオンチップ・フラッシュに格納されているデータを使用することによってコンフィグレーションできます。コンフィギュレーション・プロセスはSRAM初期化(RAMとアドレス・ポインタのクリア)、コンフィギュレーション・データのSRAMへのロード、そしてユーザモードにFPGAを設定(FPGAをウェイクアップ)することから成ります。

JTAGを用いるか、または外部スレーブSPIポートを用いることによって、オンチップ・フラッシュをプログラムすることができます。デバイスがパワーアップされている時はいつでもJTAGフラッシュ・プログラミングを実行することができます。スレーブSPIポートはsysCONFIG™ピンを用いており、直接またはバックグランドでフラッシュをプログラムすることができます。ダイレクト(直接)プログラミングはコンフィグ・モード時、バックグランド・プログラミングはユーザモード時に実行されます。FPGAはパワーアップ時にPROGRAMNピンがLowにされるか、またはJTAGを通してリフレッシュ・コマンドが発行される時、コンフ

LatticeXP2 14-1 sysCONFIG UGJ

TN1141\_1.4J1 Nov. 2008

ィグレーション・モードに入ります。ウェイクアップすると、すなわちデバイスがユーザ回路の動作を始める時に、ユーザモードに入ります。ダイレクトとバックグランドのこれら2モードは、このドキュメントでは"フラッシュ・ダイレクト"と"フラッシュ・バックグランド"と呼ぶことにします。

図14-1 プログラミング・ブロック図

# コンフィグレーション・ピン

LatticeXP2デバイスは2つのタイプ(専用とデュアル・ファンクション)のsysCONFIGピンをサポートします。 それらがコンフィグレーションに用いられない場合、デュアル・ファンクションのピンは汎用I/Oピンとして利用できます。

プログラマブル・オプションと共に、2本のコンフィグレーション・モードピンがデュアル・ファンクションのコンフィグレーション・ピンを制御します。コンフィグレーション・モードピン(CFG[1:0])は、通常PCBで固定配線され、どのコンフィグレーション・モードが用いられるかを決定します。ラティスispLEVER® デザイン・ソフトウェアか、HDLソースファイル・アトリビュートによるプリファレンスでプログラマブル・オプションを指定します。これにより、ユーザや配置配線ソフトウェアがコンフィグレーション・ピンを使用してしまうことから保護することができます。また、LatticeXP2デバイスはispJTAGによるコンフィグレーションをサポートしますが、JTAGポートはトランスペアレント・リードバックやJTAGテストにも用いられます。以下のセクションはsysCONFIGとJTAGピンの機能について説明します。JTAGとispJTAGは本書では同じ意味で用いていることに留意してください。表14-1を参考として示します。

# sysCONFIGピン

以下はLatticeXP2デバイスのsysCONFIGピンに関する記述です。これらはコンフィグレーション・プロセスを制御、或いはモニタするために用いられ、非JTAGプログラム・シーケンスのみで用いられます。JTAGピンは本ドキュメントのispJTAGピンの節で説明されます。

LatticeXP2 14-2 sysCONFIG UGJ

TN1141 1.4J1 Nov. 2008

表14-1 LatticeXP2デバイスのコンフィグレーション・ピン1

| ピン名      | VO タイプ                | ピンタイプ                     | 用いられるモード       |

|----------|-----------------------|---------------------------|----------------|

| CFG0     | 弱いプルアップの入力            | 専用                        | 全て             |

| CFG1     | 弱いプルアップの入力            |                           | MSPI, SSPI     |

| PROGRAMN | 弱いプルアップの入力            | デーマル コーン・ケン・              | MSPI, SSPI     |

| INITN    | 弱いプルアップの双方向オープン・ドレイン  | デュアル・ファンクション <sup>2</sup> | MSPI, SSPI     |

| DONE     | 弱いプルアップがある双方向オープン・ドレイ |                           | MSPI, SSPI     |

| DONL     | ン、またはアクティブなドライブ出力     |                           | MOFI, OOFI     |

| CCLK     | 入力、または出力              |                           | MSPI, SSPI     |

| SISPI    | 入力、または出力              |                           | MSPI, SSPI     |

| SOSPI    | 入力、または出力              | デュアル・ファンクシ<br>ョン          | MSPI, SSPI     |

| CSSPISN  | 弱いプルアップの入力            |                           | SSPI (スレーブSPI) |

| CSSPIN   | 弱いプルアップの出力、トライステート    |                           | MSPI (マスタSPI)  |

| TDI      | 弱いプルアップの入力            |                           |                |

| TDO      | 出力                    | JTAG                      |                |

| TCK      | ヒステリシスのある入力           | JIAG                      |                |

| TMS      | 弱いプルアップの入力            |                           |                |

注: 1. 弱いプルアップは30uAから150uAの電流源から成ります。CFGとPROGRAMNのプルアップはV<sub>CC</sub>(コア)に追従し、TDI、TDO、およびTMSのプルアップはV<sub>CCJ</sub>に追従します。他のすべてのプルアップは、そのピンのV<sub>CCIO</sub>に追従します。

#### CFG[1:0]

コンフィグレーション・モードピンCFG0は弱いプルアップがある専用入力です。CFG1ピンは弱いプルアップがあるデュアル・ファンクションの入力ピンです。CFGピンは、LatticeXP2のコンフィグレーション・モード、即ちどんなタイプのデバイスからLatticeXP2をコンフィグレーションするか、を選択するために用いられます。パワーオン・リセット(POR)かそれともPROGRAMNピンがLowにドライブされるとき、デバイスはCFG[1:0]ピンによって選択されるコンフィグレーション・モードに入ります。

表14-2 LatticeXP2のコンフィグレーション・モード

| コンフィグレーション・モード      | CFG[1] | CFG[0] |

|---------------------|--------|--------|

| SPIフラッシュブート         | 0      | 0      |

| エンベデッド・フラッシュ・ブート    | 1      | 0      |

| セルフ・ダウンロード・モード(SDM) | X      | 1      |

CFG0ピンがHighのとき、デバイスはオンチップ・フラッシュに格納されたデータを読むことで、自らをコンフィギュレーションします。これはSDM、またはSelf Download Mode (セルフ・ダウンロード・モード)と呼ばれます。SDMに関する詳しい情報は、このドキュメントの "セルフ・ダウンロード" セクションを参照してください。CFG0ピンがLowのとき、デバイスはどのモードに入るべきかを決定するために、CFG1ピンを読みます。CFG1がLowのとき最初にデバイスが試みるのは、マスタSPIモードを用いて外付けSPIフラッシュポートによるSRAMのコンフィギュレーションです。これが失敗すると、コンフィグレーション・ファイルが格納されていれば、オンチップ・フラッシュからデバイス自身をコンフィギュレーションします。CFG1がHighのとき最初にデバイスが試みるのは、オンチップ・フラッシュを用いるSRAMのコンフィギュレーションです。コンフィグレーション・ファイルが格納されていない場合、マスタSPIモードを用いて外付けSPIフラッシュポートを介してコンフィギュレーションします。

LatticeXP2 14-3 sysCONFIG UGJ

<sup>2.</sup> CFG0ピンがLowのとき、このピンは専用のプログラミング・ピンになります。

## デュアル・ファンクションのsysCONFIGピン

以下は、デュアル・ファンクションのsysCONFIGピンのリストです。これらのピンはコンフィグレーション後に汎用I/Oとして利用できます。デュアル・ファンクションのコンフィグレーション・ピンを汎用I/Oとしても用いる場合、ユーザは以下の事項を守らなければなりません。

- ・I/Oタイプは同じでなければなりません。即ち、コンフィグレーション時に、ピンが3.3V CMOSピン(LVCMOS33)であるなら、GPIOとしてもCMOS33でなければなりません。

- ・PERSISTENTオプションをOFFに設定しなければなりません。ユーザがispLEVERのデザインプランナを用いてSLAVE\_SPI\_PORTをENABLEに設定しない限り、PERSISTENTオプションはソフトウェアによってOFFに設定されます。このオプションはデザインプランナのSpeadsheetビュー、Globalタブに表示されます。

- ・ユーザはどんな内部、または外部論理もデバイス・コンフィグレーションを妨げないことを保証する責任があります。

コンフィグレーション後、GPIOとして用いられない場合、これらのピンはトライステートになり、弱くプルアップされます。

#### CFG1

CFG1ピンは弱いプルアップがあるデュアル・ファンクションの入力です。機能は上のセクションで説明されています。CFG0ピンがHighのとき、CFG1ピンはコンフィグレーションには用いられず、ユーザが利用できる汎用I/Oピンになります。

#### **PROGRAMN**

PROGRAMNは弱いプルアップがある入力専用ピンです。このピンは、非JTAG SRAMコンフィグレーション・シーケンスを開始するのに用いられます。PROGRAMNピンがHighからLowにされると、デバイスはコンフィグレーション・モードに入ります。PROGRAMNピンを用いることで、いつでもコンフィグレーションのトリガとすることができます。

PROGRAMNピンは、CFG0ピンが0に設定される(SDMモードでない)場合にのみ利用できます。CFG0ピンが 1 (High)のとき、PROGRAMNピンはユーザが利用できる汎用I/Oピンになります。

CFG0ピンが 0 (Low)のとき、PROGRAMNピンは専用のプログラミング用ピンになります。

#### INITN

INITNピンは弱いプルアップがある専用の双方向オープン・ドレイン・ピンです。INITNは外部からドライブされるLowパルスを検出すると共に、外部をLowパルスでドライブすることができます。

SRAMをコンフィギュレーションするために、SPIフラッシュブートかエンベデッド・フラッシュブート・モードを用いるとき、INITNがLowになるのは、SRAMが初期化されていることを示します。次にINITNがHighになると、FPGAはコンフィギュレーション・データを受け入れる準備ができていることを示します。コンフィグレーションを遅らせるために、外部的にINITNピンをLowに保持することができます。INITNピンがLowである限り、デバイスはコンフィグレーション・モードに入りません。コンフィグレーションが始まった後に、INITNはビットストリームの誤りを示すために用いられます。計算したCRCとコンフィギュレーション・データのCRCが一致しないと、INITNピンはLowにドライブされます。この場合DONEピンはLowのままで、LatticeXP2は起動しません。

SDMの場合でオンチップ・フラッシュからコンフィグレーションする場合、INITNは使用されず、またモニタされません。

オンチップ・フラッシュをプログラムするとき、INITNピンは用いられません。フラッシュ・ダイレクト・プログラミング時のエラーは、フラッシュからFPGAをコンフィグレーションすることを妨げます。フラッシュ・バックグランド・プログラミング時のエラーは、既に動作しているSRAMでのコンフィグレーション

LatticeXP2 14-4 sysCONFIG UGJ

には影響しません。

INITピンは、CFG0ピンが0に設定される(SDMモードでない)場合にのみ利用できます。CFG0ピンが1(High) のとき、INITNピンは汎用I/Oピンになり、ユーザが使用できます。

CFG0ピンが0(Low)のとき、INITNピンは専用のプログラミング用ピンになります。

#### DONE

DONEピンは弱いプルアップがある専用の双方向オープン・ドレイン(デフォルト)、あるいはアクティブ・ドライブできるピンです。デバイスがコンフィグレーション・モードにあり、内部Doneビットがプログラムされていない際に、DONEピンはLowにドライブされます。INITNとPROGRAMNピンがHighになり、内部DONEビットがプログラムされると、DONEピンは解除(或いは、アクティブ・ドライブであるならHighに)されます。外部からDONEピンをLowに保持することもでき、選択されたウェイクアップ・シーケンスによっては、DONEピンが外部的にHighにされるまで、デバイスは動作を開始しません。

DONEビットを読み出すことは、FPGAが構成されたかどうかを外部デバイスが知る良い方法です。

SRAMをコンフィグレーションするためにJTAGを用いるとき、DONEピンはバウンダリ・スキャンセルによってドライブされるため、コンフィグレーションが完了するまでDONEピンは意味がありません。

DONEピンはCFG0ピンが0に設定される(SDMモードでない)場合にのみ利用できます。CFG0ピンが1 (High) のとき、DONEピンは汎用I/Oピンになり、ユーザが使用できます。

CFG0ピンが0に設定されるとき、DONEピンは専用のプログラミング・ピンになります。

#### CCLK

CCLKは双方向ピンで、方向はマスタモードかスレーブモードのどちらが選択されるかに依存します。マスタモードがCFGピンによって選択されると、CCLKピンは出力になりますが、そうででなければ、CCLKは入力ピンです。

CCLKピンが出力になると、内部プログラマブル・オシレータはCCLKに接続され、外部スレーブデバイスをドライブします。CCLKは、DONEピンがHighにされ、デバイスのウェイクアップ・シーケンスが完了した後に100~500クロック周期で止まります。付加的なクロック周期により、チェインにある他のデバイスがウェイクアップするのに十分なクロックが提供されることを確実にします。止まると、CCLKは入力(トライステート出力)になります。CCLKは次のコンフィグレーション初期化シーケンスで再開し(出力になり)ます。

MCCLK\_FREQパラメータ(ispLEVERのデザインプランナにおけるグローバル設定の1つ)はCCLKマスタ周 波数を制御します。(指定できる周波数選択に関してはLatticeXP2ファミリ・データシートのオンチップ・オシレータ・セクションを参照して下さい。)コンフィグレーションCCLKのソフトウェア・デフォルト設定は 2.5MHzです。コンフィグレーション時にロードされる最初のものの1つはMCCLK\_FREQパラメータです。一度、このパラメータがロードされると、周波数は選択された値へ変化します。スレーブデバイスの周波数 仕様や、PCBレイアウトの信号インテグリティ機能を超えないように注意が必要です。

#### **CSSPIN**

CSSPINピンは弱いプルアップがあるデュアル・ファンクションの出力ピンです。マスタSPIモードで用いられると、CSSPINは外付けSPIフラッシュへのLowアクティブ・チップセレクトです。CSSPINピンは、CFG0ピンが0に設定される(SDMモードでない)場合、専用ピンになります。CFG0ピンが1 (High)のとき、CSSPINピンは汎用I/Oピンになり、ユーザが使用できます。

CFG0が0に設定される場合、マスタSPIモードでない限りは、マスタSPIモードとスレーブSPIモード間のコンテンションを避けるために、このピンはHighにドライブされるべきです。

LatticeXP2 14-5 sysCONFIG UGJ

#### **CSSPISN**

CSSPISNピンは弱いプルアップがあるデュアル・ファンクションの入力ピンです。CSSPISNは内部のSPIインターフェイスへのLowアクティブ・チップセレクトで、スレーブSPIモードと共に用いられます。

CSSPISNがマスタSPIポート動作の最中にLowにドライブされた場合、マスタSPIを無効にし、かつスレーブ SPIインターフェイスをアクティブにすべきです。

このピンをCSSPISNとして確保して、スレーブSPIインターフェイスへのアクセスを可能にするために、 PERSISTENTプリファレンスをONに設定しなければなりません。ユーザがデザインプランナで SLAVE\_SPI\_PORTオプションをセットすると、PERSISTENTプリファレンスはソフトウェアによって自動 的に設定されます。

#### SISPI

SISPIピンはデュアル・ファンクションの双方向ピンです。方向はマスタモードかスレーブモードのどちらが有効かに依存します。SISPIはスレーブSPIモードを用いるときには入力データピンで、マスタSPIモードを用いるときは出力データピンです。

このピンをSISPIとして確保して、スレーブSPIインターフェイスへのアクセスを可能にするために、 PERSISTENTプリファレンスをONに設定しなければなりません。ユーザがデザインプランナで SLAVE\_SPI\_PORTオプションをセットすると、PERSISTENTプリファレンスはソフトウェアによって自動 的に設定されます。

#### SOSPI

SOSPIピンはデュアル・ファンクションの双方向のピンです。方向はマスタモードかスレーブモードのどちらが有効かに依存します。SOSPIはマスタSPIモードを用いるときは入力データピンで、スレーブSPIモードを用いるときは出力データピンです。

このピンをSOSPIとして確保してスレーブSPIインターフェイスへのアクセスを可能にするために、 PERSISTENTプリファレンスをONに設定しなければなりません。ユーザがデザインプランナで SLAVE\_SPI\_PORTオプションをセットすると、PERSISTENTプリファレンスはソフトウェアによって自動 的に設定されます。

| SLAVE_SPI_PORTオプションをセットすると、PER<br>的に設定されます。 | SISTENTプリファレン | ′スはソフトウュ | ェアによって自動 |

|---------------------------------------------|---------------|----------|----------|

| 表14-3 フラッシュプログラミング・モードピンの使                  | U方            |          |          |

| フラッシュ・プロゲラミン                                |               |          |          |

| フラッシュ・プログラミン<br>  グ・モード   | ダイレクト             | バックグランド             | ダイレクト            | バックグランド           |

|---------------------------|-------------------|---------------------|------------------|-------------------|

| ポート <sup>6</sup>          | スレー               | ·ブSPI               | isp              | JTAG <sup>1</sup> |

| ピン                        | CCLK, CSSPISI     | N, SISPI, SOSPI     | -                | ΓΑΡ               |

| ユーザI/Oステータス               | トライステート           | ユーザ                 | BSCAN            | ユーザ               |

| PROGRAMN                  |                   | Highを保持             | High             | を保持 <sup>2</sup>  |

| INITN                     | 成功(pass)/失敗(fail) | 成功(pass)/失敗(fail)   | 未使用 <sup>3</sup> |                   |

| DONE                      | Done              | 未使用                 | High             | を保持 <sup>4</sup>  |

| SLAVE_SPI_PORT<br>プリファレンス | 無視 <sup>1 5</sup> | ENABLE <sup>5</sup> | ;                | 無視                |

- 1, CFGピンのステートにかかわらず、フラッシュをプログラムするためにispJTAGを用いることができます。

- 2. JTAGフラッシュ・プログラミングの間、PROGRAMNピンのステートをデバイスは無視しますが、このピンがLowだとコンフィグレーションの失敗を引き起こすため、Highにされている必要があります。デバイスがSDMモードにあるときはPROGRAMNピンは専用I/Oピンであるので、これはコンフィグレーションに影響しません。

- 3. JTAGフラッシュ・プログラミングの間INITNピンのステートをデバイスは無視しますが、このピンは内部プルアップ抵 抗を用いてHighになるようにする必要があります。デバイスがSDMモードにあるときINITNピンは専用のI/Oピンであるの で、これはコンフィグレーションに影響しません。

LatticeXP2 14-6 sysCONFIG UGJ

- 4. DONEピンのステートはJTAGフラッシュ・プログラミングの間デバイスによって無視されますが、ピンをLowにすることでデバイスがウェイクアップすることを妨げるので、内部プルアップ抵抗でHighになるようにする必要があります。デバイスがSDMモードにあるときDONEピンは専用のI/Oピンであるので、これはコンフィグレーションに影響しません。

- 5. デバイスがコンフィギュレーションされた後にスレーブSPIポートを用いるためには、SLAVE\_SPI\_PORTプリファレンスをENABLEに設定しなければなりません。また、デバイスがコンフィギュレーションされていないときでも、スレーブSPIポートは利用できます。

- 6. ダイレクトモードで外付けSPIフラッシュメモリからSRAMをコンフィギュレーションするためには、マスタSPIポートのみが使用できます。このモードを有効にするためには、表14-2に従ってCFGピンを設定しなければなりません。

表14-4 メモリアクセス・モード

| モード     | フラッ              | ソシュ              | SR  | AM               |

|---------|------------------|------------------|-----|------------------|

|         | リード              | ライト              | リード | ライト              |

| スレーブSPI | Yes <sup>2</sup> | Yes <sup>1</sup> | Yes | No               |

| マスタSPI  | No               | No               | No  | Yes <sup>3</sup> |

- 1, フラッシュメモリが消去されていなければ、スレーブSPIモードはバックグラウンドモードでオンチップ・フラッシュメモリのみに書き込みできます。

- 2. スレーブSPIモードは、バックグランド・モードでのみオンチップ・フラッシュメモリから読み出すことができます。

- 3. マスタSPIモードではダイレクトモードのみSRAMにライトすることができます。

#### 外付けSPIフラッシュ

マスタSPIモードがコンフィグレーションに用いられるとき、外付けSPIフラッシュ・デバイスが、コンフィギュレーション・データを保持するのに必要です。ビットストリームと必要な外付けSPIフラッシュのサイズは表14-5に示されています。

表14-5 最大コンフィグレーション・ビットサイズ

| デバイス   | ビットストリームサイズ (Mb) | SPIフラッシュサイズ (Mb) |

|--------|------------------|------------------|

| XP2-5  | 1.27             | 2                |

| XP2-8  | 1.99             | 2                |

| XP2-17 | 3.54             | 4                |

| XP2-30 | 5.79             | 8                |

| XP2-40 | 8.03             | 16               |

# プログラミング・シーケンス

2つのタイプのプログラミング、SRAM、およびフラッシュ・バックグランドがあります。このセクションは、 専用ピンがどう使用されるかを、それぞれのプロセスについて見ていきます。

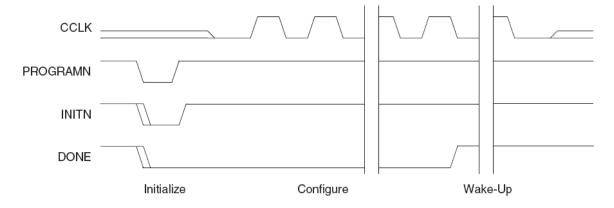

## SRAM

SRAMのコンフィグにSDMを使用しない場合、内部パワーオン・リセット(POR)がリリースされるか、またはPROGRAMNピンがLowにドライブされるとシーケンスが始まります(図14-2を参照)。LatticeXP2はINITNをLowにドライブし、I/Oをトライステートにし、内部のSRAMと制御ロジックを初期化します。これが完了すると、PROGRAMNがHighであれば、INITNはリリースされます。INITNが外部的にLowに保持されていると、LatticeXP2はHighになるまで待ち、その後LatticeXP2はCFGピンで決定される選択されたコンフィグレーション・ポート上でコンフィギュレーション・データ・プリアンブルを探し始めます。

CFG1ピンがHighで、(デバイス内部のオンチップ・フラッシュメモリがプログラムされたことを示す)Flash Doneビットがセットされると、LatticeXP2がオンチップ・フラッシュメモリからブートします。Flash Done

LatticeXP2 14-7 sysCONFIG UGJ

ビットがセットされないと、LatticeXP2は外付けSPIフラッシュメモリからマスタSPIモードを用いることでプートします。

CFG1ピンがLowの時は、LatticeXP2は外付けSPIフラッシュメモリからマスタSPIモードを用いることでブートします。エラーの場合、もしFlash Doneビットがセットされると、LatticeXP2はオンチップ・フラッシュメモリからブートします。

コンフィグレーションがいったん完了すると、内部Doneビットはセットされ、DONEピンはHighになり、FPGAは起動し(ユーザモードに入り)ます。ビットストリームを読むときにCRC誤りが検出されると、INITNはLowになり、内部Doneビットはセットされないで、DONEピンはLowのままで、LatticeXP2はウェイクアップしません。

SRAMのコンフィグレーションにSDMを使用する場合、INITが使用されない、またモニタされない以外はシーケンスは同様です。内部パワーオン・リセット(POR)がリリースされるか、またはPROGRAMNピンがLowにドライブされるとシーケンスが始まります。LatticeXP2はI/Oをトライステートにし、内部のSRAMと制御ロジックを初期化します。これが完了するとLatticeXP2はオンチップ・フラッシュからコンフィグレーション・データのロードを開始します。

SDMを使用する場合、フラッシュが既にプログラムされていると、オンチップ・フラッシュのデータを用いてコンフィグレーションが進行します。もし、フラッシュがまだプログラムされていないと、コンフィグレーションは停止します。一度フラッシュがプログラムされた後、コンフィグレーション・シーケンスを再開するためにはPOR(パワーオンリセット)かJTAGのリフレッシュ・コマンドが与えられなければなりません。

SDMモードの場合、コンフィグレーションが完了するとDoneビットがセットされ、FPGAがウェイクアップします。SDMコンフィグレーションを用いるとき、外部DONEピンは利用できません。

## 図14-2 SRAMコンフィグレーション・タイミング図

## フラッシュ・バックグランド

フラッシュ・バックグランド・プログラミングは、イネーブルされている場合、スレーブSPIポートを用いることで可能です。スレーブSPIポートは、SDMモード及びSPIモードでイネーブルすることが可能です。フラッシュ・バックグランドはSRAMにあるFPGAの現在のコンフィグレーションを妨げません。

フラッシュ・バックグランド・プログラミングはコンフィグレーション・モードとユーザモードの両方(Done ビットが0か1)で用いられます。ユーザモードでフラッシュ・バックグランド・プログラミングをサポートするためには、SLAVE SPI PORTプリファレンスをENABLEに設定しなければなりません。

LatticeXP2 14-8 sysCONFIG UGJ

CSSPISNがLowになると、FPGAはプリアンブルを待ち、そして適切なコマンドを探します。INITNがLowになるのは、フラッシュの消去やプログラミングの誤りを示します。データはSISPIとSOSPIピンでリードとライトされます。

フラッシュをプログラムした後に、SPIモードが用いられていればユーザはフラッシュ・データをSRAMに 転送するためにPROGRAMNピンをトグルすることができます。SDMモードを用いている場合、リフレッシュ命令が発行される次のパワーアップ・シーケンス時にSRAMをアップデートします。

CSSPISNピンがLowにドライブされる場合、マスタSPIモードに入ることを防ぐためにCSSPINはHighにしかつCCLKは入力として保持されなければなりません。これによりマスタ/スレープSPI両モードの競合を防ぎます。

## ispJTAGピン

ispJTAGピンは標準のIEEE1149.1 TAP(テスト・アクセス・ポート)ピンです。LatticeXP2デバイスがパワーアップされているとき、ispJTAGピンは専用ピンであり、常にアクセスできます。ispJTAGを通してSRAMをプログラムするとき、DONEなどのように、プログラミングの進捗を決定する専用プログラミング・ピンを用いることはできません。これはJTAG1149.1に従って、通常の内部ロジックではなくバウンダリ・スキャンセルのステートがピンをドライブするためです。

#### TDO

テストデータ出力ピンTDOは、シリアルのテスト命令とデータをシフトアウトするために用いられます。 TDOが内部回路によってドライブされていないとき、ピンはハイインピーダンス・ステートにあります。

#### TDI

テストデータ入力ピンは、シリアルのテスト命令とデータをシフト入力するのに用いられます。TDIピンには内部プルアップ抵抗があり、V<sub>CCJ</sub>にプルアップされています。

## **TMS**

テストモード選択ピンはTAPコントローラのテスト動作を制御します。TCKの立ち下がりエッジで、TMSのステートによって、TAPコントローラ・ステートマシンは状態遷移します。TMSピンには内部プルアップ抵抗があり、Vcc」にプルアップされています。

#### **TCK**

テストクロック・ピン(TCK)は、データ及び命令レジスタをロード、アンロードするTAPコントローラを動作させるためのクロックを提供します。TCKはHighかLowの状態で止めることができ、デバイス・データシートで示された周波数まで上げることができます。TCKピンはヒステリシスをサポートしており、値はデータシートのDCパラメータ表に示されます。TCKピンには、プルアップがありません。 $V_{CC}$ が立ち上がる際にTAPコントローラが不注意にクロッキングされるのを避けるため、PCB上に4.7Kプルダウン抵抗を置くことを推奨します。

#### $V_{CCJ}$

JTAG VCC ( $V_{CCJ}$ )は独立した電圧をJTAGポートに供給し、共通の電圧の他デバイスとJTAGチェインを作ることを可能にします。JTAGが使用されていなくても、 $V_{CCJ}$  を接続しなければなりません。また、この電圧はJTAGダウンロード・ケーブルにも供給されます。有効な電圧レベルは、3.3Vと、2.5V、1.8V、1.5V、そして1.2Vです。

さらなるJTAGチェイン情報は、www.latticesemi.comのラティス・ウェブサイトより入手できる、"In-System Programming Design Guidelines for ispJTAG Devices" を参照してください。

LatticeXP2 14-9 sysCONFIG UGJ

## コンフィグレーションとJTAG電圧レベル

制御ピンとプログラミング・ピンのすべてがLVCMOSをデフォルトとします。CFG0は $V_{CC}$  (core)に接続されます。TCK、TDI、TDO、およびTMSは $V_{CCJ}$  に追従します。他のすべてのピンがそのピン用の $V_{CCIO}$  に追従します。

# コンフィグレーション・モードとオプション

LatticeXP2デバイスはSPIポートやセルフ・コンフィグレーションを利用して、2つのコンフィグレーション・モードをサポートします。パワーアップ時、またはPROGRAMNピンがLowにドライブされると、LatticeXP2デバイスのコンフィグレーションに用いられるモードを決定するためにCFG[1:0]ピンがサンプルされます。CFGピンは通常PCB上で固定配線されており、デバイスがコンフィギュレーション・データを得るのにどのポートを用いるかを決定します。SLAVE\_SPI\_PORTは、ラティスispLEVERデザイン・ソフトウェアのデザインプランナを用いるか、HDLソースファイル・アトリビュートとして設定でき、コンフィグレーション・ピンをユーザや配置配線ソフトウェアが期せずして使用してしまうことがないように、ユーザは保護できます。

## コンフィグレーション・オプション

各コンフィグレーション・モードには複数のオプションがあります。

- ・マスタクロックを用いるとき、その周波数を設定することができます。

- · SRAMやフラッシュのリードバックを防ぐためにセキュリティ・ビットがあります。

ispLEVERデザイン・ソフトウェアで適切なパラメータを設定することにより、選択されたコンフィグレーション・オプションが生成されるビットストリームに設定されます。ビットストリームがデバイスにロードされる際に、選択されたコンフィグレーション・オプションは有効になります。これらのオプションは以下のセクションで説明されます。

#### マスタクロック

LatticeXP2がマスタデバイスになると、CCLKピンはユーザによって設定された周波数の出力になります。 デフォルトのマスタクロック周波数は2.5MHzです。

ユーザは、ispLEVERデザイン・ソフトウェアでMCCLK\_FREQプリファレンスを設定することによって、マスタクロック周波数を指定することができます。コンフィグレーション時に最初にロードされるものの一つはMCCLK\_FREQパラメータです。一度このパラメータがロードされると、周波数はグリッチのないスイッチを用いて選択された値へ変えられます。スレーブデバイスの周波数仕様や、PCBレイアウトの信号インテグリティ機能を超えないように注意します。

#### セキュリティ・ビット

セキュリティ・ビットを設定すると、JTAGやsysCONFIGピンからSRAMとフラッシュのリードバックすることを防ぎます。セキュリティ・ビットが設定されるとき、利用できる動作は消去と書き込みだけです。セキュリティ・ビットは、SRAMコンフィグレーションかフラッシュ・プログラミングの最後の動作としてアップデートされます。オンチップ・フラッシュを用い、かつセキュリティ・ビットを設定することによって、ユーザは非常に安全なデバイスを作成することができます。

セキュリティ・ビットはispLEVERのデザインプランナによってアクセスできます。

ラティスセミコンダクターのウェブサイトwww.latticesemi.comより入手できるドキュメント "FPGA Design Security Issues: Using the ispXPGA Family of FPGAs to Achieve Design Security" でデバイス・セキュリティに関する詳しい情報があります。

LatticeXP2 14-10 sysCONFIG UGJ

#### スレープSPIモード

スレーブSPIモードではCCLKピンは入力になり、SISPIピンのデータはCCLKの立ち上がりエッジでLatticeXP2に取り込まれます。データはLatticeXP2からSOSPIピンを通じてCCLKの立ち下がりで出力されます。

EBRかPFUメモリのリードバックの間、注意しなければなりません。これらのRAMを読むことでデータが確実にこわれないようにすることは、ユーザに委ねられています。すなわち、これらのRAMはユーザコードによってアクセスされている間、読むことができないかもしれません。

CSSPISNがSPIインターフェイスを有効にし、また無効にします。CSSPISNがHighのとき、SPIインターフェイスは選択が解除され、SOSPIピンはハイインピーダンスになります。CSSPISNがLowにされるとき、SPIインターフェイスは選択され、LatticeXP2にコマンドを書くことができて、またデータをLatticeXP2から読み出せます。パワーアップ後、新しいコマンドを受け付けることができるようになる前に、CSSPISNはHighからLowへ遷移しなければなりません。

また、オンチップ・フラッシュにアクセスするのにスレーブSPIモードを用いることができます。オンチップ・フラッシュに書くためにはCSSPISNピンをLowに保持しなければなりません。データはSISPIから入力されます。また、フラッシュとSRAMの両方のリードバックにスレープSPIモードを用いることができます。CSSPISNをLowにドライブすることによって、デバイスにはSISPIピンからのリードバック命令が入力され、そしてデータはSOSPIピンからライトされます。リードコマンド内のあるビットが、読み出しをフラッシュかSRAMかどうか決定します。デバイスがユーザモードにある間(DONEピンはHigh)のリードバックをサポートするためには、デザインプランナを用いてSLAVE\_SPI\_PORTプリファレンスをENABLEに設定しなければなりません。

## マスタSPIモード

マスタSPIモードでは、ビットストリームを提供するスレーブSPIデバイスのためにCCLK出力をドライブします。マスタデバイスはCCLKの立ち上がりエッジでSISPIにコマンドを出力し、立ち下がりクロックでSOSPIのデータを受け入れます。マスタシリアル・デバイスは、コンフィグレーションの開始から、外部のDONEピンがHighにドライブされるまで、そしてその後さらに100~500クロック周期の間、CCLKをドライブし続けます。パワーアップ時のCCLK周波数は2.5MHzをデフォルトとします。新しいクロック周波数がビットストリームからロードされるまで、マスタクロック周波数はデフォルトのままです。

## セルフ・ダウンロード・モード

セルフ・ダウンロード・モード(SDM)は、いかなる外部デバイスも用いないでFPGA自体をコンフィグレーションします。これはビットストリームが露出されないので、非常に安全なコンフィグレーション・モードです。ispJTAGかsysCONFIGピン上のスレーブSPIポートを用いることで、ユーザはオンチップ・フラッシュにアクセスすることができます。

デバイスがパワーアップされている間はいつでも、デバイス動作を妨げることなくJTAGを介してオンチップ・フラッシュにアクセスできます。また、JTAGはコンフィグレーションSRAMを読み書きもできます。オンチップのフラッシュとSRAMへのアクセスがJTAGのみに制限される場合、デュアル・ファンクションのピンを解放して汎用I/Oとして使用できるように、SLAVE\_SPI\_PORTはDISABLEに設定されるべきです。

## ispJTAGモード

ispJTAGポートを通してLatticeXP2デバイスをコンフィグレーションできます。選択されたコンフィグレーション・モードに係わらず、ispJTAGポートは常にオンであり、利用できます。JTAGポートが排他的に用いられること、すなわちSPIポートは用いられないことを配置配線ツールに通知するために、ispLEVERデザイン・ソフトウェアでSLAVE\_SPI\_PORTをDISABLEに設定します。これによりデュアル・ファンクションのピンすべてを汎用I/Oとして用いること可能になります。

LatticeXP2 14-11 sysCONFIG UGJ

#### ISC 1532

ispJTAGポートによるコンフィグレーションはIEEE 1532規格に準拠します。いかなる1532モード命令の間も、バウンダリ・スキャンセルがI/Oを制御します。JTAG1532モードを用いるときはいつでも、予め決められた値にバウンダリ・スキャンセルを設定することができます。このため、有効なコンフィグレーション・ステータスのためのDONEなどの専用ピンに頼ることはできません。

## トランスペアレント・リードバック

ispJTAGのトランスペアレント・リードバック・モードで、ユーザはデバイスが通常動作状態にあっても SRAMやフラッシュのデータを読み出すことが可能です。EBRと分散メモリ(RAM)を読み出すときは、注意 しなければなりません。ユーザデザインからのアクセスとの衝突を引き起こす(データが壊れる)可能性があるためです。

I/Oと非JTAGコンフィグレーション・ピンはトランスペアレント・リードバックの間、アクティブなままです。デバイスはJTAG命令によってトランスペアレント・リードバック・モードに入ります。

#### バウンダリ・スキャンとBSDLファイル

ラティス・ウェブサイトwww.latticesemi.comにデバイスのBSDLファイルがあります。バウンダリ・スキャンリングはI/Oピンのすべてと、専用およびのデュアル・ファンクションのsysCONFIGピンをカバーしています。

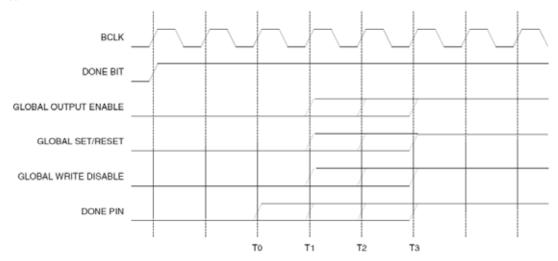

## ウェイクアップ(起動)オプション

コンフィグレーション(SRAMへのロード)が完了した後に、デバイスは予測できる形式でウェイクアップ(起動)するべきです。2つの同期ウェイクアップ・プロセスがあり、その選択でデバイスがどのように起動するかを決定します。1つは、DONEピンが外部的にLowに保持されるかどうかにかかわらず、内部Doneビットが設定されると自動的にデバイスを起動します。他方は、ウェイクアップ・プロセスを始める前にDONEピンがHighにドライブされるのを待ちます。DONE\_EXプリファレンスは、外部DONEピンが同期ウェイクアップを制御するかどうかを決定します。デバイスがSDMモードであるとき、DONEピンは使用されません。従ってDONE EXプリファレンスは無効です。

## ウェイクアップ・シーケンス

表14-6はLatticeXP2によってサポートされるウェイクアップ・シーケンスのリストを提供します。

LatticeXP2 14-12 sysCONFIG UGJ

TN1141\_1.4J1 Nov. 2008

表14-6 LatticeXP2によってサポートされるウェイクアップ・シーケンス

| シーケンス     | フェーズT0 | フェーズT1          | フェーズT2          | フェーズT3          |

|-----------|--------|-----------------|-----------------|-----------------|

| 1         | DONE   | GOE, GWDIS, GSR |                 |                 |

| 2         | DONE   |                 | GOE, GWDIS, GSR |                 |

| 3         | DONE   |                 |                 | GOE, GWDIS, GSR |

| 4         | DONE   | GOE             | GWDIS, GSR      |                 |

| 5         | DONE   | GOE             |                 | GWDIS, GSR      |

| 6         | DONE   | GOE             | GWDIS           | GSR             |

| 7         | DONE   | GOE             | GSR             | GWDIS           |

| 8         |        | DONE            | GOE, GWDIS, GSR |                 |

| 9         |        | DONE            |                 | GOE, GWDIS, GSR |

| 10        |        | DONE            | GWDIS, GSR      | GOE             |

| 11        |        | DONE            | GOE             | GWDIS, GSR      |

| 12        |        |                 | DONE            | GOE, GWDIS, GSR |

| 13        |        | GOE, GWDIS, GSR | DONE            |                 |

| 14        |        | GOE             | DONE            | GWDIS, GSR      |

| 15        |        | GOE, GWDIS      | DONE            | GSR             |

| 16        |        | GWDIS           | DONE            | GOE, GSR        |

| 17        |        | GWDIS, GSR      | DONE            | GOE             |

| 18        |        | GOE, GSR        | DONE            | GWDIS           |

| 19        |        |                 | GOE, GWDIS, GSR | DONE            |

| 20        |        | GOE, GWDIS, GSR |                 | DONE            |

| 21(デフォルト) |        | GOE             | GWDIS, GSR      | DONE            |

| 22        |        | GOE, GWDIS      | GSR             | DONE            |

| 23        |        | GWDIS           | GOE, GSR        | DONE            |

| 24        |        | GWDIS, GSR      | GOE             | DONE            |

| 25        |        | GOE, GSR        | GWDIS           | DONE            |

図14-3 内部クロックとウェイクアップ・シーケンス

#### 内部Doneビットに同期

LatticeXP2デバイスがチェインにおける唯一のデバイスである場合、またはチェインで最後のデバイスである場合、ウェイクアップ・プロセスはコンフィグレーションの完了で開始されるべきです。コンフィグレーションが完了すると、内部Doneビットがセットされ、次に、ウェイクアップ・プロセスが始まります。

## 外部DONE信号に同期

ウェイクアップを遅らせるためにDONEピンを選択することができます。DONE\_EXが真であると、DONE ピンがHighになるまでウェイクアップ・シーケンスは遅らせられ、そしてデバイスは選択されたWAKE\_UP シーケンスに従います。デバイスがSDMモードであるとき、DONEピンは使用されません。従ってDONE\_EX プリファレンスは無効です。

## ソフトウェアで選択可能なオプション

デフォルト設定を超えてLatticeXP2デバイスのコンフィグレーションを制御するために、ソフトウェア・プリファレンスが使用されます。表14-7はプリファレンスのリストをデフォルト設定と共に示します。

## 表14-7 LatticeXP2 ソフトウェア・プリファレンス・リスト

| プリファレンス名        | デフォルト設定 [全設定のリスト]         |

|-----------------|---------------------------|

| MASTER_SPI_PORT | DISABLE [disable, enable] |

| MASTER_SPI_PORT | DISABLE [disable, enable] |

| DONE_OD         | ON [off, on]              |

| DONE_EX         | OFF [off, on]             |

| MCCLK_FREQ      | Lowest Frequency          |

| CONFIG_SECURE   | OFF [off, on]             |

| WAKE UP         | 21 (DONE_EX = off)        |

| VVARE_UP        | 4 (DONE_EX = on)          |

| WAKE_ON_LOCK    | OFF [off, on]             |

| INBUF           | ON [off, on]              |

## スレーブSPIポート

ユーザモード中にSRAMやフラッシュ・メモリをリードするためにスレーブSPIポートを用いるには、SLAVE\_SPI\_PORTプリファレンスをENABLEに設定する必要があります。こうすることでFPGAが外部デバイスからアクセスできるように、スレーブSPIポートのピンを確保します。また、ソフトウェアに対してスレープSPIポートが確保され、フィッタやユーザが使用できないことを知らせます。

#### マスタSPIポート

コンフィグレーションにマスタSPIポートを用いるためには、MASTER\_SPI\_PORTプリファレンスをENABLEに設定します。

## コンフィグレーション・モード

デバイスは、CFG[1:0]のステートを読み込むことで物理的にsysCONFIGポートが用いられることがわかっていますが、フィッタ・ソフトウェアもどのポートが用いられるかを知る必要があります。フィッタは基本的にSLAVE\_SPI\_PORTおよびMASTER\_SPI\_PORTプリファレンスの設定によって、コンフィグレーション・モードを決定します。ユーザは、これらや以下にリストアップするプリファレンスを、デザインプランナを用いて設定する事ができます。

ソフトウェアによって設定される他のコンフィグレーション・オプションとしてはオーバフローなど幾つかあります。これらのオプションは、ispLEVERで "Generate Bitstream Data" プロセスを右クリックし

LatticeXP2 14-14 sysCONFIG UGJ

"Properties" を選択することによって設定できます。オーバフロー・オプションが選択されると、DONE\_EXとWAKE\_UP選択がこれに相当するように設定されます(表14-8を参照)。詳細についてはドキュメントの"コンフィグレーション・モードとオプション"セクションを参照してください。

表14-8 オーバフロー・オプションのデフォルト

| オーバフロー・オプション | DONE_EXプリファレンス    | WAKE_UPプリファレンス              |

|--------------|-------------------|-----------------------------|

| Off          | Off (デフォルト)       | Default 21 (ユーザ選択可、1 から 25) |

| Off          | On                | Default 21 (ユーザ選択可、1 から 25) |

| On (いずれか)    | ON (ソフトウェアが自動で設定) | Default 4 (ユーザ選択可、1 から 7)   |

## DONE オープン・ドレイン

DONE\_ODプリファレンスで、ユーザはオープン・ドレインとしてDONEピンを構成します。DONE\_ODプリファレンスはDONEピンのみに用いられます。DONEピンが内部的か外部的にLowにドライブされるとき、これはコンフィグレーションが完了していないことを示し、デバイスはウェイクアップ・シーケンスの準備ができていません。デバイスがいったんコンフィグレーションがエラーなしで完了し、ウェイクアップの準備ができるようになると、DONEピンはHighにされます。他のデバイスがウェイクアップ・プロセスを制御することができるように、DONEピンのコンテンションを避けるためオープン・ドレインにコンフィグレーションされる必要があります。DONEピンのためのDONE\_ODプリファレンスはデフォルトがONです。DONE\_EXプリファレンスがONに設定されると、DONE\_ODプリファレンスは自動的にONに設定されます。DONE\_ODとDONE\_EXとの関係の詳しい情報に関しては表14-9を参照してください。デバイスがSDMモードであるとき、DONEピンは使用されません。従ってDONE ODとDONE EXプリファレンスは無効です。

#### **DONE External**

Doneビットがセットされるか、またはDONEピンが外部的にHighにドライブされるのを待ったあと、 LatticeXP2デバイスはそれ自身でウェイクアップすることができます。

DONE\_EX = ONにすることで、クロックと同期する外部信号によってDONEピンがHighにドライブされるまでウェイクアップを遅らせることができます。OFFを選択すると、内部Doneビットがセットされたときに同期してウェイクアップし、DONEピンの外部状態がどのようにドライブされているかは無視します。デフォルトはDONE\_EX = OFFです。DONE\_EXがONに設定されると、DONE\_ODもONに設定されます。外部信号がDONEピンをドライブしているなら、それはまたオープン・ドレインとするべきです(外部にプルアップ抵抗を加える必要性があるかもしれません)。DONE\_ODとDONE\_EXとの関係の詳しい情報に関して表14-9を参照してください。

表14-9 DONEピン・プリファレンスに関するまとめ

| DONE_EX <sup>1</sup> | ウェイクアップ・プロセス  | DONE_OD <sup>1</sup> |

|----------------------|---------------|----------------------|

| OFF                  | 外部DONEは無視     | ユーザ選択                |

| ON                   | 外部DONEのLowで遅れ | デフォルトに設定(ON)         |

1. デバイスがSDMモードであるとき、DONEピンは使用されません。従ってDONE\_ODと DONE\_EXプリファレンスは無効です。

## マスタクロックの選択

ユーザが、LatticeXP2をマスタ・コンフィグレーション・デバイスにすると決めると(適切にCFG[1:0]ピンを設定することによる)、これは同時にコンフィグレーションのためのクロックソースとなることを意味します。CCLKピンはMCCLK\_FREQに値によって設定された周波数の出力になります。コンフィグレーションの始めでは、デバイスは2.5MHzのデフォルトのマスタクロック周波数で動作します。コンフィグレーション・ビットストリームにおける幾つかの先頭ビットの一つはMCCLK\_FREQです。これらがいったんデバイスに読み込まれると、クロックはすぐにユーザ定義の周波数で動作し始めます。グリッチのないスイッチを用いる

LatticeXP2 14-15 sysCONFIG UGJ

ことでクロック周波数を切り変えます。

#### セキュリティ

CONFIG\_SECUREがONに設定されるとき、sysCONFIGかispJTAGポートを通してのリードバック動作はサポートされません。ただしispJTAG DeviceID領域のみは読み出し可能で、これはセキュリティの対象とは考えらないためです。デフォルトはOFFです。

## ウェイクアップ(起動)シーケンス

WAKE\_UPプリファレンスは3つの内部信号とDONEピンを制御します。DONEピンはコンフィグレーションの後でかつユーザモードの前にドライブされます。位相コントロール例とウェイクアップ選択に関する情報に関しては、このドキュメントのウェイクアップ・シーケンス・セクションを参照してください。WAKE\_UPプリファレンスのデフォルト設定はDONE EXの設定で決定されます。

## DONE EX = Off でのウェイクアップ(デフォルト設定)

DONE\_EX = OFF(デフォルト)のためのWAKE\_UPプリファレンスは、表14-8で示されるようにユーザの選択可能なオプション1~25をサポートします。ユーザがウェイクアップ・シーケンスを選択しないと、DONE\_EX = OFFでは、デフォルトはウェイクアップ・シーケンス21になります。

## DONE EX = On でのウェイクアップ

DONE\_EX = ONのWAKE\_UPプリファレンスは、表14-8で示されるようにユーザの選択可能なオプション1 ~ 7をサポートします。ユーザがウェイクアップ・シーケンスを選択しないと、デフォルトはウェイクアップ・シーケンス4になります。

## Wake On Lockの選択

Wake On Lockプリファレンスは、デバイスがウェイクアップ(起動)プロセスを始める前にPLLがロックするのを待つかどうかを決定します。

ON: 特定のPLLのPLLロック信号がアクティブになるまで、デバイスは起動しません。

OFF (default); デバイスはPLLロック信号のステートにかかわらず起動します。

## Power Save (省電力モード)

INBUFと呼ばれるI/O Power Saveモードオプションは、LatticeXP2デバイスで有効で、消費電力を節約するために未使用の入力バッファを非アクティブにします。これはHSTLやSSTLなどのような( $V_{REF}$  を用いる)コンパレータ・タイプの入力ピンに影響するだけです。

Power Saveモードはバウンダリ・スキャンの機能のいくつかを制限します。バウンダリ・スキャンテストにおいては、未使用の入力バッファもアクティブにするために、INBUFグローバル・プリファレンスをONにすることを推奨します。

# OTP(ワンタイム・プログラム)ヒューズ

LatticeXP2はワンタイム・プログラム(OTP)ヒューズを持っていて、オンチップ・フラッシュ・コンフィグレーション・メモリが消去されたり、または再プログラムされることを防ぐために用いることができます。これはフラッシュ・タグメモリやフラッシュ・ユーザメモリがプログラムされるのを防止しないので、これらの機能は利用できます。OTPヒューズは、ispLEVERデザインプランナでGlobal Configurationオプションを用いるか、またはダウンロード時に直接ispVM® Systemソフトウェアを用いることで設定できます。

LatticeXP2 14-16 sysCONFIG UGJ

## ユーザGOE

LatticeXP2にはUser GOE(Global Output Enable)機能があります。これは、標準ウェイクアップ・シーケンス完了後に、I/Oをバウンダリ・スキャンの制御下に保つことを可能にします。出力がいつバウンダリ・スキャンからユーザロジックの制御に移行するかは、ユーザロジックが決定します。このユーザロジック入力はCIBを介しており、JTAGの "wake up" 命令のみに有効です。

ユーザがIOWAKEUPと呼ばれるマクロで、この機能をインスタンスします。このマクロには信号が一つだけあり、起動シーケンス直後にのみ制御することができます。

## タグメモリ

タグメモリは単一ブロックよりなるフラッシュメモリで、スレーブSPIポートを介していつでもライト(フラッシュ用語ではプログラム)やリードができます。CFG[1:0]ピン設定の如何にかかわらず、LatticeXP2はユーザモードかプログラムされていない状態(ブランク)にあり得ます。唯一の例外はLatticeXP2がBSCANテストか直接プログラミング・モードにある時です。これらのモードの間I/OはBSCANの制御下にあるので、SPIインターフェイスは使用できません。

また、タグメモリもJTAGポートを通して利用できます。

表14-10はLatticeXP2各デバイスで利用できるタグメモリのサイズを示します。それぞれのLatticeXP2デバイスには、TAGメモリ専用の列が1つあります。

#### 表14-10 LatticeXP2ファミリのタグメモリ

| デバイス   | タグメモリ (bit) | タプメモリ (Byte) |

|--------|-------------|--------------|

| XP2-5  | 632         | 79           |

| XP2-8  | 768         | 96           |

| XP2-17 | 2184        | 273          |

| XP2-30 | 2640        | 330          |

| XP2-40 | 3384        | 423          |

注: すべてのフラッシュセルのパワーオン初期値(INITVAL)は '1' です。

タグメモリには、以下の機能と制限があります。

- ・それぞれの列のタグメモリは、シーケンシャル(順次)アクセスだけに制限されます。リードコマンドがいったん指定されると、タグメモリ全体の内容がファーストイン・ファーストアウト(FIFO)方法で連続して読まれます。

- ・データアクセスの速度はフラッシュ・ベースであるタグメモリの速度によって制限されます。

- ・タグメモリは消去された状態で出荷されます。

- ・電源がオフの間でも、ユーザが割り当てたプログラム後の値を保持します。

- ・既に内部で接続されているJTAGとSPIインターフェイス・ピンを用いることで、タグメモリのリードやライトができます。

- ・タグメモリはLatticeXP2のパワーアップ後にすぐ使うことができます。組み込まれているインターフェイスでタグメモリにアクセスするために、如何なるソフトウェアIPやデザインもデバイスにロードする必要はありません。

- ・I<sup>2</sup>CポートをエミュレートするスレーブSPI CIBインターフェイス・ピンを用いることで、FPGAコアロジックからタグメモリをリードし、或いは変更することができます。

- ・タグメモリは、デバイスのセキュリティ設定に拘わらず常にアクセスできます。

LatticeXP2 14-17 sysCONFIG UGJ

タグメモリは一般的に "静的な" データ、即ち変りそうにないデータを格納するように設計されています。 このタグメモリは、以下に例として示すようなシステム管理と製造制御情報などのために用いられているで あろうPCB上のEEPROMや簡易なフラッシュメモリの置き換えができます。

- ・電子的IDコードの保存

- ・バージョン管理

- ・日付

- ・製造のバージョン制御

- ・資産管理とトラッキング

- ・システム較正設定

- ・デバイスのシリアル番号、そして/または、在庫管理

## スレープSPIモード動作

タグメモリへのスレーブSPIモード・インターフェイスはSPI Bus Mode0とMode3動作の両方をサポートします。SPI Bus Mode0では、SPIマスタがスタンバイにあるときや、データを送信していない場合、通常CLKピンはLowです。この条件の間、SPI Bus Mode3では通常CLKピンはHighです。どちらの場合も、SISPIピンのデータはCCLKの立ち上がリエッジでサンプルされ、そしてSOSPIピンのデータはCCLKの立ち下がリエッジで出力されます。

タグメモリを用いる詳しい情報に関しては、テクニカルノートTN1137 LatticeXP2 Memory Usage Guideを参照してください。

## ユーザフラッシュ

ユーザフラッシュは、EBR RAMブロックに保存されたデータをバックアップする不揮発性メモリ領域として設計されています。これは後で使用するためにRAMメモリの内容を保存するための信頼できる方法をユーザに与えます。

LatticeXP2デバイスのユーザフラッシュの規模は、デバイスのEBRブロック数に直接依存し、またそれはロジック規模に比例します。ユーザフラッシュは1つか異なる2つのユーザフラッシュ・モジュールとして物理的に構成されています。しかしながら、論理的には全ユーザフラッシュ・モジュールが1つの統合されたブロックとして扱われます。

表14-11 ユーザフラッシュの構成

| プロックタイプ    | XP2-5 | XP2-8 | XP2-17 | XP2-30 | XP2-40 |

|------------|-------|-------|--------|--------|--------|

| 物理UFMブロック数 | 1     | 1     | 2      | 2      | 2      |

| 論理UFMブロック数 | 1     | 1     | 1      | 1      | 1      |

EBRブロックはユーザフラッシュのための主要なインターフェイスとして働きます。ユーザにはユーザフラッシュに直接アクセスする手段がありません。

store-to-flash 制御信号でユーザフラッシュにEBRの内容を保存することができます。必要な場合ユーザフラッシュにEBR内容を保存しなければなりません。2つの信号、UFMFAILおよびUFMBUSYNは、store-to-flashコマンドのステータスを把握するために用意されています。UFMFAIL信号がLowで、かつUFMBUSYN信号がHighの場合、EBR内容のフラッシュメモリへの保存は成功です。

ユーザ・フラッシュメモリの使用には以下の制約があります。

LatticeXP2 14-18 sysCONFIG UGJ

- ・Store-to-Flash 動作はEBR RAM(シングルポート、[真の]デュアルポート、擬似デュアルポート構成)だけに作用します。

- ・Store-to-Flash 動作の間、EBRブロックはユーザ動作ができず、そしてフラッシュはコンフィグレーション動作ができません。

- ・EBRを選択(指定)して保存する機能はサポートされていません。Store-to-Flash 動作は全EBRブロックの内容を格納します。

- ・シリコン制限のため、SED(ソフトエラー検出マクロ)がAlwaysモードで動作している場合、ユーザは Store-to-Flash 動作を用いることができません。

- ・トランスペアレント/バックグランド・モード(フラッシュかSRAM)と同時にUFMモードを用いることができません。SSPIコンフィグレーションとベリファイ動作(本質的にはトランスペアレント・モード動作)は、ユーザによって開始され、かつユーザはUFM動作が同時に要求されないようにする必要があります。

## 表14-12 ユーザフラッシュとシャドー・フラッシュ(EBR)の振舞いの違い

| パラメータ          | ユーザフラッシュ        | シャドー・フラッシュ |

|----------------|-----------------|------------|

| リード/ライト・アクセス速度 | 遅い              | 速い         |

| アクセス方式         | シーケンシャル         | ランダム       |

| データアクセス        | 制限あり(3.3章参照)    | 無限、または制限なし |

| データの構成         | シーケンシャル、一度に1ビット | 可変長、フレキシブル |

| データの粒度         | UFM全プロック        | 単一EBRブロック  |

詳しくはテクニカルノートTN1137 LatticeXP2 Memory Usage Guideを参照してください。

LatticeXP2 14-19 sysCONFIG UGJ

TN1141\_1.4J1 Nov. 2008

# テクニカル・サポート支援

ホットライン: 1-800-LATTICE (North America)

+1-503-268-8001 (Outside North America)

e-mail: techsupport@latticesemi.com

インターネット: www.latticesemi.com

# 変更履歴 (日本語版)

| Rev.# | 日付       | 変更箇所     |

|-------|----------|----------|

| 1.4J1 | Jan.2009 | 日本語版新規発行 |

|       |          |          |

|       |          |          |

LatticeXP2 14-20 sysCONFIG UGJ