# LatticeXP2 sysIO使用ガイド

## はじめに

LatticeXP2™ のsysIOバッファは先進のシステムI/O規格を用いて容易に他のデバイスとインターフェイスする機能を設計者に与えます。このテクニカルノートは利用できるsysIO規格について、またラティスの設計ソフトウェアを用いてどうそれらを実装するかを説明します。

## sysIOバッファ概要

LatticeXP2 sysIOインターフェイスは複数のプログラマブルI/Oセル(PIC)ブロックを含んでいます。各PICはそれらのそれぞれのsysIOバッファに接続された2つのプログラマブルI/O (PIOA、およびPIOB)を含んでいます。差動のI/Oペア("T"と"C"として表記)を提供するために、隣接している2PIOを一緒にすることができます。

各PIOはsysIOバッファとI/Oロジック(IOLOGIC)を含んでいます。LatticeXP2 sysIOバッファは種々シングルエンドと差動のシグナリング規格をサポートします。また、sysIOバッファはDDRメモリとインターフェイスするために必要なDQSストローブ信号をサポートします。16~18PIO毎に1つ遅延素子があり、遅延DQSストローブ信号が生成できるようになっています。遅延DQS信号はメモリからのDDRデータを入力レジスタブロックに取り込むストローブとして用いられます。sysIOバッファのアーキテクチャに関する詳しい情報については、LatticeXP2ファミリ・データシートを参照してください。

必要なクロックやデータ選択ロジックと共に、IOLOGICはシングル・データレート(SDR)やダブル・データレート(DDR)アプリケーションを実装するための入力、出力、およびトライステート・レジスタを含んでいます。IOLOGICの中のプログラマブル遅延線と専用ロジックは、入力されるクロックとデータ信号に必要なシフトのため、またDDRメモリにおけるDQS入力に必要な遅延のために用いられます。IOLOGICのDDR実装とDDRメモリ・インターフェイス・サポートのその他詳細については、テクニカルノートTN1138 (LatticeXP2 高速I/Oインターフェイス使用ガイド)で議論します。

## サポートするsysIO規格

LatticeXP2 sysIOバッファは、シングルエンドと差動の規格を共にサポートします。シングルエンド規格は(内部)レシオ型の規格であるLVCMOS、LVTTL、及びPCIと、外部参照型のHSTL、SSTLなどに細分化することができます。バッファはLVTTL、LVCMOS 1.2/1.5/1.8/2.5/3.3Vの各規格をサポートします。LVCMOSとLVTTLモードでは、バッファは個別に構成可能なオプションとして、ドライブ強度、バス・メンテナンス(弱いプルアップ、弱いプルダウンまたはバスキーパ・ラッチ)、およびオープン・ドレインなどが指定できます。サポートする他のシングルエンド規格にはSSTLとHSTLが含まれます。サポートされる差動規格にはMLVDS、LVDS、RSDS、BLVDS、LVPECL、差動SSTL、および差動HSTLを含みます。表8-1と表8-2はLatticeXP2デバイスでサポートするsysIO規格を記載します。

表8-1 サポートする入力規格

| 入力規格               | V <sub>REF</sub> (Nom., [V]) | V <sub>CCIO</sub> <sup>1</sup> (Nom., [V]) |  |

|--------------------|------------------------------|--------------------------------------------|--|

| シングルエンド・インターフェイス   |                              | •                                          |  |

| LVTTL              | _                            | _                                          |  |

| LVCMOS33           | _                            | _                                          |  |

| LVCMOS25           | _                            | _                                          |  |

| LVCMOS18           | _                            | 1.8                                        |  |

| LVCMOS15           | _                            | 1.5                                        |  |

| LVCMOS12           | _                            | _                                          |  |

| PCI 33             | _                            | 3.3                                        |  |

| HSTL18 Class I, II | 0.9                          | _                                          |  |

| HSTL15 Class I                   | 0.75 | _ |

|----------------------------------|------|---|

| SSTL3 Class I, II                | 1.5  | _ |

| SSTL2 Class I, II                | 1.25 | _ |

| SSTL18 Class I, II               | 09   | _ |

| 差動インターフェイス                       |      |   |

| 差動SSTL18 Class I, II             | _    | _ |

| 差動SSTL2 Class I, II              | _    | _ |

| 差動SSTL3 Class I, II              | _    |   |

| 差動HSTL15 Class I                 | _    | _ |

| 差動HSTL18 Class I, II             | _    | _ |

| LVDS, MLVDS, LVPECL, BLVDS, RSDS | _    | _ |

<sup>1.</sup> 特に明記していないものは、Vccioを有効な値のどこに設定しても良いことを示す

## 表8-2 サポートする出力規格

| 出力規格                | ドライブ                          | V <sub>CCIO</sub> (Nom., [V]) |  |  |  |  |

|---------------------|-------------------------------|-------------------------------|--|--|--|--|

| シングルエンド・インターフェイス    |                               |                               |  |  |  |  |

| LVTTL               | 4mA, 8mA, 12 mA, 16 mA, 20 mA | 3.3                           |  |  |  |  |

| LVCMOS33            | 4mA, 8mA, 12 mA, 16 mA, 20 mA | 3.3                           |  |  |  |  |

| LVCMOS25            | 4mA, 8mA, 12 mA, 16 mA, 20 mA | 2.5                           |  |  |  |  |

| LVCMOS18            | 4mA, 8mA, 12 mA, 16 mA        | 1.8                           |  |  |  |  |

| LVCMOS15            | 4mA, 8mA                      | 1.5                           |  |  |  |  |

| LVCMOS12            | 2mA, 6mA                      | 1.2                           |  |  |  |  |

| LVCMOS33、オープンドレイン   | 4mA, 8mA, 12 mA, 16 mA, 20 mA | _                             |  |  |  |  |

| LVCMOS25、オープンドレイン   | 4mA, 8mA, 12 mA, 16 mA, 20 mA | _                             |  |  |  |  |

| LVCMOS18、オープンドレイン   | 4mA, 8mA, 12 mA, 16 mA        | _                             |  |  |  |  |

| LVCMOS15、オープンドレイン   | 4mA, 8mA                      | _                             |  |  |  |  |

| LVCMOS12、オープンドレイン   | 2mA, 6mA                      | _                             |  |  |  |  |

| PCI 33 <sup>2</sup> | N/A                           | 3.3                           |  |  |  |  |

| HSTL18 Class I      | 8mA, 12mA                     | 1.8                           |  |  |  |  |

| HSTL18 Class II     | N/A                           | 1.8                           |  |  |  |  |

| HSTL15 Class I      | 4mA, 8mA                      | 1.5                           |  |  |  |  |

| SSTL3 Class I, II   | N/A                           | 3.3                           |  |  |  |  |

| SSTL2 Class I       | 8mA, 12mA                     | 2.5                           |  |  |  |  |

| SSTL2 Class II      | 16mA, 20mA                    | 2.5                           |  |  |  |  |

| SSTL18 Class I      | N/A                           | 1.8                           |  |  |  |  |

| SSTL18 Class II     | 8mA, 12mA                     | 1.8                           |  |  |  |  |

| 差動インターフェイス          |                               |                               |  |  |  |  |

| 差動SSTL3 Class I, II | N/A                           | 3.3                           |  |  |  |  |

| 差動SSTL2 Class I     | 8mA, 12mA                     | 2.5                           |  |  |  |  |

| 差動SSTL2 Class II    | 16mA, 20mA                    | 2.5                           |  |  |  |  |

| 差動SSTL18 Class I    | N/A                           | 1.8                           |  |  |  |  |

| 差動SSTL18 Class II   | 8mA, 12mA                     | 1.8                           |  |  |  |  |

| 差動HSTL18 Class I    | 8mA, 12mA                     | 1.8                           |  |  |  |  |

| 差動HSTL18 Class II   | N/A                           | 1.8                           |  |  |  |  |

| 差動HSTL15 Class I    | 4mA, 8mA                      | 1.5                           |  |  |  |  |

| LVDS                | N/A                           | 2.5                           |  |  |  |  |

| MLVDS <sup>1</sup>  | N/A                           | 2.5                           |  |  |  |  |

| BLVDS <sup>1</sup>  | N/A | 2.5 |

|---------------------|-----|-----|

| LVPECL <sup>1</sup> | N/A | 3.3 |

| RSDS <sup>1</sup>   | N/A | 2.5 |

- 1. 外部抵抗を加えてエミュレート

- 2. PCI33はPCIX互換です

## sysIOのバンク体系

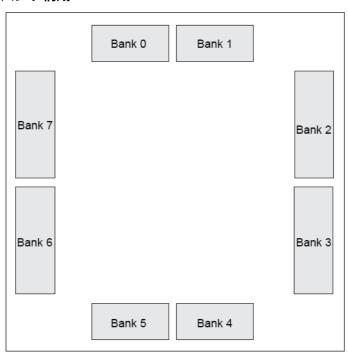

LatticeXP2デバイスには、8つの汎用プログラマブルsysIOバンクがあります。8つの汎用sysIOバンクには、それぞれ一本の $V_{CCIO}$  供給電圧、2本の基準電圧( $V_{REF1}$  および $V_{REF2}$ )があります。図8-1は8汎用バンクと関連する供給電源と共に示します。

上下辺バンクでは、sysIOバッファペアは2本のシングルエンド出力ドライバと、二組のシングルエンド入力バッファ(レシオ型と参照型共に)があります。左右のsysIOバッファペアは2本のシングルエンド出力ドライバと、二組のシングルエンド入力バッファ(レシオ型と参照型共に)があります。参照型の入力バッファは差動入力としても構成できます。LVDSサポートは左右バンクの50%に限られ(最上部ペアからはじめて)、上辺・底辺バンクのI/Oにはありません。50%のペアには差動出力ドライバがあります。ペアの両パッドはそれぞれ "true" と "comp" と表記されており、trueは差動入力ペアの正(非反転)側を意味し、compは負(反転)側を意味しています。

## SPIフラッシュメモリ・インターフェイス

SPIピン (マスタ、スレーブ)はI/Oバンク7に多重化されています。専用ピンCFG[0]とTOEは $V_{CC}$ 電圧が供給されバンク6と7の間にあります。

## JTAGインターフェイス

JTAGピンはバンク2と3の間にあり、V<sub>CCJ</sub>電圧が供給されます。

#### 図8-1 LatticeXP2 sysIOバンク構成

## V<sub>CCIO</sub> (1.2V / 1.5V / 1.8V / 2.5V / 3.3V)

合計8つの $V_{CCIO}$  電源があり、それらは $V_{CCIO0} \sim V_{CCIO7}$ です。各バンクには、シングルエンド出力ドライバ用と、LVTTLや、LVCMOS、PCIなどのレシオ入力バッファを動作させる別々の $V_{CCIO}$  電源があります。LVTTL、LVCMOS3.3、LVCMOS2.5、およびLVCMOS1.2は、それらがどこのバンクに置かれても良い固

定スレッショルド・オプションを持っています。バンクに適用されたV<sub>CCIO</sub>電圧が、そのバンクでサポートすることができるレシオ入力規格を決定します。また、それは、差動出力ドライバを動作させるのにも用いられます。

## **V<sub>CCAUX</sub>** (3.3V)

バンク $V_{CCIO}$  電源以外に、デバイスには $V_{CC}$  コアロジック電源、さらに参照電圧を用いる差動入力バッファを動作させるための $V_{CCAUX}$  補助電源があります。これらドライバと入力バッファのコモンモード範囲要件を満たすため、 $V_{CCAUX}$  をI/O参照電圧として用いる3.3Vが必要です。

## V<sub>CCJ</sub> (1.2V / 1.5V / 1.8V / 2.5V / 3.3V)

JTAGピンには、バンク $V_{CCIO}$ 電源から独立している別の $V_{CCJ}$ 電源があります。 $V_{CCJ}$ はLVCMOS JTAGピンの電気特性、すなわち出力のHighレベルと入力スレッショルドの両方を決定します。

表8-3に供給電源のまとめを示します。

## 表8-3 供給電源

| 供給電源                            | 記 述             | 值 <sup>1</sup>           |

|---------------------------------|-----------------|--------------------------|

| $V_{CC}$                        | コア電源            | 1.2V                     |

| $V_{CCIO}$                      | I/Oバンク用電源       | 1.2V/1.5V/1.8V/2.5V/3.3V |

| V <sub>CCAUX</sub> <sup>2</sup> | 補助(Auxiliary)電源 | 3.3V                     |

| V <sub>CCJ</sub> <sup>2</sup>   | JTAGピン用電源       | 1.2V/1.5V/1.8V/2.5V/3.3V |

注; 1. 推奨min. / max.値についてはLatticeXP2データシートを参照

## 入力参照電圧(V<sub>REF1</sub>, V<sub>REF2</sub>)

各バンクは、最大2つの別々の $V_{REF}$ 入力電圧( $V_{REF1}$  と $V_{REF2}$ )をサポートし、これらは参照電圧を用いる入力バッファのスレッショルドを設定するのに用いられます。これらの $V_{REF}$  ピンの位置はバンク内で予め決められています。バンクが $V_{REF}$  電圧を必要としない場合、通常のI/Oとしてこれらのピンを用いることができます。

## **DDRメモリ・インターフェイスのためのV<sub>REF1</sub>**

DDRメモリにインターフェイスするとき、メモリからのDQSとDQ入力のために、参照電圧として $V_{REF1}$ 入力を用いなければなりません。 $V_{REF1}$  とGNDの間の電圧分割器が、DQS遷移検出回路によって用いられるオンチップ基準電圧を発生させるのに用いられます。この電圧分割器は $V_{REF1}$  にのみ存在しており、 $V_{REF2}$  は利用できません。DQS遷移検出ロジックについてと、その実装についての詳しい情報は、ラティス・テクニカルノートTN1138を参照してください。DDR1メモリ・インターフェイスでは $V_{REF1}$  は1.25Vとするべきで、従ってSSTL25\_II 規格のみが許容されます。DDR2メモリ・インターフェイスにおいては $V_{REF1}$  は0.9Vとし、従ってSSTL18\_II 規格のみが許容されます。

#### バンク内における複数電圧のサポート

LatticeXP2 sysIOバッファは3本のパラレル・レシオ入力バッファに接続されています。これらの3本のパラレル・バッファは $V_{CCIO}$  と $V_{CCAUX}$ 、そして $V_{CC}$  に接続されており、 $V_{CCIO}$  に追従するスレッショルド、および3.3V ( $V_{CCAUX}$ ) / 1.2V ( $V_{CC}$ )の固定スレッショルドを共にサポートします。これによって、 $V_{CCIO}$  に追従するだけでなく、レシオ・バッファの入力スレッショルドをピンごとに割り当てることができます。このオプションは、1.2V、2.5V、および3.3Vの全レシオ入力で利用でき、バンク $V_{CCIO}$  電圧から独立しています。例えばバンク $V_{CCIO}$  が1.8Vである場合、固定スレッショルドを1.2Vと3.3Vレシオ入力バッファに与え、同時に2.5Vレシオ入力に対して追従するスレッショルドを持たせることが可能です。

デバイスのコンフィグレーション前には、レシオ入力スレッショルドは常にバンクV<sub>CCIO</sub> に追従します。このオプションはコンフィグレーションの後にのみ有効になります。バンク内の出力規格はいつもV<sub>CCIO</sub> によって設定されます。表8-4は、ユーザが同じバンクで混用することができるsysIO規格を示します。

LatticeXP2 8-4 sysIO UGJ

<sup>2.</sup> V<sub>CCIO</sub> やV<sub>CCJ</sub> が3.3Vの場合、V<sub>CCAUX</sub> と同じ電圧源から供給する必要があります。

表8-4 電圧の混在のサポート

| V                 | sysIO 入力規格 |      |      | , sysIO 入力規格 |      |      |      | sysIO 出力規格 |      |      |  |

|-------------------|------------|------|------|--------------|------|------|------|------------|------|------|--|

| V <sub>CCIO</sub> | 1.2V       | 1.5V | 1.8V | 2.5V         | 3.3V | 1.2V | 1.5V | 1.8V       | 2.5V | 3.3V |  |

| 1.2V              | Yes        |      |      | Yes          | Yes  | Yes  |      |            |      |      |  |

| 1.5V              | Yes        | Yes  |      | Yes          | Yes  |      | Yes  |            |      |      |  |

| 1.8V              | Yes        |      | Yes  | Yes          | Yes  |      |      | Yes        |      |      |  |

| 2.5V              | Yes        |      |      | Yes          | Yes  |      |      |            | Yes  |      |  |

| 3.3V              | Yes        |      |      | Yes          | Yes  |      |      |            |      | Yes  |  |

## 各バンクでサポートするsysIO規格 表8-5 各バンクのサポートするI/O規格

| 記述         | 上辺 バンク0-1                                                                              | 右辺 バンク2-3                                                                                      | 下辺 バンク4-5                                                                              | 左辺 バンク6-7                                                                                      |

|------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| I/Oバッファタイプ | シングルエンド                                                                                | シングルエンドと差動                                                                                     | シングルエンド                                                                                | シングルエンドと差動                                                                                     |

|            | LVTTL<br>LVCMOS33<br>LVCMOS25<br>LVCMOS18<br>LVCMOS15<br>LVCMOS12<br>SSTL18クラス I, II   | LVTTL<br>LVCMOS33<br>LVCMOS25<br>LVCMOS18<br>LVCMOS15<br>LVCMOS12                              | LVTTL<br>LVCMOS33<br>LVCMOS25<br>LVCMOS18<br>LVCMOS15<br>LVCMOS12<br>SSTL18クラス I, II   | LVTTL<br>LVCMOS33<br>LVCMOS25<br>LVCMOS18<br>LVCMOS15<br>LVCMOS12                              |

|            | SSTL25クラス 1, II<br>SSTL33クラス 1, II                                                     | SSTL25クラス I, II<br>SSTL33クラス I, II                                                             | SSTL25クラス I, II<br>SSTL33クラス I, II                                                     | SSTL25クラス I, II<br>SSTL33クラス I, II                                                             |

| サポートする     | HSTL15クラス I<br>HSTL18クラス I, II                                                         | HSTL15クラス I<br>HSTL18クラス I, II                                                                 | HSTL15クラス I<br>HSTL18クラス I, II                                                         | HSTL15クラス I<br>HSTL18クラス I, II                                                                 |

| 出力規格       | SSTL18Dクラス I,<br>SSTL25Dクラス I, II<br>SSTL33Dクラス I, II                                  | SSTL18Dクラス I,<br>SSTL25Dクラス I, II<br>SSTL33Dクラス I, II                                          | SSTL18Dクラス I,<br>SSTL25Dクラス I, II<br>SSTL33Dクラス I, II                                  | SSTL18Dクラス I,<br>SSTL25Dクラス I, II<br>SSTL33Dクラス I, II                                          |

|            | HSTL15Dクラス I<br>HSTL18Dクラス I, II                                                       | HSTL15Dクラス I, II<br>HSTL18Dクラス I, II                                                           | HSTL15Dクラス I<br>HSTL18Dクラス I, II                                                       | HSTL15Dクラス I<br>HSTL18Dクラス I, II                                                               |

|            | MLVDS                                                                                  | MLVDS                                                                                          | MLVDS                                                                                  | MLVDS                                                                                          |

|            | LVDS25E <sup>1</sup><br>LVPECL <sup>1</sup><br>BLVDS <sup>1</sup><br>RSDS <sup>1</sup> | LVDS<br>LVDS25E <sup>1</sup><br>LVPECL <sup>1</sup><br>BLVDS <sup>1</sup><br>RSDS <sup>1</sup> | LVDS25E <sup>1</sup><br>LVPECL <sup>1</sup><br>BLVDS <sup>1</sup><br>RSDS <sup>1</sup> | LVDS<br>LVDS25E <sup>1</sup><br>LVPECL <sup>1</sup><br>BLVDS <sup>1</sup><br>RSDS <sup>1</sup> |

| 入力         | 全シングルエンドと差動                                                                            | 全シングルエンドと差動                                                                                    | 全シングルエンドと差動                                                                            | 全シングルエンドと差動                                                                                    |

| クロック入力     | 全シングルエンドと差動                                                                            | 全シングルエンドと差動                                                                                    | 全シングルエンドと差動                                                                            | 全シングルエンドと差動                                                                                    |

| PCIサポート    | クランプありPCl33                                                                            | クランプなしPCI33                                                                                    | クランプありPCl33                                                                            | クランプなしPCI33                                                                                    |

| LVDS出力バッファ |                                                                                        | LVDS (3.5mA)バッファ <sup>2</sup>                                                                  |                                                                                        | LVDS(3.5mA)バッファ <sup>2</sup>                                                                   |

<sup>1.</sup>これらの差動規格は、外付け抵抗パックと共にコンプリメンタリLVCMOSドライバを用いることによって、実装されます。

## LVCMOSバッファの構成

すべてのLVCMOSバッファには、ソフトウェアで設定することができるプログラマブル・プル、プログラマブル・ドライブ、およびプログラマブル・スルーレートの各コンフィグレーションがあります。

## バスメンテナンス回路

各パッドには弱いプルアップ、弱いプルダウン、および弱いバスキーパ機能があります。プルアップとプルダウン設定は固定特性を提供し、ワイヤードORなどのロジックを作成する際に役に立ちます。しかし、信号ステートによっては電流は他のオプションよりわずかに高い場合があります。バスキーパ・オ

<sup>2.</sup> バンク内の50%のI/Oのみ

プションは最後にドライブされたステートで信号をラッチし、最小の電力消費で有効なレベルを保持します。またユーザはバス・メンテナンス回路をオフに選択することができ、電力消費と入力リークを最小にできます。この場合重要なのは、入力が既知のステートにドライブされることを確実にすることであり、入力バッファにおける不要な電力消費を避けなければなりません。バンクのV<sub>CCIO</sub>が3.3Vに割り当てられるとき、弱いバスキーパは利用できません。

## プログラマブル・ドライブ

LVCMOSとLVTTL出力バッファ・ピンは、幾つかの電圧参照タイプ(SSTL/HSTL)と共に、それぞれがプログラマブルなドライブ強度オプションを持っています。各I/Oにこのオプションを個別に設定することができます。用意されているドライブ強度設定は、2mA、4mA、6mA、8mA、12mA、16mA、そして20mAです。利用できる実際のオプションはI/O電圧で異なります。ドライブ強度を選択するとき、ユーザは、バンクあたりの最大許容電流とパッケージの熱限界となる電流を考慮しなければなりません。表8-6ははそれぞれの出力規格で利用できるドライブ設定を示します。

| 表8-6   | シング | ルナンド  | ・バッファ  | ァのプログラ | マブル・   | ドライブ強度値 |

|--------|-----|-------|--------|--------|--------|---------|

| 4.EO-O |     | ノレエン・ | ・ノくシンノ | ソンロンン  | X 2 1V | レンソフェクロ |

| シングルエンドI/O規格 | プログラマブル・ドライブ (mA) |

|--------------|-------------------|

| HSTL15_I     | 4, 8              |

| HSTL18_I     | 8, 12             |

| SSTL25_I     | 8, 12             |

| SSTL25_II    | 16, 20            |

| SSTL18_II    | 8, 12             |

| LVCMOS12     | 2, 6              |

| LVCMOS15     | 4, 8              |

| LVCMOS18     | 4, 8, 12, 16      |

| LVCMOS25     | 4, 8, 12, 16, 20  |

| LVCMOS33     | 4, 8, 12, 16, 20  |

| LVTTL        | 4, 8, 12, 16, 20  |

#### プログラマブル・スルーレート

LVCMOSとLVTTL出力バッファ・ピンは、プログラマブルな出力スルーレート制御も持っており、それぞれ低雑音もしくは高速性能などのために構成することができます。各I/Oピンには、個々にスルーレート制御があります。これにより、スルーレート制御をピンごとに指定できます。このスルーレート制御は、立ち上がりエッジと立ち下がりエッジの両方に影響します。

#### オープンドレイン制御

全てのLVCMOSとLVTTL 出力バッファはオープンドレインとして構成することができます。これはソフトウェアでOPENDRAINアトリビュートをオンにすることによって行います。

#### 差動SSTLとHSTLサポート

コンプリメンタリなCパッドに関連付けられたシングルエンド・ドライバは、Trueパッドと関連づけられたシングルエンド・ドライバをドライブするデータをコンプリメント(反転)して任意にドライブすることができます。これは、信号間のスキューが最も低い1組のシングルエンド・ドライバでコンプリメンタリな出力をドライブするのに用いることを可能にします。同期タイプのDRAMとSRAMで用いられるそれぞれ差動のSSTL/HSTLクロック入力で必要とされます。この機能はデバイス外部の抵抗と共に用いてLVPECLとBLVDS両出力ドライバをエミュレートして行います。

LatticeXP2 8-6 sysIO UGJ

## 表8-7 差動バッファのプログラマブル・ドライブ強度値

| シングルエンドI/O規格 | プログラマブル・ドライブ (mA) |

|--------------|-------------------|

| HSTL15D_1    | 4, 8              |

| HSTL18D_I    | 8, 12             |

| SSTL25D_I    | 8, 12             |

| SSTL25D_II   | 16, 20            |

| SSTL18D_II   | 8, 12             |

## プログラマブルPCICLAMPによるPCIのサポート

それぞれのsysIOバッファはPCl33をサポートするために構成することができます。デバイスの上辺と底辺のバッファには、ispLEVERデザインツールで任意に指定できるオプションのPClクランプ・ダイオードがあります。

プログラマブルPCICLAMPは該当バンクのI/Oで個別にオン、オフできます。

## プログラマブル入力遅延

各入力は、コアロジックか入力レジスタに渡される前に任意に遅延させることができます。入力遅延の第一の用途は、ダイレクト・ドライブ・プライマリクロックを用いるとき、入力レジスタのためのゼロホールド時間を達成することです。ゼロホールド時間に到着するように、少なくともプライマリクロックの注入遅れと同じくらい入力遅延でデータを遅らせます。このオプションはソフトウェアでFIXEDDELAYアトリビュート(属性)を用いることで、各I/O個別にON/OFFすることができます。このアトリビュートはさらに"ソフトウェアsysIOアトリビュート"セクションで説明されます。付録AはHDLアトリビュートでどのようにこの機能をイネーブルできるかを示します。

## ソフトウェアsysIOアトリビュート(属性)

sysIOアトリビュートは、デザインプランナ(Design Planner) GUIを用いて、或いはHDLで指定するか、またはASCIIプリファレンス・ファイル(.lpf)中で直接指定することができます。付録A、B、およびCはこれらの方法を用いることで、どう割り当てることができるかの例をそれぞれリストアップします。このセクションはこれらのアトリビュートについてそれぞれ詳細に説明します。

#### **IO TYPE**

これはI/OのsysIO標準を設定するのに用いられます。これらI/O規格に対応しなければならないV<sub>CCIO</sub>値は、アトリビュート名自体に組み込まれているのみです。表8-8は利用できるI/Oタイプをリストしています。

## 表8-8 IO\_TYPEアトリビュート値

| sysIO シグナリング規格       | IO_TYPE               |

|----------------------|-----------------------|

| DEFAULT              | LVCMOS25              |

| LVDS 2.5V            | LVDS25                |

| RSDS                 | RSDS                  |

| エミュレートLVDS 2.5V      | LVDS25E <sup>1</sup>  |

| バスLVDS 2.5V          | BLVDS25 <sup>1</sup>  |

| LVPECL 3.3V          | LVPECL33 <sup>1</sup> |

| HSTL18 Class I, II   | HSTL18_I, HSTL18_II   |

| 差動HSTL18 Class I, II | HSTL18D_I, HSTL18D_II |

| HSTL15 Class I       | HSTL15_I              |

| 差動HSTL15 Class I     | HSTL15D_I             |

| SSTL33 Class I, II   | SSTL33_I, SSTL33_II   |

| 差動SSTL33 Class I, II | SSTL33D_I, SSTL33D_II |

| SSTL25 Class I, II   | SSTL25_I, SSTL25_II   |

| 差動SSTL25 Class I, II | SSTL25D_I, SSTL25D_II |

| SSTL18 Class I, II   | SSTL18_I, SSTL18_II   |

| 差動SSTL18 Class I     | SSTL18D_I, SSTL18D_II |

| LVTTL                | LVTTL33               |

| 3.3V LVCMOS          | LVCMOS33              |

| 2.5V LVCMOS          | LVCMOS25              |

| 1.8V LVCMOS          | LVCMOS18              |

| 1.5V LVCMOS          | LVCMOS15              |

| 1.2V LVCMOS          | LVCMOS12              |

| 3.3V PCI             | PCI33                 |

| MLVDS                | MLVDS <sup>1</sup>    |

注1; これらの差動規格はコンプリメンタリLVCMOSドライバと外部抵抗パックを用いて実装する

## **OPENDRAIN**

OPENDRAINアトリビュートを用いることによって、LVCMOSとLVTTL規格を指定したポートをオープンドレインとして設定することができます。

値: ON, OFF デフォルト:OFF

## DRIVE

ドライブ強度アトリビュートはプログラマブル・ドライブ強度を持つLVTTLとLVCMOS出力規格に設定できます。

## 表8-9 DRIVE設定值

| 出力規格                   | DRIVE (mA)       | デフォルト |

|------------------------|------------------|-------|

| HSTL15_I / HSTL15D_1   | 4, 8             | 8     |

| HSTL18_I / HSTL18D_I   | 8, 12            | 12    |

| SSTL25_I / SSTL25D_I   | 8, 12            | 8     |

| SSTL25_II / SSTL25D_II | 16, 20           | 16    |

| SSTL18_II / SSTL18D_II | 8, 12            | 12    |

| LVCMOS12               | 2, 6             | 6     |

| LVCMOS15               | 4, 8             | 8     |

| LVCMOS18               | 4, 8, 12, 16     | 12    |

| LVCMOS25               | 4, 8, 12, 16, 20 | 12    |

| LVCMOS33               | 4, 8, 12, 16, 20 | 12    |

| LVTTL                  | 4, 8, 12, 16, 20 | 12    |

#### **PULLMODE**

PULLMODEアトリビュートはすべてのLVTLL / LVCMOS I/Oで利用できます。このアトリビュートを各I/Oごと独立してイネーブルすることができます。

值: UP, DOWN, NONE, KEEPER

デフォルト: UP

### 表8-10 PULLMODE值

| PULLオプション       | PULLMODE値 |

|-----------------|-----------|

| プルアップ ( デフォルト ) | UP        |

| プルダウン           | DOWN      |

| バスキーパ           | KEEPER    |

| プルオフ            | NONE      |

## **PCICLAMP**

デバイスの上辺と底辺にあるPCI33バッファには、オプションのPCIクランプ・ダイオードがあり、ispLEVERデザインツールでPCICLAMPアトリビュートでイネーブルできます。また、PCICLAMPはすべてのLVCMOS33とLVTTL入力で利用できます。

値: ON, OFF デフォルト: OFF

#### 表 8-11 PCICLAMP値

| 入力タイプ    | PCICLAMP値      |

|----------|----------------|

| PCI33    | ON             |

| LVCMOS33 | OFF (デフォルト)、ON |

| LVTTL    | OFF (デフォルト)、ON |

#### **SLEWRATE**

SLEWRATEアトリビュートはすべてのLVTTL / LVCMOS出力ドライバに利用できます。それぞれのI/Oピンには、個々のスルーレート制御があります。

値: FAST, SLOW デフォルト: FAST

#### **FIXEDDELAY**

FIXEDDELAYアトリビュートはそれぞれの入力ピンで利用できます。このアトリビュートがイネーブルされると、グローバル・クロックを用いるときの入力レジスタがゼロホールド時間を達成するのに用いられます。このアトリビュートはHDLソースコード内でのみアサイン可能です。

值: TRUE, FALSE

デフォルト: FALSE

#### **INBUF**

デフォルトですべての未使用の入力バッファはディセーブルされます。INBUFアトリビュートは、バウンダリスキャン・テストを実行するとき、未使用の入力バッファをイーブルするために用いられます。 これはグローバルなアトリビュートであり、ONかOFFに設定することができます。

値: ON, OFF デフォルト: OFF

#### **DIN / DOUT**

I/Oレジスタを割り当てる必要があるときに、このアトリビュートを用いることができます。DINを用いると設計内の入力レジスタがI/Oブロックに配置され、同様にDOUTアトリビュートを用いると出力レジスタがI/Oブロックに配置されます。ソフトウェアは、デフォルトでなるべくI/Oレジスタを割り当てようとします。ユーザは、論理合成のアトリビュート、またはソフトウェアのデザインプランナを用いることによって、オフにすることができます。これらのアトリビュートはレジスタにのみ適用することができます。

#### LOC

設計内のI/Oポートへのピン割り当てにこのアトリビュートを用いることができます。このアトリビュートは、HDLソース内でピン割り当てがされているときだけ用いられます。ソフトウェアのデザインプランナGUIを用いることでピンの割り当てをすることもできます。付録でさらに詳細に説明します。

## 設計における考察と使用法

このセクションでは、LatticeXP2 sysIOバッファを設計するとき、考慮に入れる必要がある設計ルールと配慮事項のいくつかについて論じます。

## バンクに関するルール

- どのバンクでも $V_{CCIO}$  か $V_{CCJ}$  が3.3Vに設定される場合、それを $V_{CCAUX}$  と同じ電源に接続されることを勧めます。その結果リークを最小にします。

- どのバンクでも $V_{CCIO}$  か $V_{CCJ}$  が1.2Vに設定される場合、それを $V_{CC}$  と同じ電源に接続されることを勧めます。その結果リークを最小にします。

- DDRメモリ・インターフェイスを実装するとき、バンクのV<sub>REF1</sub>をインターフェイス・ピンの参照 電圧を提供するのに用います。いかなる他の参照電圧を用いる入力の動作にも用いることはでき ません。

- 上辺・底辺バンク(バンク0、1、4、5)のみがPCIクランプをサポートします。

- すべての有効な入力バッファはバンクV<sub>CCIO</sub> から独立していますが、1.8Vと1.5VバッファのみはバンクV<sub>CCIO</sub> としてそれぞれ1.8Vと1.5Vが必要です。

## 差動 1/0 ルール

- すべてのバンクがLVDS入力バッファをサポートすることができます。左右バンク(2、3、6、および7)のバンクだけが、真のLVDS差動出力バッファをサポートします。全てのバンクがLVDS入力バッファをサポートします。ユーザはこれらバンクではエミュレートしたLVDS出力バッファとして用いることができます。

- 全バンクは、外部抵抗パックとコンプリメンタリなLVCMOSドライバを用いることで、差動バッファをエミュレートすることをサポートします。

- 左右辺のI/Oのうち50%のみにLVDSバッファ出力機能があります。LVDSはTRUEパッドのみに割り当てることができます。差動ペアの他方のI/OをコンプリメンタリなパッドにispLEVERデザインツールが自動的にアサインします。すべてのLVDSペアのピンについてはデバイスのデータシートを参照してください。

LatticeXP2 8-10 sysIO UGJ

## 差動 I/O の実装

LatticeXP2デバイスは以下のセクションで詳しく述べるように種々の差動規格をサポートします。

#### LVDS

真のLVDS (LVDS25)出力ドライバは、デバイスの左右辺バンクの50%で利用でき、外部抵抗を一切必要としません。LVDS入力はデバイスの全バンクでサポートします。またすべてのバンクで外部抵抗と共にコンプリメンタリLVCMOSドライバ(LVDS25E)を用いてLVDSをサポート(エミュレート)します。これらLVDS実装についてはLatticeXP2ファミリ・データシートを参照してください。

#### **BLVDS**

全てのシングルエンドsysIOバッファペアが、外部抵抗と共にコンプリメンタリなLVCMOSドライバを用いることでバスLVDS (BLVDS)規格をサポートします。BLVDS実装に関しては、LatticeXP2ファミリ・データシートを参照してください。

#### **RSDS**

全てのシングルエンドsysIOバッファペアが、外部抵抗と共にコンプリメンタリなLVCMOSドライバを用いることでRSDS規格をサポートします。RSDS実装に関しては、LatticeXP2ファミリ・データシートを参照してください。

#### **LVPECL**

すべてのsysIOバッファがLVPECL入力をサポートします。LVPECL出力は、外部抵抗と共にコンプリメンタリLVCMOSドライバを用いることでサポートされます。LVPECL実装に関しては、LatticeXP2ファミリ・データシートを参照してください。

### 差動SSTLと差動HSTL

全てのシングルエンドsysIOバッファペアは、差動のSSTLとHSTLをサポートします。差動HSTL/SSTLの実装についてはLatticeXP2ファミリ・データシートを参照してください。

## **MLVDS**

全てのシングルエンドsysIOバッファペアが、外部抵抗と共にコンプリメンタリなLVCMOSドライバを用いることでMLVDS規格をサポートします。MLVDS実装に関しては、LatticeXP2ファミリ・データシートを参照してください。

## テクニカル・サポート支援

ホットライン: 1-800-LATTICE (North America)

+1-503-268-8001 (Outside North America)

e-mail: techsupport@latticesemi.com インターネット: http://www.latticesemi.com

## 変更履歴(日本語版)

| Rev.# | 日付       | 変更箇所     |

|-------|----------|----------|

| 1.1J  | Jan.2009 | 日本語版新規発行 |

|       |          |          |

|       |          |          |

## 付録A Synplicity®とPrecision®RTL Synthesis用HDLアトリビュート

HDLアトリビュートを用いて、直接ソース内でsyslOに属性を割り当てることができます。設計者は、用いようとしている論理合成ツール・ベンダのアトリビュート定義と構文を用いる必要があります。以下は、PrecisionとSynplifyのための全syslOアトリビュート構文のリストと例です。このセクションはこれらデバイスのためのsyslOバッファ・アトリビュートのみを記載します。設計者は論理合成アトリビュートに関する全リストについてPrecisionとSynplifyのユーザ・マニュアルを参照して下さい。これらのマニュアルはispLEVERソフトウェア・ヘルプでも利用できます。

## VHDL Synplify/Precision RTL Synthesis

PrecisionかSynplify論理合成ツールを用いる場合のため、このセクションはVHDLのすべてのsysIOアトリビュートの構文と例をリストアップします。

## 構文(シンタックス)

## 表8-12 SynplifyとPrecisionのためのVHDLアトリビュート構文

| アトリビュート(属性) | 構 文                                                                                          |

|-------------|----------------------------------------------------------------------------------------------|

| IO_TYPE     | attribute IO_TYPE: string; attribute IO_TYPE of Pinname: signal is "IO_TYPE Value";          |

| OPENDRAIN   | attribute OPENDRAIN: string; attribute OPENDRAIN of Pinname: signal is "OpenDrain Value";    |

| DRIVE       | attribute DRIVE: string; attribute DRIVE of Pinname: signal is "Drive Value";                |

| PULLMODE    | attribute PULLMODE: string; attribute PULLMODE of Pinname: signal is "Pullmode Value";       |

| PCICLAMP    | attribute PCICLAMP: string; attribute PCICLAMP of Pinname: signal is "PCIClamp Value"        |

| SLEWRATE    | attribute PULLMODE: string; attribute PULLMODE of Pinname: signal is "Pullmode Value";       |

| FIXEDDELAY  | attribute FIXEDDELAY: string; attribute FIXEDDELAY of Pinname: signal is "Fixeddelay Value"; |

| DIN         | attribute DIN: string; attribute DIN of Pinname: signal is " ";                              |

| DOUT        | attribute DOUT: string; attribute DOUT of Pinname: signal is " ";                            |

| LOC         | attribute LOC: string; attribute LOC of Pinname: signal is "pin_locations";                  |

## 例 IO TYPE

--\*\*\*Attribute Declaration\*\*\*

ATTRIBUTE IO TYPE: string;

--\*\*\*IO\_TYPE assignment for I/O Pin\*\*\*

ATTRIBUTE IO\_TYPE OF portA: SIGNAL IS "PCI33";

ATTRIBUTE IO\_TYPE OF portB: SIGNAL IS "LVCMOS33";

ATTRIBUTE IO\_TYPE OF portC: SIGNAL IS "LVDS25";

#### **OPENDRAIN**

--\*\*\*Attribute Declaration\*\*\*

ATTRIBUTE OPENDRAIN: string;

--\*\*\*OPENDRAIN assignment for I/O Pin\*\*\*

ATTRIBUTE OPENDRAIN OF portB: SIGNAL IS "ON";

#### **PCICLAMP**

--\*\*\*Attribute Declaration\*\*\*

ATTRIBUTE PCICLAMP: string;

--\*\*\*PCICLAMP assignment for I/O Pin\*\*\*

ATTRIBUTE PCICLAMP OF portA: SIGNAL IS "ON";

#### **DRIVE**

--\*\*\*Attribute Declaration\*\*\*

ATTRIBUTE DRIVE: string;

--\*\*\*DRIVE assignment for I/O Pin\*\*\*

ATTRIBUTE DRIVE OF portB: SIGNAL IS "20";

#### **PULLMODE**

--\*\*\*Attribute Declaration\*\*\*

ATTRIBUTE PULLMODE: string;

--\*\*\*PULLMODE assignment for I/O Pin\*\*\*

ATTRIBUTE PULLMODE OF portA: SIGNAL IS "DOWN"; ATTRIBUTE PULLMODE OF portB: SIGNAL IS "UP";

#### **SLEWRATE**

--\*\*\*Attribute Declaration\*\*\*

ATTRIBUTE SLEWRATE: string;

--\*\*\* SLEWRATE assignment for I/O Pin\*\*\*

ATTRIBUTE SLEWRATE OF portB: SIGNAL IS "FAST";

#### **FIXEDDELAY**

--\*\*\*Attribute Declaration\*\*\*

ATTRIBUTE FIXEDDELAY: string;

--\*\*\* FIXEDDELAY assignment for I/O Pin\*\*\*

ATTRIBUTE FIXEDDELAY OF portB: SIGNAL IS "TRUE";

### **DIN/DOUT**

--\*\*\*Attribute Declaration\*\*\*

ATTRIBUTE din : string; ATTRIBUTE dout : string;

--\*\*\* din/dout assignment for I/O Pin\*\*\*

ATTRIBUTE din OF input\_vector: SIGNAL IS " ";

ATTRIBUTE dout OF output\_vector: SIGNAL IS " ";

#### LOC

--\*\*\*Attribute Declaration\*\*\*

ATTRIBUTE LOC: string;

--\*\*\* LOC assignment for I/O Pin\*\*\*

ATTRIBUTE LOC OF input\_vector: SIGNAL IS "E3,B3,C3";

## **Verilog / Synplify**

このセクションは、Synplify合成ツールを用いる場合の、すべてのsysIOアトリビュートVerilog構文と例をリストアップします。

表8-13 Verilog / Synplifyアトリビュート構文

| アトリピュート   | 構文                                                          |

|-----------|-------------------------------------------------------------|

| IO_TYPE   | PinType PinName /* synthesis IO_TYPE="IO_Type Value"*/;     |

| OPENDRAIN | PinType PinName /* synthesis OPENDRAIN="OpenDrain Value" */ |

| DRIVE     | PinType PinName /* synthesis DRIVE="Drive Value"*/;         |

| PULLMODE   | PinType PinName /* synthesis PULLMODE="Pullmode Value"*/;    |

|------------|--------------------------------------------------------------|

| PCICLAMP   | PinType PinName /* synthesis PCICLAMP="PCIClamp Value"*/     |

| SLEWRATE   | PinType PinName /* synthesis SLEWRATE="Slewrate Value"*/;    |

| FIXEDDELAY | PinType PinName /* synthesis FIXEDELAY="Fixeddelay Value"*/; |

| DIN        | PinType PinName /* synthesis DIN=" "*/;                      |

| DOUT       | PinType PinName /* synthesis DOUT=" "*/;                     |

| LOC        | PinType PinName /* synthesis LOC="pin_locations "*/;         |

#### 例

## //IO\_TYPE, PULLMODE, SLEWRATE and DRIVE assignment

output portB /\*synthesis IO\_TYPE="LVCMOS33" PULLMODE ="UP" SLEWRATE ="FAST" DRIVE ="20"\*/;

output portC /\*synthesis IO\_TYPE="LVDS25" \*/;

#### // OPENDRAIN

input load /\* synthesis OPENDRAIN="ON" \*/;

#### // PCICLAMP

output portA /\* synthesis IO\_TYPE="PCI33" PULLMODE="PCICLAMP"\*/;

#### // Fixeddelay

input load /\* synthesis FIXEDDELAY="TRUE" \*/;

## // Place the flip-flops near the load input

input load /\* synthesis din="" \*/;

### // Place the flip-flops near the outload output

output outload /\* synthesis dout="" \*/;

#### //I/O pin location

input [3:0] DATA0 /\* synthesis loc="E3,B1,F3"\*/;

#### //Register pin location

reg data\_in\_ch1\_buf\_reg3 /\* synthesis loc="R40C47" \*/;

#### //Vectored internal bus

reg [3:0] data\_in\_ch1\_reg /\*synthesis loc ="R40C47,R40C46,R40C45,R40C44" \*/;

## **Verilog / Precision**

このセクションは、Precision RTL Synthesisツールを用いる場合の、すべてのsysIOアトリビュート Verilog構文と例をリストアップします。

#### 構文

## 表8-14 Verilog / Precisionアトリビュート構文

| アトリビュート    | 構文                                                      |

|------------|---------------------------------------------------------|

| IO_TYPE    | //Precision attribute PinName IO_TYPE IO_TYPE Value     |

| OPENDRAIN  | //Precision attribute PinName OPENDRAIN OpenDrain Value |

| DRIVE      | //Precision attribute PinName DRIVE Drive Value         |

| PULLMODE   | //Precision attribute PinName IO_TYPE Pullmode Value    |

| PCICLAMP   | //Precision attribute PinName PCICLAMP PCIClamp Value   |

| SLEWRATE   | //Precision attribute PinName IO_TYPE Slewrate Value    |

| FIXEDDELAY | //Precision attribute PinName IO_TYPE Fixeddelay Value  |

| LOC        | //Precision attribute PinName LOC pin_location          |

## 例

#### //\*\*\*\*IO\_TYPE \*\*\*

//pragma attribute portA IO\_TYPE PCI33 //pragma attribute portB IO\_TYPE LVCMOS33 //pragma attribute portC IO\_TYPE SSTL25\_II

## //\*\*\* Opendrain \*\*\*

//pragma attribute portB OPENDRAIN ON //pragma attribute portD OPENDRAIN OFF

#### //\*\*\* Drive \*\*\*

//pragma attribute portB DRIVE 20 //pragma attribute portD DRIVE 8

### //\*\*\* Pullmode\*\*\*

//pragma attribute portB PULLMODE UP

## //\*\*\* PCICLAMP\*\*\*

//pragma attribute portA PCICLAMP ON

## //\*\*\* Slewrate \*\*\*

//pragma attribute portB SLEWRATE FAST //pragma attribute portD SLEWRATE SLOW

## // \*\*\*Fixeddelay\*\*\*

//pragma attribute load FIXEDDELAY TRUE

## //\*\*\*LOC\*\*\*

//pragma attribute portB loc E3

LatticeXP2 8-15 sysIO UGJ

## 付録B デザインプランナ・ユーザGUIを用いるsysIOアトリビュート

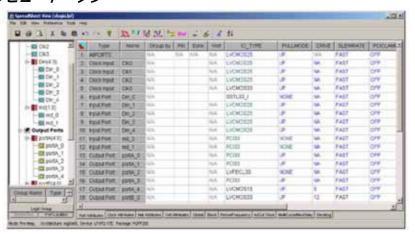

ispLEVERツールのDesign Planner GUIを用いることでsysIOバッファ・アトリビュートを割り当てることもできます。ピン・アトリビュート(Pin Attribute)タブが、設計内の全てのポートと、プリファレンスとして指定している全sysIOアトリビュートをリストします。これらの各セルをクリックすると、そのポートに有効な全てのI/Oプリファレンスのリストが与えられます。特定のIO\_TYPEが選ばれていると、そのIO\_TYPEのために有効な組み合わせDRIVE、PULLMODE、およびSLEWRATEコラムのみをリストします。ユーザは、ピン・アトリビュート・シート内のピン・ロケーション(pin location)コラムを用いることでピン位置をロックすることができます。セル上で右クリックすると、全ての利用できるピン位置がリストされます。またデザインプランナは、不正なピン割り当てを探すためにDRCチェックを実行します。

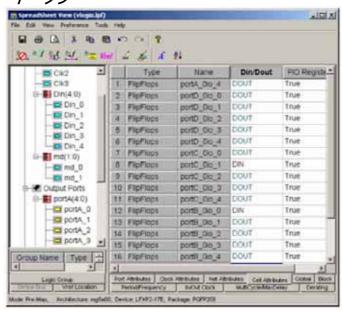

デザインプランナのセル・アトリビュート (Cell Attributes) タブを用いることで、DIN / DOUTプリファレンスを入れることができます。デザインプランナを用いて割り当てた全てのプリファレンスは、プリファレンス・ファイル (.lpf) の中に書き出されます。

図8-2と図8-3はデザインプランナのピン・アトリビュート・タブとセル・アトリビュート・タブの概観です。デザインプランナに関する詳細については、ソフトウェアのヘルプ・メニュー・オプションにあるispLEVERヘルプ・ドキュメントを参照してください。

## 図8-2 ピン・アトリビュート・タブ

図8-3 セル・アトリビュート・タブ

## 付録C プリファレンス・ファイル(ASCII)を用いるsysIOアトリビュート

sysIOバッファ制約は、プリファレンス・ファイル (.lpf) にsysIOアトリビュートとして直接入れることもできます。LPFファイルは論理合成後のFPGA制約ファイルで、デザインプランナやテキストエディタで生成・修正された論理的な制約(プリファレンス)を記述しています。また、HDLソースに含まれている論理制約も含みます。

#### **IOBUF**

このプリファレンスは、アトリビュートのIO\_TYPE、PULLMODE、SLEWRATE、PCICLAMP、およびDRIVEを割り当てるのに用いられます。

#### 構文

IOBUF [ALLPORTS | PORT <port\_name> | GROUP <group\_name>] (keyword=<value>)+;

#### ここで:

<port\_name> = これらは実際のトップレベル・ポート名ではなく、ポートに付けられた信号名である必要があります。物理設計ファイル(.ncd)内のPIOはこの慣例(コンベンション)を用いて命名されます。複数のリスティングやワイルドカードの場合は、GROUPを用いないといけません。

+-9- =  $10_{-}$  TYPE, OPENDRAIN, DRIVE, PULLMODE, PCICLAMP, SLEWRATE.

#### 例

IOBUF PORT "port1" IO\_TYPE=LVTTL33 OPENDRAIN=ON DRIVE=8 PULLMODE=UP PCICLAMP=OFF SLEWRATE=FAST;

DEFINE GROUP "bank1" "in\*" "out\_[0-31]";

IOBUF GROUP "bank1" IO TYPE=SSTL18 II;

#### LOCATE

明示されたコンポーネントに適用されるとき、このプリファレンスは、指定されたサイトにそのコンポーネントを配置してロックします。指定されたマクロ・インスタンスに適用される場合、(1)マクロの参照コンポーネントを指定されたサイトに配置し、(2)マクロ内のライブラリ・ファイルに事前に配置された全てのコンポーネントをサイトに配置し、そして(3)これらのコンポーネントのすべてをそのサイトにロックします。以下にLOCATE文法と例の幾つかを示します。より詳細はispLEVERへルプ・ドキュメントを参照してください。

### 構文

LOCATE [COMP <comp\_name> | MACRO <macro\_name>] SITE <site\_name>; LOCATE VREF <vref name> SITE <site name>;

注; comp\_name、macro\_name、あるいはsite\_nameがアルファ・キャラクタ以外の何か(例えば、"11C7") で始まる場合、名前をクウォート記号で囲まなければなりません。ワイルドカード表記は<comp\_name>で許容されています。

#### 例

このコマンドはポートClk0をサイトA4に置きます。

LOCATE COMP "CIk0" SITE "A4";

このコマンドはコンポーネントPFU1をサイトにR1C7置きます。

LOCATE COMP "PFU1" SITE "R1C7";

このコマンドはbus1をROW 3に、bus2をCOL4に置きます。

LOCATE BUS "bus1" ROW 3; LOCATE BUS "bus2" COL 4;

#### **USE DIN CELL**

このプリファレンスは、入力フリップフロップとして用いる特定のレジスタを指定します。

#### 構文

USE DIN CELL <cell\_name>;

ここで: <cell\_name> := string

例

USE DIN CELL "din0";

#### **USE DOUT CELL**

出力フリップフロップとして用いる特定のレジスタを指定します。

## 構文

USE DOUT CELL <cell\_name>;

ここで: <cell\_name> := string

例

USE DOUT CELL "dout1";

## **GROUP VREF**

このプリファレンスは、バンク内の1本の $V_{REF}$  ピンに関連づけられる必要があるすべてのコンポーネントをグループ化するのに用いられます。

### 構文

LOCATE VREF <vref\_name> SITE <site\_name>;

### 例

IOBUF GROUP <group\_name> BANK=<bank\_name> VREF=<Vref\_name>; LOCATE VREF "ref1" SITE PR29C; LOCATE VREF "ref2" SITE PR48B; IOBUF GROUP "group1" IO\_TYPE=SSTL18\_II BANK=0 VREF=vref1;

LatticeXP2 8-18 sysIO UGJ