# LatticeECP2M SERDES/PCS ユーザガイド

# PCSの概要

LatticeECP2M™ FPGAファミリは業界をリードするアーキテクチャを持ち、高性能FPGAファブリックと、高性能I/O、および大規模組み込みメモリを単一チップに集積しています。また、すべてのLatticeECP2Mデバイスが特徴としているのは、組み込みSERDES(最大16チャネル)とこれに付随するPhysical Coding Sublayer(PCS)ロジックです。多数の業界標準高速データ転送プロトコルをサポートするためにPCSロジックを構成することができます。

各チャネルに専用のPCSロジックは送受信SERDESを含み、データレート3.125Gbpsの高速全二重シリアルデータ転送に対応します。PCSロジックはイーサネット(1GbEとSGMII)、PCI Express、CPRI、およびOBSAIを含む一連のポピュラーなデータプロトコルをサポートするために各チャネルを構成することができます。さらに、ユーザの高速データインターフェイス設計に柔軟に対応できるように、多くの構成でプロトコルベースのロジックを完全か部分的にバイパスすることができます。

またPCSはバイパスモードを提供し、SERDESからFPGAロジックとは8ビット、または10ビットの直接インターフェイスがあります。また、それぞれのSERDESピンは個別にDC結合に設定することでき、高速動作と、シリアル・デジタルビデオ(SDI)アプリケーションのような低速動作を、同じSERDESピンで対応することが可能です。

# 機能

- ・最大16チャネルの高速SERDES

- チャネルあたり250Mbpsから3.125Gbps

- 3.125Gbps動作時にチャネルあたり100mWの低消費電力

- フォームファクタの小さいバックプレーン動作の為の受信等化と送信プリエンファシス

- PCI Express、イーサネット(1GbEとSGMII)、および他の複数の規格をサポート

- ユーザ指定の汎用(Generic) 8b10bモードをサポート

- PCI Expressのビーコンをサポート

- 低速入力用のOOB (out-of-band)信号インターフェイス(ビデオ用途)

- ・複数のクロックレートをサポート

- 各PCSクワッド用に個別の基準クロックが使用でき、単一デバイスで複数のプロトコルレートを容易に扱うことが可能

- ・フル機能の組み込み物理コーディング・サブレイヤ(PCS)ロジックで業界標準プロトコルをサポート

- デバイス当たり最大16チャネルの全二重データ通信をサポート

- 単一チップで複数プロトコルをサポート

- 8b10bベースの広く採用されているパケットプロトコルをサポート

- SERDES OnlyモードはFPGAロジックと8ビット、または10ビットで直接インターフェイスが可能

- ・ギガビット・イーサネットのサポート

- IEEE 1000BASE-Xに準拠

- 8b10bエンコーディング/デコーディング

- 自動ネゴシエーションをサポートするための受信データストリーム中への /l2/ シンボル挿入

- コンマキャラクタのワードアライメント

- クロックトレランス補償 (CTC) 回路

LatticeECP2M 8-1 SERDES/PCS-UGJ

- ・PCI Expressサポート

- 単一PCSクワッドでx1またはx4をサポート

- ワードアライナを集積

- 8b10bエンコーディング/デコーディング

- クロックトレランス補償(CTC)回路

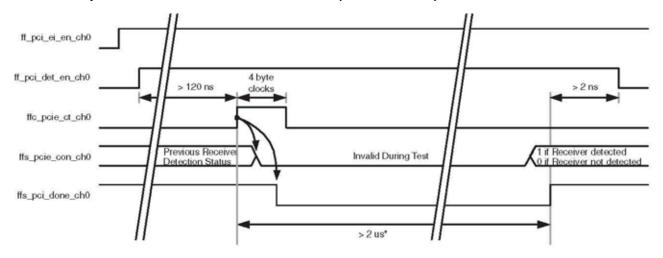

- 電気的アイドルとレシーバ検出のサポート

- ビーコン送信とビーコン検出のサポート

- ・複数プロトコルに準拠するクロックトレランス補償(CTC)ロジック

- 基準クロックと受信データレートとの周波数差を補償

- 長さ1/2/4バイトのユーザ定義スキップパターンの使用が可能

- ・システムデバッグのためのループバック・モードを集積

- システムデバッグのために3つのループバック・モードを提供

# サポート規格

サポートする規格を表8-1にリストアップします。

表8-1 サポートするSERDES規格 (フルサポート)

| 規格                                 | レート [Mbps]            | REFCLK [MHz]              | FPGA CLK<br>[MHz]     | 符号化             | 信号タイプ |

|------------------------------------|-----------------------|---------------------------|-----------------------|-----------------|-------|

| PCI Express                        | 2500                  | 100                       | 250                   | 8b10b           | CML   |

| GbE/SGMII                          | 1250                  | 125                       | 125                   | 8b10b           | CML   |

| Generic 8b10b                      | 250 ~ 3125            | 25.0 ~ 312.5              | 25.0 ~ 312.5          | 8b10b/なし        | CML   |

| 10-bit SERDES<br>Only <sup>1</sup> | 250 ~ 3125            | 25.0 ~ 312.5              | 25.0 ~ 312.5          | なし              | CML   |

| 8-bit SERDES<br>Only <sup>1</sup>  | 250 ~ 3125            | 25.0 ~ 312.5              | 25.0 ~ 312.5          | なし              | CML   |

| SD-SDI <sup>2</sup>                | 143, 177, 270,<br>360 | 14.3, 17.7, 27.0,<br>36.0 | 143, 177, 135,<br>180 | SMPTEスクランブ<br>ル | CML   |

| HD-SDI                             | 1483.5, 1485          | 148.35, 148.5             | 148.35, 148.5         | SMPTEスクランブ<br>ル | CML   |

| CPRI                               | 614.4<br>1228.8       | 61.44<br>122.88           | 61.44<br>122.88       | 8b10b           | CML   |

<sup>1.</sup>SERDES Onlyモードは8ビットと10ビット共に、リンクアライン/コンマアラインと、8b10bエンコーダ/デコーダ、およびCTCをバイパスします。CDRはバイパスしません。

上記SERDESモードでXAUI、SRIO、OBSAI、CPRI、1XFC、2XFC、PICMG3.1、PICMG3.4、PICMG3.5、および3G-SDIの各規格をサポートすることができます。より詳細な情報が必要な場合はラティスセミコンダクターのテクニカルサポート・グループにご連絡ください。

LatticeECP2M 8-2 SERDES/PCS-UGJ

<sup>2.</sup>標準精細度(SD)用のシリアルデジタル・インターフェイス(SDI): 143Mbps、177MbpsはSERDES/PCSブロックをバイパスします。クロックとデータはRXピンからBSCANパスを通してFPGAコアに入ります。CDRはFPGAコアで行われます。送信方向では、これらの低いビットレートにはデシメーションが用いられます。FPGA内でCDRを実行するためには、14.3MHzと17.7MHzの基準クロックが必要です。270Mbpsは最も一般的な周波数です。これは10ビットのデータパスを通ります。

# アーキテクチャ概要

PCSロジックは独立する4系統の全二重データチャンネル用のロジックを含み、クワッドごとにアレンジされています。表8-2はLatticeECP2Mファミリで各デバイスにあるSERDES/PCSクワッドを示します。

表8-2 LatticeECP2MファミリのデバイスごとのSERDES/PCSクワッド

| デバイス          | ECP2M20 | ECP2M35 | ECP2M50 | ECP2M70 | ECP2M100 |

|---------------|---------|---------|---------|---------|----------|

| Quad URC (右上) | Yes     | Yes     | Yes     | Yes     | Yes      |

| Quad LRC (右下) | -       | -       | Yes     | Yes     | Yes      |

| Quad ULC (左上) | -       | -       | -       | Yes     | Yes      |

| Quad LLC (左下) | -       | -       | -       | Yes     | Yes      |

#### PCSクワッド

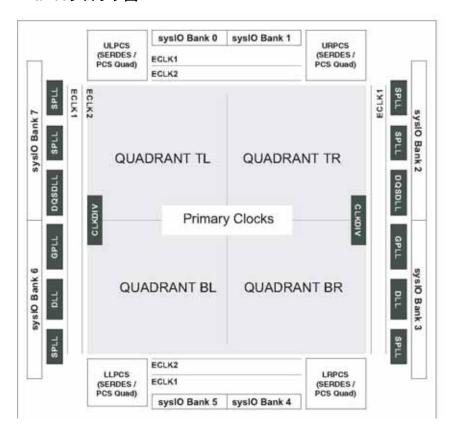

図8-1はデバイス内でPCSクワッドの配置を示すLatticeECP2Mのレイアウトです。(4つのクワッドを含む最も大きいアレイが示されています。他のデバイスではクワッド数は少なくなります。)

図8-1 LatticeECP2M70/100プロック図

全てのクワッドは複数のプロトコルベースのモードの1つにプログラムすることができます。各クワッドはそれ自身の基準クロックを必要とし、外部からパッケージピンを介して、或いは内部FPGAロジックから供給することができます。

各クワッドにはそれぞれ基準クロックがあるので、クワッドが異なれば同一チップでも違う規格をサポートすることができます。この機能はLatticeECP2Mファミリを、異なる規格間のブリッジ機能の実装に理想的な

LatticeECP2M 8-3 SERDES/PCS-UGJ

#### デバイスにします。

PCSクワッドは単に業界標準プロトコル専用なだけではありません。多くのユーザ定義のデータ操作モードのために、各クワッド(そしてクワッド内の各チャネル)をプログラムすることができます。例えば、ユーザ定義のワードアライメントとクロックトレランス補償を司るモードは、非プロトコル動作としてプログラムすることができます。

#### PCSクワッドとチャネル

デバイスの各クワッドは最大4チャネルの全二重データをサポートします。アプリケーションによって、ユーザは単一クワッドで1~4チャネルのいづれも利用することができます。どのクワッドであれ、ユーザが各チャネルごとに独立して設定できる多くのオプションがあります。

また図8-1には4つのPCSクワッド、合計16のPCSチャネルを含むデバイスの例を示します。それぞれのクワッドはLatticeECP2Mアレイ内を4分割した位置に従って命名されています。すなわちURPCS(右上のPCS)、ULPCS(左上のPCS)、LRPCS(右下のPCS)、LLPCS(左下のPCS)です。

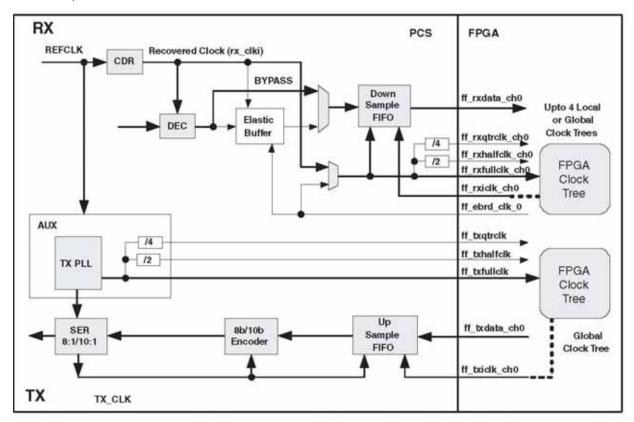

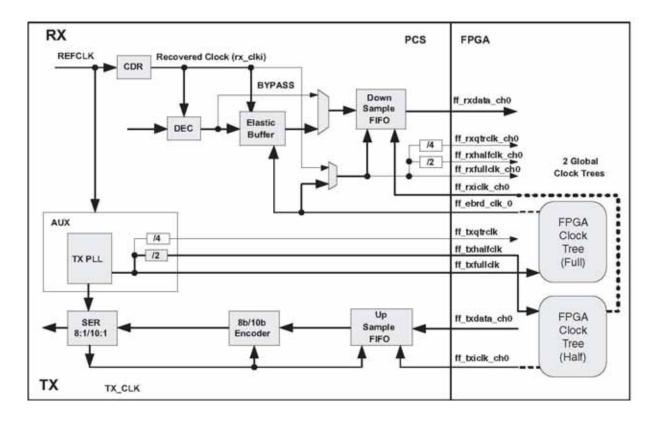

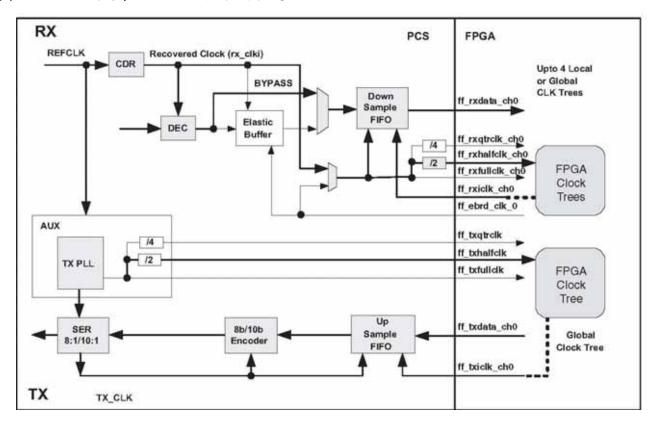

# チャネル単位のPCS/FPGAインターフェイス・ポート

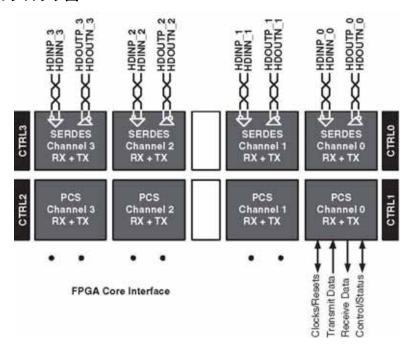

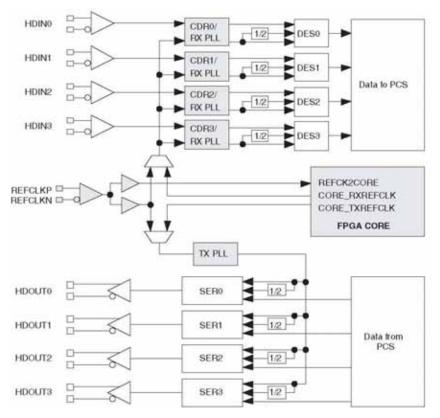

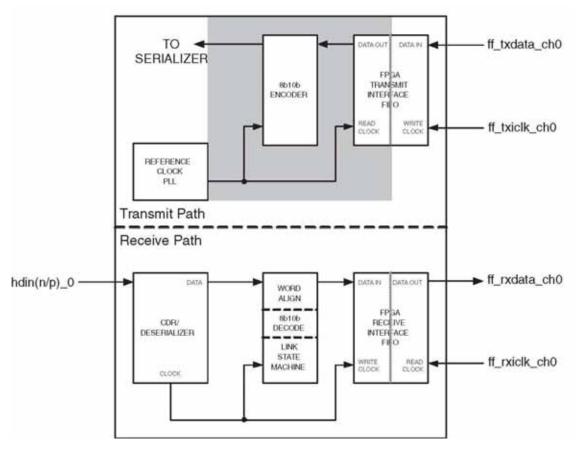

選ばれたモードにかかわらず、すべてのPCSクワッドはパッケージピンに共通の外部高速シリアル・インターフェースを持っています。しかしながら、各クワッドとFPGAロジック間のI/Oポートには、それぞれのPCSモードで選択されたプロトコルに適切となる独自のリストがあります。本ドキュメントでは各モード用のクワッド入出力信号の詳細を記述します。単一クワッド内のチャネルを示す概略図を図8-2に示します。

#### 図8-2 PCSクワッドのブロック図

### PCSクワッドの配置

LatticeECP2M-50以上の規模のデバイスは2~4つのPCSクワッドを含んでいます。

ユーザは、プリファレンス(設計制約)ファイルの中でLOCATEプリファレンスを用いることで、各PCSクワッド配置を所望の位置に指定することができます。LOCATE制約については、以下に例を示します。

LOCATE COMP "PCS\_instantiation\_1" SITE "URPCS"; (訳注; PCS\_instantiation\_1はコンポーネント名)

LatticeECP2M 8-4 SERDES/PCS-UGJ

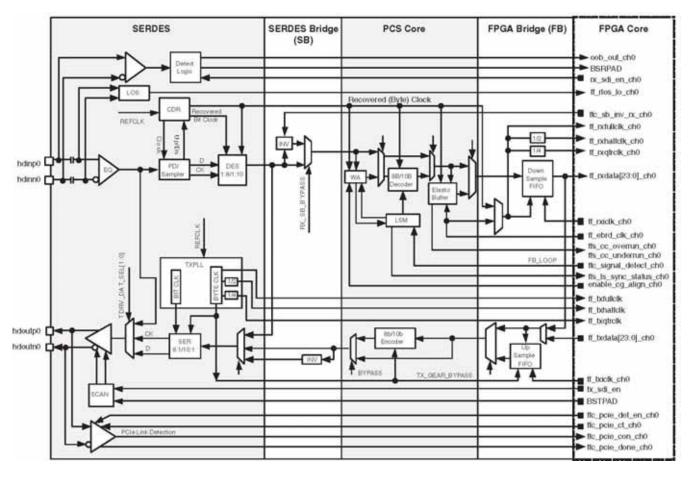

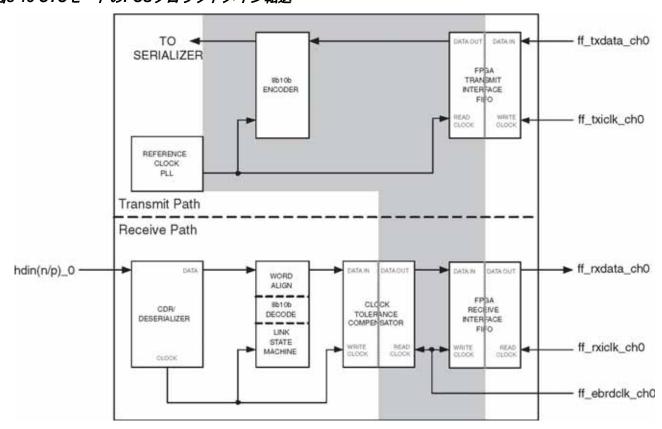

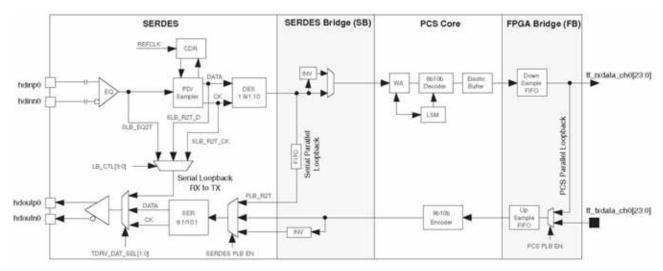

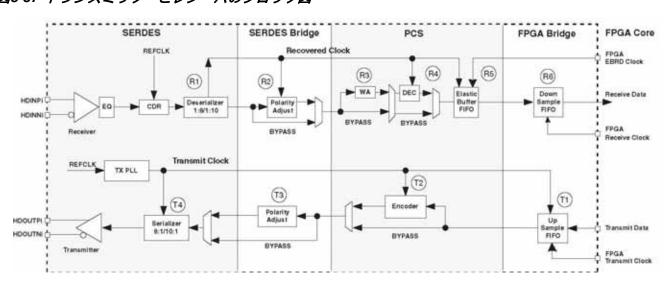

### 詳細なチャネルプロック図

図8-3は、LatticeECP2M SERDES/PCS単一チャネルの主要な機能の詳細なブロック図を表します。この図にはFPGAでユーザロジックから見えるすべての主要なブロック、および制御とステータス信号の大部分が示されています。また、この図はチャネルSERDES、SERDESブリッジ、PCSコア、およびFPGAブリッジの主要なサブブロックも示しています。

図8-3 LatticeECP2M SERDES/PCSチャネルの詳細プロック図

以下にFPGAインターフェイス信号の概要説明が続きます。

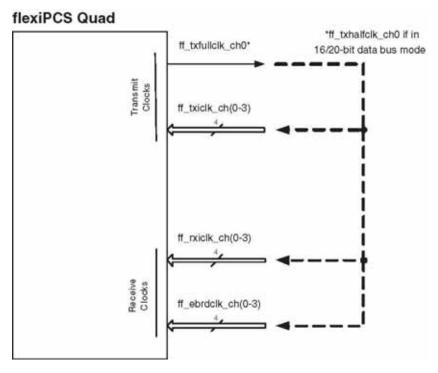

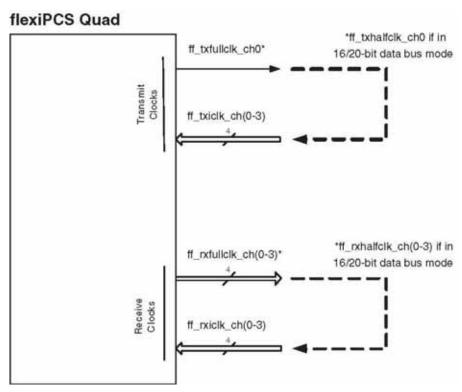

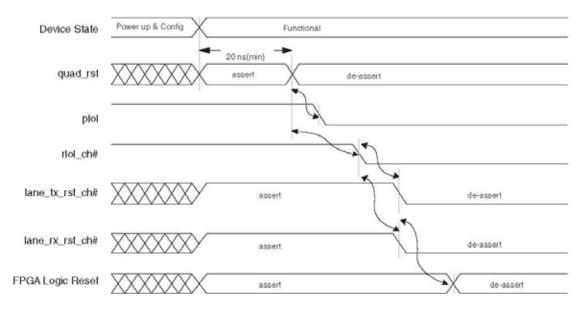

### クロックとリセット

PCSクワッドはFPGAロジック・インターフェイスに対して、(Tx PLLに)ロックした基準クロックおよびチャネルごとの受信再生クロックを供給します。各PCSクワッドはこれらのクロックをプライマリ、及びセカンダリのFPGAクロック配線に提供します。また、各クワッドのPCS/FPGAインターフェイスには、FPGAファブリックから全4チャネルに供給する送受信クロックポートがあります。

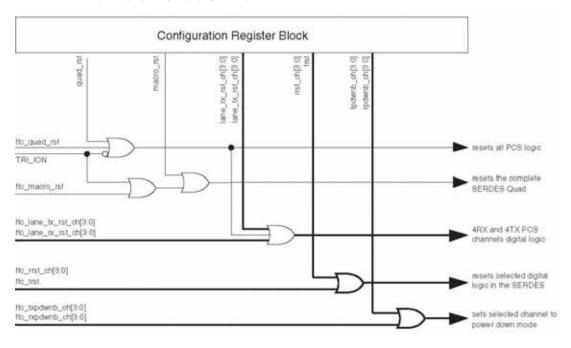

各クワッドには、クワッド内のSERDESとPCSロジックの両方か、或いはSERDESのみを強制リセットする 信号入力があります。さらに送受信方向共に、PCSロジック専用のリセットが各チャネルごとにあります。

#### 送信データバス

送信データパスの信号はFPGAからPCSブロック内のFPGAブリッジまでです。高速伝送規格のために、(制御/ステータス信号と共に)8ビット幅の内部PCSデータパス用に2:1変換すること(ギアリング)ができます。

LatticeECP2M 8-5 SERDES/PCS-UGJ

PCI Express x1用インターフェイスの最高速度は2:1変換しないモードで250MHzです。ギアリング2:1あり (すなわち、16ビット幅データパス)で、最大速度は156.25MHz(XAUI 4xチャネルモード用)です。SERDES とPCSは、156.25MHz(2:1ギアリングあり)のインターフェイス速度に対応する3.125Gbpsデータレートまで サポートします。

| 表8-3 異なるモードごとの送信データバスのと | シッ | 卜配分 |

|-------------------------|----|-----|

|-------------------------|----|-----|

| データビット<br>(ff_tx_d[23:0]) | GE           | XAUI      | PCI Express<br>(8b10b) | 8-bit I/F (8b10b)     | 10-bit I/F <sup>2, 3</sup> |

|---------------------------|--------------|-----------|------------------------|-----------------------|----------------------------|

| [11], [23]                | Correct_disp | 0でドライブ    | pcie_ei_en             | correct_disp          | 0でドライブ                     |

| [10], [22]                | xmit 4       | 0でドライブ    | disp_sel               | disp_sel <sup>1</sup> | 0でドライブ                     |

| [9], [21]                 | 0でドライブ       | 0でドライブ    | force_disp             | force_disp 1          | txd [9]                    |

| [8], [20]                 | k_cntrl      | txc       | k_cntrl                | k_cntrl               | txd [8]                    |

| [7:0], [19:12]            | txd [7:0]    | txd [7:0] | txd [7:0]              | txd [7:0]             | txd [7:0]                  |

- 1. G8B10Bモードで動作しているとき、force\_disp信号はデータワード[7:0]に対してdisp\_sel信号で選択された コラムのビットにディスパリティを強制します。disp\_selが1の場合、10ビットコードは現在のRD+(正のディスパリティ)コラムから選択されます。disp\_selが0の場合,10ビットコードは現在のRD-(負のディスパリティ) コラムから選択されます

- 2. データにギアリングがある(2:1)とき、低位ビット(ff\_tx\_[9:0])が最初に送信されるオクテットであり、高位ビット(ff\_tx\_d[19:10])が2番目に送信されるオクテットです。データがギアリングなしの場合、低位ビット(ff\_tx\_d[9:0])が有効なビットであり、高位ビットは全てゼロにされるべきです。

- 3.8ビットモード、或いは10ビットモードで用いられるインターフェイスと8b10bエンコーダ/デコーダはバイパスされます。例えば、SDIなど。

- 4. 自動ネゴシエーション・ステートマシンは信号xmitを生成します。これはハードロジック内でGigE Idle SMと相互にインターフェイスする為に用いられます。

### 受信データバス

受信パスの信号は、PCSブロック内のFPGAブリッジからFPGAまでです。データパスは8ビット幅の内部 PCSデータパス用に2:1ギアリングされるかもしれません。ソフトウェア・レジスタビットでギアリングを禁止することが可能で、その場合バス幅は半分にされます。データがギアリングされるとき、低位ビット (ff\_rx\_d[9:0])が最初に受信されたオクテットであり、高位ビット(ff\_rx\_d[9:0])が2番目に受信されたオクテットです。データがギアリングなしの場合、低位ビット(ff\_rx\_d[9:0])が有効なビットであり、高位ビットは使用されるべきではありません。

表8-4 異なるモードごとの受信データのバスビット配分

| データピット<br>(ff_rx_d[23:0]) | GE <sup>1</sup> | XAUI      | PCI Express<br>(8b10b) <sup>2</sup> | 8-bit I/F (8b10b) <sup>1</sup> | 10-bit I/F |

|---------------------------|-----------------|-----------|-------------------------------------|--------------------------------|------------|

| [11], [23]                | rx_even 2       | NC        | rxstatus[2]3                        | NC                             | NC         |

| [10], [22]                | cv              | cv        | rxstatus[1]3                        | cv                             | NC         |

| [9], [21]                 | disp_err        | disp_err  | rxstatus[0]3                        | disp_err                       | rxd [9]    |

| [8], [20]                 | k_cntrl         | txc       | k_cntrl                             | k_cntrl                        | rxd [8]    |

| [7:0], [19:12]            | rxd [7:0]       | rxd [7:0] | rxd [7:0]                           | rxd [7:0]                      | rxd [7:0]  |

- 1. コードバイオレーションがあるとき、PCS 8b10bパケットデコーダはその出力を0xEEとKアサートに置き替えます(K=1かつd=EEは8b10b符号スペースに定義がありません)。

- 2. rx\_evenはGigE自動ネゴシエーションと受信ステートマシン(FPGAロジックで実装される)での使用のためにGigEリンク・ステートマシンによって生成される信号です。

0

LatticeECP2M 8-6 SERDES/PCS-UGJ

#### 制御

各モードにはそれ特有の制御信号の組があり、FPGAロジックから様々なPCS機能の直接制御を可能にします。通常これらの制御入力は、それぞれの制御レジスタビットへのライト操作と同等の作用を与えます。 ispLEVERデザインツールは、これらのポートをFPGAインターフェイスに取り出すためのオプションをユーザに与えます。

#### ステータス

各モードにはそれ特有のステータスやアラーム信号の組があり、FPGAロジックからモニタできます。通常これらのステータス出力は、特定のステータス・レジスタビットにそれぞれ対応しています。ispLEVERデザインツールは、これらのポートをPCS FPGAインターフェイスに取り出すためのオプションをユーザに与えます。制御とステータスに関する詳細な情報については "モード特有の制御/ステータス信号" セクションを参照してください。

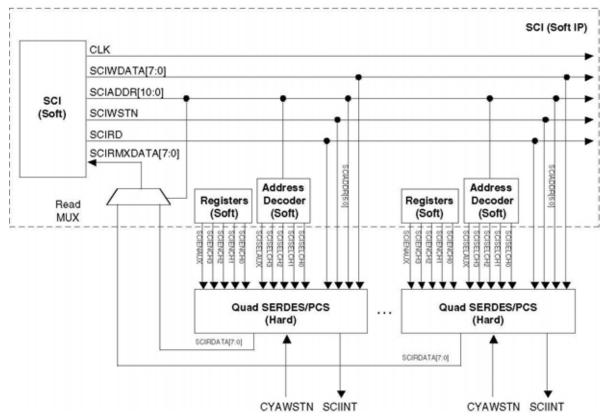

# SCI (SERDESクライアント・インターフェイス)バス

SCIはソフトIPで、SERDES/PCSクワッドブロックがコンフィグレーション・メモリセルではなく、レジスタによって制御されることを可能にします。それは簡単なレジスタ・コンフィグレーション・インターフェイスです。

### このテクニカルノートの利用

ラティスからのispLEVERデザインツールはPCSの全モードをサポートします。殆んどのモードが特定の業界標準データ通信プロトコルのアプリケーション専用です。他のモードは、ユーザが自身のカスタムアプリケーション設定を定義する、より汎用のモードです。 ispLEVERデザインツールで、ユーザのデザインで使用するモードに各クワッドを定義します。

このドキュメントはispLEVERによってサポートされるSERDESとPCSのすべてのモードの動作について説明します。このドキュメントは組み込みSERDESと、連携するPCSロジックの完全な機能を詳細に記述します。組み込みSERDESの電気的特性とタイミング特性はLatticeECP2/Mファミリデータシートにあります。PCSロジックの動作はPCSセクションにあり、SCIバスを介してアクセスすることができるSERDES/PCSロジックに関連する全ステータス・制御レジスタは、その一覧表がメモリマップ・セクションに提供されています。パッケージピン配置情報はLatticeECP2/Mファミリデータシートのアーキテクチャ・セクションに含まれています。

LatticeECP2M 8-7 SERDES/PCS-UGJ

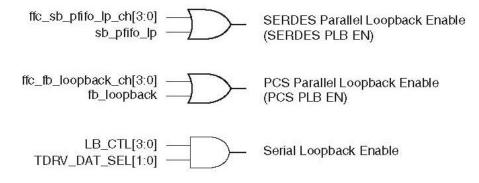

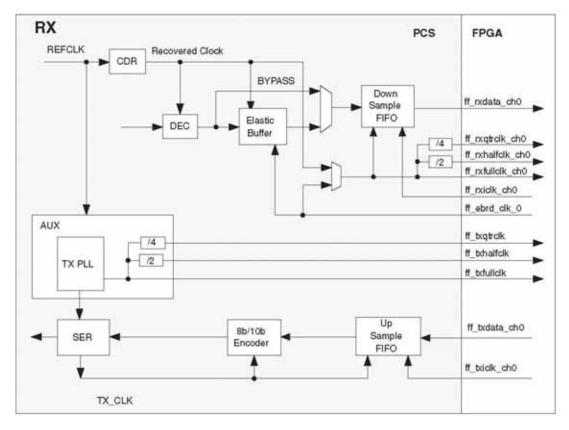

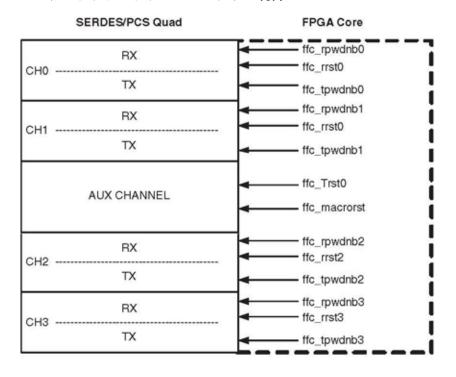

# SERDES/PCS

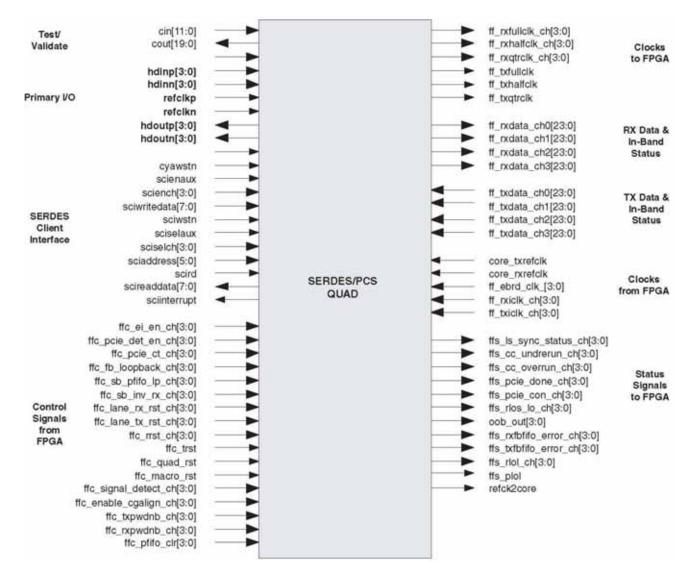

クワッドは4チャネルのRxとTx回路、及びTx PLLを含む補助チャネルを含んでいます。Tx PLLへの基準クロックは、基準クロック差動入力ピンかFPGAコアから供給することができます。クワッドSERDES/PCSマクロは4レーンのデータのためにシリパラ変換とパラシリ変換機能を実行し、マクロ内のPLLはFPGAロジックにシステムクロックを提供します。またクワッドはTxとRx各回路で、フルデータレートとハーフデータレート動作モードの両方を独立してサポートします。ブロックレベルの図が図8-4で示されています。

#### 図8-4 SERDES\_PCSブロックの信号インターフェイス

### I/O定義

表8-5にPCSクワッドに対するすべてのデフォルトおよびオプションのI/Oをリストアップします。ユーザは、IPexpress GUIを用いることでPCSクワッドのオプションポートを選ぶことができます。

LatticeECP2M 8-8 SERDES/PCS-UGJ

# 表8-5 SERDES\_PCS I/O記述

| 信号名                                     | I/O  | タイプ    | 記述                                                       | Default /<br>Optional |

|-----------------------------------------|------|--------|----------------------------------------------------------|-----------------------|

| プライマリI/O, SERDESク                       | フワッド |        |                                                          |                       |

| hdinp0                                  | I    | チャネル   | 高速CML非反転入力、チャネル0                                         | D                     |

| hdinn0                                  | I    | チャネル   | 高速CML反転入力、チャネル0                                          | D                     |

| hdinp1                                  | I    | チャネル   | 高速CML非反転入力、チャネル1                                         | D                     |

| hdinn1                                  | I    | チャネル   | 高速CML反転入力、チャネル1                                          | D                     |

| hdinp2                                  | - 1  | チャネル   | 高速CML非反転入力、チャネル2                                         | D                     |

| hdinn2                                  | I    | チャネル   | 高速CML反転入力、チャネル2                                          | D                     |

| hdinp3                                  | I    | チャネル   | 高速CML非反転入力、チャネル3                                         | D                     |

| hdinn3                                  | ı    | チャネル   | 高速CML反転入力、チャネル3                                          | D                     |

| hdoutp0                                 | 0    | チャネル   | 高速CML非反転出力、チャネル0                                         | D                     |

| hdoutn0                                 | 0    | チャネル   | 高速CML反転出力、チャネル0                                          | D                     |

| hdoutp1                                 | 0    | チャネル   | 高速CML非反転出力、チャネル1                                         | D                     |

| hdoutn1                                 | 0    | チャネル   | 高速CML反転出力、チャネル1                                          | D                     |

| hdoutp2                                 | 0    | チャネル   | 高速CML非反転出力、チャネル2                                         | D                     |

| hdoutn2                                 | 0    | チャネル   | 高速CML反転出力、チャネル2                                          | D                     |

| hdoutp3                                 | 0    | チャネル   | 高速CML非反転出力、チャネル3                                         | D                     |

| hdoutn3                                 | 0    | チャネル   | 高速CML反転出力、チャネル3                                          | D                     |

| refclkp                                 | ı    | クワッド   | 基準クロック非反転入力、専用CML入力                                      | D                     |

| refclkn                                 | ı    | クワッド   | 基準クロック反転入力、専用CML入力                                       | D                     |

| 送受信データバス(詳細な                            | バス使ん | 用法について | よ表8-3を参照)                                                | -                     |

| ff_rxdata_ch0[23:0]                     | I    | チャネル   | チャネル0受信パスのデータ信号                                          | D                     |

| ff_rxdata_ch1[23:0]                     | 1    | チャネル   | チャネル1受信パスのデータ信号                                          | D                     |

| ff_rxdata_ch2[23:0]                     | ı    | チャネル   | チャネル2受信パスのデータ信号                                          | D                     |

| ff_rxdata_ch3[23:0]                     | I    | チャネル   | チャネル3受信パスのデータ信号                                          | D                     |

| ff_txdata_ch0[23:0]                     | 0    | チャネル   | チャネル0送信パスのデータ信号                                          | D                     |

| ff_txdata_ch1[23:0]                     | 0    | チャネル   | チャネル1送信パスのデータ信号                                          | D                     |

| ff_txdata_ch2[23:0]                     | 0    | チャネル   | チャネル2送信パスのデータ信号                                          | D                     |

| ff_txdata_ch3[23:0]                     | 0    | チャネル   | チャネル3送信パスのデータ信号                                          | D                     |

| 制御信号                                    |      |        | 1                                                        | -                     |

| ffc_sb_inv_rx_ch[3:0]                   | I    | チャネル   | 受信データの反転制御<br>1 = データを反転<br>0 = データを反転しない                | 0                     |

| ffc_enable_cgalign_ch[3:0] <sup>4</sup> | I    | チャネル   | コンマアライナを制御<br>1 = コンマアライナをイネーブル<br>0 = コンマアライナを現在の位置にロック | 0                     |

| ffc_signal_detect_ch[3:0] <sup>4</sup>  | I    | チャネル   | リンクステートマシン (LSM) を制御<br>1 = LSMをイネーブル<br>0 = LSMをディセーブル  | 0                     |

| ffc_fb_loopback_ch[3:0]                 | 1    | チャネル   | FPGAブリッジ・ループバック<br>1 = RxからTxへのループバックをイネーブル<br>0 = 通常動作  | 0                     |

LatticeECP2M 8-9 SERDES/PCS-UGJ

|                                     |   |      | SERDESブリッジ・パラレルループバック                                                                                                             |   |

|-------------------------------------|---|------|-----------------------------------------------------------------------------------------------------------------------------------|---|

| ffc_sb_pfifo_lp_ch[3:0]             | I | チャネル | 1 = RxからTxへのループバックをイネーブル<br>0 = 通常動作                                                                                              | 0 |

| ffc_pfifo_clr_ch[3:0]               | I | チャネル | SERDESブリッジ・パラレルループバックFIFO<br>のクリア<br>1 = ループバックFIFOをリセット<br>0 = 通常のループバック動作                                                       | D |

| rx_sdi_en                           | I | チャネル | BSCANモードのみで使用                                                                                                                     | 0 |

| tx_sdi_en                           | I | クワッド | BSCANモートのみで使用                                                                                                                     | U |

| リセット信号                              |   |      |                                                                                                                                   |   |

| ffc_lane_rx_rst_ch[3:0]             | I | チャネル | Highアクティブ、非同期入力。PCS内の個々の<br>Rxチャネルロジックのみをリセット。                                                                                    | D |

| ffc_lane_rx_tst_ch[3:0]             | I | チャネル | Highアクティブ、非同期入力。PCS内の個々のTxチャネルロジックのみをリセット.                                                                                        | D |

| ffc_rrst_ch[3:0]                    | I | チャネル | Highアクティブ、非同期入力。SERDES Rxチャネル内の一部ロジックのみをリセット。                                                                                     | D |

| ffc_trst                            | I | クワッド | Highアクティブ、非同期入力。SERDES全Txチャネル内の一部ロジックをリセット。                                                                                       | D |

| ffc_quad_rst                        | I | クワッド | Highアクティブ、非同期入力。補助チャネルを<br>含むSERDES全チャネルをリセット。                                                                                    | D |

| ffc_macro_rst                       | I | クワッド | Highアクティブ、SERDESクワッドへの非同期入力。PCSロジック以外の補助チャネルを含むSERDES全チャネルをリセット。ソフトウェア・レジスタビットfpga_reset_enableとゲートされる。fpga_reset_enableのデフォルトは1。 | D |

| ffc_txpwdnb_ch[3:0]                 | I | チャネル | Lowアクティブ送信チャネルパワーダウン。<br>0 = 送信チャネルパワーダウン                                                                                         | D |

| ffc_rxpwdnb_ch[3:0]                 | Ι | チャネル | Lowアクティブ受信チャネルパワーダウン。<br>0 = 受信チャネルパワーダウン                                                                                         | D |

| ステータス信号                             |   |      |                                                                                                                                   |   |

| ffs_rlos_lo_ch[3:0]                 | 0 | チャネル | 各チャネル用LOS検出。閾値設定にはレジスタ<br>ビットrlos_hset[2:0]が用いられる。Low側の閾<br>値はユーザからアクセスできない。<br>1 = LOS<br>0 = 信号検出                               | D |

| ffs_ls_sync_status_ch[3:0]          | 0 | チャネル | 1 = レーンはコンマに同期<br>0 = レーンはコンマを不検出.                                                                                                | D |

| ffs_cc_underrun_ch[3:0] 6           | 0 | チャネル | 1 = Rxクロック補償FIFOのアンダーランエラー<br>0 = FIFOエラーなし                                                                                       | 0 |

| ffs_cc_overrun_ch[3:0] <sup>6</sup> | 0 | チャネル | 1 = Rxクロック補償FIFOのオーバーランエラー<br>0 = FIFOエラーなし                                                                                       | 0 |

| ffs_rxfbfifo_error_ch[3:0]          | 0 | チャネル | 1 = Rx FPGAブリッジFIFOエラー<br>0 = FIFOエラーなし                                                                                           | D |

| ffs_txfbfifo_error_ch[3:0]          | 0 | チャネル | 1 = Tx FPGAブリッジFIFOエラー<br>0 = FIFOエラーなし.                                                                                          | D |

| ffs_rlol_ch[3:0]                    | 0 | チャネル | 1 = Rx CDR LOL<br>0 = ロックを維持                                                                                                      | D |

| ffs_plol                            | 0 | クワッド | 1 = Tx PLL LOL<br>0 = ロックを維持                                                                                                      | D |

LatticeECP2M 8-10 SERDES/PCS-UGJ

| oob_out_ch[3:0] <sup>3</sup> | 0             | チャネル     | FPGA内ビデオSERDES用へのチャネルのシングルエンド出力                                                                                                                                                          | D |

|------------------------------|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| refck2core                   | 0             | クワッド     | FPGAへの基準クロック                                                                                                                                                                             | 0 |

| FPGAへのクロック信号                 |               |          |                                                                                                                                                                                          |   |

| ff_rxfullclk_ch[3:0]         | 0             | チャネル     | Rxチャネル再生クロック。ユーザモードではソースは常にチャネルの再生クロック。GbEや10GbEなどCTCサポートの規格では、ソースは当該送信チャネルのシステムクロック。PCSバイパスモードでもTxシステムクロックであり、8b10bモードか8b10bデコーダをディセーブルして(10-bit or 20-bit data path)実行する"raw"モードが必要です。 | D |

| ff_rxhalfclk_ch[3:0]         | 0             | チャネル     | Rxチャネル再生ハーフクロック。2:1ギアリング<br>では2分周された出力。                                                                                                                                                  | D |

| ff_rxqtrclk_ch[3:0]          | 0             | チャネル     | Rxチャネル再生クオータ(1/4)クロック。もう一段の2:1ギアリング用。                                                                                                                                                    | 0 |

| ff_txfullclk                 | 0             | チャネル     | Tx PLLフルレートクロック                                                                                                                                                                          | D |

| ff_txhalfclk                 | 0             | チャネル     | Tx PLLハーフレートクロック                                                                                                                                                                         | D |

| ff_txqtrclk                  | 0             | チャネル     | Tx PLLクオータ (1/4) レートクロック                                                                                                                                                                 | 0 |

| FPGAからのクロック信号                | <del></del> 号 |          |                                                                                                                                                                                          |   |

| core_rxrefclk                | - 1           | クワッド     | FPGAからのRx基準クロック。CDR PLL用。                                                                                                                                                                | D |

| core_txrefclk                | ı             | クワッド     | FPGAロジックからのTx基準クロック。Tx<br>SERDES PLL用。                                                                                                                                                   | D |

| ff_ebrd_clk_[3:0]            | ı             | チャネル     | FPGAからのRxチャネルクロック入力。CTC<br>FIFO (エラスティックバッファ) リード用。                                                                                                                                      | D |

| ff_rxiclk_ch[3:0]            | ı             | チャネル     | FPGAからの各Rxチャネル用クロック入力。基準クロックや受信基準クロックに同期する FIFOとRx FPGA部のインターフェイス用クロック。                                                                                                                  | D |

| ff_txiclk_ch[3:0]            | ı             | チャネル     | FPGAからの各Txチャネル用クロック入力。基準クロックに同期したFIFOとインターフェイスするため。CTCが用いられる場合は、Rx FPGA部が基準クロックに同期したFIFOにインターフェイスするために用いられる。                                                                             | D |

| SERDESクライアント・                | インター          | フェイス(SCI | ·                                                                                                                                                                                        |   |

| scienaux                     | I             | R        | 1: sciwdataがクワッド制御レジスタにライト<br>0: メモリデータがクワッド制御レジスタにラ<br>イト                                                                                                                               | 0 |

| scien_ch[3:0]                | ı             | R        | 1: sciwdataがチャネル制御レジスタにライト<br>0: メモリデータがチャネル制御レジスタにラ<br>イト                                                                                                                               | 0 |

| sciselaux                    | I             | R        | 1: クワッドレジスタを選択                                                                                                                                                                           | 0 |

| scisel_ch[3:0]               | I             | R        | 1: チャネルレジスタを選択                                                                                                                                                                           | 0 |

| sciaddress[5:0]              | I             | R        | アドレスバス入力                                                                                                                                                                                 | 0 |

| scireaddata[7:0]             | 0             | R        | リードデータ出力                                                                                                                                                                                 | 0 |

| sciwritedata[7:0]            | i             | R        | ライトデータ入力                                                                                                                                                                                 |   |

LatticeECP2M 8-11 SERDES/PCS-UGJ

| scird                       | I | R | 1: リードデータを選択<br>0: リードデータは非選択                        | 0 |

|-----------------------------|---|---|------------------------------------------------------|---|

| sciwstn                     | I | R | ライトストローブ                                             | 0 |

| sciinterrupt                | 0 | R | 割り込み出力                                               | 0 |

| cyawstn                     | I | R | 1: "sciwstn = 0" の場合、全メモリセルをレジス<br>タにコピー<br>0: デフォルト | 0 |

| SERDESキャラクタライゼーション / テスト用バス |   |   |                                                      |   |

| cin[11:0]                   | I | R | キャラクタライズ用テストバスロジックのデータ入力                             | D |

| cout[19:0]                  | 0 | R | キャラクタライズ用テストバスロジックのデー<br>タ出力                         | D |

- 1. コンフィグレーションの間、HDOUTPとHDOUTNは共にVCCOBにプルアップされます。

- 2. Generic 8b10b PCSモジュールはオプションとして4本のPCI制御/ステータス信号を含んでいます。用いられない場合、制御信号はGNDに接続し、またステータス信号はフローティングのままでも構いません。

- 3. CDRを用いないで信号を得る唯一の方法はOOB OUT信号を用いることです。この信号はSDIモード用のみ。

- 4. 外部リンクステートマシンが選択されると、PCSポートリストにこれらの信号が表れます。図8-28を参照してください。

- 5. ラティスセミコンダクター社内での用途のみ。

- 6. これら信号はパルスです。正しくモニタするためにはラッチする必要があります。

# SERDES/PCSの機能記述

LatticeECP2Mファミリのデバイスには、組み込みSERDES/PCSロジックのクワッドが1~4あります。各クワッドは、独立する全二重データチャンネルを4系統サポートします。単一チャネルはデータリンクを1系統サポートすることができ、各クワッドはそのような4つのチャネルまでサポートすることができます。モード選択はクワッド単位でされることに注意してください。例えば或るクワッドをギガビット・イーサネットモードに選択すると、そのクワッドにおける全4チャネルがギガビット・イーサネットモード専用になります。

組み込みSERDES CDR PLLとTx PLLは広範囲の業界標準プロトコルをカバーするデータレートをサポートします。

図8-3はSERDES/PCSチャネル内の主なブロックとサブブロックを説明します。

- SERDES

- イコライザ

- CDR(クロックデータ・リカバリ)

- デシリアライザ

- プリエンファシス

- シリアライザ

- シリアル・ループバック

- ・SERDESブリッジ(SB)

- インバータ;受信データを反転します。PCI Expressで必要です。

- SERDESブリッジ・パラレル・ループバック

- PCSコア

- ワードアライメント

LatticeECP2M 8-12 SERDES/PCS-UGJ

- 8b10bデコーダ

- 8b10bエンコーダ

- リンクステートマシン

- エラスティック・バッファ(CTC)

- ・FPGAブリッジ(FB)

- ダウンサンプルFIFO

- アップサンプルFIFO

- PCSパラレル・ループバック

#### **SERDES**

### イコライザ

デジタル伝送のデータレートがGbps以上に進化するにつれて、周波数依存の減衰によって受信信号に厳しいシンボル間干渉をもたらす結果となり得ます。従ってイコライザを用いることは、正しくデータを復元するために必須になります。LatticeECP2Mでは3つの極配置オプションを用意しており、これらは低/中/高周波領域です。

### プリエンファシス

プリエンファシスはシステムプロセスに関するものです。ユーザは最大80%のプリエンファシスを選択することができます。

# レシーバのCID(同一ディジットの連続)

Rx-CID; BER 10<sup>-12</sup> でのレシーバのCID(0/1同一ディジットの連続)

- ・3.125Gbpsで7ビット

- ・1.25Gbpsで20ビット

これはDC結合を用いるとき、入力データストリームが0/1の遷移なしで許容されるビット数です。

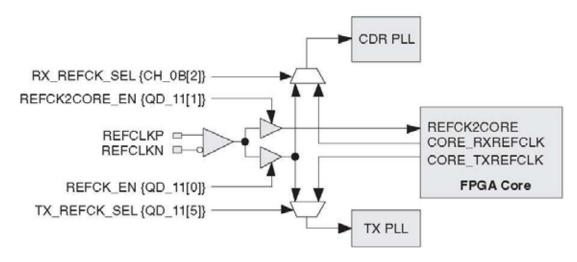

#### 基準クロックの使用

1本の基準クロック(REFCLK)がLatticeECP2Mファミリではサポートされます。Tx PLLと4個のRx PLLはすべて同じ周波数で、基準クロック周波数の倍数で動作します。各チャネルのTxシリアライザは、そのままのレート(フルデータレート・モード)か半分のレート(ハーフデータレート・モード)で動作するかを、独立してプログラムすることができます。同様に、各チャネルのRxデシリアライザもフルデータレート・モード、ハーフデータレート・モードのいづれで動作するかを独立してプログラムすることができます。すべてのTxとRxが同じモードでプログラムされると(通常はフルレート)、クワッドの全4チャネルが同一Tx/Rx周波数で動作することになります。

SERDES内の送信PLLは、ピンからの外部基準クロックか、FPGAコア(core\_txrefclk)から提供される基準クロックかのどちらかに、ロックすることができます。SERDES内の受信PLLも、ピンからの外部基準クロックかFPGAコア(core\_rxrefclk)から供給される基準クロックのどちらかにロックすることができます。

LatticeECP2M 8-13 SERDES/PCS-UGJ

### 図8-5 ブロック図、基準クロックの使用

#### 基準クロックのソース

#### refclkp, refclkn

CMLのSERDESクロック専用入力。送受信用に特に別のソースが用意されていない限り、最初のオプションです。ソースはCML、LVDS、LVPECLのいづれかです。インターフェイス例についてはTN1114 (Electrical Recommendations for Lattice SERDES )を参照してください。

#### core\_rxrefclk, core\_txrefclk

FPGAロジックからの基準入力。プライマリクロック(PCLK)を使用するべきです。

#### **FPGA PLL**

FPGA PLLが基準クロックとして用いられるとき、そのPLLに対する基準クロックは専用クロック入力ポートを用いるべきです。高速データレート用のクロックではFPGA PLL出力のジッタはシステム規格を満たさないかもしれません。ジッタが重要な用途では用いないことを推奨します。

### フルデータレートとハーフデータレート

各TxシリアライザとRxデシリアライザは、フルデータレートとハーフデータレートに分けることができ、各方向と各チャネルにおいて2つの異なるデータレートを許容します。

このデュアルレート機能を用いるには、チャネルベースのプロトコルモードを選択しなければなりません。 例:

1. IPexpress(図8-22)のQuad Tabウィンドウでは、G8B10B Mode、Channel Based Protocol Mode、Channel0(Full Rate)が選択されています。

LatticeECP2M 8-14 SERDES/PCS-UGJ

- 2. Reference Clock(CM)ウィンドウ(図8-24)で、Full Rate Channelコラムの下に、以下を入力します。

- ・シリアル・ビットクロックレート: 2.5 GHz

- ・基準クロックの乗数: 10X

- ・残り3つのエントリーはそのまま

- 3. Half Rate Channelコラムはハーフレートのために計算された値を表示します:

フルレートチャネル ハーフレートチャネル

シリアル・ビットクロックレート2.5GHz1.25GHz基準クロック乗数10X5X計算された基準クロックレート250MHz250MHzFPGAインターフェイス・データバス幅88計算後のFPGA I/Fクロックレート250MHz250MHz

#### フルクロック、ハーフクロック、およびクオータクロックの使用

多くの場合、図8-32で図示されるff\_txfullclkはff\_rxiclk\_chx、ff\_txiclk\_chx、ff\_ebrd\_clk\_xに用いられます。

Reference Clock MultiplierとFPGA Interface Data Bus Widthが選択されているとき、IPexpress GUIは自動的にFPGAインターフェイスのクロック周波数を計算します。

表8-6はrefclk\_multiplierモードと、8ビットまたは16ビットのインターフェイス・データバス幅の取り得るすべての組み合わせに対するクロック使用例について示します。

表8-6 クロック使用例、G8B10Bモード、REFCLK=120MHz

| 基準クロック乗数        | 10xH               | 10x      | 20xH     | 20x      |

|-----------------|--------------------|----------|----------|----------|

| ピットレート          | 600 Mbps           | 1.2 Gbps | 1.2 Gbps | 2.4 Gbps |

| 8ビット・インターフェイス例  |                    |          |          |          |

| rxfullclk 1     | 60                 | 120      | 120      | 240      |

| rxhalfclk       | 30                 | 60       | 60       | 120      |

| txfullclk       | 120                | 120      | 240      | 240      |

| txhalfclk       | 60                 | 60       | 120      | 120      |

| txqtrclk        | 30                 | 30       | 60       | 60       |

| 16ビット・インターフェイス例 |                    |          |          |          |

| rxfullclk       | 60                 | 120      | 120      | 240      |

| rxhalfclk 1     | 30                 | 60       | 60       | 120      |

| txfullclk       | 120                | 120      | 240      | 240      |

| txhalfclk       | 60                 | 60       | 120      | 120      |

| txqtrclk        | 30 <sup>2, 3</sup> | 30       | 60       | 60       |

- 1. CTC BYPASSモードでは、これら再生クロックはrxiclkのソースとして用いられます。図8-34/-36参照。

- 2. 陰影をつけられたセル中のクロックは、FPGAインターフェイス・クロックとして各モードで使用されます。

- 3. このモードが選択されるとき、コンフィグレーションGUIのOptional PortタブウィンドウでPLL Quarter Clockをチェックしなければなりません(図8-28を参照してください)。

フルデータレート・チャネルのVCOはビットクロックと同じです。ハーフデータレート・チャネルではビットクロックはVCOの半分です。

LatticeECP2M 8-15 SERDES/PCS-UGJ

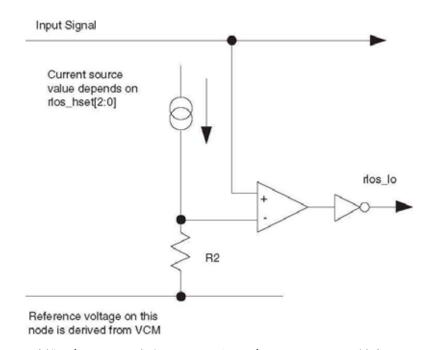

### LOS(信号の喪失)

各チャネルは図8-6で示されるようにプログラマブルなLOS(信号の喪失)検出器を含んでいます。LOS閾値は プログラマブル電流源の値に依存し、rlos\_hset[2:0]制御ビットを用いて選ばれます。

# LOL(ロックはずれ)

送信PLLと個別チャネルのCDRには、いづれもカウンタベースのデジタルLOL検出器があります。送信PLLのロックがはずれるとLOLがアサートされ、PLLが再ロックするまでそのままです。

CDRのロックがはずれると、そのチャネルのLOLがアサートされ、CDRのVCOを基準クロックにロックしようと試みます。これが達成されるとそのチャネルのLOLはネゲートされ、CDRは入力データにロックするために元に戻ります。CDRはデータにロックし続けるか、または再びロックはずれに戻り再トレーニングへと、その繰り返しとなります。

#### **図8-6 LOS検出器**

注:rlos\_lsel[2:0]制御ビットと関連するステータスビットはラティス社内のみでの用途です。

### Txレーン間スキュー

制御ビットsync\_toggleは、アクティブな全Txチャネルがbit0からパラシリ変換を始めるためのリセット用に加えられました。ほとんどのマルチチャンネル・プロトコル規格では、ある規定値の中にTxレーン間スキューが収まることを保証する要件があります。マルチチャンネル・アライメント(MCA)はLatticeECP2MのハードPCSではサポートされません。

Txシリアライザへのリセットはsync\_toggle制御ビットをトグルするか、PLL LOLの遷移によって生成されます。リセットはすべてのアクティブなTxシリアライザに適用されます。これらのソース信号が共にレベルである場合、Txシリアライザは通常動作しています。

LatticeECP2M 8-16 SERDES/PCS-UGJ

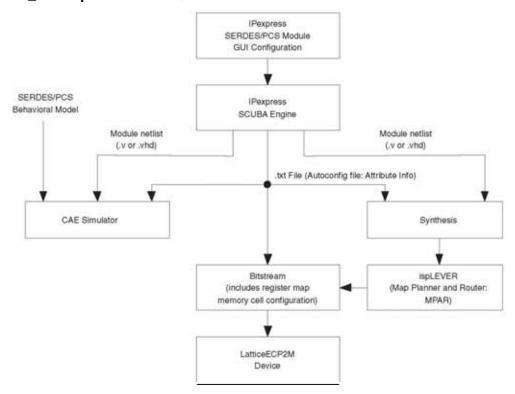

### PCS機能のセットアップ

LatticeECP2M PCSは様々なアプリケーションでの用途に構成することができます。セットアップは ispLEVER IPexpressモジュール生成ツールで選ばれ、ユーザはPCSのモードと機能オプションを選択できます。選択オプションは自動構成(auto-configuration)ファイルの中に保存され、これはispLEVERビットストリーム・ジェネレータによって用いられてビットストリーム内に書き出されます。PCS選択オプションを変えるためには、ユーザはIPexpressを再実行してPCSモジュールを作り直し、新しい自動構成ファイルを作成することを推奨します。ビットストリーム・ジェネレータを実行する前に、マニュアルで自動構成ファイルを編集することによって幾つかのオプションを変えることもできます。

コンフィグレーション後に、オプションのSERDESクライアント・インターフェイス(SCI)バスを通してPCSレジスタに書くことによって、動的にPCSオプションを変えることができます。SCIはソフトIPで、SERDES/PCSクワッドがコンフィグレーション・メモリセルの設定と異なるレジスタ値によって制御されることを可能にします。SCIを介してアクセスできる制御/ステータス・レジスタの一覧表を、このドキュメントのメモリマップ章に示してあります。

### 自動構成(auto-configuration)ファイル

ispLEVERの自動構成機能を用いることで、それぞれのPCSモードのための初期レジスタ設定を行うことが可能です。モジュール・ジェネレータは、選ばれたモード用にクワッド/チャネルレジスタ設定の自動構成ファイル (<module名>.txt) を生成します。このファイルはフロントエンド・シミュレーションで参照することができ、またビットストリームに統合されます。すべてのクワッド/チャネルレジスタが、コンフィグレーションの際に自動構成ファイルで定義された値に設定されます。したがって全レジスタが自動構成ファイルで設定されるのみで良ければ、SCIは不要です。他方、ユーザがデバイス動作中に制御レジスタの値を変えるか、またはステータス・レジスタをモニタする必要がある場合は、デザイン内にSCIを含まなければなりません。

#### 送信データ

PCSクワッド送信データパスはチャネル単位での8b10bエンコーダとシリアライザから成ります。

#### 8b10bエンコーダ

このモジュールはIEEE 802.3ae-2002 1000BASE-X仕様の中で記述されている8b10bエンコーダを実装しています。エンコーダは仕様で説明されるように8ビットから10ビットコードへの変換を実行し、同時に規定されているディスパリティ規則を維持します。CHx\_8B10B(xはチャネル番号)の属性をBYPASSに設定することによって、8b10bエンコーダをバイパスすることができます。

#### シリアライザ

8b10b符号化されたデータはパラシリ変換され、組み込みSERDESを介してチップ外部に送信されます。

#### 受信データ

PCSクワッド受信データパスはチャネルごとに次のサブブロックからなります;デシリアライザ、ワードアライナ、8b10bデコーダ、オプションのリンクステートマシン(LSM)、およびオプションの受信クロックトレランス補償(CTC)FIFO。

#### デシリアライザ

データは組み込みSERDESを介してオンチップに取り込まれ、シリアルからパラレルになります。

#### ワードアライメント(バイト境界の検出)

このモジュールはコンマ符号語の検出とアライメント動作を実行します。受信ロジックで入力されるデータストリームに10ビットのワードアライメントを実行するために、コンマキャラクタが用いられています。

LatticeECP2M 8-17 SERDES/PCS-UGJ

CHx\_COMMA\_ALIGN(xはチャネル番号)のアトリビュートをBYPASSに設定することによって、ワードアライナをバイパスすることができます。コンマ記述は802.3.2002 1000BASE-X仕様のセクション36.2.4.9と、セクション48.2.6.3(10GBASE-X仕様の図48-7)にあります。

ワードアライメント・モジュール内で多くのプログラマブル・オプションがサポートされます:

・ソフトウェア・イネーブル制御(User Configured; UCモード)

注: UC Modeは8-bit SERDES Only、10-bit SERDES Only、SD-SDI、HD-SDIを意図します。

・2つのプログラマブル・ワードアライメント・キャラクタ(通常正と負のディスパリティのためにそれぞれ1つ)を設定できる機能と、アライメント・コンペア(比較)のためのビット単位でプログラマブルなマスクレジスタ。アライメント・キャラクタとマスクレジスタはクワッド毎に設定されます。

多くのプロトコルにおいて、"XXX0000011" (正のランニング・ディスパリティ・コンマキャラクタでコードグループK28.1、K28.5、およびK28.7に適合するjhgfiedcbaビット)と "XXX1111100" (負のランニング・ディスパリティ・コンマキャラクタでコードグループK28.1、K28.5、およびK28.7に適合するjhgfiedcbaビット) にワードアライメント・キャラクタを設定することができます。しかしながら、ユーザは最大10ビット長のどのようなビットパターンも定義することができます。

- ・最初のアライメント・キャラクタは属性COMMA\_Aに割り当てられた10ビットの値によって定義されます。 この値はPCSクワッドの全チャンネルに適用されます。

- ・第二のアライメント・キャラクタは属性COMMA\_Bに割り当てられた10ビットの値によって定義されます。 この値はPCSクワッドの全チャンネルに適用されます。

- ・マスクレジスタは、どのワードアライメント・ビットを比較したらよいかを定義します(マスクレジスタで1のビットは、ワードアライメント・キャラクタレジスタで対応するビットをチェックすることを意味します)。属性COMMA\_Mに割り当てられた10ビットの値によって定義されたマスクレジスタ。この値はPCSクワッドの全チャンネルに適用されます。

属性CHx\_COMMA\_ALIGNがAUTOに設定されると、プロトコルベースのリンクステートマシンの1つがワードアライメントを制御します。詳しい動作に関する情報は、後述のプロトコル特有のリンクステートマシン記述を参照してください。

### 8b10bデコーダ

8b10bデコーダは、IEEE802.3-2002規格で記述されるようにデコーダ動作を実装しています。デコーダはランニング・ディスパリティの検証と共に10ビットから8ビットコードへの変換を実行します。CHx\_8B10B(x はチャネル番号)の属性をBYPASSに設定することによって、8b10bデコーダをバイパスすることができます。

コードバイオレーションが検出されると、ff\_rxdata受信データは0xEEに、ff\_rx\_k\_cntrl\_chは1に設定されます。

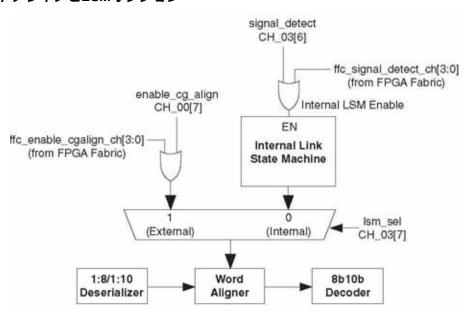

# プロトコル特有のリンクステートマシン(LSM)

PCSは様々なクワッドモードで用いられる種々プロトコルのためにLSMを実装しています。

プロトコル特有のLSMが選択されるとき、CH(0-3)\_COMMA\_ALIGNをAUTOに設定することによって、そのチャネルのLSMをイネーブルしなければなりません。各モードでイネーブルされる特有LSMの選択は、以下に記述され、また図8-7にまとめられています。

PROTOCOL属性がGIGEであるとき、ギガビット・イーサネット用のLSMが選択されます。リンク同期は、アラインされたコードワード(符号語)が必要数連続して検出された後に達成されます。ギガビット・イーサ

LatticeECP2M 8-18 SERDES/PCS-UGJ

ネットリンク同期ステートマシンは802.3-2002 1000BASE-X仕様の図36-9で示される同期ステート図を実装します。

G8B10Bと10-bit SERDES Onlyプロトコルでは、COMMA\_ALIGNがAUTOに設定されるとき、ギガビット・イーサネット・リンクステートマシンが使用されます。

#### 外部リンクステートマシンのオプション

属性CHx\_COMMA\_ALIGNがDYNAMICに設定されるとき、プロトコル特有のLSMはバイパスされます。その場合、ffc\_enable\_cgalign\_ch(0-3)が少なくとも1クロック周期Lowにされた後、ワードアライナは比較が成功した最初か第二のユーザ定義ワードアライメント・キャラクタのどちらかで、アライメントはロックします。(入って来るデータをユーザ定義のワードアライメント・キャラクタに比較するのをやめて、現在のアライメントを維持します。)その後にFPGAインターフェイスのffc\_enable\_cgalign\_ch(0-3)ポートに与えられるLowパルスは、ワードアライナをアンロックします。そして、ワードアライナはユーザ定義のワードアライメント・キャラクタの1つに次に一致した時に再ロックされます。望まれるなら、一定の条件下でのワードアライメントの変化を許容するために、PCSクワッドの外部に実装されたLSMによりffc\_enable\_cgalign\_ch(0-3)を制御することができます。

図8-7はLSMオプションについて図示します。

### 図8-7 PCSワードアライナとLSMオプション

表8-7 リンクステートマシン (LSM) とワードアライナ(WA)の選択

| COMMA<br>ALIGNモード | 記述                                                                                   |

|-------------------|--------------------------------------------------------------------------------------|

| AUTO              | WAがイネーブル、LSMがイネーブル(GbE LSM: デフォルト)                                                   |

| DYNAMIC           | WAがイネーブル、LSMはディセーブル。cg_alignとsig_detect信号は0に設定される。<br>潜在的に外部LSMが両信号を制御できる            |

| BYPASS            | WAはバイパス、LSMはディセーブル。ユーザは、FPGAコアにワードアライナを設計し、ロジック内に自らのcg_alignとsig_detect信号を与えることもできる。 |

LSMが選択/イネーブルされたとき、リンク同期に成功すると、その特定チャネルに関するステータス信号ffs\_ls\_sync\_status(0-3)はHighになります。

LatticeECP2M 8-19 SERDES/PCS-UGJ

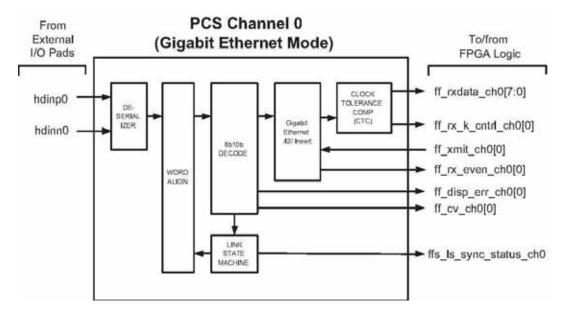

# ギガビット・イーサネットモードのアイドル挿入

Generic 8b10bモードには、さらにワードアライメントのためにLSMを選択するオプションがあります。ギガビット・イーサネットモードに設定されたPCSは、自動ネゴシエーションのために、受信データストリームの中に /l2/ シンボル挿入を行います。ギガビット・イーサネットの自動ネゴシエーションはソフトロジックで実行されます。この機能は2048クロックサイクル毎に8つの /l2/ オーダーセット・シーケンスを挿入します。/l2/ 挿入は自動ネゴシエーション・ソフトロジックからドライブされるPCSへのff\_xmit\_ch(0-3)入力で制御されます。また、PCSから自動ネゴシエーション・ソフトロジックまでの信号ff\_rx\_even\_ch(0-3)[0]を提供します。図8-8はPCSがギガビット・イーサネットモードに設定されたときの、1チャネルの受信ロジックを示し(この例ではチャネルの)、これらの制御/ステータス信号を示しています。

図8-8 ギガビット・イーサネットモードのPCS受信パス(チャネル0の例)

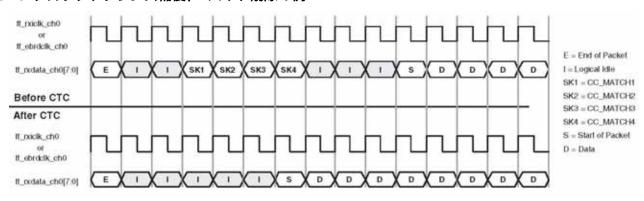

# クロックトレランス補償(CTC)

CTCは、受信再生クロックとロックする基準クロックの間のクロックレートの調整を実行します。クロック 補償は、パケットデータの損失を引き起こすことなく、事前に定められた位置でバイトを挿入するか、また は削除することによって実行されます。16バイトのエラスティックFIFOは、2つのクロックドメイン間のデ ータ転送に用いられ、LatticeECP2M SERDESのためにクロック偏差の規定ppm上限まで対応します。 (LatticeECP2/Mファミリデータシートの "DCおよびスイッチング特性" セクションを参照して下さい。)

属性CHx\_CTC\_BYPがNORMALに設定されると、そのチャネルのCTCブロックはイネーブルされ、BYPASSに設定されるとバイパスされます。

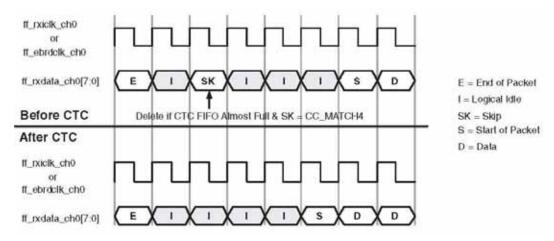

1バイト削除について図8-9で示します。

LatticeECP2M 8-20 SERDES/PCS-UGJ

図8-9 クロックトレランス補償、1パイト削除の例

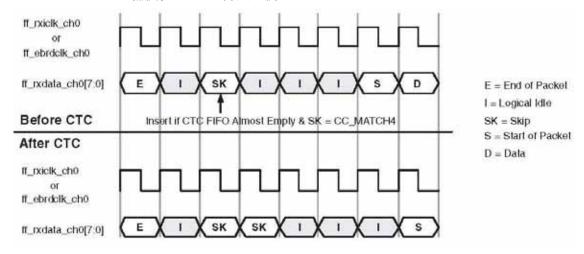

1バイト挿入について図8-10で示します。

図8-10 クロックトレランス補償、1バイト挿入の例

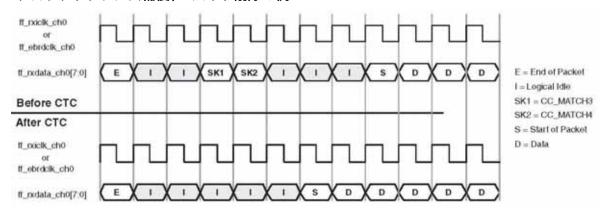

2バイト削除について図8-11で示します。

図8-11 クロックトレランス補償、2パイト削除の例

LatticeECP2M 8-21 SERDES/PCS-UGJ

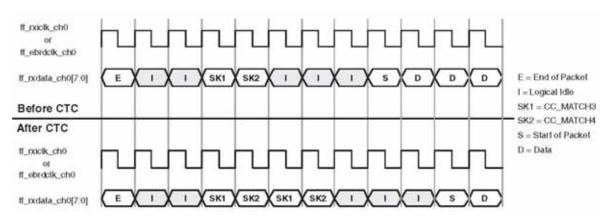

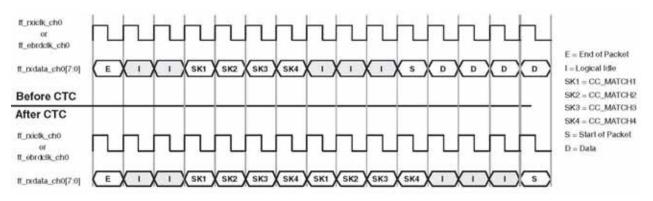

2バイト挿入について図8-12で示します。

### 図8-12 クロックトレランス補償、2バイト挿入の例

4バイト削除について図8-13で示します。

図8-13 クロックトレランス補償、4バイト削除の例

4バイト挿入について図8-14で示します。

図8-14 クロックトレランス補償、4バイト挿入の例

クロック補償値はクワッドベースで設定されます。CHx\_CTC\_BYP(xはチャネル番号)の属性をBYPASSに設定することによって、CTCをバイパスすることができます。CHx\_CTC\_BYPをNORMALに設定することは、CTCがアクティブであることを意味します。ispLEVERモジュール・ジェネレータでは、チャネルをSingleと定義するとCTCをイネーブルする自動構成ファイルが作成されます。チャネルをMCA Group1かMCA Group 2と定義すると、CTCをバイパスする自動構成ファイルが作成されます。CTCが使用されるとき、意

LatticeECP2M 8-22 SERDES/PCS-UGJ

図されたアプリケーションのクロック補償のために、以下の設定を適切に設定しなければなりません。

- ・CC\_MATCHMODE属性を用いて、挿入/削除パターン長を設定します。これは挿入や削除を実行する前に CTCが比較しスキップするバイト数を設定します。CC\_MATCHMODEの値は、MATCH\_4 (1バイトの挿入/削除)と、MATCH\_3\_4 (2バイトの挿入/削除)、及びMATCH\_1\_2\_3\_4 (4バイトの挿入/削除)です。また、ターゲット・アプリケーションに適切な最小パケット間ギャップを設定しなければなりません。パケット間ギャップは属性CC\_MIN\_IPGに値を割り当てることによって設定されます。CC\_MIN\_IPGの許容値は0、1、2、および3です。これらの属性設定に基づいてスキップキャラクタ削除が実行された後の、許容される最小パケット間ギャップは以下の表8-8で説明されています。

- ・選ばれたCC\_MATCHMODEに対応するように、スキップバイトかオーダーセットが設定されなければなりません。4バイトの挿入/削除(CC\_MATCHMODE = MATCH\_1\_2\_3\_4)に関しては、属性MATCH\_1を最初のバイトに割り当て、属性MATCH\_2に第二バイト、属性MATCH\_3を第三バイト、そして属性MATCH\_4に第四バイトをそれぞれ割り当てなければなりません。割り当てられる値は2進の10ビット値です。例えば、4バイトのスキップ・オーダーセットが /K28.5/D21.4/D21.5/D21.5 である場合、MATCH\_1は "0110111100"、 MATCH\_2 = "0010010101"、そしてMATCH\_3 = MATCH\_4 = "0010110101" であるべきです。2バイトの挿入/削除 (CC\_MATCHMODE = MATCH\_3\_4) に関しては、属性MATCH\_3が最初のバイトに割り当て、属性MATCH\_4に第二バイトをそれぞれ割り当てなければなりません。1バイトの挿入/削除 (CC\_MATCHMODE = MATCH\_4が最初のバイトに割り当てられなければなりません。

- ・クロック補償FIFOにおいて、ターゲット・プロトコル用のHigh/Lowウォーターマーク(水位標)を設定しなければなりません。値は0~15の範囲を取り得、HighウォーターマークをLowウォーターマークより高い値に設定しなければなりません(等しい値に設定するべきではありません)。属性CCHMARKに値を割り当てることによって、Highウォーターマークが設定されます。CCHMARKの許容値は16進値の0からFです。属性CCLMARKに値を割り当てることによって、Lowウォーターマークが設定されますCCLMARKの許容値も16進値の0からFです。

- ・ispLEVERモジュール・ジェネレータでPCSブロックを生成するとき、Error Status Portsが選択されている場合、チャネルごとのクロック補償FIFOオーバーランは、PCS/FPGAインターフェイスでffs\_cc\_overrun\_ch(0-3)という名称のポートでモニタすることができます。

- ・ispLEVERモジュール・ジェネレータでPCSブロックを生成するときError Status Portsが選択されている場合、チャネルごとのクロック補償FIFOアンダーランは、PCS/FPGAインターフェイスでffs\_cc\_underrun\_ch(0-3)という名称のポートでモニタすることができます。

### 最小パケット間ギャップの計算

表8-8はパケット間ギャップ(CC\_MIN\_IPG属性で定義される)のユーザ定義の値と、PCSからのスキップ・キャラクタ削除後の保証されるパケット間最小バイト数との関係を示します。表は乗数としてパケット間ギャップを示します。パケット間の最小バイト数と、挿入/削除を表中で示された乗数倍されたバイト数は等しいです。例えば挿入/削除あたりのバイト数が4(CC\_MATCHMODEはMATCH\_1\_2\_3\_4に設定される)で、かつ最小パケット間ギャップの属性C\_MIN\_IPGが2の時、最小のパケット間ギャップは4(CC\_MATCHMODE = MATCH\_1\_2\_3\_4)掛ける3(表8-8のCC\_MIN\_IPG = 2)、即ち12バイトに等しくなります。最小のパケット間バイト数がCTCを通り抜けるまで、PCSはスキップキャラクタの削除を実行しません。

LatticeECP2M 8-23 SERDES/PCS-UGJ

表8-8 最小パケット間ギャップの乗数

| CC_MIN_IPG | 挿入/削除の乗数 |

|------------|----------|

| 0          | 1 X      |

| 1          | 2 X      |

| 2          | 3 X      |

| 3          | 4 X      |

#### クロックドメイン

図8-15は、PCS内でCTCブロックを利用するモードでの、単一チャネルの送受信両方向のクロックドメインを示します。

送信側では、FPGAインターフェイスにおけるff\_txiclk\_ch入力からロックした基準クロックまでのクロックドメイン転送は、FPGA送信インターフェイスFIFOで起こります。FPGA送信インターフェイスFIFOは、同じ周波数である2クロック間の位相差を吸収する意図があります。これらのFIFO(1チャネルあたり1つ)は周波数偏差を補うことはできません。

受信側のクロックドメイン転送は、チャネル再生クロックから基準クロック間のCTCブロックで起こります。CTCは、LatticeECP2Mの最大許容値まで、再生受信クロックと基準クロックの周波数差を調節することができます。CTCの後、FPGA受信インターフェイスFIFOで、ロックされた基準クロックとff\_rxiclk\_chの間でクロック・インターフェイスがあります。FPGA受信インターフェイスFIFOは、同一周波数の2クロック間の位相差の調整をすることが目的です。FPGA受信インターフェイスFIFO(1チャネルあたり1つ)は、周波数偏差を補うことはできません。

図8-15 CTCモードのPCSクロックドメイン転送

LatticeECP2M 8-24 SERDES/PCS-UGJ

### 図8-16 CTCを用いるPCSクワッドへの同期入力クロック

同期インターフェイスを保証するためには、送信クロック入力と受信クロック入力の両方が、Generic 8b10bモードに設定されたPCSクワッドの基準クロック出力の1つからドライブされるべきです。図8-16は同期インターフェイスとなるような、取り得る接続について図示します。

図8-17は、PCS内でCTCブロックを利用しないモードでの、単一チャネルの送受信両方向のクロックドメインを示します。送信側では、FPGAインターフェイスにおけるff\_txiclk\_ch入力からロックした基準クロックまでのクロックドメイン転送は、FPGA送信インターフェイスFIFOで起こります。FPGA送信インターフェイスFIFOは、同一周波数の2クロック間の位相差を調整することが目的です。これらのFIFO(1チャネルあたり1つ)は周波数偏差を補うことはできません。受信側のクロックドメイン転送は、FPGA受信インターフェイスFIFOで受信再生クロックとff\_rxiclk\_chの間で起こります。FPGA受信インターフェイスFIFOは、同一周波数の2クロック間の位相差を調整することが目的です。FPGA受信インターフェイスFIFO(1チャネルあたり1つ)は周波数偏差を補うことはできません。

LatticeECP2M 8-25 SERDES/PCS-UGJ

### 図8-17 非CTCモードでのPCSクロックドメイン転送

同期インターフェイスを保証するためには、送信クロック入力と受信クロック入力の両方が、Generic 8b10bモードに設定されたPCSクワッドの基準クロック出力の1つからドライブされるべきです。図8-18は同期インターフェイスとなる、取り得る接続について図示します。

LatticeECP2M 8-26 SERDES/PCS-UGJ

#### 図8-18 CTCを用いないPCSクワッドへの同期入力クロック

# スペクトル拡散クロック(SSC)のサポート

LatticeECP2M SERDES/PCSにはスペクトル拡散ジェネレータがありませんが、スペクトル拡散データを受信することができます。

LatticeECP2MでのSSCサポートは同様の機能を必要とするすべてのプロトコルに適用されますが、リンク両端のポートは互いに600ppm以内に収まるレートでデータを伝送しなければなりません。これはビットレート用クロックソースに+/-300ppmの偏差を許容する仕様です。変調レート30KHzからの33KHzの範囲で、データレートは定格の+0%から-0.5%まで変調ことができます。+/-300ppmの許容限界に加えて、データがSSCで変調されるとき、両ポートは同じビットレート・クロックを必要とします。

(PCI Expressでは)ルート・コンプレックスは基準クロックを拡散する責任があります。そしてエンドポイントは、TXを通してスペクトルを戻すために、それと同じクロックを用います。したがって別のRXREFCLKは必要ありません。

この支配的なアプリケーションはアドインカードです。これは、PCI ExpressコネクタのようにコネクタからのREFCLKを用いる必要はありませんが、同じSSCで受信し、送信しなければなりません。

# シリアル・デジタルビデオとOOB (帯域外) 低速SERDES動作

レシーバCDRと付随するSERDES/PCSロジックをバイパスすることによって、低速度(250Mbps未満、Out-Of-Band=OOB信号)の入力にSERDES受信バッファを用いることができます。この機能はシリアル・デジタルビデオ用途など、高速データと低速データの両方からDCまでの伝送に、同一の端子で対応する必要があるアプリケーションに有用です。

LatticeECP2M SERDES/PCS は標準精細度シリアル・デジタルインターフェイスSD-SDI(143Mbps、177Mbps、270Mbps、360Mbps)、および高精細度シリアル・デジタルインターフェイスHD-SDI(1.485Gbps

LatticeECP2M 8-27 SERDES/PCS-UGJ

と1.4835Gbps)をサポートします。これらは送受信ピンを共用することが必要です。考えられる実装方法の1つが図8-19で示されます。PCS/FPGAインターフェイスにおけるOOB信号ポートは、250Mbpsより低速の信号を入力するのに用いられます。

SD-SDIモードが選択されると、このポートが利用できます。OOB\_OUT信号は、SERDES入力バッファから FPGAインターフェイスまで直接通され、また基準クロックにはロックしません(図8-3を参照してください)。

低速信号でSERDES入力バッファをドライブするとき、SERDES入力バッファはDCモードに設定されるべきです。これはIPexpress PCSコンフィグレーションGUIのRx I/O Couplingドロップダウン・ボックスにおいてDCを選択することによって、チャネル単位で行われます(図8-25を参照して下さい)。

以上はシリアル・デジタルビデオに関する議論ですが、FPGAロジックでRx CDR(クロックデータ・リカバリ)を行い、Tx方向にデシメーションを必要とするような、低ビットレート・アプリケーションではいづれも同様な使い方をすることが意図されていることに留意して下さい。

入力BSCAN回路は、高速SERDESと並列に見え、入力データをデバイスの(クワッドでない)ほかの場所に位置する低速度デシリアライザに接続するために用いることができます。BSCANステートマシンに関与せずに入力BSCAN回路(1チャネルあたり1つ)をオンするためのイネーブル信号が必要です。

Quad Top ✓ FPGA Core

✓ SERDES/PCS Block OOB EN RSRMODE from JTAG config logic BSCAN input cell OOB OUTn low rate data output RX power up HDINP0 EQ Input Data HDINNO I TX power up SERDES Output Data HDOUTP0 HDOUTN0 ■◀ BSCAN output cell

図8-19 考えられるシリアル・デジタルビデオのサポート実装例

LatticeECP2M 8-28 SERDES/PCS-UGJ

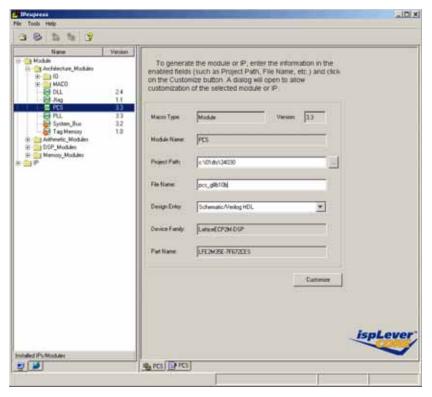

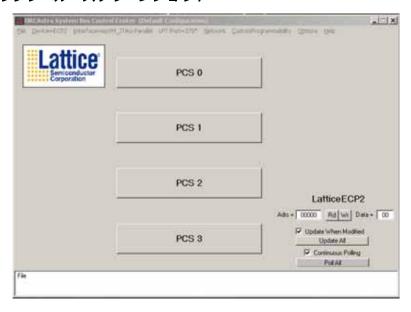

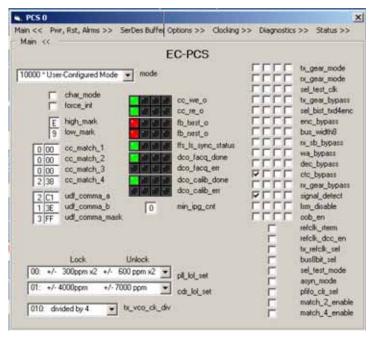

# コンフィグレーションGUI

IPexpress™は、SERDESとPCSブロックを生成し、構成するために用いられます。設計者は、特定のクワッドやチャネルのSERDESプロトコル規格を選択する際に、GUIを用います。IPexpressはこのGUIから入力を得て、自動構成ファイル(.txtファイル)とHDLネットリストを生成します。HDLモデルはシミュレーションと合成フローで用いられます。自動構成ファイルは属性レベルの配置情報を含んでいて、シミュレーションとispLEVER bitgen(ビットファイル生成)プログラムの入力となります。設計に変更やアップデートが生じた場合は、IPexpressに戻って自動構成ファイルを生成し直すことを、強く推奨します。いくつかの例外時に限って、ユーザは自動構成ファイルを変更しても構いません。SERDESプロトコル規格用にSERDES/PCSプロックを生成するためIPexpressを用いるときのツールフローを、図8-20に示します。

プロジェクトが異なるディレクトリに保存されるとき、この自動構成ファイルもプロジェクトファイルと同 じディレクトリに手動で移動(又はコピー)する必要があります。

#### 図8-20 SERDES PCS ispLEVERユーザフロー

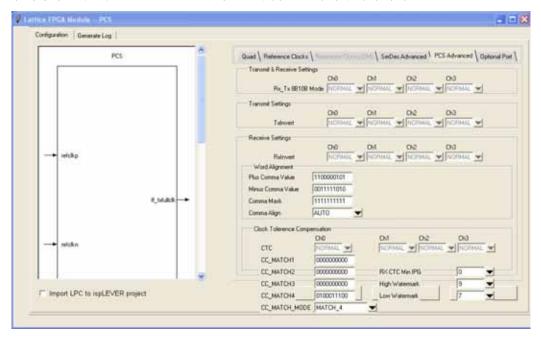

図8-21は、PCSがIPexpress GUIで選択された時のメインウィンドーを示します。

LatticeECP2M 8-29 SERDES/PCS-UGJ

### 図8-21 IPexpress PCSメインウィンドー

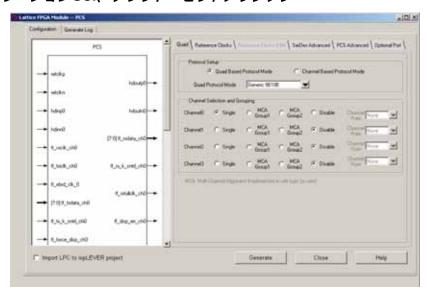

# クワッド・セットアップタブ

図8-22は、メインウィンドーでファイル名が入力され、Customizeボタンがチェックされた時のクワッド・セットアップタブを示します。このウィンドウで必要な最初のエントリは、プロトコルモードをQuad Based ModeかChannel Based Modeから選択することです。このスクリーン上の他のエントリーは、チャネルの選択とグループの選択です。図8-23から図8-28で示す5つのタブがあり、デフォルト値設定と共にユーザアクセス可能なすべての属性を示します。

図8-22 コンフィグレーションGUI、クワッド・セットアップタブ

LatticeECP2M 8-30 SERDES/PCS-UGJ

| 表8-9 SERDES PCS GUI属性 - クワッドタブ・セット | <i>アットタフ・ヤットアッフ</i> |

|------------------------------------|---------------------|

|------------------------------------|---------------------|

| GUIテキスト                 | 属性名      | 範 囲                                                                                                                    | デフォルト値              |

|-------------------------|----------|------------------------------------------------------------------------------------------------------------------------|---------------------|

| Protocol Setup          |          | Quad Based Protocol Mode,                                                                                              | Quad Based Protocol |

| r totocor Setup         |          | Channel Based Protocol Mode                                                                                            | Mode                |

| Quad Protocol Mode      | PROTOCOL | PCI Express, Gigabit Ethernet, Generic<br>8b10b, 10-bit SERDES Only, 8-bit SERDES<br>Only, SD-SDI, HD-SDI <sup>2</sup> |                     |

| Single                  | CH_MODE  | チャネルをイネーブル                                                                                                             | Disable             |

| MCA Group1 <sup>3</sup> | CH_MODE  | Multi-Channel Alignment Group 1                                                                                        | Disable             |

| MCA Group2 <sup>3</sup> | CH_MODE  | Multi-Channel Alignment Group 2                                                                                        | Disable             |

| Disable                 | CH_MODE  | チャネルをディセーブル                                                                                                            | Disable             |

| Channel Rate 1          | CH_MODE  | Full Rate, Half Rate                                                                                                   | Full Rate           |

- 1. Channel Rate選択はChannel Based Protocol Mode内のみに適用できます。

- 2. プロトコル属性名:PCI Express=PCIE、ギガビットイーサネット=GIGE、汎用8b10b=G8B10B、8ビット SERDES Only=8BSER、10ビットSERDES Only=10BSER、SD-SDI=SDSDI(HD-SDI=HDSDI)。

- 3. マルチチャネル・アライメント (MCA) は送信レーン間スキュー調整のためのものです。レシーバのMCA はハードPCSでは提供していません。MCA Group1とMCA Group2は、ユーザがFPGAコアでMCAを構築できるように、チャネルをCTCバイパスモードに設定します。マルチプロトコル・アプリケーションで、チャネルの識別に2つのグループを指定できます。

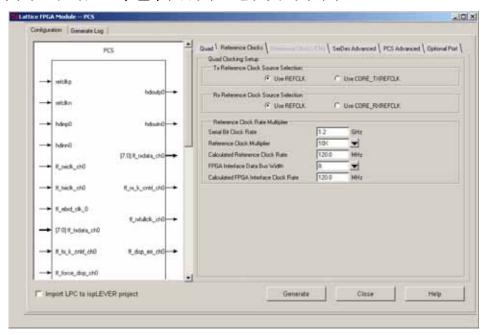

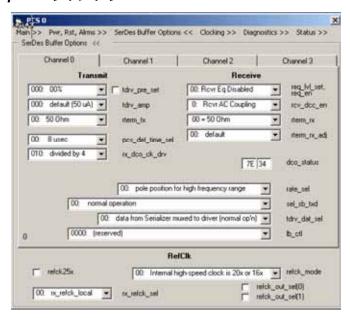

### 基準クロック・セットアップタブ

このタブでは、TxとRx基準クロックソースの属性を選択します。クワッドベースの場合、Rx基準クロックソースとして REFCLK か CORE\_RXREFCLK の選択、Tx 基準クロックソースとして REFCLK か CORE\_TXREFCLKを選択できます。クワッドベースでは、TxとRx共に全チャネルが共通の基準クロックソースを用います。また、特定のデータレートに必要なクロックレートと乗数の設定を提供するツールがあります。選択したデータバス幅に対して、クワッドをコアとインターフェイスするために必要なクロックレートを自動計算して表示します。

図8-23 コンフィグレーションGUI、基準クロック・セットアップタブ

LatticeECP2M 8-31 SERDES/PCS-UGJ

表8-10 SERDES\_PCS GUI属性(LatticeECP2M) - 基準クロック・セットアップタブ

| GUIテキスト                                                       | 属性名                                                                     | ボタン/ボッ<br>クスタイプ | 範 囲                      | デフォル<br>ト値 | コメント                                        |

|---------------------------------------------------------------|-------------------------------------------------------------------------|-----------------|--------------------------|------------|---------------------------------------------|

| Tx Reference Clock Source Selection                           | PLL_SRC                                                                 | Radio           | REFCLK,<br>CORE_TXREFCLK | REFCLK     |                                             |

| Rx Reference Clock<br>Source Selection                        | CH0_CDR_SRC,<br>CH1_CDR_SRC,<br>CH2_CDR_SRC,<br>CH3_CDR_SRC             | Radio           | REFCLK,<br>CORE_RXREFCLK | REFCLK     |                                             |

| Serial Bit Clock Rate<br>(GHz)                                | DATARANGE <sup>1</sup>                                                  | Check Box       | 0.27 ~ 3.125             | 2.5        | LOW:<br>MEDLOW:<br>MED:<br>MEDHIGH:<br>HIGH |

| Reference Clock<br>Multiplier                                 | CH0_REFCK_MULT,<br>CH1_REFCK_MULT,<br>CH2_REFCK_MULT,<br>CH3_REFCK_MULT | Drop Down       | 表8-11参照                  | 25X        |                                             |

| Calculated Reference<br>Clock Rate (MHz) <sup>2</sup>         | CP:REFCLK_RATE                                                          | Text Box        |                          |            | 編集不可                                        |

| FPGA Interface Data<br>Bus Width                              | CH0_DATA_WIDTH,<br>CH1_DATA_WIDTH,<br>CH2_DATA_WIDTH,<br>CH3_DATA_WIDTH | Drop Down       | 表8-11参照                  | 8          |                                             |

| Calculated FPGA<br>Interface Clock Rate<br>(MHz) <sup>2</sup> | CP:<br>FPGAINTCLK_RATE                                                  | Text Box        |                          |            | 編集不可                                        |

### 1. DATARANGE;

量産用デバイス; Low 500Mbps, 500 Mbps < Medlow 1.0 Gbps, 1.0 Gbps < Med < 2.0 Gbps, 2.0 Gbps Medhigh < 2.5 Gbps, 2.5 Gbps High 3.2 Gbps

エンジニアリング・サンプル; Low 540 Mbps, 540 Mbps < Medlow 1.0 Gbps, 1.0 Gbps < Med < 2.0 Gbps, 2.0 Gbps Medhigh < 2.5 Gbps, 2.5 Gbps High 3.2 Gbps

等価な制御レジスタとビットの詳細については表8-105を参照してください。

2. SERDES Only Modeは8ビットと10ビット共にリンク/コンマ・アラインと、8b10bエンコーダ/デコーダ、およびCTCをバイパスしますが、CDRはバイパスしません。

表8-11 プロトコルごとの基準クロック乗数とFPGAインターフェイス・データバス幅

| プロトコル              | 基準クロック乗数       | FPGAインターフェイス・<br>データバス幅 |

|--------------------|----------------|-------------------------|

| PCI Express        | 20X, 25X       | 8, 16                   |

| GbE                | 10XH, 10X, 20X | 8, 16                   |

| G8B10B             | 10XH, 10X, 20X | 8, 16                   |

| 10-bit SERDES Only | 10XH, 10X, 20X | 10, 20                  |

| 8-bit SERDES Only  | 8HX, 8X, 16X   | 8, 16                   |

LatticeECP2M 8-32 SERDES/PCS-UGJ

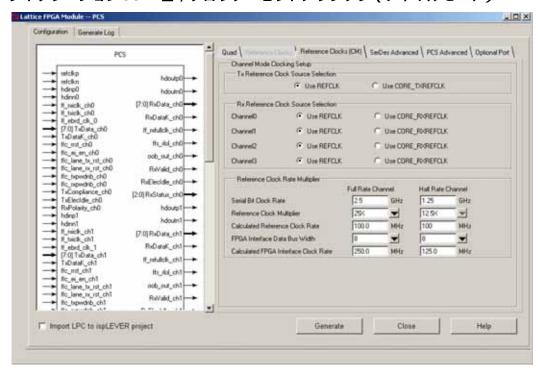

# 基準クロック・セットアップタブ(チャネルモード)

このタブでは、選択されたTx基準クロックは全チャンネルに共通ですが、チャネルモードでのRx基準クロックは、チャネルごとにREFCLKかCORE\_RXREFCLKのどちらかを選択できます。

図8-24 コンフィグレーションGUI - 基準クロック・セットアップタブ(チャネルモード)

ユーザがQuadタブでChannel Based Protocol Modeを選択して、いづれかのチャネルをハーフレートモードとして設定すると、このタブはハーフレートモード・クロックデータを表示します。

LatticeECP2M 8-33 SERDES/PCS-UGJ

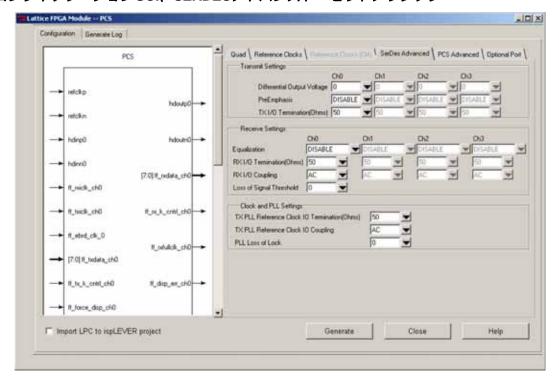

### SERDESアドバンスト・セットアップ

このタブは、全4チャネル用のSERDESの送受信用アドバンスト属性にアクセスするために使用されます。 プリエンファシス、終端、差動出力電圧の選択などの送信用属性や、等化、終端、I/Oカップリングなどの受 信用属性が選択されます。また、SERDES送信クロックとPLLの属性も指定できます。

図8-25 コンフィグレーションGUI、SERDESアドバンスト・セットアップタブ

LatticeECP2M 8-34 SERDES/PCS-UGJ

表8-12 SERDES\_PCS GUI属性 (LatticeECP2M)、SERDESアドバンスト・セットアップタブ

| GUIテキスト                           |                                                        |                                                              | ボタン/ボ        | 範囲                                                                                                                                                                                                                |                                                                        | デフォル    |

|-----------------------------------|--------------------------------------------------------|--------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------|

|                                   |                                                        | 属性名                                                          | ックスタ<br>イプ   | PCI Express,<br>GIGE                                                                                                                                                                                              | G8B10B, 8bSER<br>10bSER                                                | ト値      |

|                                   | LatticeECP2M-35<br>その他の全デバイ<br>ス                       | CH0_TDRV_AMP<br>CH1_TDRV_AMP<br>CH2_TDRV_AMP<br>CH3_TDRV_AMP | Drop<br>Down | 0(1040mV: default), 1(1280mV),<br>2 (1320mV), 3 (1360mV), 4 (640mV),<br>5 (760mV), 6 (870mV), 7 (990mV)<br>0(990mV: default), 1(1250mV),<br>2 (1300mV), 3 (1350mV), 4 (610mV),<br>5 (730mV), 6 (820mV), 7 (940mV) |                                                                        | 0       |

|                                   | LatticeECP2M-35<br>その他の全デバイ<br>ス                       | CH0_TX_PRE<br>CH1_TX_PRE<br>CH2_TX_PRE<br>CH3_TX_PRE         | Drop<br>Down | Disable, 0 (0%), 1<br>3 (40%), 4 (44%),<br>Disable, 0 (0%), 1<br>3 (30%), 4 (33%),                                                                                                                                | (16%), 2 (36%),<br>5 (56%), 6 (80%)<br>(12%), 2 (26%),                 | DISABLE |

|                                   | ination (Ohms) <sup>3</sup><br>端)                      | CH0_RTERM_TX<br>CH1_RTERM_TX<br>CH2_RTERM_TX<br>CH3_RTERM_TX |              | 50 75 5K                                                                                                                                                                                                          |                                                                        | 50      |

| Equalization<br>(等化)              | 1                                                      | CH0_RX_EQ<br>CH1_RX_EQ<br>CH2_RX_EQ<br>CH3_RX_EQ             | Drop<br>Down | Mid_High,<br>Long_High                                                                                                                                                                                            | Mid_Low,<br>Mid_Med<br>Mid_High,<br>Long_Low<br>Long_Med,<br>Long_High | DISABLE |

| Rx I/O Term<br>(受信I/O終            | iination (Ohms) <sup>3</sup><br>端)                     | CH0_RTERM_RX<br>CH1_RTERM_RX<br>CH2_RTERM_RX<br>CH3_RTERM_RX | Drop<br>Down | · 1 50 60 /5 F100                                                                                                                                                                                                 |                                                                        | 50      |

| Rx I/O Coup<br>(レシーバル             |                                                        | CH0_RX_DCC<br>CH1_RX_DCC<br>CH2_RX_DCC<br>CH3_RX_DCC         | Drop<br>Down | ·   A(, 1)(,                                                                                                                                                                                                      |                                                                        | AC 2    |

| Loss of Sign<br>(LOS検出間           | nal Threshold<br>閾値)                                   | LOS_THRESHOL<br>D                                            | Drop<br>Down | 0 (default), 1 (+10%), 2 (+15%),<br>3 (+25%), 4 (-10%),<br>5 (-15%), 6 (-25%), 7 (-30%)                                                                                                                           |                                                                        | 0       |

| Termination                       | eference Clock I/O<br>(Ohms) <sup>3</sup><br>長準クロック入力の | DII TEDM                                                     | Drop<br>Down | op 50.2K                                                                                                                                                                                                          |                                                                        | 50      |

| Coupling                          | eference Clock I/O<br>基準クロック入力の                        | DLL DCC                                                      | Drop<br>Down | Δι. 1)ι.                                                                                                                                                                                                          |                                                                        | AC      |

| PLL Loss of Lock<br>(PLLロックはずれ検出) |                                                        | PLL_LOL_SET                                                  | Drop<br>Down | Lock 0 (+/-600ppmx) 1 (+/-300ppm) 2 (+/-1500ppm) 3 (+/-4000ppm)                                                                                                                                                   | Unlock 0 (+/-1200ppm) 1 (+/-2000ppm) 2 (+/-2200ppm) 3 (+/-6000ppm)     | 0       |

<sup>1.</sup> 詳細については付録Dを参照してください。

LatticeECP2M 8-35 SERDES/PCS-UGJ

<sup>2.</sup> 内部のオンチップAC結合のコンデンサーTyp.値は5pFです。

<sup>3.</sup> 終端抵抗とその使い方 Rx I/O終端:

- 50: 現状ではSMTPE以外のプロトコルはすべて50 終端抵抗を用います。

- 60: 柔軟性の目的だけに提供します。

- 75: SMPTEは75 終端抵抗を用います。

- High: PCI Expressのレシーバ検出用など。

#### Tx I/O終端:

- 50: 現状ではSMTPE以外のプロトコルはすべて50 終端抵抗を用います。

- 75: SMPTEは75 終端抵抗を用います。

- 5K: PCI Expressの電気的アイドルやレシーバ検出のような場合。

#### Tx PLL終端:

- 50: PCB上に50 終端抵抗がない場合

- 2k: PCB上に50 終端抵抗がない場合

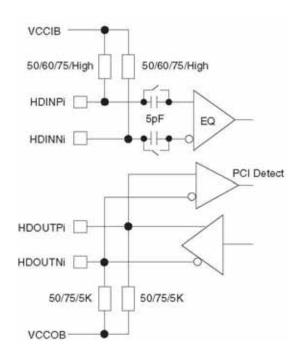

高速I/O終端トポロジーを図8-26に示します。

#### 図8-26 高速I/O終端

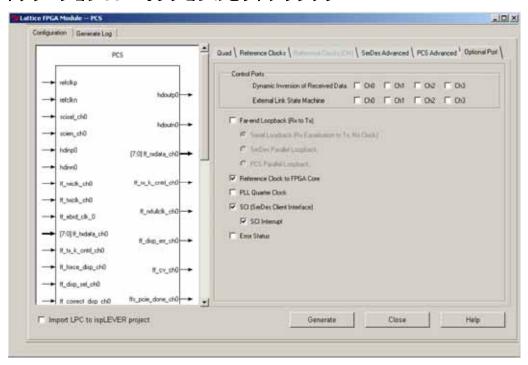

### PCSアドバンスト・セットアップ

このタブは、PCSの送受信全4チャネルのアドバンスト属性にアクセスするために使用されます。各TxとRx チャネルの極性や動作モード(例えば、8b10b)を個別に選択することができます。さらに、コンマ値やコンママスク、コンマアラインなどのワードアライメント指定や、CTCブロック用パラメータを設定するためにも用いられます。

LatticeECP2M 8-36 SERDES/PCS-UGJ

図8-27 コンフィグレーションGUI - PCSのアドバンスト・セットアップタブ

表8-13 SERDES/PCS GUI 'Range' - PCSのアドバンスト・セットアップタブ

| GUIテキスト                  | 属性名                 | 8b<br>SERDES<br>Only | 10b<br>SERDES<br>Only       | G8B10<br>B           | PCI<br>Express | GIGE | SD-SDI | HD-SDI     | Default    |

|--------------------------|---------------------|----------------------|-----------------------------|----------------------|----------------|------|--------|------------|------------|

| TX Invert                | CHx_TX_SB           |                      |                             | Nor                  | mal, Inve      | rt   |        |            | Normal     |

|                          | CHx_RX_SB           |                      |                             | INOI                 | IIIai, IIIvei  | ι    |        |            | Normal     |

|                          | CHx_8B10B           | Вур                  | Bypass Normal Bypass        |                      |                |      | pass   | Normal     |            |

| value                    | COMMA_A 4           |                      |                             |                      |                |      |        | 1100000101 |            |

| Minus Comma<br>Value     | COMMA_B⁴            | N/A                  | 注1                          |                      |                | N    | N/A    | 0011111010 |            |

| Comma Mask               | COMMA_M             |                      |                             |                      |                |      |        | 1111111111 |            |

| Comma Align <sup>2</sup> | CHx_COMMA_A<br>LIGN | Bypass               | Auto,<br>Dynamic,<br>Bypass | Auto,<br>Dynami<br>c | Au             | to   | Ву     | pass       | Auto       |

| CTC <sup>3</sup>         | CHx_CTC_BYP         | Bypass               | Normal, I                   | Bypass               | Norr           | mal  | Ву     | pass       | Normal     |

| CC_MATCH1                | CC_MATCH1           |                      |                             |                      |                |      |        |            | 000000000  |

| CC_MATCH2                | CC_MATCH2           |                      |                             | 注                    | ÷a             |      |        |            | 000000000  |

| CC_MATCH3                | CC_MATCH3           |                      |                             | /王                   | J              |      |        | I/A        | 0100011100 |

| CC_MATCH4                | CC_MATCH4           |                      |                             |                      |                |      |        |            | 0100011100 |

|                          | CC_MATCH_MO<br>DE   | N/A                  | MATCH_3_4                   |                      | MATC           | CH_4 |        |            | MATCH_4    |

| RX CTC Min IFG           | RX CTC Min IFG      |                      | 0, 1, 2, 3                  |                      |                |      | 0      |            |            |

| High Watermark           | CCHMARK             |                      |                             | 0.1.2 14.15          |                |      |        | 9          |            |

| Low Watermark            | CCLMARK             |                      |                             | 0, 1, 2,, 14, 15     |                |      |        | 7          |            |

<sup>1.</sup> 詳細な情報はこのドキュメントの"ワードアラインメント"セクションを参照してください。

LatticeECP2M 8-37 SERDES/PCS-UGJ

- 2. 表8-7を参照してください。

- 3. 詳細な情報はこのドキュメントの"クロックトレランス補償"セクションを参照してください。

- 4. 定義上、COMMA\_AとCOMM\_Bは正と負のランニング・ディスパリティがある1組の8b10bコード化された制御キャラクタです。例えば、一つのデザインでBC(K28.5)とFD(K29.7)をCOMMA\_AとCOMM\_Bとして用いることはできません。8ビットモードと16ビットモードでのCOMM\_AとCOMM\_Bの使用法は全く同じです。ユーザはIs\_syncを得るためには規則に従う必要があります。例えば、1GbEがIDLEとなる(ワードアライメントと同期ステートマシン)にはK28.5+D5.6かD16.2が必要です。

#### オプションのセットアップ

このタブは、チャネルあたりのダイナミック・ロジック反転とダイナミックな外部リンクステートマシン機能を選択するのに用いられます。さらにユーザはSCI、エラーレポート、PLLの4分周クロック、およびループバック機能をイネーブルすることができます。

図8-28 コンフィグレーションGUI - オプションのセットアップタブ

表8-14 Tab5、SERDES\_PCS GUI属性(LatticeECP2M) - オプションのセットアップタブ

| GUIテキスト                           | 属性名                                | ボタン/ボッ<br>クスタイプ | 範囲                                                               | デフォル<br>ト値         |

|-----------------------------------|------------------------------------|-----------------|------------------------------------------------------------------|--------------------|

| Dynamic Inversion of Receive Data |                                    | Check Box       | TRUE, FALSE                                                      | FALSE              |

| External Link State Machine       |                                    | Check Box       | TRUE, FALSE                                                      | FALSE              |

| Loopback (Rx to Tx)               |                                    | Check Box       | TRUE, FALSE                                                      | FALSE              |

| Loopback Type                     | OS_SSLB OS_SPLBPORTS OS_PCSLBPORTS | Radio Box       | Serial Loopback, SERDES Parallel Loopback, PCS Parallel Loopback | Serial<br>Loopback |

| Reference Clock to FPGA Core      | OS_REFCK2CORE                      | Check Box       | TRUE, FALSE                                                      | FALSE              |

| PLL Quarter Clock                 | OS_PLLQCLKPORTS                    | Check Box       | TRUE, FALSE                                                      | FALSE              |

| SCI                               |                                    | Check Box       | TRUE, FALSE                                                      | FALSE              |

LatticeECP2M 8-38 SERDES/PCS-UGJ

| SCI Interrupt | OS_INT_ALL | Check Box | TRUE, FALSE | FALSE |

|---------------|------------|-----------|-------------|-------|

| Error Status  |            | Check Box | TRUE, FALSE | FALSE |

#### コンフィグレーション(自動構成)ファイル記述

IPexpressは属性レベルのマッピング情報を含むこのファイルを生成します。自動構成ファイルはファイルタイプ拡張子として "txt" を用います。

以下にファイル例を示します。

```

# This file is used by the simulation model as well as the ispLEVER bitstream

# generation process to automatically initialize the PCSC quad to the mode

# selected in the IPexpress. This file is expected to be modified by the

# end user to adjust the PCSC quad to the final design requirements.

DEVICE NAME "LFE2M35E"

PROTOCOL "G8B10B"

CHO MODE "SINGLE"

CH1 MODE "DISABLE"

CH2 MODE "DISABLE"

CH3 MODE "DISABLE"

PLL SRC "REFCLK"

DATARANGE "HIGH"

CHO CDR SRC "REFCLK"

CHO DATA WIDTH "8"

CHO REFCK_MULT "10X"

#REFCLK_RATE 250.0

#FPGAINTCLK RATE 250.0

CHO TDRV AMP "0"

CHO TX PRE "DISABLE"

CHO_RTERM_TX "50"

CHO_RX_EQ "DISABLE"

CHO_RTERM_RX "50"

CHO_RX_DCC "AC"

LOS_THRESHOLD "0"

PLL TERM "50"

PLL DCC "AC"

PLL LOL SET "0"

CHO TX SB "NORMAL"

CHO RX SB "NORMAL"

CHO 8B10B "NORMAL"

COMMA A "1100000101"

COMMA B "0011111010"

COMMA " 1111111111"

CHO COMMA ALIGN "AUTO"

CHO CTC BYP "BYPASS"

CC MATCH1 "000000000"

CC MATCH2 "000000000"

CC MATCH3 "0100011100"

CC_MATCH4 "0100011100"

CC_MATCH_MODE "MATCH 4"

CC MIN IPG "0"

CCHMARK "4"

CCLMARK "4"

OS REFCK2CORE "0"

OS PLLQCLKPORTS "0"

```

### モード特有の制御/ステータス信号

モードに依存する制御/ステータス信号名は、選択されたPCSモードで決定されます。表8-15は24ビット・デ

LatticeECP2M 8-39 SERDES/PCS-UGJ

ータバスの使い方を説明します。表8-16はすべてのIPexpress GUIで選択可能なPCSモードの制御/ステータス信号のポート名を示します。

表8-15 データバスの用途

| データバス                | I/O   | 信号名     | 記述                              |

|----------------------|-------|---------|---------------------------------|

| 送受信データバス;            | 8ビット  | バス      |                                 |

| ff_rxdata_ch0[7:0]   | 0     | 受信データバス | チャネルごと、FPGAへの8ビット受信並列データバス      |

| ff_rxdata_ch0[11:8]  | 0     | 表8-16参照 | モード特有の受信ステータスビット                |

| ff_rxdata_ch0[23:12] | 0     |         | 16ビットモード用予約                     |

| ff_txdata_ch0[7:0]   | I     | 送信データバス | チャネルごと、FPGAからの8ビット送信並列データバス     |

| ff_txdata_ch0[11:8]  | I     | 表8-16参照 | モード特有の送信制御ビット                   |

| ff_txdata_ch0[23:12] | I     |         | 16ビットモード用予約                     |

| 送受信データバス;            | 16ビット | トバス     |                                 |

| ff_rxdata_ch0[7:0]   | 0     | 受信データバス | チャネルごと、FPGAへの第一8bデータ用受信並列データバス  |

| ff_rxdata_ch0[11:8]  | 0     |         | モード特有の第一8bデータ用の受信ステータスビット       |

| ff_rxdata_ch0[19:12] | 0     | 受信データバス | チャネルごと、FPGAへの第二8bデータ用受信並列データバス  |

| ff_rxdata_ch0[23:20] | 0     |         | モード特有の第二8bデータ用の受信ステータスビット       |

| ff_txdata_ch0[7:0]   | I     | 送信データバス | チャネルごと、FPGAからの第一8bデータ用送信並列データバス |

| ff_txdata_ch0[11:9]  | I     |         | モード特有の第一8bデータ用の送信制御ビット          |

| ff_txdata_ch0[19:12] | I     | 送信データバス | チャネルごと、FPGAからの第二8bデータ用送信並列データバス |

| ff_txdata_ch0[23:20] | I     |         | モード特有の第二8bデータ用の送信制御ビット          |

注: チャネル0を示します。他のすべてのチャネルが同様に割り当てられます。

#### 表8-16 モード特有の制御/ステータス信号名

#### 受信データステータス信号、8ビットバス

| モード              | ff_rxdata_ch0[8]  | ff_rxdata_ch0[9] | ff_rxdata_ch0[10] | ff_rxdata_ch0[11] |

|------------------|-------------------|------------------|-------------------|-------------------|

| GbE, OBSAI, CPRI | ff_rx_k_cntrl_ch0 | ff_disp_err_ch0  | ff_cv_ch0         | ff_rx_even_ch0    |

| FC, SRIO, G8B10B | ff_rx_k_cntrl_ch0 | ff_disp_err_ch0  | ff_cv_ch0         | NA                |

| XAUI             | ff_rxc_ch0        | ff_disp_err_ch0  | ff_cv_ch0         | NA                |

| PCI Express      | ff_rx_k_cntrl_ch0 |                  |                   |                   |

### 送信データ制御信号、8ビットバス

| モード              | ff_txdata_ch0[8]  | ff_txdata_ch0[9]  | ff_txdata_ch0[10] | ff_txdata_ch0[11]   |

|------------------|-------------------|-------------------|-------------------|---------------------|

| GbE, OBSAI, CPRI | ff_tx_k_cntrl_ch0 | NA                | ff_xmit_ch0       | ff_correct_disp_ch0 |

| FC, SRIO         | ff_tx_k_cntrl_ch0 | ff_force_disp_ch0 | ff_disp_sel_ch0   | NA                  |

| XAUI             | ff_txc_ch0        | NA                | NA                | NA                  |

| PCI Express      | ff_tx_k_cntrl_ch0 | ff_force_disp_ch0 | ff_disp_sel_ch0   | ff_pci_ei_en_ch0    |

| G8B10B           | ff_tx_k_cntrl_ch0 | ff_force_disp_ch0 | ff_disp_sel_ch0   | ff_correct_disp_ch0 |

#### モード特有の制御/ステータス信号記述

表8-17はモード特有の制御/ステータス信号について説明します。

LatticeECP2M 8-40 SERDES/PCS-UGJ

#### 表8-17 制御信号とそれらの機能

| 信号名                          | 記述                                                                                 |

|------------------------------|------------------------------------------------------------------------------------|

| 送信制御信号                       |                                                                                    |

| ff_tx_k_cntrl_ch[3:0]        | チャネルごと、Highアクティブの制御キャラクタ・インジケータ。                                                   |

| ff_force_disp_ch[3:0]        | チャネルごと、Highアクティブの信号で、ff_disp_sel_ch(0-3)FPGAインターフェイス入力からのディスパリティ値を受け入れるようPCSに指示する。 |

| ff_disp_sel_ch[3:0]          | チャネルごとで、ディスパリティ値はFPGAロジックから与えられる。<br>ff_force_disp_ch(0-3)がhighのときに有効。             |

| ff_correct_disp_ch[3: 0]     | パケット間ギャップが負のディスパリティ·ステートで始まることを保証するために使用される。                                       |

| 受信ステータス信号                    |                                                                                    |

| ff_rx_k_cntrl_ch[3:0]        | チャネルごと、Highアクティブの制御キャラクタ・インジケータ。                                                   |

| ff_disp_error_detect_ch[3:0] | チャネルごと、PCSからドライブされるhighアクティブの信号で、関連するデータにディスパリティ・エラーが検出されたことを示す。                   |

| ff_cv_detect_ch[3:0]         | チャネルごと、Highアクティブのコードバイオレーション検出。                                                    |

1. 詳細な情報はこのドキュメントの "ギガビット・イーサネットモードのLatticeECP2M PCS" セクションを参照してください。

Generic 8b10b(G8B10B)モードにおけるデータと制御/ステータスビットのマッピング例:

```

8-bit mode

.FF TX D 0 0(ff txdata ch0[0]),

.FF TX D 0 3 (ff txdata ch0[3]),

.FF_TX_D_0_4(ff_txdata_ch0[4]),

.FF_TX_D_0_5(ff_txdata_ch0[5]),

.FF_TX_D_0_6(ff_txdata_ch0[6]),

.FF_TX_D_0_7(ff_txdata_ch0[7]),

.FF_TX_D_0_8(ff_tx_k_cntrl_ch0[0]),

.FF_TX_D_0_9(ff_force_disp_ch0[0]),

.FF TX D_0_10(ff_disp_sel_ch0[0]),

.FF_TX_D_0_11(ff_correct_disp_ch0[0]),

.FF_TX_D_0_12(fpsc_vlo),

.FF TX D 0 13 (fpsc vlo),

.FF_TX_D_0_14(fpsc_vlo),

.FF_TX_D_0_15(fpsc_vlo), .FF_TX_D_0_16(fpsc_vlo),

.FF_TX_D_0_17(fpsc_vlo),

.FF_TX_D_0_18(fpsc_vlo), .FF_TX_D_0_19(fpsc_vlo),

.FF TX D 0 20 (fpsc vlo),

.FF_TX_D_0_21(fpsc_vlo),

.FF_TX_D_0_22(fpsc_vlo),

.FF_TX_D_0_23(fpsc_vlo),

.FF_RX_D_0_1(ff_rxdata_ch0[0]),

.FF_RX_D_0_1(ff_rxdata_ch0[1]),

.FF_RX_D_0_2(ff_rxdata_ch0[2]),

.FF RX D 0 3 (ff rxdata ch0[3]),

.FF_RX_D_0_4(ff_rxdata_ch0[4]),

.FF_RX_D_0_5(ff_rxdata_ch0[5]),

.FF RX D 0 6 (ff rxdata ch0[6]),

.FF_RX_D_0_9(ff_rxdata_ch0[7]),

.FF_RX_D_0_8(ff_rx_k_cntrl_ch0[0]),

.FF_RX_D_0_9(ff_disp_err_ch0[0]),

.FF RX D 0 10 (ff cv ch0 \overline{[0]}),

.FF_RX_D_0_11(fpsc_vlo),),

.FF_RX_D_0_12(fpsc_vlo),

.FF RX D 0 13 (fpsc vlo),

.FF_RX_D_0_14(fpsc_vlo), .FF_RX_D_0_15(fpsc_vlo),

```

LatticeECP2M 8-41 SERDES/PCS-UGJ

```

.FF_RX_D_0_16(fpsc_vlo),

.FF_RX_D_0_17(fpsc_vlo),

.FF_RX_D_0_18(fpsc_vlo),

.FF_RX_D_0_19(fpsc_vlo),

.FF_RX_D_0_20(fpsc_vlo), .FF_RX_D_0_21(fpsc_vlo),,

.FF RX D 0 22(fpsc vlo),

.FF_RX_D_0_23(fpsc_vlo),

16-bit mode

.FF TX D 0 0(ff txdata ch0[0]),

.FF TX D 0 3 (ff txdata ch0[3]),

.FF_TX_D_0_4(ff_txdata_ch0[4]),

.FF_TX_D_0_5(ff_txdata_ch0[5]),

.FF_TX_D_0_6(ff_txdata_ch0[6]),

.FF TX D 0 7(ff txdata ch0[7]),

.FF_TX_D_0_8(ff_tx_k_cntrl_ch0[0]),

.FF_TX_D_0_9(ff_force_disp_ch0[0]),

.FF TX D_0_10(ff_disp_sel_ch0[0]),

.FF_TX_D_0_11(ff_correct_disp_ch0[0]),

.FF_TX_D_0_12(ff_txdata_ch0[8]),

.FF_TX_D_0_13(ff_txdata_ch0[9]),

.FF_TX_D_0_14(ff_txdata_ch0[10]),

.FF_TX_D_0_15(ff_txdata_ch0[11]), .FF_TX_D_0_16(ff_txdata_ch0[12]),

.FF TX D 0 17(ff txdata ch0[13]),

.FF_TX_D_0_18(ff_txdata_ch0[14]),

.FF_TX_D_0_19(ff_txdata_ch0[15]),

.FF_TX_D_0_20(ff_tx_k_cntrl_ch0[1]),

.FF_TX_D_0_21(ff_force_disp_ch0[1]),

.FF_TX_D_0_22(ff_disp_sel_ch0[1]),

.FF_TX_D_0_23(ff_correct_disp_ch0[1]),

.FF_RX_D_0_0(ff_rxdata_ch0[0]),

.FF_RX_D_0_1(ff_rxdata_ch0[1]),

.FF_RX_D_0_2(ff_rxdata_ch0[2]),

.FF_RX_D_0_3 (ff_rxdata_ch0[3]),

FF_RX_D_0_5(ff_rxdata_ch0[4]),

FF_RX_D_0_5(ff_rxdata_ch0[5]),

FF_RX_D_0_6(ff_rxdata_ch0[6]),

.FF_RX_D_0_7(ff_rxdata_ch0[7]),

.FF_RX_D_0_8(ff_rx_k_cntrl_ch0[0]),

.FF_RX_D_0_9(ff_disp_err_ch0[0]),

.FF_{RX}D_0_{10}(ff_{cv}ch0[0]),

.FF_RX_D_0_11(),

.FF_RX_D_0_12(ff_rxdata_ch0[8]),

.FF_RX_D_0_13(ff_rxdata_ch0[9]),

FF RX D 0 14 (ff rxdata ch0[10]),

FF RX D 0 15 (ff rxdata ch0[11]),

FF RX D 0 16 (ff rxdata ch0[11]),

.FF_RX_D_0_17(ff_rxdata_ch0[13]),

.FF_RX_D_0_18(ff_rxdata_ch0[14]),

.FF_RX_D_0_19(ff_rxdata_ch0[15]),

.FF_RX_D_0_20(ff_rx_k_cntrl_ch0[1]),

.FF_RX_D_0_21(ff_disp_err_ch0[1]),

.FF_RX_D_0_22(ff_cv_ch0[1]),

.FF_RX_D_0_23(),

```

### ギガビット・イーサネットモードのLatticeECP2M PCS

### ギガビット・イーサネット(1000BASE-X)のアイドル挿入

アイドルパターンの挿入がクロック補償と自動ネゴシエーションには必要です。自動ネゴシエーションは FPGAロジックで行われます。このモジュールは自動ネゴシエーションの間、自動的に /l2/ シンボルを受信 データストリームの中に挿入します。自動ネゴシエーション中、リンクパートナは連続して /C1/ と /C2/ の

LatticeECP2M 8-42 SERDES/PCS-UGJ

オーダーセットを送信するでしょう。クロック補償回路はこれらのオーダーセットを削除せず、/l2/ オーダーセットのみを挿入するか、または削除するように構成されています。クロック補償回路におけるオーバーランとアンダーランを防ぐため、挿入/削除する機会をクロック補償回路に与えるように定期的に /l2/ オーダーセットを挿入しなければなりません。

自動ネゴシエーションを実行している間、このモジュールは2048クロックサイクル毎に8回の /l2/ オーダーセット(それぞれ2バイト)シーケンスを挿入します。このモジュールは8b10bデコーダの後にあるため、この動作はどのようなランニング・ディスパリティ誤りを生起することはありません。GMIIインターフェイスは、自動ネゴシエーションの間、RxステートマシンによってIDLEステートに置かれるので、/l2/ オーダーセットがFPGA受信インターフェイスに送られることはありません。自動ネゴシエーションがいったん完了すると、受信データのいかなるエラーをも防ぐために、/l2/ 挿入はディセーブルされます。