# LatticeECP2/M sysCONFIG 使用ガイド

# はじめに

LatticeECP2™ とLatticeECP2M™ FPGA内にあるコンフィグレーション・メモリは、揮発性のSRAMが用いられています。電源がなくなると喪失するコンフィグレーション・データを保持する不揮発メモリが必要です。パワーアップ時、或いはデバイスを更新する必要がある際は、常にこの不揮発性メモリがコンフィグレーション・データを提供します。

複数のコンフィグレーション・オプションをサポートするため、LatticeECP2/MにはsysCONFIG™ インターフェイスと、専用のispJTAG™ ポートがあります。利用できるコンフィグレーション・オプション、ポートが表15-1にリストされています。

表15-1 サポートするコンフィグレーションとポート

| インターフェイス  | ポート                            |

|-----------|--------------------------------|

|           | SPI                            |

| oveCONEIC | SPIm                           |

| sysCONFIG | スレーブシリアル                       |

|           | スレーブパラレル                       |

| ispJTAG   | JTAG (IEEE 1149.1とIEEE 1532準拠) |

このテクニカルノートはLatticeECP2/Mで使用できる全コンフィグレーション・オプションをカバーします。

# 一般的なコンフィグレーション・フロー

LatticeECP2/Mは次の3つのどれかが起きるとコンフィグレーションを開始します。即ちチップに電源が供給されるか、PROGRAMNピンがLowにドライブされるか、もしくはJTAGのリフレッシュ・コマンドがあたえられる場合です。コンフィグレーション・モードに入るとINITピンとDONEピンがLowにドライブされデバイスが初期化されている、即ちコンフィグレーション・データを受け取る準備ができつつあることをことを示します。

LatticeECP2/Mが初期化を終えると、INITNピンはHighにドライブされます。INITNピンのLowからHighへの 遷移時にCFGピンがサンプルされ、その値によりLatticeECP2/Mをどのポートからコンフィグレーションす るかが取り込まれます。次にLatticeECP2/Mは選択されたポートからデータを読み始めて、プリアンブル、 BDB3(16進)を探し始めます。プリアンブル後の全データが有効なコンフィギュレーション・データです。

LatticeECP2/Mが全コンフィギュレーション・データの読み込みを完了し、誤りが全くなかった場合には、DONEピンがHighにされます。そしてLatticeECP2/Mはユーザモード、すなわちユーザの設計に従ってデバイスが機能し始めます。

またLatticeECP2/MはJTAGを介してプログラムすることができることに留意してください。JTAGを介してプログラムするとき、INITN、およびDONE信号は意味がありません。これはIEEE規格に従ってJTAGがチップとそのI/Oの完全な制御を行うためです。

LatticeECP2/Mデバイスもまた、暗号化ビットストリーム・コンフィグレーション・ファイルの使用をサポートする "S" バージョンを提供します。これらのバージョンには、本書で述べられている点を除いて、標準版と同じコンフィグレーション・オプションがあります。これらのデバイスを用いるとき、ユーザは、コンフィグレーション要件を理解するために本テクニカルノートに加えてLatticeECP2/Mファミリ・データシー

LatticeECP2/M 15-1 sysCONFIG UGJ

トとTN1109 (Lattice ECP2/M S-Series Configuration Encryption Usage Guide) を参照してください。

以下の各セクションはLatticeECP2/Mのコンフィグレーション・ピン、各コンフィグレーション・モード、およびすべてのコンフィグレーション・オプションを定義します。

# コンフィグレーション・ピン

LatticeECP2/Mデバイスは2つのタイプ(専用とデュアル用途)のsysCONFIGピンをサポートします。専用ピンはコンフィグレーションのみに用いられます。デュアル用途のピンはコンフィグレーションとして用いられない場合は汎用I/Oピン(GPIO)としても利用できます。その場合以下の事項を守る必要があります。

- ・ I/Oタイプは同じでなければなりません。即ち、コンフィグレーションの間、ピンが3.3V CMOSピン (LVCMOS33)であるなら、それはGPIOとしても3.3V CMOSピンのままでなければなりません。

- デザインプランナ(Design Planner、旧 Preference Editor)を用いて適切なCONFIG\_MODEを選択しなければなりません。そして、コンフィグレーションの後にデュアル・ファンクションのsysCONFIGピンをGPIOとして用いるために、PERSISTENTビットをOFFに設定します。ispLEVER® Design Plannerでこれらの設定ができます。

- ・ ユーザはどのような内部、または外部論理もデバイス・コンフィグレーションを妨げないことを保証 する責任があります。

また、もしスレーブパラレル・コンフィグレーションモードが用いられていない場合、2本のチップセレクト(CSN、CS1N)の一方か両方がコンフィグレーション中にHighかトライステートでなければなりません。

プログラマブル・オプションがデュアル用途のコンフィグレーション・ピンを制御します。このオプションは、ラティスispLEVERソフトウェア内のプリファレンス(設計制約)か、HDLソースファイルの中のアトリビュート(属性)として行います。

表15-2 LatticeECP2/Mデバイス用コンフィグレーション・ピン

| ピン                           | 記述                                   | ピンタイプ                                 | 用いられるモード              |

|------------------------------|--------------------------------------|---------------------------------------|-----------------------|

| CFG[2:0]                     | 入力、弱いプルアップ                           |                                       | 全て                    |

| PROGRAMN                     | 入力、弱いプルアップ                           |                                       | 全て                    |

| INITN                        | 双方向オープン・ドレイン、弱いプルア<br>ップ             | 専用                                    | 全て                    |

| DONE                         | 弱いプルアップのある双方向オープン<br>ドレイン、アクティブ・ドライブ |                                       | 全て                    |

| CCLK                         | 入力、または出力                             |                                       | 全て                    |

| DI/CSSPI0N <sup>2</sup>      | 入力、弱いプルアップ                           |                                       | Serial, SPI, SPIm     |

| DOUT / CSON 2                | 出力                                   |                                       | Parallel, Serial, SPI |

| CSN <sup>2</sup>             | 入力、弱いプルアップ                           | , <del>-</del> , , , , , , ,          | Parallel              |

| CS1N <sup>2</sup>            | 入力、弱いプルアップ                           | ンクション                                 | Parallel              |

| WRITEN <sup>2</sup>          | 入力、弱いプルアップ                           |                                       | Parallel              |

| BUSY/SISPI <sup>2</sup>      | 出力、トライステート、弱いプルアップ                   |                                       | Paralle, SPI, SPIm    |

| D[0] / SPIFASTN <sup>2</sup> |                                      | _,                                    | Parallel, SPI, SPIm   |

| D[1:6] <sup>2</sup>          | 入力、または出力                             | デュアル・ファ<br>ンクション                      | Parallel              |

| D[7] / SPID0 <sup>2</sup>    |                                      |                                       | Parallel, SPI, SPIm   |

| TDI                          | 入力、弱いプルアップ                           |                                       | JTAG                  |

| TDO                          | 出力、弱いプルアップ                           | 専用                                    | JTAG                  |

| TCK                          | ヒステリシスあり入力、                          | 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 | JTAG                  |

| TMS                          | 入力、弱いプルアップ                           |                                       | JTAG                  |

LatticeECP2/M 15-2 sysCONFIG UGJ

- 1. 弱いプルアップは30uA ~ 150uAの電流ソースよりなります。sysCONFIG専用およびデュアル用途ピンのプルアップはV<sub>CCIO8</sub> に追従し、TDI、TDO、およびTMSはV<sub>CCJ</sub> に追従します。

- 2. LatticeECP2M50/M70/M100のsysCONFIGピンはsysCONFIG専用です。sysCONFIG出力ピンは通常のデバイス動作時に、アクティブにドライブされます。

LatticeECP2/Mデバイスはまた、コンフィグレーションのためにispJTAGポートをサポートしますが、これはトランスペアレント・リードバックとJTAGテスト用にも使用します。以下のセクションはsysCONFIGピンとJTAGピンの機能について説明します。表15-2 を参照のために示します

# 専用の制御ピン

以下はコンフィグレーションを制御するのに用いられるLatticeECP2/MのsysCONFIG専用ピンの記述です。 これらのピンの電源はV<sub>CCIO8</sub>です。

デバイスがIEEE1149.1か1532 JTAG制御下にある間、専用のプログラミング・ピンには意味がありません。これはJTAG 1149.1に基づき、通常の内部ロジックではなく、むしろバウンダリ・スキャンセルがピンを制御するためです。

### CFG[2:0]

コンフィグレーション・モードピンCFG[2:0]は弱いプルアップのある専用入力ピンです。CFGピンはINITN の立ち上がりエッジでサンプルされ、コンフィグレーション・モード、即ちLatticeECP2/Mがどのタイプのデバイスからコンフィグレーションされるかを選択します。結果として、CFGピンがどのグループのデュアル用途ピンがデバイスのコンフィグレーションに用いられるかを決定します(表15-2の最左列)。表15-3はコンフィグレーション・モードのリストです。

表15-3 LatticeECP2/Mデバイスのコンフィグレーション・モード

| コンフィグレーション・モード          |                    | CFG[2] | CFG[1] | CFG[0] | D[0] / SPIFASTN |

|-------------------------|--------------------|--------|--------|--------|-----------------|

| SPI                     | ノーマル (0x03)        | 0      | 0      | 0      | プルアップ           |

| SFI                     | 高速 ( 0x0B )        | 0      | 0      | 0      | プルダウン           |

| リザーブ                    |                    | 0      | 0      | 1      | X               |

| SPIm                    | ノーマル (0x03)        | 0      | 1      | 0      | プルアップ           |

| SFIIII                  | 高速 ( 0x0B )        | 0      | 1      | 0      | プルダウン           |

| リザーブ                    |                    | 0      | 1      | 1      | X               |

| リザーブ                    |                    | 1      | 0      | 0      | X               |

| スレーブシリアル (Slave Serial) |                    | 1      | 0      | 1      | Х               |

| リザーブ                    |                    | 1      | 1      | 0      | X               |

| スレーブパラレ                 | ル (Slave Parallel) | 1      | 1      | 1      | D0              |

注; IEEE1149.1と1532のサポート用にJTAGは常時使用可能

#### **PROGRAMN**

PROGRAMNピンは弱いプルアップのある専用入力ピンです。これは非JTAGのSRAMコンフィグレーション・シーケンスを起動するために用いられます。

このピンに与えられる信号がHighからLowになると、デバイスはユーザモードから抜けて、コンフィグレーション・モードに設定されます。LowからHighの遷移でコンフィグレーション・プロセスを開始します。 PROGRAMNピンをLowに維持することで、コンフィグレーション・プロセスの開始を遅らせます。

LatticeECP2/M 15-3 sysCONFIG UGJ

#### INITN

INITNピンは双方向のオープンドレイン制御ピンです。これはLowパルスを駆動することができると共に、Lowパルス入力を検出することができます。

PROGRAMNピンがLowにされるときや、JTAGリセット命令を受け取ったとき、あるいはパワーアップ間にパワーオン・リセット信号が解放された後に、INITNピンはコンフィグレーション回路と外部PROMをリセットするためにLowにドライブされます。PROGRAMNピンがHighにされると、コンフィグレーションの初期化が開始され、それが終了するとINITNピンがHighになります。外部的にINITNピンをLowにしておくことでコンフィグレーションの開始を遅らせられます。INITNピンがLowに保たれている限り、デバイスはコンフィグレーション・モードには入りません。INITNピンがLowからHighに遷移する際にCFGピンをサンプルして、LatticeECP2/Mにどのポートを使用するか決定し、コンフィグレーションを開始します。

コンフィグレーションの間、INITNピンはエラー検出ピンになります。コンフィグレーション中にCRCエラーが検出されると、INITNピンはLowにドライブされます。エラー状態は次のコンフィグレーション開始時にクリアされます。

#### **DONE**

DONEピンは弱いプルアップのある専用の双方向オープンドレイン(デフォルト)か、アクティブ・ドライブの制御ピンです。

INITNがLowになる時にDONEもLowになり、その後INITNとPROGRAMNがHighになり、内部Doneビットがコンフィグレーションの終わりにプログラムされると、DONEピンはリリースされ(オプション設定によってはHighにドライブされ)ます。選択されたウェイクアップ・シーケンスによっては、外部的にDONEピンをLowに保持することができます。その場合、DONEピンが外部的にHighにされるまで、デバイスは機能を開始しません。

DONEピンを用いて外部的にウェイクアップ・シーケンスを遅らせるのは、複数のFPGAの起動を同期させる良い方法です。また、ただ一つのコンフィグレーション・デバイスから複数のFPGAをコンフィグレーションするときは、そのようにする必要があります。

外部デバイスがDONEピンをサンプルするのは、FPGAがコンフィグレーションを終えたかどうかを知る良い方法です。しかしながら、IEEE1532 JTAGを用いてSRAMをコンフィグレーションする場合、DONEピンはバウンダリスキャン・セルによってドライブされるので、コンフィグレーションの間DONEピンの状態には意味がありません(コンフィグレーションが完了すると、DONEは内部ロジック動作に戻って、Highになります)。

#### CCLK

CCLKは双方向ピンです。方向はマスタモードかスレーブモードのどちらが選択されるかに依存します。CFG ピンがサンプルされたときにマスタモードが選択されていると、CCLKピンは出力ピンになります。そうでなければ、CCLKは入力ピンになります。

CCLKピンが出力ピンになる場合、内部プログラマブル・オシレータがCCLKに接続されて、スレーブデバイス用に出力されます。CCLKは、DONEピンがHighにされ、デバイスのウェイクアップ・シーケンスが完了した後120クロックサイクルで止まります。これら余分なクロックは、チェーン内の他デバイスがウェイクアップするのに十分であることを保証できるように出力されます。CCLK出力が止まると、入力としてトライステートになります。例えばPROGRAMNピンがトグルされるなど、次のコンフィグレーション初期化シーケンスでCCLK出力は再開します。

ispLEVERのデザインプランナでのグローバルな設定の1つであるMCCLK\_FREQパラメータは、CCLKマスタ周波数を制御します(周波数選択に関してはデータシートの"オンチップ・オシレータ"セクションを参照してください)。コンフィグレーションCCLKのソフトウェア・デフォルト設定は2.5MHzです。コンフィグレーション中の最初の動作の1つはMCCLK\_FREQパラメータです。一度このパラメータがロードされると、選択された値への周波数が変化します。注意すべきは、スレーブデバイスの周波数仕様やPCBレイアウトの信

LatticeECP2/M 15-4 sysCONFIG UGJ

号インテグリティ機能を損なわないようにすることです。

暗号化されたビットストリーム・ファイルをLatticeECP2/M Sシリーズデバイスにダウンロードするとき、ユーザはCCLK信号に対しての適切な条件を確実に満たなければなりません。これらの条件はTN1109 (LatticeECP2/M Configuration Encryption Usage Guide)に示されています。

# デュアル・ファンクションsysCONFIGピン

以下はデュアル・ファンクションsysCONFIGピンのリストです。これらピンのいづれかがコンフィグレーションやユーザI/Oとして用いられる場合、ユーザは本章の最初に記述されている要件を満たすようにしなければなりません。LatticeECP2M50 / M70 / M100デバイスでは、以下で説明されたsysCONFIGピンは専用のピンです。外付けブートフラッシュにアクセスするために同じピンを用いるとき、これらの出力ピンが異なるI/Oピンからドライブされる間はトライステートになるように、設計時には注意しなければなりません。

これらピンの電源はV<sub>CCIO8</sub>です。

#### DI / CSSPION

DI/CSSPIONデュアル用途ピンはシリアル・コンフィグレーションでのデータ入力DI専用で、弱い内部プルアップがあります。CCLKの立ち上がりでデータを捕捉します。

SPIとSPImモードではDI/CSSPI0NはLowアクティブのチップセレクト出力になり、SPIシリアルフラッシュのチップセレクトをドライブします。

#### **DOUT / CSON / CSSPI1N**

DOUT / CSON / CSSPI1Nピンは出力ピンであり、3つの目的を持っています。

シリアルまたはパラレル・コンフィグレーション・モードでバイパスモードが選択されるとき、このピンは DOUTになります(図15-9を参照)。デバイスが完全にコンフィグレーションされると、ビットストリームにおけるバイパス命令が実行されます。そして次にDI、或いはパラレルのコンフィグレーション・モードの場合はD[0:7]のデータはDOUTピンに配線されます。こうしてデータはシリアルに次のデバイスに渡されます。パラレル・コンフィグレーション・モードでは、D0が最初にシフトアウトされ、D1、D2のように続きます。

パラレル・コンフィグレーション・モードにはまた、フロースルー (FLOW\_THROUGH) オプションがあります。フロースルー・モードが選択されるとき、このピンはChip Select Out (CSON)になります。デバイスが完全にコンフィグレーションされてビットストリームのフロースルー命令が実行されると、CSONピンは次のデバイスをイネーブルするためにLowにドライブされます。データピン[0:7]は各デバイスとパラレルに接続されます(図15-10を参照)。

SPImモードでsysCONFIGデイジーチェイン・モードはサポートされません。

DOUT / CSONは起動時にHighをドライブしますが、ビットストリーム中のバイパス/フロースルー命令の実行、またはユーザコードでI/Oタイプを変えるまでは、Highのままです。

## CSN & CS1N

CSNとCS1Nは共に弱いプルアップがあるローアクティブの入力ピンで、パラレルモードでのみ用いられます。これらの入力は内部でORされ、データピンD[0:7]入力や出力バイトデータをイネーブルするために用いられます。

CSNかCS1NがHighの時、D[0:7]、INITN、およびBUSYピンはトライステートになります。D[0:7]、INITN、およびBUSYピンを制御しているとき、CSNとCS1Nは互換です。CSNとCS1Nの両方をHighにドライブすることは、LatticeECP2/Mがバイパス/フロースルー・モードを抜けることとなり、そしてバイパス・レジスタをリセットします。バイパスやフロースルー・モードを用いない場合、CSNかCS1Nの一方はLowに接続しても構いません。すなわち、この場合これらピンの一方のみがドライブされる必要があります。コンフィグ

LatticeECP2/M 15-5 sysCONFIG UGJ

レーション・ビットストリームをデバイスに入力される間は、CSNとCS1NピンはLowのままにしておかなければなりません。そうでないとコンフィグレーションは失敗します。

デバイスがユーザモードにある間(DONEピンはHigh)に、パラレルピンを用いてコンフィグレーション SRAMをアクセスする必要がある場合、CSNとCS1Nとしてこれらのピンを維持するために、PERSISTENT プリファレンスをONに設定しなければなりません。SRAMはJTAGもしくはスレーブパラレル・モードを用いることでのみ読み出すことができることに留意してください。

#### WRITEN

WRITENピンはパラレルモードのみで用いられる弱くプルアップされたLowアクティブの入力です。

WRITENピンはデータピンD[0:7]の方向を決定するために用いられます。WRITENピンは、デバイスにバイトデータを取り込むにはLowにドライブし、デバイスからデータを読み出すためにはHighにドライブしなければなりません。

デバイスがユーザモードにある間(DONEピンはHigh)にパラレルピンを用いてコンフィグレーションSRAMをアクセスする必要がある場合、WRITENとしてこれらのピンを維持するためにPERSISTENTプリファレンスをONに設定しなければなりません。SRAMはJTAGもしくはスレーブパラレル・モードを用いることでのみ読み出すことができることに留意してください。

#### **BUSY / SISPI**

BUSY/SISPIには二つの機能があります。

パラレル・コンフィグレーション・モードでは、BUSYピンはトライステート出力です。D[0:7]ピンでバイトデータを受ける準備ができているとき、またはバイトデータを読み出す準備ができているときのみ、BUSYピンはデバイスによってLowにドライブされます。BUSYピンはLatticeECP2/Mがパラレルポートでのデータ転送を中断することを可能にします。

デバイスがユーザモードにある間(DONEピンはHigh)にパラレルピンを用いてコンフィグレーションSRAMをアクセスする必要がある場合、BUSYとしてこのピンを維持するためにPERSISTENTプリファレンスをONに設定しなければなりませんSRAMはJTAGもしくはスレーブパラレル・モードを用いることでのみ読み出すことができることに留意してください。

SPIやSPImコンフィグレーション・モードでは、BUSY/SISPIピンはSPIシリアルフラッシュにコントロール信号とデータをドライブする出力になります。コントロール信号とデータはCCLKの立ち下がりエッジで出力されます。デバイスがユーザモードにあるとき(DONEピンがHigh)に、SPIポートを介してSPIメモリをアクセスする必要がある場合、本ピンをSISPIとして確保するためにはPERSISTENT制約を与えなければなりません。

#### DI01 / SPIFASTN

D[0] / SPIFASTNピンには2つの機能があります。

パラレルモードではこのピンD[0]となり、D[1:5]と同様に以下のように動作します。パラレル・データバス D[0:7] の一部で、D[0]は最上位ビットです。デバイスがユーザモードにある間(DONEピンはHigh)に、パラレルピンを用いてコンフィグレーションSRAMをアクセスする必要がある場合、D[1:5]と同様にD[0]としてこのピンを維持するために、PERSISTENTプリファレンスをONに設定しなければなりません。SRAMはJTAG もしくはスレーブパラレル・モードを用いることでのみ読み出すことができることに留意してください。

SPIやSPImモードではD0/SPIFASTNピンは入力になります。SPIFASTNはINITNの立ち上がりエッジでサンプルされます。SPIFASTNがHighである場合、LatticeECP2/Mはオペコード03 (16進)をSPIシリアルフラッシュの読み出しに用いるでしょう。読み出しオペコード03 (16進)は、すべての "25" シリーズSPIシリアルフラッシュで用いられている標準のリードコマンドです。SPIFASTNがLowである場合、LatticeECP2/MはSPI

LatticeECP2/M 15-6 sysCONFIG UGJ

シリアルフラッシュの高速読み出しにオペコードOB (16進)を用います。高速読み出しオペコードOB (16進)は、より高い周波数の読み出しクロックに対応します。正確なクロック速度は各SPIシリアルフラッシュ・メーカーのデータシートに記述されています。

全てのSPIシリアルフラッシュがOB (16進)オペコードをサポートしている訳ではありませんので、メーカーのデータシートを確認してください。またPCBでの信号インテグリティが確保できるように注意しなければなりません。

デバイスがユーザモードにあるとき(DONEピンがHigh)に、SPIポートを介してSPIメモリをアクセスする必要がある場合、本ピンをSPIFASTNとして確保するためにはPERSISTENT制約を与えなければなりません。

SPIやSPImモードではSPIFASTNピンはHighかLowのどちらかに固定しなければなりません。フローティング状態にあるとコンフィグレーションに問題が生じます。

#### D[1:6]

D[1:6]ピンはパラレルモードのみをサポートします。D[1:6]ピンはデータのリード/ライトに用いられるトライステート双方向I/Oピンです。WRITEN信号がLowで、CSNとCS1NピンがLowのとき、D[1:5]ピンはデータ入力になります。WRITEN信号がHighにドライブされ、CSNとCS1NピンがLowのとき、D[1:5]ピンはデータ出力になります。CSNかCS1NのどちらかがHighであると、D[1:6]はトライステートになるでしょう。

ユーザモード中にパラレルピンを用いてSRAMコンフィグレーション・メモリをアクセスする必要があるなら(DONEピンはHigh)、D[1:6]としてこれらのピンをリザーブするようにPERSISTENTプリファレンスをONに設定しなければなりません。SRAMはJTAGもしくはスレーブパラレル・モードを用いることでのみ読み出すことができることに留意してください。

EBRや分散メモリのリードバックには注意が必要です。本動作によってこれらRAMの内容が壊れないようにするのはユーザの責任です。ユーザコードによるアクセス時にリードバックでアクセスすると、壊れるかもしれません。

#### D[7] / SPID0

D[7] / SPID0ピンには、それぞれ2つの機能があります。

パラレルモードでは、これらのピンはD[7]であり、上述のD[1:5]と同じように動作します。D[0:7]はパラレルのデータバスを形成し、D[7]はバイトの最下位ビット(LSb)です。D[1:6]のように、ユーザモード中にパラレルピンを用いてSRAMコンフィグレーション・メモリをアクセスする必要があるなら(DONEピンはHigh)、D[7]としてこれらのピンをリザーブするようにPERSISTENTプリファレンスをONに設定しなければなりません。SRAMはJTAGもしくはスレーブパラレル・モードを用いることでのみ読み出すことができることに留意してください。

SPIとSPImモードでは、D[7] / SPID0ピンは入力になり、SPIシリアルフラッシュの出力データピンに接続します。SPID0上のデータはCCLKの立ち上がりエッジに同期します。

デバイスがユーザモードにあるとき(DONEピンがHigh)に、SPIポートを介してSPIメモリをアクセスする必要がある場合、本ピンをSPID0として確保するためにはPERSISTENT制約を与えなければなりません。

# ispJTAG ピン

ispJTAG ピンは標準のIEEE1149.1TAP(Test Access Port)ピンです。ispJTAG ピンは専用ピンで、LatticeECP2/Mデバイスがパワーアップしているときは常にアクセスできます。加えて、LatticeECP2/MがispJTAGピンを用いているとき、INITNやDONE、CCLKなどのsysCONFIG専用ピンには意味がありません。これは通常の内部論理ではなく、IEEE規格に従ってバウンダリスキャン・セルが各ピンを制御するためです。LatticeECP2/MデバイスがJTAG制御下にある間はPROGRAMNピンも無視されます。

LatticeECP2/M 15-7 sysCONFIG UGJ

これらピンの電源はVcc」です。

#### TDC

テストデータ出力ピンTDOは、シリアルのテスト命令とデータをシフトアウトするのに用いられます。TDOが内部回路によってドライブされていないとき、ピンはハイ・インピーダンス状態にあります。このピンはJTAGコネクタのTDO、またはJTAGチェインの下流のデバイスのTDIに配線されるべきです。TDOピンには内部プルアップ抵抗があります。内部抵抗はVcc」にプルアップされています。

#### TDI

テストデータ入力ピンTDIは、シリアルのテスト命令とデータをシフトインするのに用いられます。このピンはJTAGコネクタのTDI、またはJTAGチェインの上流のデバイスのTDOに配線されるべきです。TDIピンには内部プルアップ抵抗があります。内部抵抗はVcc」にプルアップされています。

#### **TMS**

テストモード・セレクトピンTMSはTAPコントローラのテスト動作を制御します。TCKの立ち下がりエッジで、TMSのステートによって、TAPコントローラ・ステートマシンの状態遷移が行われます。TMSピンには内部プルアップ抵抗があり、 $V_{CCJ}$ にプルアップされています。

#### **TCK**

テストクロック・ピンTCKは、TAPコントローラを動作させ、データおよび命令レジスタへのロード、リロードのためのクロックを提供します。TCKはHighまたはLow状態で止めることができ、またデバイス・データシートで示される周波数まで動作させることができます。TCKピンはTYP値100mV( $V_{CCJ}$ =3.3V時)のヒステリシスをサポートします。TCKピンにはプルアップがありません。 $V_{CC}$ が立ち上がる際にTAPコントローラが不注意にクロッキングされるのを避けるため、PCB上に4.7VCプルダウン抵抗をTCKとグランド間に置くことを推奨します。

暗号化されたビットストリーム・ファイルをLatticeECP2/M Sシリーズデバイスにダウンロードするとき、ユーザはTCK信号に対しての適切な条件を確実に満たなければなりません。これらの条件はLatticeECP2/M S-Series Configuration Encryption Usage Guide(TN1109)に示されています。

#### オプションのTRST

テストリセットTRSTはLatticeECP2/Mではサポートされていません。

#### $V_{CC}$

JTAG用 $V_{CC}$ ピン( $V_{CCJ}$ )を別に持っているため、ユーザはデバイスの他とは異なる電圧レベルをJTAGポートに供給することができます。有効な電圧レベルは3.3Vと、2.5V、1.8V、1.5V、及び1.2Vですが、用いられる電圧はJTAGチェインの他の電圧と同一でなければなりません。JTAGが使用されていなくても $V_{CCJ}$ を接続しなければなりません。

さらなるJTAGチェイン情報に関しては "In-System Programming Design Guidelines for ispJTAG Devices" を参照してください。

# コンフィグレーションとJTAGピンの物理的な記述

sysCONFIG専用ピンとデュアル用途のピンすべてがバンク8の一部です。バンク8の $V_{CCIO}$ が、これらのピンの出力電圧を決定し、入力スレッショルドはispLEVERのデザインプランナで選択されたI/Oタイプによって決定されます(デフォルトは3.3V LVCMOS)。

JTAG電圧レベルとスレッショルドは $V_{CCJ}$  ピンで決定しますので、LatticeECP2/Mが1.2Vから3.3VまでのJTAGチェイン電圧に対応することができます。

LatticeECP2/M 15-8 sysCONFIG UGJ

# コンフィグレーション・モード

シリアルもしくはパラレル・データパスのどちらかを利用して、LatticeECP2/Mデバイスは多くの異なるコンフィグレーション・モードをサポートします。起動時にJTAGリフレッシュ命令が発行されると、或いはPROGRAMNピンがトグルされると、コンフィグレーション・モードを決定するためにCFG[2:0]ピンがサンプルされます。利用できるコンフィグレーション・モードのリストは表15-3を参照してください。

以下の各サブセクションは各コンフィグレーション・モードについてブレークダウンします。各モードのオプションの詳しい情報に関しては、"コンフィグレーション・オプション" セクション以下を参照してください。

# SPIモード

LatticeECP2/MはSPIシリアルフラッシュ規格をサポートするメモリに直接接続することができます(表15-5を参照)。設定のそばのコンフィグレーション・ピンCFG[2:0]をすべてLowにすることで、LatticeECP2/MはSPIインターフェイスからコンフィグレーションします。SPIインターフェイスは、2種のコンフィグレーション・トポロジをサポートします。

- ・単一のSPIシリアルフラッシュから構成される単一のFPGA

- ・単一のSPIシリアルフラッシュから構成される複数個のFPGA

それぞれのECP2/Mデバイスに必要なブートメモリ・サイズは表15-4に示されています。示された値は単一のLatticeECP2/Mデバイスのものです。デュアルブート・アプリケーションのためのサイズは示された値の2倍になります。

表15-4コンフィグレーション最大ビットサイズとSPIフラッシュ・モードのメモリサイズ

| デバイス     | ピットストリーム・<br>サイズ[Mb] | SPI フラッシュの<br>サイズ [Mb] | デュアルプート用SPI<br>フラッシュのサイズ [Mb] |

|----------|----------------------|------------------------|-------------------------------|

| ECP2-6   | 1.5                  | 2                      | 4/8 <sup>2</sup>              |

| ECP2-12  | 2.9                  | 4                      | 8                             |

| ECP2-20  | 4.5                  | 8                      | 16                            |

| ECP2-35  | 6.3                  | 8                      | 16                            |

| ECP2-50  | 8.9                  | 16                     | 32                            |

| ECP2-70  | 13.3                 | 16                     | 32                            |

| ECP2M20  | 5.9                  | 8                      | 16                            |

| ECP2M35  | 9.8                  | 16                     | 32                            |

| ECP2M50  | 15.8                 | 16                     | 32                            |

| ECP2M70  | 19.8                 | 32                     | 64                            |

| ECP2M100 | 25.6                 | 32                     | 64                            |

<sup>1,</sup> 次に記述する以外は、SPIフラッシュのこれら値は暗号化・非暗号化に拘わらず適用されます

LatticeECP2/M 15-9 sysCONFIG UGJ

<sup>2,</sup> LatticeECP2-6 Sシリーズ・デバイスでは、デュアルブート・フラッシュ時の所用サイズはセクタ数の関係で8Mb。

TN1108\_02.1J Sept. 2008

表15-5コンフィグレーション最大ビットサイズとシリアル / パラレル・モードのメモリサイズ

| 4.4      | 全モード                       | スレープシリアル<br>モード           | スレープパラレル<br>モード<br>暗号化時のピット<br>ストリーム・サイズ[Mb] |  |

|----------|----------------------------|---------------------------|----------------------------------------------|--|

| デバイス     | 非暗号化時のピット<br>ストリーム・サイズ[Mb] | 暗号化時のピット<br>ストリーム・サイズ[Mb] |                                              |  |

| ECP2-6   | 1.5                        | 2.3                       | 7.5                                          |  |

| ECP2-12  | 2.9                        | 1.3                       | 14.2                                         |  |

| ECP2-20  | 4.5                        | 6.7                       | 22.0                                         |  |

| ECP2-35  | 6.3                        | 9.4                       | 31.2                                         |  |

| ECP2-50  | 8.9                        | 13.4                      | 44.3                                         |  |

| ECP2-70  | 13.3                       | 20.0                      | 66.1                                         |  |

| ECP2M20  | 5.9                        | 8.9                       | 29.5                                         |  |

| ECP2M35  | 9.8                        | 14.8                      | 48.9                                         |  |

| ECP2M50  | 15.8                       | 23.7                      | 78.6                                         |  |

| ECP2M70  | 19.8                       | 29.7                      | 98.6                                         |  |

| ECP2M100 | 25.6                       | 38.5                      | 127.6                                        |  |

コンフィグレーション時間は表15-4のビットストリームサイズをCCLK周波数で割ることで計算できます。 CCLK周波数はispLEVERのデザインプランナ(Design Planner)を用いて、グローバル制約設定タブで選択できます。CCLK周波数に関する詳細は、本テクニカルノートの"マスタクロック"節、およびD[0]/SPIFASTNピン節の各記述を参照してください。

暗号化されたビットストリーム・ファイルをLatticeECP2/M Sシリーズデバイスにダウンロードするとき、ユーザはCCLK信号に対しての適切な条件を確実に満たなければなりません。これらの条件はLatticeECP2/M S-Series Configuration Encryption Usage Guide (TN1109)に示されています。

#### 表15-6 SPIシリアルフラッシュのベンダーリスト

| ペンダ                        | 品番         |

|----------------------------|------------|

| ST Microelectronics        | M25Pxx     |

| Winbond                    | W25Pxx     |

| Silicon Storage Technology | SST25VFxx, |

|                            | SST25LFxx  |

| Spansion                   | S25FLxx    |

| Atmel                      | AT25Fxx    |

| NexFlash                   | NX2Pxx     |

| Macronix                   | MX25Lxx    |

注;これは完全なリストを意図するものではなく、後日更新される可能性があります。

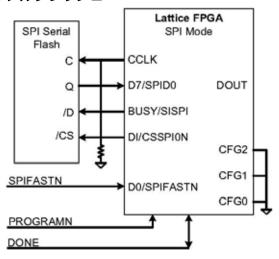

# 単一FPGA、単一SPIフラッシュ

最も簡単なSPIアプリケーションは、図15-1に示されるように、SPIモードによるLatticeECP2/MデバイスのSPID0に接続された、1つのSPIシリアルフラッシュです。これらの条件はTN1109に示されています。暗号化されたビットストリーム・ファイルをLatticeECP2/M Sシリーズデバイスにダウンロードするとき、これは推奨する方法です。

LatticeECP2/M 15-10 sysCONFIG UGJ

TN1108\_02.1J Sept. 2008

図15-1 単一FPGA、単一SPIシリアルフラッシュ

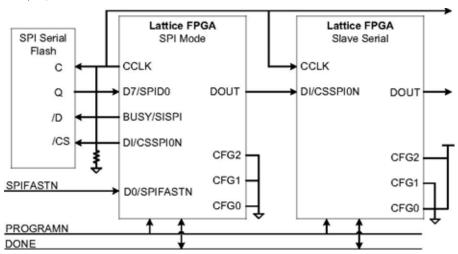

#### 複数のFPGA、単一SPIフラッシュ

十分大きいSPIフラッシュで、図15-2で示されるように複数のFPGAを構成することができます。最初のFPGAはSPIモードで構成されて、次のFPGAはスレーブシリアル・モードで構成されます。

図15-2 複数のFPGA、単一SPIシリアルフラッシュ

注: LatticeECP2/M Sシリーズデバイスに暗号化されたビットストリーム・ファイルを用いるとき、この方法は利用できません。暗号化されたビットストリーム・ファイルを用いることに関する詳しい情報についてはLatticeECP2/M S-Series Configuration Encryption Usage Guide (TN1109)を参照してください。

# SPImモード

SPImモードは、CFGピンを除いて外部的にはSPIモードに似ており、同じSPIシリアルフラッシュ・デバイスを用い、またFPGAに同じ様に配線されます(図15-1を参照)。SPImモードは、図15-2で示されるような単一のSPIシリアルフラッシュから構成される複数個のFPGAはサポートしません。内部的に2つのモードは異なって扱われます。

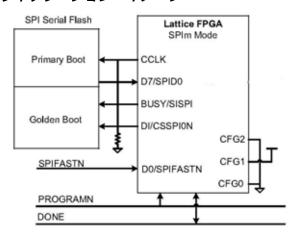

SPIモードは、アドレス・ゼロで始まる単一ブロックのメモリとしてSPIシリアルフラッシュを扱います。 SPImモードは、SPIシリアルフラッシュを単一ブロックのメモリとしてではなく、個別ブロックのメモリと して扱います。これは別々のメモリブロックに異なるコンフィグレーション・イメージの格納することを許 容します。SPImはデュアル・コンフィグレーション・イメージ(または、ブートイメージ)をサポートします

LatticeECP2/M 15-11 sysCONFIG UGJ

が、ここではゴールデン・イメージとプライマリ・イメージと呼ぶことにします。

リモート・アップデートなどのように意図せずSPIシリアルフラッシュに不正なデータをロードされた可能性がある場合に、ゴールデン・イメージが使用されます。例えばフラッシュ消去やプログラミング手順が停電のため中断されると、恐らくフラッシュがこわれたデータを含むため、システムは動作不能に陥るでしょう。理想的には、FPGAはデータが壊れたことを検出し、正しいことがわかっている(ゴールデン)ブートイメージから起動するべきです。これはまさにSPImが実行することです。

ゴールデン・イメージはフラッシュ・アドレス空間の先頭に格納されます。アップデートされる、またはプライマリ・イメージはゴールデン・イメージのアドレス上位に格納されます。コンフィグレーションの間、FPGAがプライマリ・イメージにおけるデータの不正を検出すると、ゴールデン・イメージから自動的にリブートします。FPGAがパワーアップする度に、またはPROGRAMNピンがトグルされる毎に、もしくはJTAGリフレッシュ命令が発行されると、まず最初にプライマリ・イメージからコンフィグレーションしようとします。ゴールデン・イメージのデータも不正であることをLatticeECP2/Mが検出すると、INITNがLowにドライブされ、デバイスはコンフィギュレーションを試みるのを止めることに留意してください。

## デュアルブート・イメージのセットアップ

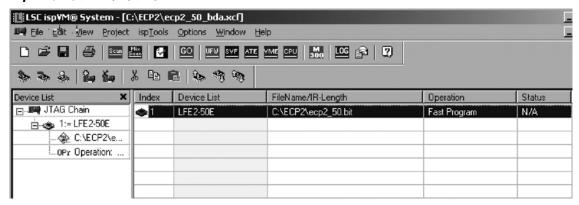

デュアル・コンフィグレーションのファイルを用いるためには、最初にSPIシリアルフラッシュの中に適切にファイルを格納しなければなりません。これはラティスのIspVMソフトウェアで簡単にできます。

図15-3 ispVMメイン・ウィンドー

まず最初にispLEVERを用いて必要なファイルを作成してください。アプリケーションによって、これらのファイルは同じ設計であるか、または異なる設計でも構いません。これらのファイルは何も特別なものではありません。言い換えれば、これらはFPGAを完全にコンフィギュレーションするために必要な情報のすべてを含んでいます。

次にispVMを開き(図15-3参照)、そしてツールバーでSCANボタンをクリックすることによって、ボードのスキャンをしてください。次に、LatticeECP2/Mがあるチェインの列をダブルクリックします。するとデバイス情報ウィンドウが現れます(図15-4)。

LatticeECP2/M 15-12 sysCONFIG UGJ

TN1108\_02.1J Sept. 2008

図15-4 デバイス情報 (Device Information ) ウィンドウ

デバイスオプション ( Device Options ) ドロップダウン・ボックスから、Dual Boot SPI Flash Programming を選択します。そしてSPIフラッシュオプション ( SPI Flash Options ) ボタンをクリックして、SPIシリアルフラッシュ・デバイス ( SPI Serial Flash Device ) ウィンドウを開けてください(図15-5)。このウィンドウで Selectをクリックし、そしてボード上に実装されているSPIフラッシュを選びます。

図15-5 SPIシリアルフラッシュ・デバイスウィンドウ

2番目にBrowseをクリックして、出力ファイル名を選択します。

LatticeECP2/M 15-13 sysCONFIG UGJ

3番目にSPI Flash Erase、Program、Verifyなどの動作を選択します。

4番目に、ゴールデン・ファイルとプライマリ・ファイルを選択します。これらがLatticeECP2/M Sバージョンに暗号化されたファイルか、暗号化されていないファイルかに注意してください。これらがいづれも暗号化されたファイルである場合、それらを同じキーで暗号化しなければなりません。

そして最後にGenerateボタンをクリックします。ファイル生成が完了したときに、OKをクリックしてメインに戻ってください。SPIシリアルフラッシュにファイルをプログラムするには、ツールバーで単にGOボタンをクリックします。

電源起動時にPROGRAMNピンがトグルされると、或いはJTAGリフレッシュ命令が発行されると、LatticeECP2/MはSPIシリアルフラッシュからプライマリ・ファイルを読み出します。もしCRCエラーが見つかると、LatticeECP2/Mは自動的にリブートし、プライマリ・ファイルの代わりにゴールデン・ファイルからのコンフィギュレーション・データを読み出します。ゴールデン・ファイルの中で誤りが見つかると、LatticeECP2/MはINITNピンをLowにドライブし、コンフィギュレーションしようとするのやめることに留意してください。

ここで特定されたフローはSPIシリアルフラッシュの最初のプログラミングに対してであることに注意してください。SPIシリアルフラッシュのフィールド・アップデートの時、ゴールデン・ファイルではなく、プライマリ・コンフィグレーション・ファイルだけをアップデートすると想定しています。これは重要で、なぜなら正常であることがわかっているコンフィグレーション・ファイルを得られることを保証するためです。

#### 図15-6 SPIm、デュアルコンフィグレーション・イメージ

Note: The CSSPI1N pin should not be connected

#### SPIシリアルフラッシュのプログラミング

LatticeECP2/MはJTAGがSPIポートにアクセスできる専用のハードウェアを含んでいます。これによりボード上にある場合でも、ispVMや、組み込みハードウェア、またはATE機器からフラッシュをプログラムすることを可能にします。JTAGを用いてSPIシリアルフラッシュをプログラムするためには、SPIかSPImモードにCFGピンを設定しなければなりません(表15-3を参照)。詳しい情報についてはispVMのヘルプを参照してください。

# スレープシリアル・モード

スレーブシリアル・モードではCCLKピンは入力になり、入って来るクロックを受け取ります。デバイスは CCLKの立ち上がりエッジでDIのデータを受け入れます。スレーブシリアルではFPGAへの書き込みだけをサポートし、FPGAから読み出しはサポートしません。

LatticeECP2/M 15-14 sysCONFIG UGJ

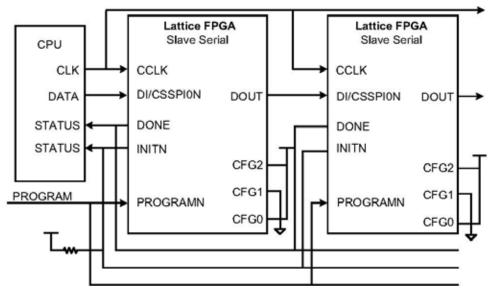

デバイスのコンフィグレーションが完了し、バイパス・オプションが設定されていると、DIに送られたデータは図15-7に示されるようにDOUTピンに出され、次のデバイスに送られます。

### 図15-7 シリアルモードのデイジーチェイン

注: スレーブシリアル・モードでは、LatticeECP2/M Sシリーズデバイスに暗号化されたビットストリーム・ファイルを用いるとき、Bypassオプションはサポートされません。暗号化されたビットストリーム・ファイルを用いることに関する詳しい情報についてはLatticeECP2/M S-Series Configuration Encryption Usage Guide (TN1109)を参照してください。

# スレープパラレル・モード

CCLK、CSN、CS1N、およびWRITENピンはホストシステムによってドライブされます。デバイスに書き込むためにはWRITEN、CSN、およびCS1NをLowに保持しなければなりません。データはD[0:7]から入力されます。D0はMSbで、D7はLSbです。

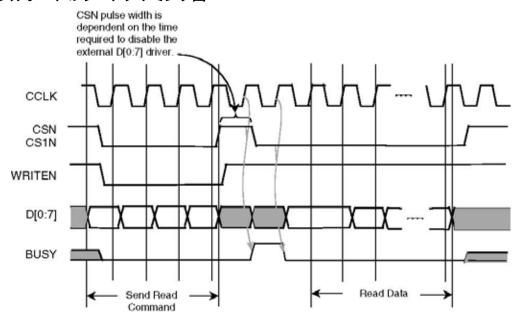

またスレーブパラレル・モードは、内部コンフィグレーションのリードバックのために用いることができます。WRITENピンと、CSN、およびCS1NをLowにドライブすることによって、デバイスにD[0:7]ピン上のリードバック命令を入力します。WRITENがその後Highにドライブされると、D[0:7]にリードデータが出力されます(図15-8)。リードバックをサポートするためには、ispLEVERのデザインプランナでPERSISTENTビットをONに設定しなければなりません。

LatticeECP2/M 15-15 sysCONFIG UGJ

図15-8 パラレルポートのリードタイミング図

ホストはプリアンブルBDB3(16進)を送出し、次にリードコマンドを送ります。LatticeECP2/MはD[0:7]にリードデータを送りますが、必要に応じてデータフローを中断するためにBUSYをHighにドライブします。ビットストリームの例に関しては、表15-7を参照してください。表15-8は種々リードコマンドをリストします。ビットストリーム例とリードコマンドのリストは、ユーザがフローをよく理解する手助けとしての参考であることに注意してください。リードコマンドを含んでいる実際のビットストリームはispLEVERとispVMによって作成され、ホストは制御信号をトグルして、ビットストリームを送ります。

表15-7 パラレルポートのビットストリーム読み出し例

| フレーム       | 内容       | 記 述                           |

|------------|----------|-------------------------------|

|            | 11111111 | 2 ダミーバイト                      |

| ヘッダ        | 10111101 | <br> 2バイトプリアンブル(BDB3)         |

|            | 10110011 | 2//1 ( J J J J J J J ( BDB3 ) |

| ベリファイID    |          | 8バイトのコマンドとデータ                 |

| リセットアドレス   |          | 4バイトのコマンドとデータ                 |

| リードインクリメント |          | 4バイトのコマンドとデータ                 |

表15-8 パラレルポート・リードコマンド

| コマンド       | 32ピットオペコード | 機能                                                        |

|------------|------------|-----------------------------------------------------------|

| リセットアドレス   | 62xx_xxxx  | アドレスレジスタをリセットし、先頭のデータフレームをポイン<br>トする                      |

| リードインクリメント | 01vv_vvvv  | アドレスレジスタで選ばれたコンフィグレーション・メモリフレームをリードバックし、アドレスをポストインクリメントする |

| リードユーザコード  | 03xx_xxxx  | USERCODEレジスタの内容を読みだす                                      |

| リード制御レジスタ0 | 04xx_xxxx  | 制御レジスタ0の内容を読みだす                                           |

| リードCRC     | 06xx_xxxx  | CRCレジスタの内容を読みだす                                           |

| リードIDコード   | 07xx_xxxx  | IDコードを読む                                                  |

| NOOP       | FFxx_xxxx  | ノーオペレーション                                                 |

注; x=don't care (ドントケア), v=variable (変数)

LatticeECP2/M 15-16 sysCONFIG UGJ

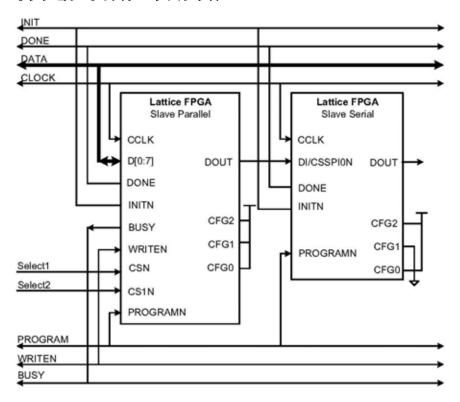

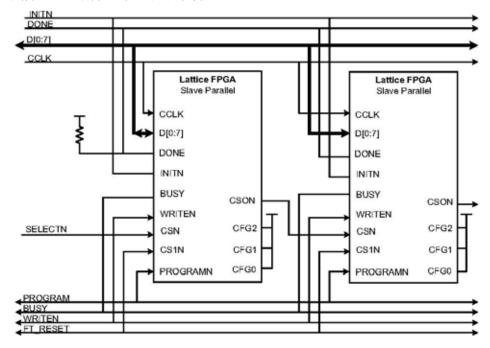

スレーブパラレル・モードは2つのタイプのオーバフロー、バイパスおよびフロースルー、をサポートすることができます。最初のデバイスがコンフィギュレーション・データのすべてを受けた後に、バイパス・コマンドがビットストリームに検出されると、D[0:7]ピンに示されたデータはシリアル化されてDOUTピンにバイパスされます(図15-9を参照)。

バイパス・コマンドでなくフロースルー・コマンドがビットストリームに検出されると、図15-10で示されるように、CSON信号は次段のパラレルモード・デバイスのチップセレクトをLowにドライブします。どちらかのタイプのオーバフローがアクティブであるなら、CSNとCS1Nピンの両方がHighにドライブされるとオーバフローをリセットします。すなわちデバイスはオーバフロー動作から抜けます。

## 図15-9 バイパス・オプションでのスレーブパラレル

注: スレーブパラレル・モードでは、LatticeECP2/M Sシリーズデバイスに暗号化されたビットストリーム・ファイルを用いるとき、Bypassオプションはサポートされません。暗号化されたビットストリーム・ファイルを用いることに関する詳しい情報についてはLatticeECP2/M S-Series Configuration Encryption Usage Guide (TN1109)を参照してください。

LatticeECP2/M 15-17 sysCONFIG UGJ

TN1108\_02.1J Sept. 2008

図15-10 フロースルーでのスレーブ・パラレル

注: スレーブパラレル・モードでは、LatticeECP2/M Sシリーズデバイスに暗号化されたビットストリーム・ファイルを用いるとき、Flow-Throughオプションはサポートされません。暗号化されたビットストリーム・ファイルを用いることに関する詳しい情報についてはLatticeECP2/M S-Series Configuration Encryption Usage Guide (TN1109)を参照してください。

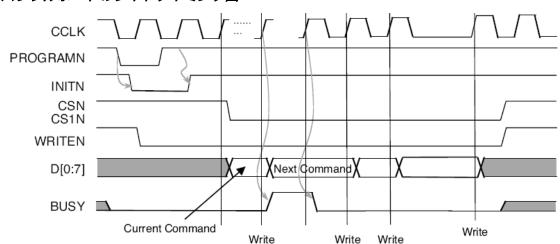

非同期コンフィグレーションは、FPGAが受け取ることができる速度よりも速いレートでホストが送出する場合のために、スレーブパラレル・モードではBUSY信号を用いることができます。BUSY信号をHighにドライブすることでスレーブデバイスはホストに一時的にデータ送出を止めるように知らせます。すべてのデータと制御信号がCCLKと同期していることに注意してください。ここでは非同期という意味はBUSYを用いることでデータ転送を中断・再開する機能を指します。図15-11を参照してください。

図15-11 パラレルポートのライトタイミング図

注: 暗号化されたビットストリーム・ファイルをLatticeECP2/M Sシリーズデバイスにダウンロードするとき、ユーザはCCLK信号に対しての適切な条件を確実に満たなければなりません。これらの

LatticeECP2/M 15-18 sysCONFIG UGJ

条件はLatticeECP2/M S-Series Configuration Encryption Usage Guide (TN1109)に示されています。

コンフィグレーション・ビットストリームをデバイスに入力される間は、CSNとCS1NピンはLowのままにしておかなければなりません。そうでないとコンフィグレーションは失敗します。暫定的にライトアクセスを停止するためにCCLK信号とデータを止めることができます。図15-11はその例を示しています。。

## IspJTAGモード

LatticeECP2/Mは高速プログラム、あるいはIEEE1532モードを用いてispJTAGポートを介してコンフィグレーションすることが可能です。どのコンフィグレーション・モードが選択されてもJTAGポートは常にオンであり、使用可能です。IEEE1532モードはispVMではErase (消去)、Program、Verify (ベリファイ)と呼ばれています。

#### 高速(Fast)プログラム

高速プログラムはJTAGポートを用いるシリアル・コンフィグレーションとして考えることができます。高速プログラムに用いられるデータファイルは、sysCONFIGシリアルモード・コンフィグレーションに用いられるファイルと同じです。言い換えると、ヘッダー、プリアンブル、およびコンフィギュレーション・データがあります。ビットストリームがCRCチェックを含んでいるので、、時間がかかるプログラム後の一ビット毎の検証をする必要がなく、高速プログラムは結果としてより速いコンフィグレーション時間で済みます。また、SVFとVMEファイル形式も、Fastプログラミングをサポートします。

JTAGコンフィグレーションの間、バウンダリスキャン・セルはLatticeECP2/MのI/Oを制御します。バウンダリスキャン・セルは通常、I/Oをトライステート・レベルにドライブしますが、ispVMを用いてこれを制御することが可能で、またカスタマイズすることさえできます。JTAGコンフィグレーションの間、バウンダリスキャン・セルによって制御されるため、PROGRAMN、INITN、およびDONEには意味がないことに留意してください。しかしながら、JTAGコンフィグレーションが完了した後は、INITNとDONEはコンフィグレーション・ステータスを示します。

#### **IEEE 1532**

高速プログラム以外に、JTAGを通してIEEE1532規格を用いることでもLatticeECP2/Mをコンフィギュレーションすることができます。IEEE 1532コンフィグレーション・ファイルはコンフィギュレーション・データと共にJTAG命令を含んでいます。

ispVMのユニバーサル・ファイルライタ (Universal File Writer; UFW) を用いることでISC、SVF、および VMEを含むIEEE 1532ファイルを生成することができます。これらのファイルはispVMやサードパーティ ATE機器で用いることができます。またボード上のプロセッサがJTAG信号を制御してデータを供給するような、組み込み状態でもこれらのファイルを用いることができます。これはispVMエンベデッド(Embedded) と呼ばれます。ispVMのヘルプで詳しい情報を見つけることができます)。IEEE 1532プログラミングは高速プログラム・モードよりも遅いですが、これはプログラミング後の一ビット毎の検証を必要とするためです。

JTAGコンフィグレーションの間、バウンダリスキャン・セルがLatticeECP2/Mの I/Oを制御します。バウンダリ・スキャンセルは通常、I/Oをトライステート・レベルにドライブしますが、ispVMを用いてこれを制御することが可能で、またカスタマイズすることさえできます。JTAGコンフィグレーションの間、バウンダリスキャン・セルによって制御されるため、PROGRAMN、INITN、およびDONEには意味がないことに注意してください。しかしながら、IEEE 1532コンフィグレーションが完了した後は、DONEピンはコンフィグレーション・ステータスを示します。

LatticeECP2/M 15-19 sysCONFIG UGJ

## トランスペアレント・リードバック

ispJTAGトランスペアレント・リードバック・モードで、デバイスが機能している状態にあっても、ユーザはデバイスの内容を読むことができます。I/Oと非JTAGコンフィグレーション・ピンはトランスペアレント・リードバックの間、アクティブなままです。デバイスはJTAG命令を通してトランスペアレント・リードバック・モードに入ることができます。ユーザは、内部ロジックがEBRや分散RAMにアクセスしている時に、トランスペアレント・リードバックがこれらのリソースに同時にアクセスしないことを保証しなければなりません。そうでなければRAMの内容が壊れるかもしれません。

## バウンダリスキャンとBSDLファイル

ラティスセミコンダクターのウェブサイトにLatticeECP2/M BSDLファイルがあります。バウンダリ・スキャンリングは、すべてのI/Oピン、専用のおよびデュアル用途のsysCONFIGピンをカバーします。PROGRAMN、CCLK、およびCFGピンは観測のみ(BC4、JTAGリードオンリ)のバウンダリ・スキャンセルであることに留意してください。

## コンフィグレーション・オプション

各コンフィグレーション・モードで複数のコンフィグレーション・オプションが利用できます。

- ・複数のFPGAデバイスをチェインにする場合、シリアルとパラレルのコンフィグレーション・モードのためにオーバフロー・オプションが提供されます。

- ・SPIかSPImモードを用いる場合、マスタクロック周波数を設定することができます。

- ・RAMリードバックを防ぐようにセキュリティ・ビットを設定することができます。

- ・ビットストリームを圧縮することができます。

- ・パーシスタンス (PERSISTENT) オプションを設定することができます。

- ・コンフィグレーション・ピンを保護することができます。

- ・DONEピン・オプションを選択することができます。

ラティス・デザインソフトウェアで適切なパラメータを設定することによって、選択されたコンフィグレーション・オプションが生成され、ビットストリームにセットされます。ビットストリームがデバイスにロードされるときに、選択されたコンフィグレーション・オプションは有効になります。これらのオプションは以下のセクションで説明されます。

#### バイパス (Bypass) オプション

バイパス・オプションはispLEVERのBitgenプロパティでセット可能ですが、ispVMを用いてビットストリームのチェインを構成したりBypassを設定もできます。バイパス・オプションは、パラレルおよびシリアル・デバイス・デイジーチェーンで用いられます。SPImコンフィグレーションを用いる場合はバイパスオプションはサポートされません。

先頭デバイスのコンフィグレーションが完了し、バイパス・コマンドがビットストリームとして入力されると、FPGAのコンフィグレーション・ポートに入力されるデータはシリアルにDOUTから出力され、次のデバイスのDIに渡されます。(チェインの下流にあるデバイスはスレーブシリアルに設定されなければなりません。)

シリアル・コンフィグレーション・モードでは、バイパス・オプションはバイパス・レジスタを経由してDIをDOUTに接続します。バイパス・レジスタはコンフィグレーションの始めに 1 で初期化され、バイパス・コマンドが実行されるまでその値を保持します。

パラレル・コンフィグレーション・モードでは、バイパス・オプションはD[0:7]に入って来たデータを、バ

LatticeECP2/M 15-20 sysCONFIG UGJ

イパス・レジスタを経由してシリアルにDOUTにシフトアウトします。バイト幅データのD0が最初にシフトアウトされ、D1、D2が続きます。一度バイパス・オプションが開始されると、デバイスはウェイクアップ・シーケンスが完了するまでバイパス状態のままになります。パラレルモードでバイパス・オプションから抜ける1つの方法はCSNとCS1Nを共にHighにすることで、これはバイパスリセットとして機能します。

#### フロースルー (Flow-Through) オプション

バイパス同様、ソフトウェアのBitgenプロパティにフロースルーを見つけることができます。フロースルー・オプションはパラレルのデイジーチェインだけで用いることができます。SPImコンフィグレーションを用いるとき、フロースルー・オプションはサポートされません。LatticeECP2/M Sシリーズデバイスに暗号化されたビットストリーム・ファイルを用いるとき、フロースルー・オプションはサポートされません。暗号化されたビットストリーム・ファイルを用いることに関する詳しい情報についてはTN1109 (LatticeECP2/M S-Series Configuration Encryption Usage Guide)を参照してください。

最初のデバイスがコンフィグレーションを完了して、フロースルー・コマンドがビットストリームから入力されるとき、CSONピンはLowにドライブされます。また、CSONをLowにドライブすることに加えて、他のデイジーチェインされたデバイスとのコンテンションを避けるために、フロースルーはデバイスのD[0:7]とBUSYピンをトライステートにします。フロースルー・オプションがいったん始まると、デバイスはウェイクアップ・シーケンスが完了するまでフロースルーのままです。フロースルーを中止する必要がある場合、CSNとCS1Nの両方をHighにドライブします。これがフロースルー・リセット信号として動作します。

#### マスタクロック

CFGピンがSPIかSPImモードを示す場合、CCLKピンはユーザによって設定された周波数の出力になります。デフォルトのマスタクロック周波数は2.5MHzです。サポートしているマスタクロック周波数の全リストに関しては、Lattice ECP2/Mファミリ・データシートを参照してください。Lattice ECP2/M Sシリーズデバイスを用いるとき、選択できる周波数はデータシートに示されるように制限されます。

ユーザはispLEVERのデザインプランナ内でMCCLK\_FREQグローバル・プリファレンスを設定することで、マスタクロック周波数を変更できます。コンフィグレーションの最初にロードされることの一つはMCCLK\_FREQパラメータで、これが読まれるとグリッチを生成しないようなスイッチで周波数が切り替えられます。注意しないといけないことは、スレーブデバイスの周波数仕様を超えないことや、PCBのレイアウトによる信号インテグリティを損なわないことです。

コンフィグレーション時間は表15-4に示される最大コンフィグレーション・ビットサイズをマスタクロック 周波数で割ることで求められます。

#### セキュリティ・ビット

CONFIG\_SECUREオプションをONに設定すると、JTAGやsysCONFIGピンからSRAMのリードバックを防ぎます。CONFIG\_SECUREがONに設定されるとき、利用できる唯一の動作は消去と書き込みです。SRAMコンフィグレーションの最後の動作としてセキュリティ・ヒューズをアップデートします。安全にされたデバイスが読み出されると、それはゼロのみを出力します。

LatticeECP2/MデバイスではCONFIG\_SECUREオプションはispLEVERのデザインプランナを通してアクセスでき、デフォルトはOFFです。

LatticeECP2/M Sバージョンデバイス(品番ECP2S、ECP2MS)ではCONFIG\_SECUREオプションは ispLEVERのプロジェクトナビゲータの**Tools**メニュー下にある**Security Settings**オプションを通してアクセスできます。

LatticeECP2/M 15-21 sysCONFIG UGJ

## ビットストリームの圧縮

ispLEVERのデザインプランナのグローバルな設定であるCOMPRESS\_CONFIGオプションをONにすると、 圧縮されたビットストリームを生成します。ビットストリームがデバイスに入力されるとき、LatticeECP2/M は自動的に伸張します。ビットストリームの圧縮前データパターンに従って、実際の圧縮後のサイズは異な ります。ありそうもないのですが、圧縮されたビットストリームが圧縮前より大きいことは、理論的にあり 得ます。

ビットストリームを圧縮すると、より速いコンフィグレーションをもたらすことができます。デフォルト設定はOFFです。

#### パーシスタント・オプション

PERSISTENTオプションはispLEVERのデザインプランナを用いて設定されます(デフォルトはOFFです)。 PERSISTENTは2つの目的を持っています。

PERSISTENTをONに設定すると、sysCONFIGピン(DI以外のデュアル・ファンクション・ピンのすべて)に関連するパラレルポートのいずれも用いないようにソフトウェアの配置配線ツールに指示します。

またPERSISTENTがONだとハードウェア・ヒューズも設定されます。従って、単にピンがソフトウェアで 予約されるのでではなく、またそれらはハードウェアでリザーブされます。

スレーブパラレル・ポートを用いてユーザがSRAMコンフィグレーション・メモリを読み出す必要がある場合にだけ、PERSISTENTはONに設定されます。パラレルポートを用いるて読み出しを実行するために、ユーザは最初にリードコマンドを送らなければなりません。PERSISTENT=ON設定でユーザモード(DONEピンはHigh)においても、パラレルポートからのこのコマンドを受付ることができます。デザインがこの機能を必要としないなら、PERSISTENTオプションはOFFに設定されるべきです。

デバイスがユーザモードにあるとき(DONEピンがHigh)に、SPIポートを介してSPIメモリをアクセスする必要がある場合、SPIポートピンを確保するためにPERSISTENT制約を与えなければなりません。

#### コンフィグレーション・モード

CFGピンの設定がハードウェア的にどのポートからコンフィグレーションするかを決めるように、CONFIG\_MODEオプションがソフトウェアにどのポートを使用するかを通知します。CONFIG\_MODEはユーザがsysCONFIGピンを使用できるようにします。例えば、CONFIG\_MODEをSPIにすると、SPI用のピンを汎用IOとして使用しないようにします。しかしながら、ユーザはそれでも汎用IOとしてアサイン可能で、この場合注意を促すためウォーニングが生成されます(コンフィグレーション・ピン関係の記述を参照)。

選択できるオプションはNone、JTAG、SPI、SPIm、Slave Serial(スレーブシリアル)、そしてSlave Parallel(スレーブパラレル)です。デフォルトはSlave Serialです。

### DONE\_OD、DONE\_EX

コンフィグレーション中、DONEピンはLowです。コンフィグレーションが完了すると、内部Doneビットがセットされ、ウェイクアップ・シーケンスが開始され、DONEピンはHighになります。殆どの環境ではこのフローがまさに必要なことですが、もし複数のデバイスが同一チェインにある場合、全デバイスのウェイクアップを同期させるためにウェイクアップ・シーケンスの開始を遅らせることが望ましいかもしれません。デザインプランナにはこの同期を可能にするオプションがあります。

DONE\_ODはデフォルトがONで、これによりオープンドレイン・ピンとしてDONEピンを構成します。複数のDONEピンを接続する場合はオープンドレインにすべきですが、市あごのデバイスはDONEピンはアクティブ・ドライブにしたほうが良いかもしれません。DONE\_ODをOFFにするとDONEピンはアクティブ・ドライブになります。

LatticeECP2/M 15-22 sysCONFIG UGJ

DONE\_EXはデフォルトがOFFです。ONにするとLatticeECP2/MはDONEピンをサンプルし、外部敵にDONEピンがLowにドライブされていると、ウェイクアップ・シーケンスの開始を遅らせます。デフォルトでは内部Doneビットがセットされると直ちにシーケンスを開始します。

# デバイスのウェイクアップ

コンフィグレーションが完了すると、デバイスは予測できるやり方でウェイクアップされるべきです。コンフィグレーションが成功しエラーがないとウェイクアップが始まり、コンフィグレーション・モードからユーザモードに移行する手順を与えます。ウェイクアップ・プロセスは内部Doneビットがセットされると開始されます。

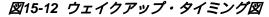

表15-8はLatticeECP2/Mデバイスによってサポートされるウェイクアップ・シーケンスのリストで、図15-12がタイミングを示します。

表15-9 ウェイクアップ・オプション

| シーケンス      | フェーズT0 | フェーズT1          | フェーズT2          | フェーズT3          |

|------------|--------|-----------------|-----------------|-----------------|

| 1          | DONE   | GOE, GWDIS, GSR |                 |                 |

| 2          | DONE   |                 | GOE, GWDIS, GSR |                 |

| 3          | DONE   |                 |                 | GOE, GWDIS, GSR |

| 4          | DONE   | GOE             | GWDIS, GSR      |                 |

| 5          | DONE   | GOE             |                 | GWDIS, GSR      |

| 6          | DONE   | GOE             | GWDIS           | GSR             |

| 7          | DONE   | GOE             | GSR             | GWDIS           |

| 8          |        | DONE            | GOE, GWDIS, GSR |                 |

| 9          |        | DONE            |                 | GOE, GWDIS, GSR |

| 10         |        | DONE            | GWDIS, GSR      | GOE             |

| 11         |        | DONE            | GOE             | GWDIS, GSR      |

| 12         |        |                 | DONE            | GOE, GWDIS, GSR |

| 13         |        | GOE, GWDIS, GSR | DONE            |                 |

| 14         |        | GOE             | DONE            | GWDIS, GSR      |

| 15         |        | GOE, GWDIS      | DONE            | GSR             |

| 16         |        | GWDIS           | DONE            | GOE, GSR        |

| 17         |        | GWDIS, GSR      | DONE            | GOE             |

| 18         |        | GOE, GSR        | DONE            | GWDIS           |

| 19         |        |                 | GOE, GWDIS, GSR | DONE            |

| 20         |        | GOE, GWDIS, GSR |                 | DONE            |

| 21 (デフォルト) |        | GOE             | GWDIS, GSR      | DONE            |

| 22         |        | GOE, GWDIS      | GSR             | DONE            |

| 23         |        | GWDIS           | GOE, GSR        | DONE            |

| 24         |        | GWDIS, GSR      | GOE             | DONE            |

| 25         |        | GOE, GSR        | GWDIS           | DONE            |

LatticeECP2/M 15-23 sysCONFIG UGJ

### ウェイクアップの同期

デバイスが他のデバイスに対してどのようにウェイクアップするかどうかの選択と共に、ウェイクアップ・シーケンスの内部クロックソースを選ぶことができます。

# ウェイクアップ・クロックの選択

ウェイクアップ・シーケンスはユーザ選択可能なクロックソースと同期します。クロックソースは、 External(外部:デフォルト)とUser Clock (ユーザクロック)です。

Externalが選択されると、LatticeECP2/Mはウェイクアップ・シーケンスの間、コンフィグレーション・データのソースによって、2つのクロックの1つを用いるでしょう。LatticeECP2/MがJTAGからのコンフィギュレーションであるなら、JTAGのTCKがウェイクアップ・シーケンスに用いられるでしょう。コンフィギュレーション・データがsysCONFIGポート(シリアル、パラレル、またはSPI)から入力される場合、CCLKが用いられるでしょう。

Userが選択されるとき、デザインのクロック信号のいずれでもクロックソースとして用いることができます。

#### 内部Doneビットに同期

LatticeECP2/Mがコンフィグレーション・チェーンにおける唯一のデバイス、またはチェインで最後のデバイスである場合、DONE\_EXはデフォルト値(OFF)に設定されるべきです。ウェイクアップ・プロセスはコンフィグレーションが無事終了したときに、内部Doneビットがセットされると開始されます。

## 外部DONEピンと同期

ウェイクアップをコンフィグレーション・チェーンにある他のデバイスと同期させるためにDONEピンを用いることができます。DONE\_EXがON(上のDONE OD、DONE EXセクション)の場合、DONEピンは双方向ピンです。外部デバイスがDONEピンをLowにドライブすると、ウェイクアップ・シーケンスは遅らせられます。コンフィグレーションは完了することができますが、ウェイクアップは遅れます。DONEピンがいったんHighになると、デバイスは選択されたWAKE\_UPシーケンスに従います。

コンフィグレーション・チェーンで、(図15-2のように)全デバイスが同一ソースからのコンフィギュレーションである場合、最後のデバイスがコンフィグレーションを終えるまでデバイスのすべてのウェイクアップを遅らせることが通常望ましいか、または必要でさえあります。これは最後のデバイスをDONE ODとDONE\_EXを共にOFFに設定すし、一方で、他のデバイスはDONE\_ODとDONE\_EXを共にONに設定して達

LatticeECP2/M 15-24 sysCONFIG UGJ

成します。

## ウェイクアップ・シーケンス・オプション

表で示されるウェイクアップ・シーケンス・オプションは3つの内部信号、GSR、GWDIS、およびGOE、そして1本の外部信号(DONE)の適用順序を決定します。

- ・GSRは、デバイスのコアをセット・リセットするために用いられます。GSRはコンフィグレーションの間アサートされて(Low)、ウェイクアップ・シーケンスでネゲートされます(High)。

- ・GWDISがLowであると、デバイス内のRAMブロックとLUTを保護します。この信号はデバイスがウェイクアップする前にはLowです。

- ・GOEがHighの場合、デバイスのI/Oバッファがピンをドライブするのを防ぎます。

- ・DONEピンがHighの場合、コンフィグレーションが終了して、誤りが全く検出されなかったことを示します。

DONE\_EXがOFFである場合、シーケンス21がデフォルトですが、ユーザは8~25までどのシーケンスも選択することができます。DONE\_EXがONの場合デフォルト・シーケンスは4ですが、ユーザは1~7のシーケンスを選択することができます。

# コンフィグレーションFAQ

ここに、デバイス・コンフィグレーションに関する、より一般的な質問がいくつかあります。

## 全般

#### Q. JTAG以外に、最も安価なコンフィグレーションの方法は何ですか?

A. プロセッサと付加的な記憶領域(素子)がボード上に既にある場合、コンフィギュレーション・データをLatticeECP2/Mに与えるのにプロセッサを用いることができます。最も安価なスタンドアロンのコンフィグレーション・オプションはSPIシリアルフラッシュです。

# Q. 私はピットストリームを作成しましたが、次にLatticeECP2/Mにどのようにピットストリームをロードするのでしょうか?

A. 無料のツール、ラティスispVM ( www.latticesemi.comから)、およびラティスispDOWNLOADケーブルを用いてください。

## Q. JTAGを用いてLatticeECP2/MのデバイスIDを読み出すことができません。何が問題でしょうか?

A. これは最も基本的なJTAG操作です。デバイスにIDを読み出すことに問題があるということは、何か基本的な問題があります。JTAG接続が正しいこと、 $V_{CCJ}$ とダウンロード・ケーブルの $V_{CC}$ が正しい(同じ)であることをチェックしてください。XRESピンが10Kの抵抗を通してグランドに接続されていることを確認してください。すべての $V_{CC}$ とグランド・ピンが適切に接続されるかどうかをチェックしてください。JTAG信号の上に雑音がないかどうかチェックしてください。時々適切にグランド処理されたオシロスコープのプローブをTCKに触れると、現象が変わることがあります。もしそうだとすれば、信号線への雑音という問題があります。 $V_{CC}$ ピン上に過度の雑音がないかどうかチェックしてください。

#### Q. デバッグをより簡単にするボード設計として何かできることはありますか?

A. コンフィグレーション専用ピン、PROGRAMN、INITN、DONE、およびCCLKのテストポイントをアクセスしやすい外部に持って来てください。

LatticeECP2/M 15-25 sysCONFIG UGJ

# Q. PROGRAMN、INITN、またはDONEピンに外部プルアップ抵抗は必要ですか?

A. これらの信号のすべてには、内部に弱いプルアップがあります。しかしながら、雑音のある環境であるとか、または幾つかのデバイスがこれらのピンに接続されている場合、これら信号に10Kのプルアップ抵抗を付加することを推奨します。

# Q. コンフィグレーションの問題についてどうすれば支援を得られますか?

A. ispVMのオンラインアシスタント (On-line Assistant) 機能を用いてください。ヘルプメニューの下でそれを見つけることができます。

## モード特有の事項

#### SPI / SPIm

### Q. SPIシリアルフラッシュが既にボード上にあるとき、どのようにすればプログラムできますか?

A. 本書に示されているようにSPIシリアルフラッシュをLatticeECP2/Mに接続してください。次にフラッシュにビットストリームをプログラムするために、ispVMおよびラティスispDOWNLOADケーブルをJTAGポートに接続して用いてください。

LatticeECP2/MデバイスにはSPIシリアルフラッシュをプログラムするためのJTAG命令があり、これによりプログラミング中にSPIをドライブするクロックであるCCLKにデバイス内部でTCKを接続させます。IspVMを起動後、まづScanボタンをクリックしてJTAGチェインにあるデバイスをスキャンし、次にLatticeECP2/Mデバイスを選択し、その後Edit → Edit Deviceと選択してデバイス情報ウィンドウを開きます。この中でSPI Flash ProgrammingをクリックすることでSPI Serial Flash Deviceウィンドウを開き、デバイスアクセスのオプション設定を行います。SPIフラッシュメモリとプログラムするデータファイルを選択します。

#### Q. SPIフラッシュをLatticeECP2/Mに配線するための何か特別な要件はありますか?

A. フラッシュを正しいピンに接続すること以外は、唯一の提案はCCLKとグランド間に4.7Kのプルダウン抵抗を加えることです。Vccの立ち上がる間、このCCLKをあばれないようにします。

### Q. SPIフラッシュを動作させるのに2.5Vを用いることができますか?

A. 今日すべての " 25シリーズ " のタイプが3.3Vであるので、フラッシュと $V_{CCIO8}$  を3.3Vに接続しなければなりません。

#### Q. "25"タイプ以外のSPIシリアルフラッシュ何か使用できますか。

A. 読み出しのオペコード03hを認識するデバイスだけがLatticeECP2/Mと共に用いることができます。ベンダのリストについて表15-5を参照してください。

#### Q. デザインは小さいので、推奨されるよりも小さい容量のSPIフラッシュを用いてもよいですか?

A. デバイス・ヒューズの状態、それらがデザインの一部であるか否かに関係なく、すべてビットストリームに含まれています。デザインのサイズはビットストリームのサイズに影響しません。

#### シリアル

#### Q. スレープシリアル・モードにフリーラン・クロックを用いることができますか?

A. LatticeECP2/Mは、データに対して常にCCLKの立ち上がりエッジで動作しますので、データ・ビットごとに立ち上がリクロックエッジが一つである必要があります。

LatticeECP2/M 15-26 sysCONFIG UGJ

TN1108\_02.1J Sept. 2008

# Q. シリアルモードのビットストリームは他モードのビットストリームと異なりますか?

A. 16進かバイナリなどの異なったファイルの種類であるかもしれませんが、データは同じです。すべてのsysCONFIGビットストリームは同じです。

# パラレル

Q. プロセッサが適切な制御信号を生成しているにもかかわらず、LatticeECP2/Mがコンフィギュレーションされません。INITNはHighになったままで、DONEはLowのままです。何が問題ですか?

A. DOがMSbで、D7はLSbです。ビットストリーム内の各バイトのビット順を逆にしてみてください。プロセッサを用いることでこれを実行することができます。またはispVMを用いることでビット反転(bit mirror)ファイルを生成することもできます。ラティスはプロセッサを用いることを推奨します。ファイル生成でビット順を反転することを覚えている必要がありません。

# テクニカル・サポート支援

ホットライン: 1-800-LATTICE (North America)

+1-503-268-8001 (Outside North America)

e-mail: techsupport@latticesemi.com インターネット: http://www.latticesemi.com

# 変更履歴(日本語版)

| Rev.# | 日付        | 変更箇所                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.7J1 | June 2007 | 既発行                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.1J  | Jan. 2009 | 1, (p.15-1) 下から第三節から "PROGRAMN" 削除。下から第二節追加 2, (p.15-2) 旧第二節(GPIO)削除。第三節(列記事項の第二)に記述追加 3, (p.15-2, 表15-2) 脚注 2 追加 4, (p.15-3) PROGRAMN項、第二節の最後の文を削除 5, (p.15-4) [1] CCLK 項、第二節、120clock に更新。第四節追加。 [2] Dual Purpose sysCONFIG Pins項に記述追加。 6, (p.15-5) CSN and CS1N 項、第二節に文章追加。 7, (p.15-7) TCK 項、第二節追加。 8, (p.15-8) 表15-4 更新、表15-5 追加。 9, (p.15-9) [1] 第一、第二節追加。 [2] One FPGA, One SPI Flash 項、文章追加。 10, (p.15-17) [1] 図15-11 更新。[2] 最下節追加。 11, (p.15-19) [1] Flow-Through Option 項、第一節に記述追加。 [2] Master Clock 項、第一節に記述追加。 |

|       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

LatticeECP2/M 15-27 sysCONFIG UGJ