# LatticeECP2/M 高速I/Oインターフェイス 使用ガイド

# はじめに

LatticeECP2<sup>TM</sup>およびLatticeECP2M<sup>TM</sup>デバイスは、プログラマブルI/O(PIO)に組み込まれたロジックを用いることで種々のダブル・データレート(DDR)やシングル・データレート(SDR)インターフェイスをサポートします。SDRアプリケーションはクロックの片方のエッジでデータを捕捉しますが、一方DDRインターフェイスはクロックの立ち上がりと立ち下がり両方のエッジでデータを補捉するため、結果として性能を倍にします。LatticeECP2/M I/OにはDDRとDDR2 SDRAMメモリ・インターフェイスをサポートするために専用回路があります。このドキュメントはLatticeECP2/Mデバイスにおいて、一般的なDDRとDDR/DDR2メモリ・インターフェイスが共に実装できる機能をどのように利用するかについて詳細に記述します。

### DDRとDDR2 SDRAMインターフェイス概要

DDR SDRAMインターフェイスはクロックの立ち上がりと立ち下がりエッジの両方でデータを転送します。 DDR2はDDR SDRAMメモリの第二世代です。

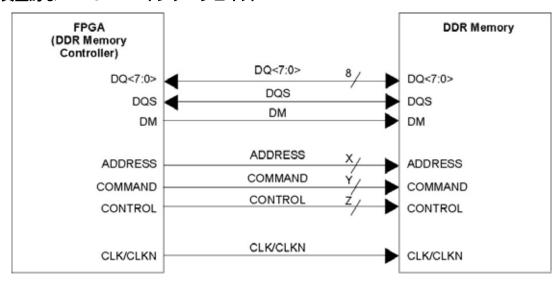

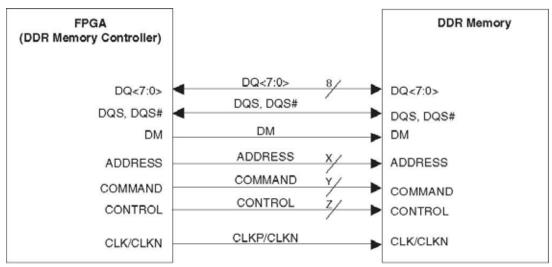

DDRとDDR2 SDRAMインターフェイスは高速動作のためにDQSと呼ぶデータストローブ信号の使用に依存しています。DDR SDRAMインターフェイスはシングルエンドのDQSストローブ信号を用いますが、DDR2インターフェイスは差動DQSストローブを用います。図12-1と図12-2は典型的なDDR / DDR2 SDRAMインターフェイス信号を示します。SDRAMインターフェイスは通常DQS信号あたり8ビットデータで実装されます。16ビットの場合、DQSは2本で、それぞれ8本のDQに関連づけられます。DQとDQSは双方向ポートで、同じ信号線が書き込みと読み出し動作の両方で用いられます。

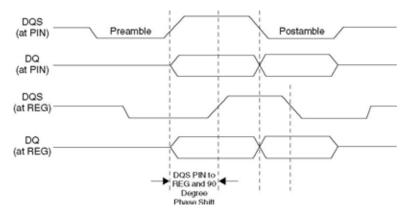

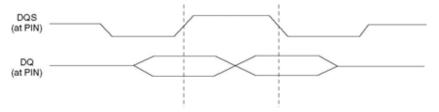

外部メモリデバイスからデータを読むとき、デバイスに入力されるデータのエッジはDQS信号と位相が合わせられています。このDQSストローブ信号は、FPGAロジックがリードデータをサンプルする前に、90度位相シフトされる必要があります。一方DDR SDRAMに書き込む時、メモリ・コントローラ(FPGA)はDQSをデータ信号(DQ)の中央に合わせて出力するために、予め90度シフトしなければなりません。

またクロック信号をメモリに供給します。デューティ比変動を最小にするために差動クロック(CLKPと CLKN)としてこのクロックを提供します。また、メモリは読み出し動作時にメモリ内のDLLによってDQS信号を生成するためにこのクロック信号を用います。図12-3と図12-4は、リード/ライトサイクルのDQとDQSのタイミング関係を示します。他の詳細なタイミング要件については、DDR SDRAM JEDEC仕様(JESD79C)を参照してください。

リードの開始時に、DQS信号はトライステートから抜けた後にある期間Lowです。このステートはプリアンブルと呼ばれます。最後の有効データ転送後、DQSはトライステートに入る前にLowとなり、これはポストアンブル・ステートです。これは最後の有効データの後の遷移期間です。

またDDR SDRAMは、ライトサイクルの間データビットにマスクをかけるためにデータマスク(DM)信号を必要とします。DQS対データビットの比率が全ビット幅から独立していることに注意してください。x8の場合8ビット・インターフェイスには、1本のストローブ信号があります。

DDR SDRAMはSSTL25クラスI / II I/Oインターフェイス規格を用いますが、DDR2 SDRAMはSSTL18クラスI / II I/Oインターフェイス規格を用います。またDDR2 SDRAMは差動DQS (DQSとDQS#)をサポートします。

LatticeECP2/M 12-1 高速 IO I/F UGJ

図12-1 典型的なDDR SDRAMインターフェイス

図12-2 典型的なDDR2 SDRAMインターフェイス

図12-3 / 12-4はメモリリード・メモリライト時のDQとDQSの関係をそれぞれ示します。

図12-3 リード時のDQ-DQS

LatticeECP2/M 12-2 高速 IO I/F UGJ

#### 図12-4 ライト時のDQ-DQS

## LatticeECP2/MデバイスでのDDRメモリ・インターフェイスの実装

DDRSDRAM概要セクションで説明されているように、DDR SDRAMインターフェイスは主として高速動作のためにDQSと呼ばれるデータストローブ信号の使用に依存しています。外部メモリデバイスからデータを読み出すとき、LatticeECP2/Mデバイスに入るデータはDQS信号のエッジにタイミングが合わせられています。したがって、LatticeECP2/Mデバイスは、リードデータをサンプルする為、DQSを用いる前に(90度の)位相シフトさせます。DDR SDRAMに書き込みでは、LatticeECP2/Mデバイス内のメモリコントローラはデータ信号DQの中央にエッジが合わせられたDQS信号を生成しなければなりません。これはDQデータに比してDQSストローブを90度進めることによって達成されます。

LatticeECP2/MデバイスはDQSの適切な位相シフトを生成するための専用DQSサポート回路を持っています。DQS位相シフト回路は、それぞれの専用DQSピンに関連する遅延制御信号を生成するために周波数参照モードのDLLを用います。それは、プロセス、電圧、および温度(PVT)変動を補うように設計されています。グローバルクロック・ピンの1つを通して参照周波数を提供します。

また、専用のDDRサポート回路は、データサンプル・ウィンドウに適切で一貫したマージンを提供するように設計されています。

本セクションは、DDRメモリ・インターフェイスの読み出し・書き込み部分をどのように実装するかを説明します。また、LatticeECP2/Mデバイスに関連するDQとDQSのグループ化規則の詳細も明らかにします。

### DQ-DQSグルーピング

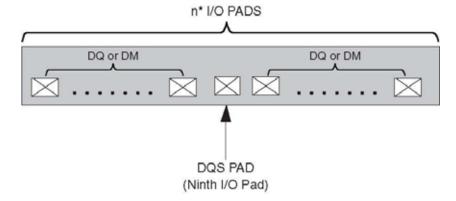

各DQSグループは、完全な8ビットのDDRメモリ・インターフェイスを実装するために、少なくとも10本の I/O (1DQS、8DQ、および1DM)よりなります。LatticeECP2/Mデバイスは、デバイスの下辺、左辺、および右辺の各バンクでDQS信号をサポートします。それぞれのDQS信号はデバイスの下半分のI/Oでは18本にわたって、またデバイスの左右辺のI/Oでは16本にわたってグループ化されています。8ビットDDRメモリ・インターフェイスの実装にDQSのスパンのいづれかを使用できます。

#### 図12-5 DQ-DQSグルーピング

注:下辺バンクでは n=18、左右辺バンクでは n=16

LatticeECP2/M 12-3 高速 IO I/F UGJ

図12-5は典型的なDQ-DQSグループを示します。16 I/Oのグループ(下辺バンク)または14 I/Oのグループ(左右辺バンク)の第9のI/Oは専用DQSピンです。DQSの前にある全8パッドと、後の7パッド(左右辺バンク)或いは9パッド(下辺バンク)にわたってそのDQSバスがカバーします。ユーザは16本のI/Oパッドのうちどの8本でもDQデータピンに割り当てることができます。したがって、32ビット幅のメモリ・インターフェイスを実装するためには、4つのDQ-DQSグループを用いる必要があります。

メモリ・インターフェイスとして使用しないとき、専用DQSピンを汎用I/Oとして用いることができます。これら専用DQSピンはそれぞれ内部でDQS位相シフト回路に接続されています。DQSパッドのピン位置情報はLatticeECP2/Mファミリそれぞれのデータシートに含まれています。表12-1はデータシートから一部を抜き出したものです。

この場合、DQSはLDQS8として記述されています(L=左側、8=関連するPFU行/列)。DQSはDQ-DQSグループで常に第5のTrueパッドであるので、LDQS8はPFU行/列の低い方から数えてPL2AからPL11Bまでをカバーします。ユーザはこれらのI/Oパッドのうちの8本をDQデータピンに割り当てます。

表12-1 EC2-50 672 fpBGA ピン配置 (LatticeECP2/Mファミリ・データシートより)

| ボール番号  | ボール・ファンクション | バンク | デュアル・ファンクション | 差動 |

|--------|-------------|-----|--------------|----|

| D2     | PL2A        | 7   | VREF2_7      | T* |

| D1     | PL2B        | 7   | VREF1_7      | C* |

| GND    | GNDIO       | 7   |              |    |

| F6     | PL5A        | 7   |              | Т  |

| F5     | PL5B        | 7   |              | С  |

| VCCIO  | VCCIO       | 7   |              |    |

| E4     | PL6A        | 7   |              | T* |

| D3     | PL6B        | 7   |              | C* |

| VCC    | VCC         | 7   |              |    |

| E2     | PL7A        | 7   |              | Т  |

| E1     | PL7B        | 7   |              | С  |

| GND    | GNDIO       | 7   |              |    |

| GND    | GND         | 7   |              |    |

| H6     | PL8A        | 7   | LDQS8        | T* |

| H5     | PL8B        | 7   |              | C* |

| F2     | PL9A        | 7   |              | Т  |

| VCCIO  | VCCIO       | 7   |              |    |

| F1     | PL9B        | 7   |              | С  |

| H8     | PL10A       | 7   |              | T* |

| J9     | PL10B       | 7   |              | C* |

| G4     | PL11A       | 7   |              | Т  |

| GND    | GNCIO       | 7   |              |    |

| G3     | PL11B       | 7   |              | С  |

| H7     | PL12A       | 7   |              | T* |

| VCCAUX | VCCAUX      | 7   |              |    |

### **DDRソフトウェア・プリミティブ**

このセクションは、DDRにインターフェイスを実装する際に用いることができるソフトウェア・プリミティブについて説明します。プリミティブとしては以下を含みます。

- DQSDLL DQS遅延較正DLL

- DQSBUFC DQS遅延機能とクロック極性選択ロジック

- INDDRMX1A DDR入力とDQSのシステムクロック転送レジスタへのハーフサイクル転送

- INDDRMFX1A DDR入力とDQSのシステムクロック転送レジスタへのフルサイクル転送

- ODDRMXA DDR出力レジスタ

LatticeECP2/M 12-4 高速 IO I/F UGJ

これら各プリミティブの使用例を本ドキュメント末尾の付録AとBに示しています。

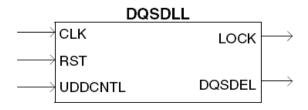

#### **DQSDLL**

DQSDLLは90度位相シフトしたDQS信号を生成します。このプリミティブは、オンチップDQSDLLを実装します。デバイスI/Oの半分で1つのDQSDLLだけがインスタンスされる必要があります(デバイスには計2つのDLLがあります。データシートの図2-34参照)。このDLLへのクロック入力は、DDRインターフェイスと同じ周波数にします。DLLはこの周波数と、このブロックへのアップデート・コントロール(UDDCNTL)入力に基づく遅延を生成します。図12-6はプリミティブ・シンボルを示します。アクティブLowのUDDCNTLはDQS位相調整をアップデートしますが、その動作はリードサイクルのはじめに起動されるべきです。

#### 図12-6 DQSDLLシンボル

表12-2はポートの記述を与えます。

### 表12-2 DQSDLLポート

| ポート名    | I/O | 記 述                                            |

|---------|-----|------------------------------------------------|

| CLK     | I   | FPGAコアからのシステムCLKは、DDRインターフェイスの周波数と同じでなければなりません |

| RST     | I   | DQSDLLをリセットします                                 |

| UDDCNTL | I   | ダイナミック遅延を更新するアップデート信号をDLLに供給します                |

| LOCK    | 0   | DLLが位相ロックしていることを示します                           |

| DQSDEL  | 0   | DLLによって生成されるデジタル遅延情報。DQSBUFCプリミティブに接続されます      |

**DQSDLLアップデートの制御**; PVT変動のためにUDDCNTL入力を用いることでDQS遅延をアップデートすることができます。UDDCNTLがLowに保持されるとDQSDELがアップデートされます。変動が予測されるとき、DQSDELをアップデートすることができます。READサイクル毎にアップデートすることができ、この場合READがアサートされる前に少なくとも1クロック周期アサートされるべきです。

**DQSDLLの構成**:このDLLはその基準入力クロックの周波数に基づいて、DQSを90度位相シフトするための情報をデフォルトで生成します。DLLロック検出回路にはジッタ感度の多少を制御できる2動作モードがあり、LOCK\_SENSITIVITYアトリビュートを用いることによって指定します。このコンフィグレーション・ビットはHIGHもしくはLOWとしてプログラムできます。

DLLロック検出回路はLOCK\_SENSITIVITYビットで制御される2通りの動作モードがあります。DLLが150MHzより高い周波数で動作する場合、LOCK\_SENSITIVITYビットをHighにプログラム(ジッタの感度がより高い)することを勧めます。100MHz未満で動作する場合、本ビットをLowにプログラム(ジッタをより許容)することを勧めます。133MHzでは、LOCK\_SENSITIVITYビットはいずれでも良いでしょう。

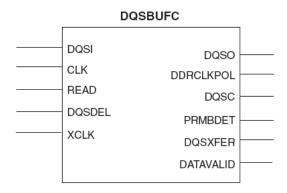

**DQSBUFC**;このプリミティブはDQS遅延とDQS遷移検出ロジックを実装します。図12-7はプリミティブ・シンボルとそのポートを示します。

LatticeECP2/M 12-5 高速 IO I/F UGJ

#### 図12-7 DQSBUFCシンボル

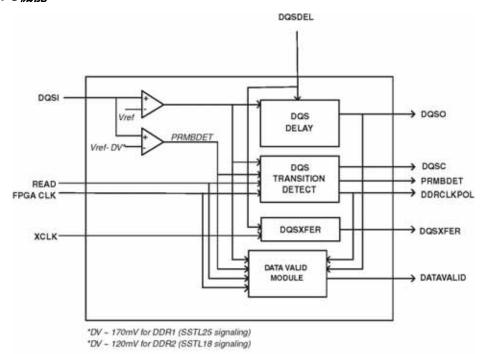

DQSBUFCは図12-8で示されるようにDQS遅延(Delay)、DQS遷移検出(Transition Detect)、およびDQSXFERプロックで構成されます。このプロックはDQSを入力して、それを90度遅らせます。またDDRクロック極性(Clock Polarity)とDQSXFER信号を生成します。プリアンブル検出(PRMBDET)信号は、DQSI入力から電圧分割回路を用いて生成されます。

#### 図12-8 DQSBUFC機能

**DQS遅延プロック**; DQS遅延ブロックは、2つあるDQSDLLブロックの1つから来るデジタル制御遅延線 (DQSDEL)を受け取ります。これらの制御信号は、DQSIを90度遅らせるために用いられます。DQSOは遅延されたDQSであり、初段のDDRレジスタペアのクロック入力に接続されます。

**DQS Transition Detect (遷移検出)**; DQS遷移検出ブロックは最初のDQS遷移時のFPGAクロックとの位相関係に基づくDDR Clock Polarity(クロック極性)信号を生成します。(読み出し動作であることを示す)DDR READ制御信号とFPGA CLK入力はFPGAコアから加えられます

**DQSXFER**;このブロックはDDRライト・インターフェイスのために90度位相シフトされたクロックを生成します。このブロックへの入力はXCLKです。ユーザは、これをエッジクロックかFPGAクロックのどちらに

LatticeECP2/M 12-6 高速 IO I/F UGJ

接続するかを選ぶことができます。DQSXFERは、そのDQSバスがカバーするすべてのI/Oグループに DQSXFERツリーを用いて配線されます。

**Data Valid(有効データ)モジュール;** Data ValidモジュールはDATAVALID信号を生成します。この信号は、有効なデータが入力DDRレジスタからFPGAコアに転送されていることをFPGAに示します。

表12-3はDQSBUFCプリミティブに関連する入出力ポートについて記述します。

### 表12-3 DQSBUFCポート

| ポート名      | I/O | 記 述                         |

|-----------|-----|-----------------------------|

| DQSI      | I   | メモリからのDQS信号                 |

| CLK       | I   | システムCLK                     |

| READ      | I   | FPGAコアから生成される読み出しモードを示す信号   |

| DQSDEL    | I   | DQSDLLプリミティブからのDQS遅延情報      |

| XCLK      | 1   | エッジクロック、またはシステムCLK          |

| DQSO      | 0   | 遅延されたDQS信号。入力キャプチャレジスタブロックへ |

| DQSC      | 0   | 遅延前のDQS。FPGAコアロジックへ         |

| DDRCLKPOL | 0   | DDRクロック極性信号                 |

| PRMBDET   | 0   | プリアンブル検出信号。FPGAコアロジックへ      |

| DQSXFER   | 0   | 90度シフトされたクロック。DDRレジスタブロックへ  |

| DATAVALID | 0   | FPGAコアへのデータが有効であることを示す信号    |

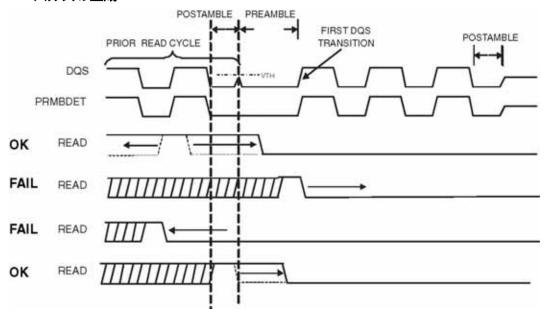

#### READパルスの生成

DQSBUFCブロックへのREAD信号はFPGAコア内部で生成する必要があります。READ信号はDDR SDRAM に対して初めに読み出し制御コマンドがアサートされる際にHighにされます。これは、通常DQSプリアンブルに1サイクル先行するはずですが、直前のリードサイクルの後尾のビットと重ね合わされるかもしれません。LatticeECP2/MデバイスのDQS検出回路は、READ信号の立ち下がりエッジがプリアンブル・ステージの間にある必要があります。

CAS遅延値と、FPGAとメモリ・デバイス間の信号一巡遅延値を用いて、DQSのプリアンブル・ステートを検出することができます。READパルスの立ち上がりは、リード・バースト先頭のREADコマンドと同時に起こる必要があり、またプリアンブルがHighになる前にLowになる必要があります。

図12-9はPRMBDET信号に関してREADパルスのタイミング例を示します。

LatticeECP2/M 12-7 高速 IO I/F UGJ

#### 図12-9 READ/(ルスの生成

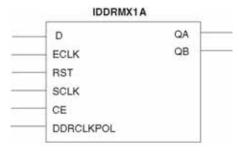

#### IDDRMX1A

このプリミティブは入力レジスタブロックを実装します。DDRレジスタは、I/O側にエッジクロック配線を、FPGA側にプライマリクロックを使用する用に設計されています。ECLK入力は、DQS遅延ブロック(DQSBUFCプリミティブ)から来るDQSストローブに接続します。SCLK入力はシステム(FPGA)クロックに接続します。DDRCLKPOLはDQSクロック極性ツリーからの入力で、ハードウェアのDQS遷移検出回路で生成されます。またこの信号は同期レジスタに供給するSCLKの極性を選択する為に用いられます。

### 図12-10 IDDRMX1Aシンボル

表12-4はIDDRMX1Aプリミティブに関連する全I/Oポートの記述を与えます。

表12-4 IDDRMX1Aポート

| ポート名      | I/O | 記 述               |

|-----------|-----|-------------------|

| D         | I   | DDR データ           |

| ECLK      | ı   | 位相シフトされたDQS入力     |

| LSR       | I   | リセット              |

| SCLK      | I   | システムCLK           |

| CE        | ı   | クロック・イネーブル        |

| DDRCLKPOL | I   | DDRクロック極性信号       |

| QA        | 0   | CLKの立ち上がりエッジでのデータ |

| QB        | 0   | CLKの立ち下がりエッジでのデータ |

注;IDDRMX1AのDDRCLKPOL入力はDQSBUFCのDDRCLKPOL出力と接続します。

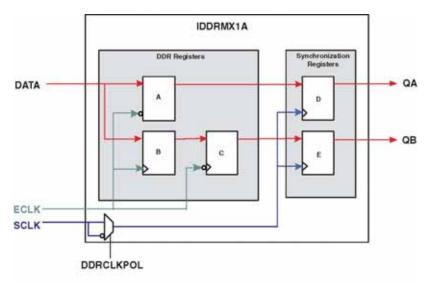

図12-11はIDDRMX1Aモードに構成された入力レジスタブロックを示します。

### 図12-11 IDDRMX1Aモードの入力レジスタブロック

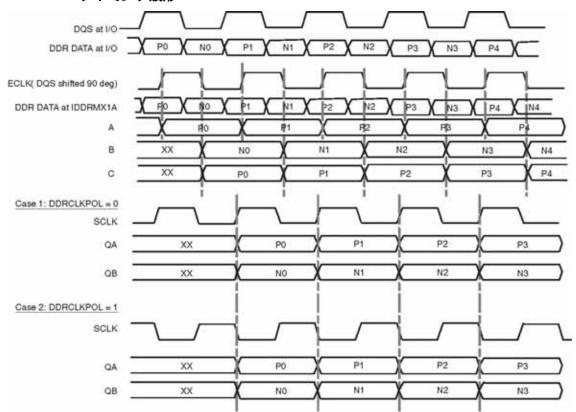

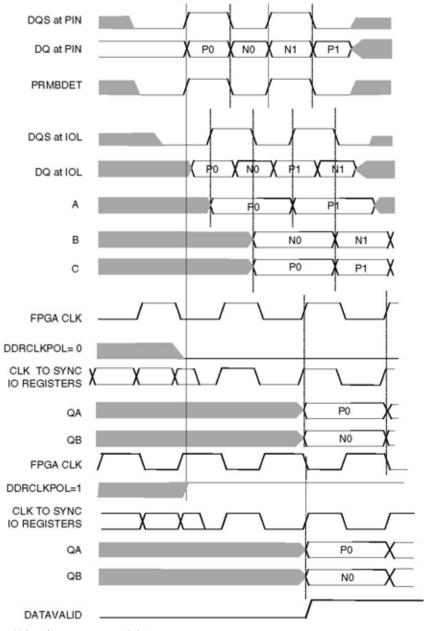

図12-12はIDDRMX1Aタイミング波形を示します。

### 図12-12 IDDRMX1A タイミング波形

LatticeECP2/M 12-9 高速 IO I/F UGJ

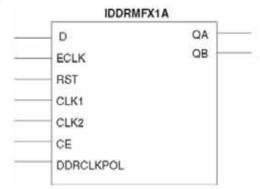

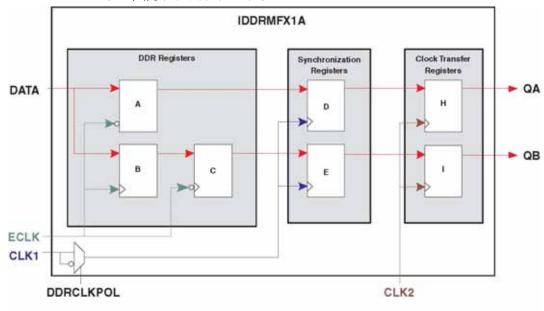

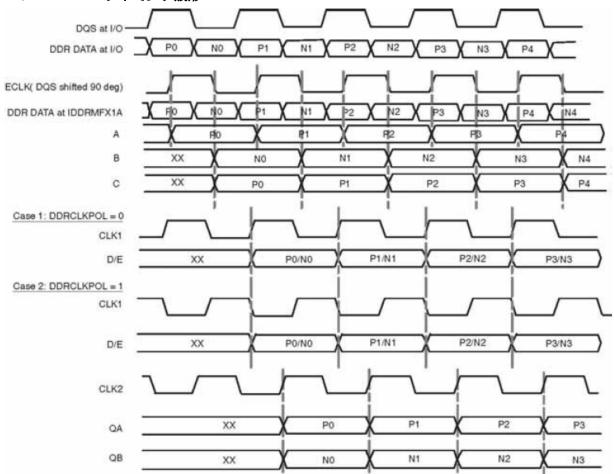

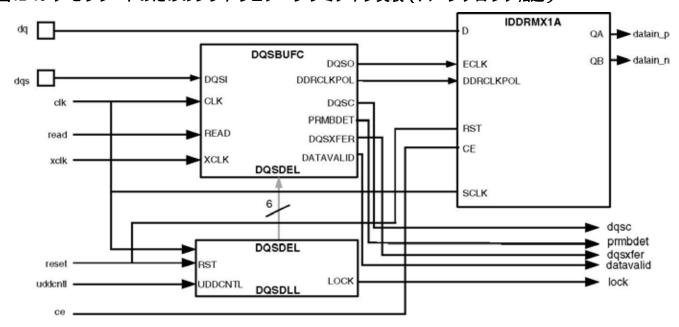

#### **IDDRMFX1A**

IDDRMFX1Aによって、データはDDRCLKPOL信号のステートに依存して、SCLKの立ち上がりか立ち下が リエッジでFPGAに入れることができます。IDDRMFX1Aモジュールは、データがシステムクロックの既知 の (known) エッジで転送されることを確実にする、追加クロック転送ステージを含んでいます。

#### 図12-13 IDDRMFX1Aシンボル

表12-5はIDDRMFX1Aプリミティブに関連する全I/Oポートの記述を与えます。

#### 表12-5 IDDRMX1Aポート

| ポート名      | I/O | 記 述               |

|-----------|-----|-------------------|

| D         | I   | DDR データ           |

| ECLK      | I   | 位相シフトされたDQS入力。    |

| LSR       | I   | リセット              |

| CLK1      | I   | 低速FPGAクロック        |

| CLK2      | I   | 低速FPGAクロック        |

| CE        | I   | クロック・イネーブル        |

| DDRCLKPOL | I   | DDRクロック極性信号。      |

| QA        | 0   | CLKの立ち上がりエッジでのデータ |

| QB        | 0   | CLKの立ち下がりエッジでのデータ |

注;IDDRMX1AのDDRCLKPOL入力はDQSBUFCのDDRCLKPOL出力と接続します。

図12-14はIDDRXMFX1Aモードに構成されたLatticeECP2入力レジスタブロックを示します。

DDRレジスタはI/O側でエッジクロック配線を、FPGA側でプライマリクロックを用いるように設計されています。ECLK入力は、DQS遅延ブロック(DQSBUFCプリミティブ)から来るDQSストローブに接続して用いられます。CLK1とCLK2入力は遅いシステム(FPGA)クロックに接続されるべきです。DDRCLKPOLはDQS Clock Polarity(クロック極性)ツリーからの入力です。この信号はハードウェアのDQS遷移検出回路で生成されます。付加的なクロック転送レジスタは出力レジスタブロックと共有されます。

LatticeECP2/M 12-10 高速 IO I/F UGJ

図12-14 IDDRMXF1Aモードの入力レジスタブロック

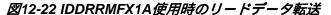

図12-15はIDDRMX1Aタイミング波形を示します。

図12-15 IDDRMX1A タイミング波形

LatticeECP2/M 12-11 高速 IO I/F UGJ

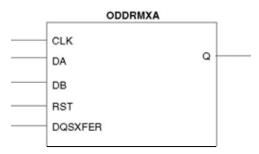

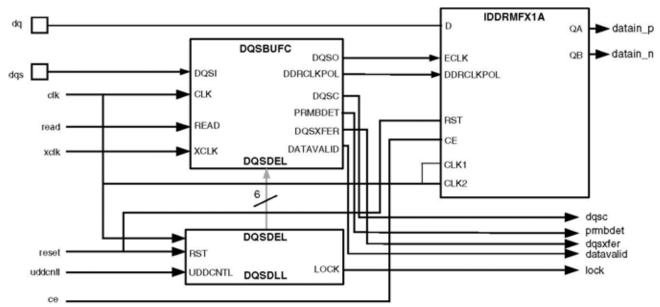

#### **ODDRMXA**

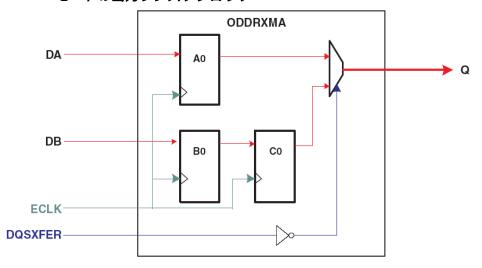

ODDRMXAプリミティブは書き込み機能とトライステート機能を共に実装し、メモリにDDRデータとDQS ストローブを出力するために用いられます。また、すべてのDDR出力トライステート制御も同じプリミティブを用いて生成できます。

図12-16はODDRMXAプリミティブ・シンボルとそのI/Oポートを示します。

#### 図12-16 ODDRMXAシンボル

表12-6はODDRMXAプリミティブに関連する全I/Oポートの記述を与えます。

#### 表12-6 ODDRMXAポート

| ポート名    | I/O | 記 述                         |

|---------|-----|-----------------------------|

| CLK     | I   | システムCLK、またはECLK             |

| DA      | I   | クロックの立ち下がりエッジでのデータ          |

| DB      | I   | クロックの立ち上がりエッジでのデータ          |

| RST     | I   | リセット                        |

| DQSXFER | I   | 90度シフトされたクロック。DQSBUFCプロックより |

| Q       | I   | メモリへのDDRデータ                 |

- 注1. RSTはDDR書き込み動作の間、Lowに保持する必要があります。

- 2. DDR出力レジスタ、トライステート・レジスタでは、CEはサポートされません。RSTはトライステートDDRXモードで利用できます(読み出しの間)。トライステート・モードで用いられると、RSTはデフォルトがセット(High)になります。

- 3. DDR書き込みの間リセットがアサートされても、これはFFをリセットするだけで、ラッチはリセットされないことに留意が必要です。

図12-17はODDRXMAモードに構成された出力レジスタブロックを示します

#### 図12-17 ODDRXMAモードの出力レジスタブロック

LatticeECP2/M 12-12 高速 IO I/F UGJ

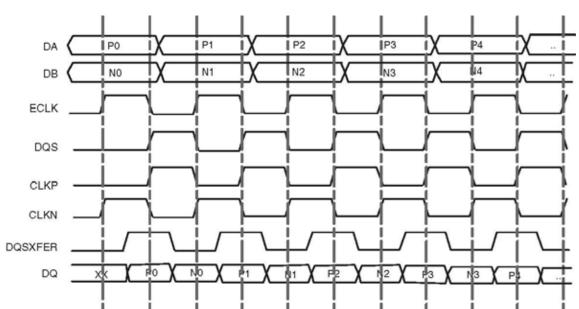

図12-18はODDRXMAタイミング波形を示します。

#### 図12-18 ODDRXMA波形

DQSXFERがODDRXMAの中で反転されることに留意してください。これは、ODDRXMAから出て来るデータがODDRXCモジュールの出力に対して -90°の位相関係をもたらします。

### メモリリードの実装

LatticeECP2/Mデバイスは、DDRインターフェイスの読み出し部分の実装を簡素化する種々の機能を含んでいます。

- DLLで補償されたDQS遅延素子

- DDR入力レジスタ

- システムクロック・ドメインへの転送(乗り換え)回路用の自動DQS

- Data Validモジュール

### DLL補償されたDQS遅延エレメント(Delay Elements)

メモリからのDQSはDQS遅延エレメントに接続されます。DQS遅延ブロックはオンチップDQSDLLから6ビットの遅延制御を受けます。この6ビット遅延線はソフトウェア内では1ビットのモデルになっています。LatticeECP2/Mデバイスには2つのDQSDLL、デバイスの左側と右側にそれぞれ1つ、があります。左側のDQSDLLによって生成されたDQSDELはデバイスの左辺と下辺の半分の全DQSブロックに配線されます。右側のDQSDLLによって生成されたDQSDELは、デバイスの右辺と残りの下辺の全DQS遅延ブロックに分配されます。DQSピンはデバイス上辺のバンクには全くありません。これらのデジタル遅延制御信号は、メモリからのDQSを90度遅らせるのに用いられます。

メモリから受け取ったDQSは各DQS遅延ブロックで遅らせられ、この遅延DQSは、DDR入力レジスタの初段の組のクロックとして用いられます。

DQS Transition Detect(遷移検出)、Automatic Clock Polarity Select(自動クロック極性選択)

リードサイクルの間、典型的なDDRメモリ・インターフェイス設計では、到来する遅れたDQSストローブと内部のシステムクロックとの位相関係は不定です。DDRメモリでは読み出し動作の前に、DQSは(終端抵抗でプルされる)トライステートにあります。トライステートから抜けて、DDRメモリデバイスはDQSをLowにドライブします(プリアンブル)。DQS遷移検出ブロックはプリアンブル遷移後の最初の立ち上がりエッジを検出して、FPGAシステムクロック(DDRCLKPOL)のために必要な極性を示す信号を生成します。この信号は、同期化レジスタ用のクロック極性を制御するために用いられます。

LatticeECP2/M 12-13 高速 IO I/F UGJ

#### Data Validモジュール

Data ValidモジュールはDATAVALID信号を生成します。この信号は、有効なデータが入力DDRレジスタから FPGAコアに転送されていることをFPGAに示します。

#### DDR I/O レジスタの実装

最段のDDRレジスタの組は、位相シフトされたDQSの正のおよび負のエッジを用いてDDRデータをデマルチプレクス(非多重化)します。立ち上がりエッジ動作のレジスタの後に、立ち下がりエッジ動作のレジスタが続きます。このレジスタは、先頭のレジスタからのDQS立ち上がりエッジデータを立ち下がりエッジに変換することで、正負両エッジのデータをDQSの立ち下がりエッジに揃えます。

第二段のレジスタはFPGAクロックが用いられ、このクロックの極性はDQS 遷移検出ブロックによって生成されたDDRクロック極性信号によって選択されます。

I/Oロジック・レジスタは2つのモードで実装することができます。

- ・ハーフクロック転送モード

- ・フルクロック転送モード

ハーフクロック転送モードでは、データは第二段のレジスタの後からFPGAコアに転送されます。フルクロック転送モードでは、データをFPGAコアに転送するために、FPGAクロックによってクロッキングされるもう一段のレジスタが用いられます。

LatticeECP2/Mファミリ・データシートはこれらの回路要素について詳述しています。

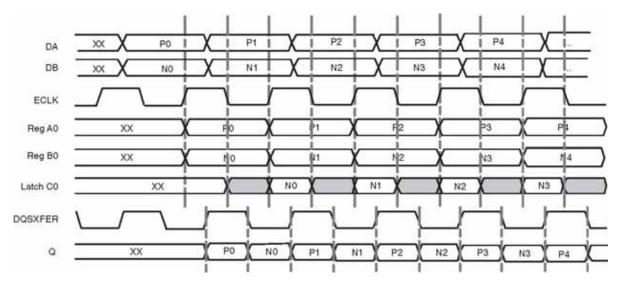

### ソフトウェアにおけるメモリリードの実装

ispLEVERデザインツールの3つのプリミティブがこれら3要素の機能を表わします。DQSDLLはこの較正用に用いられるDLLを意味します。IDDRMX1A/IDDRMFX1AプリミティブはDDR入力レジスタとクロックドメイン転送レジスタを表わします。最後に、DQSBUFCはDQS遅延ブロックとクロック極性制御ロジック、Data Validモジュールを意味します。図12-19、図12-20はispLEVERソフトウェアのIPexpressツールで生成されるメモリインターフェイス・ブロックの読み出し部を示します。

図12-19 メモリリードのためのソフトウェア・プリミティブ実装(ハーフクロック転送)

LatticeECP2/M 12-14 高速 IO I/F UGJ

### 図12-20 メモリリードのためのソフトウェア・プリミティブ実装(フルクロック転送)

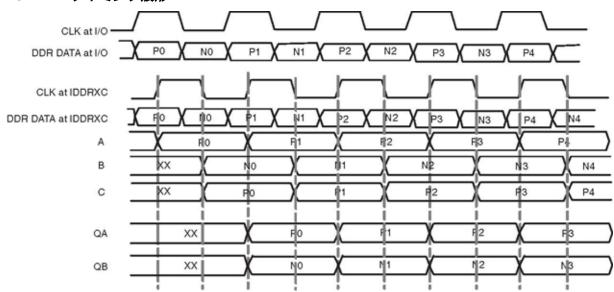

#### リードタイミング波形

図12-19と図12-20はDQS遷移検出器ロジックの結果に基づく2つのケースのリードデータ転送を示します。 この回路は、DQSI(遅延する前のDQS)とシステムクロックCLKの相対的な位相に基づいて、2つの同期レジ スタに与えるFPGAシステムCLKの位相を反転させるかどうかを決めます。

- ケース1: 最初のPRMBDET遷移時にFPGAクロックがLowであるなら、DDRCLKPOLはLowで、FPGA クロックCLKの反転は不要です。

- ケース2: 最初のPRMBDET遷移時にFPGAクロックがHighであるなら、DDRCLKPOLはHighで、FPGA クロックCLKはそれが同期化に用いられる前に反転される必要性があります。

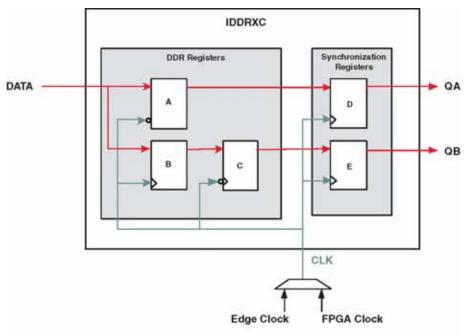

図12-21は、IDDRMX1Aレジスタの異なるステージでハーフクロック転送モードを用いるDDRデータ・タイミングについて図示します。レジスタの初段は、立ち上がりエッジ信号Aを、立ち下がりエッジで信号Bを捕捉します。データストリームAはさらにハーフクロック周期転送を通り信号Cになります。位相が合わせられたデータストリームBとCはFPGAクロックによってクロッキングされる次段のレジスタに送られます。

図12-22はIDDRMFX1Aレジスタの異なるステージでフルクロック転送モードを用いるDDRデータ・タイミングについて図示します。ハーフクロック・モードによる最初の2つのレジスタ・ステージに加えて、フルクロック転送モードはFPGAクロックでクロッキングするレジスタ段がもう一つあります。この場合、DとEは第二段のレジスタ後のデータストリームで、FPGAクロックでクロッキングされる最終段のレジスタに送られます。

LatticeECP2/M 12-15 高速 IO I/F UGJ

- 注 1 DDRメモリがDQSに位相があったDQを送出する。

- 2 専用DQSロジックを用いてDQSが90度遅延される。

- 3 DQの中央にDQSのエッジが合う。

- 4 PRMBDETはDQSBUFCプリミティブで生成されるプリアンブル検出信号で、DDRCLKPOL信号の生成に用いる。

- 5 初段のI/Oレジスタ(AとB)はDQSの立ち上がりと立ち下がりエッジでデータを捕捉する。

- 6 I/OレジスタCにデータを転送し、DQSの立ち下がりエッジにタイミングを揃える。

- 7 DDRCLKPOLがFPGA CLKを反転するかどうかを決定。PRMBDETの最初の立ち上がり時にFPGA CLK=Lowの場合 DDRCLKPOL=0で、同期レジスタへのクロックは反転されない。逆にCLK=High時はDDRCLKPOL=1でクロックは反転される。

- 8 I/O同期レジスタがFPGA CLKの立ち上がり、或いは立ち下がりでデータを捕捉する。

- 9 有効データをFPGAコアに入力時、DATAVALID信号がHighになる。一度アサートされると次のREADパルスが来るまでアサートされたままとなる。

LatticeECP2/M 12-16 高速 IO I/F UGJ

- 注 1 DDRメモリがDQSに位相があったDQを送出する。

- 2 専用DQSロジックを用いてDQSが90度遅延される。

- 3 DQの中央にDQSのエッジが合う。

- 4 PRMBDETはDQSBUFCプリミティブで生成されるプリアンブル検出信号で、DDRCLKPOL信号の生成に用いる。

- 5 初段のI/Oレジスタ(AとB)はDQSの立ち上がりと立ち下がりエッジでデータを捕捉する。

- 6 I/OレジスタCにデータを転送し、DQSの立ち下がりエッジにタイミングを揃える。

- 7 DDRCLKPOLがFPGA CLKを反転するかどうかを決定。PRMBDETの最初の立ち上がり時にFPGA CLK=Lowの場合 DDRCLKPOL=0で、同期レジスタへのクロックは反転されない。逆にCLK=High時はDDRCLKPOL=1でクロックは反転される。

- 8 レジスタDとEがFPGA CLKでデータを捕捉する。

- 9 フルサイクル転送を確実にするため、データはもう一度FPGA CLKを使うレジスタに加えられる。

- 10 有効データをFPGAコアに入力時、DATAVALID信号がHighになる。一度アサートされると次のREADパルスが来るまでアサートされたままである。

LatticeECP2/M 12-17 高速 IO I/F UGJ

### データリードのクリティカルパス

DDRレジスタ第二ステージのデータは、DDRCLKPOL信号のレベルに従って、FPGAクロックの立ち上がり、または立ち下がりエッジでサンプルされます。FPGAコア内のレジスタに転送されるデータが、システムクロックの立ち上がりエッジに合うことを確実にするために、このパスにはハーフクロック(半クロック周期) 転送の制約を与えるべきです。すべての最初のPFUレジスタへのデータパスに対して、ソフトウェアでマルチサイクル制約(0.5xのマルチサイクル)を割り当てることによって、このハーフクロック転送を制約することができます。

### DQSポストアンブル

リードサイクルの終わりで、DDR SDRAMデバイスはリードサイクル・ポストアンブルを出力して、直後にDQとDQS出力ドライバの両方をトライステートにします。その時点でメモリ・コントローラ(FPGA)もDDR SDRAMデバイスもDQやDQSをドライブしていないため(フローティング)、これらの信号はチップ外にある終端抵抗で決定されるレベルになります。これらの信号がフローティングの間にDQSストローブに雑音が乗ると、FPGA入力バッファにとっては有効なストローブ信号と解釈されてしまうかもしれません。そうなると、データをFPGA内のフリーランしている再同期レジスタに転送する前に、IOLの入力DDRレジスタに捕らえられた最後のリードデータは上書きされることになり得ます。

LatticeECP2/Mデバイスには、DQS遅延ブロックに付加的な専用ロジックがあり、このポストアンブル問題を防ぎます。DQSポストアンブル・ロジックは、DQS遅延ロジック(DQSBUFCプリミティブ)を設計にインスタンスすることで、自動的に実装されます。

### メモリライトの実装

DDRメモリ・インターフェイスの書き込み部分を実装するためには、シングル・データレートの2本のストリームデータは、クロックの両エッジで変化するデータとして一本に多重化されなければなりません。さらに、ライトサイクルの間、データDQの中央に合わせられた状態で、DQSはメモリピンに到着しなければなりません。ストローブやデータと共に、インターフェイスのこの部分はメモリへのCLKP、CLKN、アドレス

LatticeECP2/M 12-18 高速 IO I/F UGJ

/コマンド及びデータマスク(DM)信号を提供します。

DDR用出力制御信号(DQとDMを除くADDRとCMD、DQS)を出力差動クロック(CLKP / CLKN)の立ち上がリエッジに合わせる必要があります。

メモリライト期間の困難さは以下によります。

- 1. DDRデータDQの中央にDQSのエッジが合っている必要がある

- 2. 差動CLK信号(CLKPとCLKN)が生成される必要がある

- 3. コントローラはDDRインターフェイス仕様の $t_{DSS}$ と $t_{DSH}$ パラメータを満たさなければならない(DQS 立ち下がりに対するCLKPの立ち上がりエッジのセットアップおよびホールドタイム)

- 4. 2本のSDRストリームから一本のDDRデータストリームにDDR出力データを多重化しなければならない

DDR用出力信号(ADDR、CMD、DQS、DQ、DM)は、初めはFPGAコア内ではCLKの立ち上がりエッジに合わせられています。これら信号の相対位相は、FPGAから出力される前にIOLロジックで調整されます。その様子は図12-24で示されています。

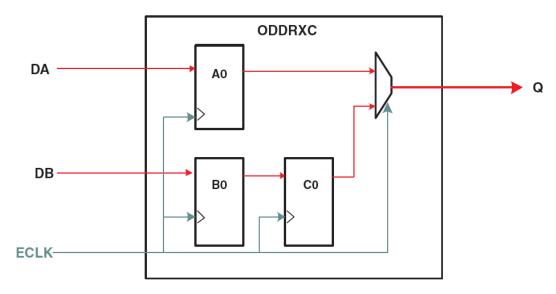

LatticeECP2/Mデバイスは、DQSBUFCによって生成されたDQSXFER信号と共に、DDR出力レジスタとトライステート・レジスタを含んでいます。これがDDRメモリ・インターフェイスの書き込み部分の容易な実装を可能にします。ODDRMXAとODDRXCプリミティブでデザインツールでDDR出力レジスタにアクセスすることができます。

DQS信号とDDRクロック出力は、ODDRXCプリミティブを用いることで生成されます。図で示されるように、CLKPとDQS信号はクロックに同期して180度の位相差であるように生成されます。これはODDRXCプリミティブのDA入力を "1" に、DB入力を "0" に接続することによって行います。ODDRXCタイミング波形については、このドキュメントの汎用DDRソフトウェア・プリミティブ・セクションを参照してください。

次にDDRクロック出力は、CLKPとCLKNの差動クロックを生成するためにSSTL差動出力バッファに加えられます。CLKNをこの様に生成すると、2信号間のスキューを防ぐことになります。DDR1インターフェイスの場合、SDRAMメモリのCLKPはSSTL25D I/O規格で接続されるべきです。DDR2インターフェイスの場合、SDRAMメモリのCLKPはSSTL18D I/O規格で接続されるべきです。

DQSBUFCブロックからのDQSXFER出力は90度位相シフトされたクロックです。このクロックは入力としてODDRMXAブロックで用いられます。ODDRMXAは、メモリへのDQとDM出力を生成するのに用いられます。ODDRMXAモジュールでは、データは最初にECLKかFPGAクロック入力でレジスタに取り込まれ、次にDQSXFER信号を用いてシフトアウトされます。メモリに出力されるデータの中央にDQS位相が合うのを確実にするために、DQSXFERはODDRXMAプリミティブ内で反転されます。これは中央でDQSに合わせられたデータを生成するでしょう。ODDRXMAタイミング波形については、本ドキュメントのソフトウェア・プリミティブ・セクションを参照してください。

DDRインターフェイス仕様の $t_{DSS}$ と $t_{DSH}$ パラメータは、DQS立ち下がりに対するCLKP立ち上がりのセットアップ時間とホールド時間として規定され、これを満たさなければなりません。これはCLKPとDQS信号の位相が確実に同じになるようにすることによって達成されます。

また、DQSとDQ出力のためのトライステート制御をODDRXCプリミティブを用いることで実装することができます。

図12-24はDDRプリミティブを用いるDDRライト・インターフェイスの実装を示します。

LatticeECP2/M 12-19 高速 IO I/F UGJ

ECLK / FPGA Clock DQSXFER (clk+90) CLKP (CLK+180) ODDRXC CLK Q DA CLKN (CLK) .0. DB RST ODDRXC CLK Q dqstri\_p DA dqstri\_n -DB RST ODDRXC DQS (CLK+180) CLK Q 4. DA "0" DB RST **ODDRMXA** CLK Q datatri\_p DA datatri\_n . DB RST DQSXFER DQ (CLK+270) ODDRMXA CLK dataout\_p DA dataout\_n DB RST DOSXFER **ODDRMXA** DM (CLK+270) CLK Q dmout\_p DA dmout\_n \_ DB RST DOSXFER

図12-24 メモリライトのためのソフトウェア・プリミティブの実装

### ライトタイミング波形

図12-25は、DQポートとDQSポートのDDR書き込み側データ転送タイミングを示します。DDRメモリに書き込みする時には、DM(データマスク)とADDR / CMD(アドレスとコマンド)信号がデータとストローブ信号と共にメモリに送られます。

LatticeECP2/M 12-20 高速 IO I/F UGJ

### 図12-25 DQデータのDDRライト・データ転送

### 設計ルール / ガイドライン

以下に記載されているのは、LatticeECP2/MデバイスでDDRメモリ・インターフェイスを実装するときに押さえておきたい幾つかのルールとガイドラインです。

- LatticeECP2/Mデバイスは専用DQ-DQSバンクを持っています。これらのピンをロック(固定)する前に、LatticeECP2/Mデータシートで、グループの論理的な信号接続を確認します。

- デバイスには2つのDQSDLLがあり、それぞれデバイスの左半分用と右半分用です。したがって DQSDLLプリミティブは、デバイスの半分のために1つだけがそれぞれインスタンスされる必要があ ります。デバイスの半分に1つのDQSDLLしかないので、その中にあるすべてのDDRメモリ・イン ターフェイスが同じ周波数で動作する必要があります。各DQSDLLは、DLLへの基準クロック入力に 基づく90度の遅延情報をデジタル遅延ビットとして、該当するデバイス半分の全DQS遅延ブロック に与えます。

- DDR SDRAMインターフェイスを実装する場合、すべてのインターフェイス信号がSSTL25 I/O規格で接続されなければなりません。DDR2 SDRAMインターフェイスの場合は、インターフェイス信号はSSTL18 I/O規格で接続される必要があります。

- DDR2では、差動DQS信号はSSTL18差動I/O規格で接続される必要があります。

- DDRインターフェイスを実装するとき、バンクのV<sub>REF1</sub> は、参照電圧をインターフェイス・ピンに供給するために用いられます。

#### 汎用高速DDRの実装

DDRメモリ・インターフェイスに加えて、ユーザは、高速DDRインターフェイスを実装するのにもI/O LOGIC レジスタを用いることができます。入力DDRレジスタはフルクロック転送とハーフクロック転送モードで動作することができます。またDDR入出力レジスタは、ギアリング比のx1とx2をサポートします。ギアリング機能はI/Oデータ信号のレート(ECLK)をFPGAクロックレート(SCLK)に多重化/非多重化(Mux / Demux)するためにあります。DDRインターフェイスにおいては、この比率はSDRでの比と若干異なっています。基本的な2x DDR要素はFPGA側のクロックレートの半分で、I/O側2ビットに対してFPGA側4ビットを与えます。

DDRレジスタへのデータはDDRレジスタブロックの前で、任意に遅らせることができます。

LatticeECP2/M 12-21 高速 IO I/F UGJ

### 汎用DDRソフトウェア・プリミティブ

DDRモジュールを生成するためにispLEVERソフトウェアのIPexpressツールを用いることができます。以下で説明された様々なDDRモードはIPexpressツールでコンフィギュレーションすることができます。それらモードは以下のソフトウェア・プリミティブを用いることで実装されます。

- ·IDDRXC ~ 汎用DDR入力

- ・IDDRFXA ~ フルクロック転送がある汎用DDR入力(x1ギアボックス)

- ・IDDRX2B ~ 2xギアリング比がある汎用DDR入力。DDRX2には、ダブルデータレート信号を4本のデータストリームとして入力します。2段のDDRレジスタは、入力パッドでシリアルのDDRデータをFPGAコアロジックに入力する4本のSDRデータストリームに変換するために用いられます。

- ・ODDRXC ~ 汎用DDR出力

- ・ODDRX2B ~ 2xギアリング比がある汎用DDR出力。DDRX2は、4本の別々のデータストリームを入力して、I/Oバッファにただ一本のデータストリームを出力します。

- ・DELAYB ~ DDR入力をレジスタに達する前に遅延させるオプションです。ユーザは、固定遅延値を用いるか、またはダイナミック遅延を選んで実装することができます。

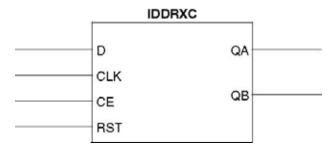

#### **IDDRXC**

このプリミティブはCLKの両エッジでDDRデータを入力して、2本のデータストリームを生成します。この モジュールへのCLKは、エッジクロックかプライマリクロックのどちらかを接続することができます。

図12-26はIDDRXCモードのプリミティブシンボルを示します。

### 図12-26 IDDRXCシンボル

表12-7はIDDRXCプリミティブのポート名と記述をリストします。

#### 表12-7 IDDRXCポート名

| ポート名 | I/O | 記 述                   |

|------|-----|-----------------------|

| D    | I   | DDRデータ                |

| CLK  | I   | ECLKまたはFPGAクロックに接続します |

| CE   | I   | クロックイネーブル             |

| RST  | I   | リセット                  |

| QA   | 0   | クロックの立ち上がりエッジでのデータ出力  |

| Q    | 0   | クロックの立ち下がりエッジでのデータ出力  |

LatticeECP2/M 12-22 高速 IO I/F UGJ

図12-27はIDDRXFCモードに構成された入力レジスタブロックを示します。

### 図12-27 IDDRXCモードの入力レジスタブロック

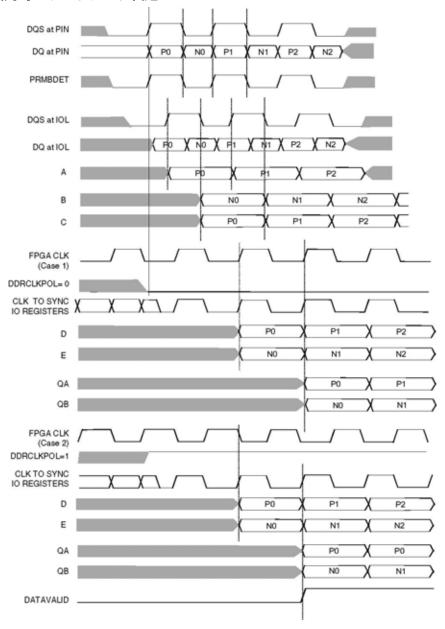

図12-28はIDDRXCモジュールを用いるときのタイミング波形を示します。

#### 図12-28 IDDRXタイミング波形

#### **IDDRFXA**

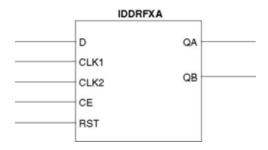

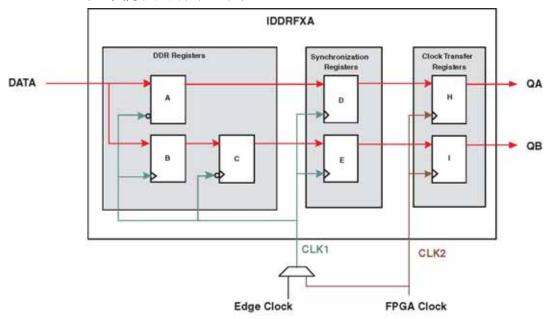

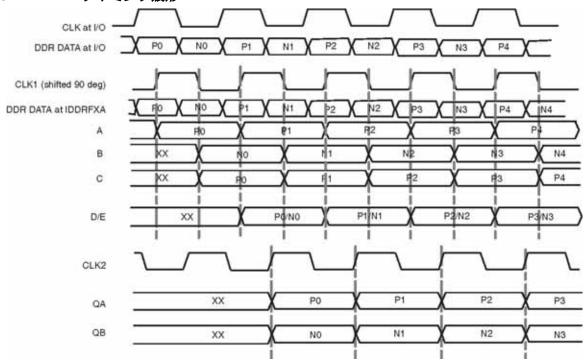

このプリミティブは、クロックCLK1の両エッジでDDRデータを入力して、CLK2のクロックに位相が合った2本のデータストリームを生成します。CLK1はエッジクロックかFPGA内部のクロックに接続することができます。エッジクロック入力がCLK1に用いられるなら、CLK2はCLK1に行く同じクロックから生成されるべきです。図12-29はIDDRFXAモードのプリミティブシンボルを示します。

LatticeECP2/M 12-23 高速 IO I/F UGJ

### 図12-29 IDDRFXAシンボル

表12-8はIDDRFXAプリミティブのポート名と記述をリストします。

### 表12-8 IDDRFXAポート名

| ポート名     | I/O | 記 述                   |

|----------|-----|-----------------------|

| D        | I   | DDRデータ                |

| CLK1     | I   | ECLKまたはFPGAクロックに接続します |

| CLK2     | I   | FPGAクロックに接続します        |

| CE       | I   | クロックイネーブル             |

| RST      | I   | DDRレジスタのリセット          |

| QA0, QA1 | 0   | クロックの立ち上がりエッジでのデータ出力  |

| QB0, QB1 | 0   | クロックの立ち下がりエッジでのデータ出力  |

図12-30はIDDRXFXAモードに構成された入力レジスタブロックを示します。CLK1はDDRレジスタと最初の同期レジスタペアのクロックです。CLK2は3段目のレジスタのクロッキングに用いられ、これはFPGAクロックに接続されるべきですこれらのクロック転送レジスタは出力レジスタブロックと共有されます。

### 図12-30 IDDRFXAモードの入力レジスタブロック

LatticeECP2/M 12-24 高速 IO I/F UGJ

図12-31はIDDRFXAモジュールを用いるときのタイミング波形を示します。

### 図12-31 IDDRFXA タイミング波形

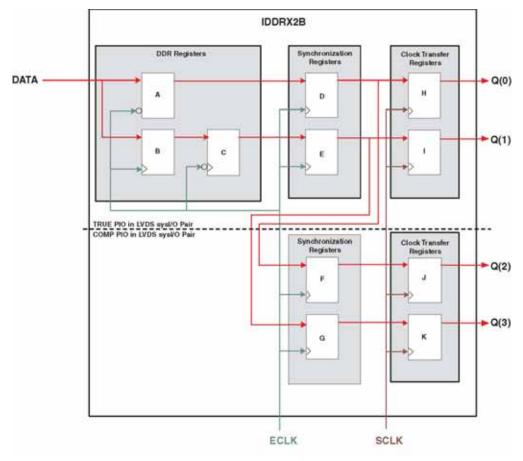

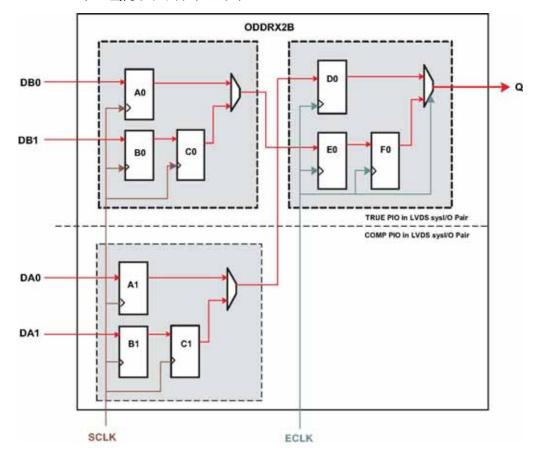

#### IDDRX2B

このモジュールはギアリング機能が必要であるときに用いられます。このプリミティブはエッジクロックの両エッジでDDRデータを入力して、SCLKにアラインした4本のデータストリームを生成します。SCLKは常にECLKの半分の周波数です。ECLKからSCLKを生成する為にCLKDIVモジュールかPLLを用いることを推奨します。

図12-32はIDDRX2Bモードのプリミティブシンボルを示します。

### 図12-32 IDDRX2Bシンボル

LatticeECP2/M 12-25 高速 IO I/F UGJ

表12-9はIDDRX2Bプリミティブのポート名と記述をリストします。

表12-9 IDDRX2Bポート名

| ポート名     | I/O | 記 述                       |

|----------|-----|---------------------------|

| D        | I   | DDRデータ                    |

| ECLK     | I   | クロック入力。高速クロックに接続することができます |

| SCLK     | I   | クロック入力。FPGAクロックに接続します     |

| CE       | I   | クロックイネーブル                 |

| RST      | I   | DDRレジスタのリセット              |

| QA0, QA1 | 0   | クロックの立ち上がりエッジでのデータ出力      |

| QB0, QB1 | 0   | クロックの立ち下がりエッジでのデータ出力      |

図12-33はIDDRX2Bモードに構成された入力レジスタブロックを示します。DDRレジスタと初段の同期レジスタペアはECLK入力が用いられます。SCLKが3段目のレジスタのクロックに用いられます。このプリミティブは4本のデータストリームを出力します。2xギアリング機能は、コンプリメンタリなPIOの同期レジスタを用いることによって実装されます。クロック転送レジスタは出力レジスタブロックと共有されます。

図12-33 IDDRX2Bモードの入力レジスタブロック

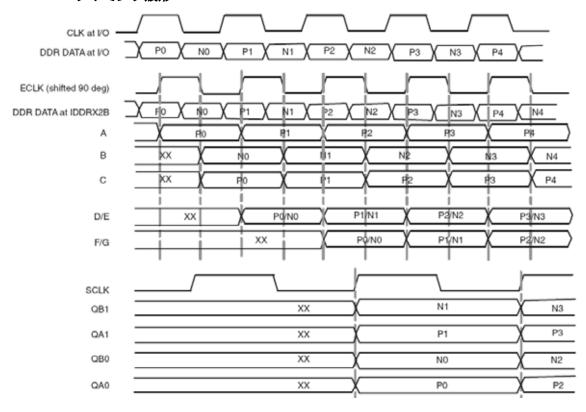

図12-34はIDDRX2Bモジュールを用いるときのタイミング波形を示します。

LatticeECP2/M 12-26 高速 IO I/F UGJ

### 図12-34 IDDRX2Bタイミング波形

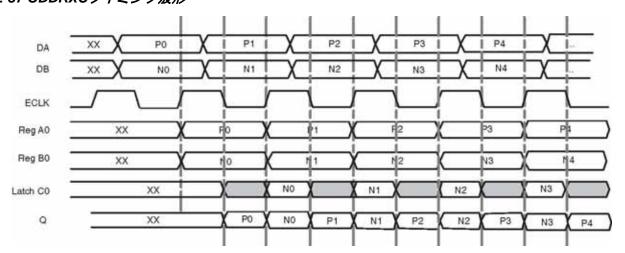

#### **ODDRXC**

これはDDR出力モジュールです。このプリミティブには、2本のデータストリームを入力し、sysIOバッファに行く一本のデータストリームを生成するために多重化します。このモジュールのCLKをエッジクロック、またはFPGAクロックに接続することができます。またこのプリミティブは、DDR機能にトライステート信号が必要である場合にも用いられます。

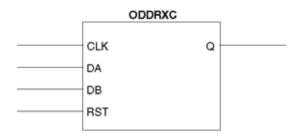

図12-35はODDRXCモードのプリミティブシンボルを示します。

#### **図12-35 ODDRXCシンボル**

表12-10はODDRXCプリミティブのポート名と記述をリストします。

LatticeECP2/M 12-27 高速 IO I/F UGJ

表12-10 ODDRXCポート名

| ポート名 | I/O | 記 述                   |

|------|-----|-----------------------|

| DA   | I   | クロックの立ち下がりエッジでのデータ出力  |

| DB   | I   | クロックの立ち上がりエッジでのデータ出力  |

| CLK  | I   | ECLKまたはFPGAクロックに接続します |

| RST  | I   | リセット信号                |

| Q    | 0   | DDRデータ出力              |

図12-36はODDRXCモードに構成された出力レジスタブロックを示します。

図12-36 ODDRXC出力レジスタブロック

図12-37はODDRXCモジュールを用いるときのタイミング波形を示します。

**図12-37 ODDRXCタイミング波形**

LatticeECP2/M 12-28 高速 IO I/F UGJ

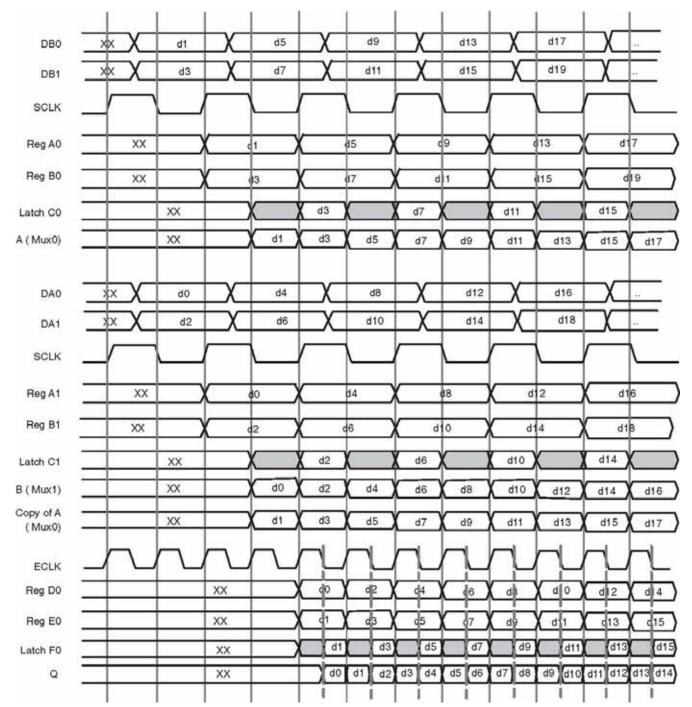

#### ODDRX2B

このDDR出力モジュールはギアボックス(ギアリング)機能が必要であるときに用いることができます。このプリミティブは、4本のデータストリームを入力し、sysIOバッファに行く一本のデータストリームを生成するために多重化します。

コンプリメンタリなPIOのDDRレジスタがこのモードで用いられます。DDR機能を実行するために、コンプリメンタリなPIOレジスタを用いることはもうできません。このプリミティブに行く2本のクロックがあります。ECLKはより高速なエッジクロックに接続され、SCLKはより低速なFPGAクロックに接続されます。このプリミティブのDDRデータ出力は、高速のエッジクロックに合わせられます。

図12-38はODDRX2Bモードのプリミティブ・シンボルを示します。

### 図12-38 ODDRX2Bシンボル

表12-11はODDRX2Bプリミティブのポート名と記述をリストします。

#### 表12-11 ODDRX2Bポート名

| ポート名     | I/O | 記 述                       |

|----------|-----|---------------------------|

| DA0, DB0 | I   | クロックの立ち下がりエッジでのデータ出力      |

| DA1, DB1 | I   | クロックの立ち上がりエッジでのデータ出力      |

| ECLK     | I   | クロック入力。高速クロックに接続することができます |

| SCLK     | I   | クロック入力。FPGAクロックに接続します     |

| RST      | I   | リセット信号                    |

| Q        | 0   | DDRデータ出力                  |

LatticeECP2/M 12-29 高速 IO I/F UGJ

図12-39はODDRX2Bモードに構成された出力レジスタブロックを示します。

### 図12-39 ODDRX2Bモードの出力レジスタブロック

LatticeECP2/M 12-30 高速 IO I/F UGJ

図12-40はODDRX2Bモジュールを用いるときのタイミング波形を示します。

### 図12-40 ODDRX2Bタイミング波形

LatticeECP2/M 12-31 高速 IO I/F UGJ

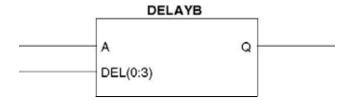

#### **DELAYB**

DDRレジスタに行くデータを、遅延ブロックを用いることで遅延させるオプションがあります。遅延ブロックは4ビットの遅延制御信号を受けます。4ビットの遅延は、固定の乗数を用いるか、またはユーザが制御するように設定することができます。DELAYBブロックは入力DDRレジスタと使用するときに利用できます。

DELAYBブロックは、IPexpressツールでDDR入力モジュールを生成するときに、構成することができます。 遅延は35psのステップで調整できます。ユーザは3タイプの遅延値から選ぶことができます。

- 1. ダイナミック ~ 遅延値は、DELAYBブロックへのDEL[3:0]入力を用いることで、ユーザ・ロジックによって制御されます。

- 2. 固定 ~ 固定値を選ぶとき、ユーザは同様に16ある乗数値の1つから選ぶ必要があります。これはDELAYB ブロックのDEL[3:0]入力を,選ばれた乗数に該当する固定値にします。

- 3. FIXED\_XGMII ~ XGMIIインターフェイスを実装するとき、DEL[3:0]は必要な遅延値に構成されます。 図12-41はDELAYBモードのプリミティブシンボルを示します。

#### 図12-41 DELAYBシンボル

表12-12はDELAYBプリミティブのポート名と記述をリストします。

#### 表12-12 DELAYBポート名

| ポート名     | I/O | 記 述               |

|----------|-----|-------------------|

| Α        | ı   | sysIOバッファからのDDR入力 |

| DEL(0:3) | I   | 遅延入力              |

| Z        | 0   | 遅延DDRデータ出力        |

#### 設計ルール/ガイドライン

以下に記述されるのは、LatticeECP2/Mデバイスに汎用DDRインターフェイスを実装するための幾つかの規則とガイドラインです。

- ・2xギアリングモードを実装する場合は、コンプリメンタリなPIOレジスタペアが用いられます。仕上がってペアとなる側のPIOレジスタは他の用途に用いることができないため、注意が必要です。

- ・DDRレジスタはデバイスの左右辺バンクと下辺バンクにあります。上辺バンクではサポートされていません。

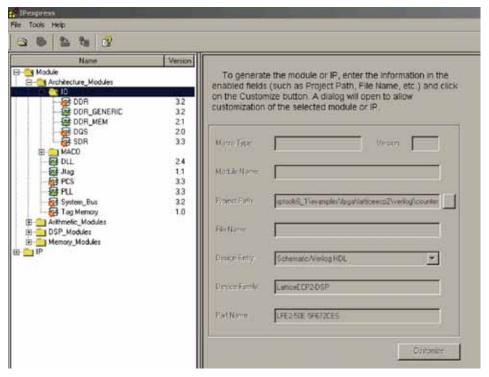

#### 汎用DDRとIPexpressの使い方

DDRメモリ・インターフェイスと汎用DDRモジュールは、IPexpressを用いてコンフィギュレーションし、 生成することができます。ツールはDDRプリミティブを含むHDLモジュールを生成します。このモジュール はトップレベル・デザインで用いることができます。

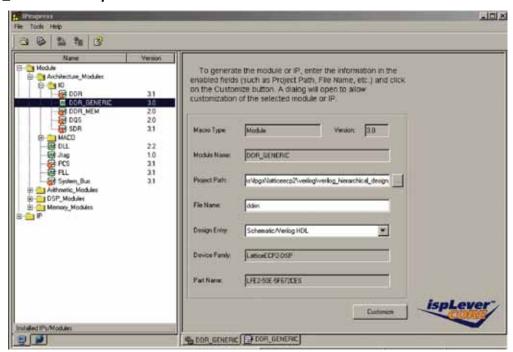

図 12-42 はIPexpress のメインウィンドーを示します。 **Architechture → IO**の下の**DDR\_Generic** と **DDR MEM**オプションが、DDRモジュールをコンフィギュレーションするのに用いられます。

LatticeECP2/M 12-32 高速 IO I/F UGJ

### 図12-42 IPexpressメインウィンドー

### 汎用DDR (DDR Generic)

図12-43はDDR\_Genericが選択された場合のメインウィンドーに示します。このウィンドウで必要な唯一の入力はモジュール名です。他のエントリーはプロジェクト設定に合わせてセットされます。望む場合、ユーザはこれらのエントリーを変えても構いません。モジュール名を入れた後に**Customize**をクリックすると、図12-44で示されるようなConfiguration Tabウィンドウが開きます。

図12-43 DDR\_GenericのIPexpressメインウィンドー

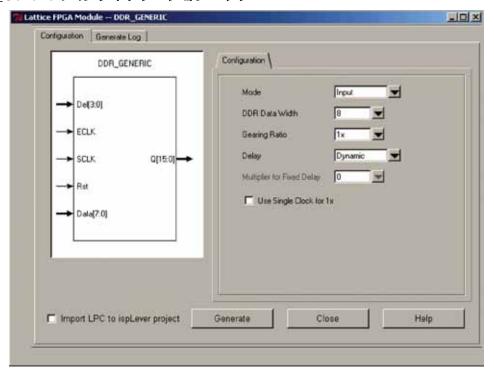

### コンフィグレーション・タブ(Configuration Tab)

コンフィグレーション・タブは、ユーザがアクセスできる全アトリビュートをデフォルト値に設定してリストアップします。完了した後、**Generate**をクリックしてソースコードと制約ファイルを生成します。ユーザは、パラメータをロードするために.lpcファイルを用いることを選ぶこともできます。

図12-44 DDR Genericのコンフィグレーション・タブ

ユーザはModeパラメータを変えることができ、Input、Output、BidirectionまたはTristate DDRモジュールを選べます。選択されたモードに応じて、他のコンフィグレーション・パラメータも変わります。遅延(Delay)パラメータはInputとBidirectionalモードで利用できます。同様に、遅延パラメータが固定(Fixed)に構成されるときだけ、固定遅延(Fixed Delay)パラメータの乗数(Multiplier)が利用できます。

表12-13 IPexpress GUIのユーザパラメータ

| ユーザパラメータ                   | 記 述                                       | 値 / 範囲                                    | デフォルト   |

|----------------------------|-------------------------------------------|-------------------------------------------|---------|

| Mode                       | DDRブロックのモード選択                             | Input, Output,<br>Bidirectional, Tristate | Input   |

| Data Width                 | データバス幅                                    | 1 ~ 64                                    | 8       |

| Gearing Ratio              | ギアリング比の選択                                 | 1x, 2x <sup>1</sup>                       | 1x      |

| Delay                      | 入力遅延                                      | Dynamic, Fixed, Fixed XGMII               | Dynamic |

| Multiplier for Fixed Delay | 固定遅延の設定。遅延が固定(Fixed)として構成される場合にだけ利用できる    | 0 ~ 15                                    | 0       |

| Use Single Clk for 1x      | ユーザがギアリングロジックのためにただー<br>本のクロックを選択するのを許容する | On / Off                                  | Off     |

注1. モードがBidirectionかTristateの場合、1xのみが利用できます。

LatticeECP2/M 12-34 高速 IO I/F UGJ

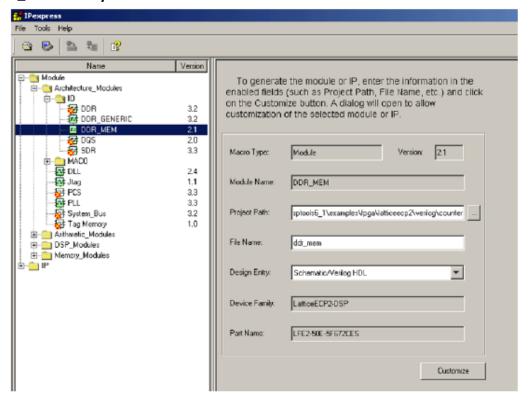

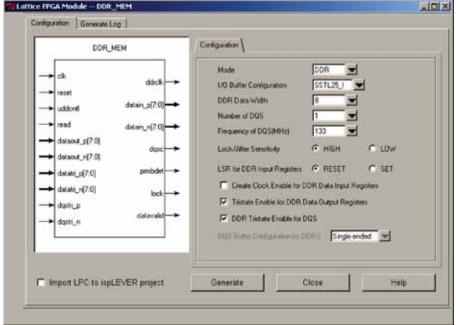

#### DDR MEM

図12-45はDDR\_MEMが選択された場合のメインウィンドーを示します。DDR\_Genericと同様に、ここで唯一必要である入力はモジュール名です。他の項目はプロジェクト設定を元に入力されています。望まれるなら、ユーザはこれらの入力を変えても構いません。モジュール名を入れた後にCustomizeをクリックすると、図12-46で示されるようにConfiguration Tabウィンドウが開きます。

### 図12-45 DDR\_MEMのIPexpressメインウィンドー

#### コンフィグレーション・タブ

Configuration Tabは、ユーザがアクセスできる全アトリビュートをデフォルト値に設定してリストアップします。完了した後、Generateをクリックしてソースコードと制約ファイルを生成します。ユーザは、パラメータをロードするのに.lpcファイルを用いることを選ぶこともできます。

ユーザは、ModeパラメータでDDRかDDR2インターフェイスのどちらかを選ぶことができます。選択された Modeに応じて、他のコンフィグレーション・パラメータは変わります。DQS本数(Number of DQS)のパラメータがDDRインターフェイスの本数を決定します。ソフトウェアは、各DQSあたり8データビットがあると 想定します。また、ユーザは動作周波数を選ぶことができ、DDR DLLはこの周波数でコンフィギュレーションされます。

ユーザには、クロックイネーブルとDDRレジスタ用のトライステート・イネーブルイネーブルするオプションがあります。DDRインターフェイスが150MHzかそれ以上で動作している場合、Lock / Jitterをイネーブルすることを推奨します。

LatticeECP2/M 12-35 高速 IO I/F UGJ

利用できるパラメータは選択されたモードに依存します。表12-14と12-15は、DDRとDDR2各モードでIPexpress GUIにあるユーザパラメータのすべてと、それらの使用法について説明しています。

表12-14 DDRモードのIPexpress GUIでのユーザパラメータ

| ユーザパラメータ                                   | 記述                                                 | 値 / 範囲                            | デフォルト    |

|--------------------------------------------|----------------------------------------------------|-----------------------------------|----------|

| I/O Buffer Configuration                   | インターフェイスに用いられるI/O規格。これも選択されたモードに依存する               | SSTL25_I, SSTL25_II               | SSTL25_I |

| Data Width                                 | データバス幅                                             | 8 ~ 64                            | 8        |

| Number of DQS                              | DQS本数はDQSグループ数を決定する                                | 1, 2, 4, 8                        | 1        |

| Frequency of DQS                           | DDRインターフェイス周波数。またこれはDDR DLLに入力される。値は選択されたモードに依存する。 | 100MHz, 133MHz,<br>166MHz, 200MHz | 200MHz   |

| Lock/Jitter Sensitivity                    | DLLのジッタに対する感度                                      | High, Low                         | High     |

| LSR for DDR Input Register                 | LSR制御                                              | RESET, SET                        | RESET    |

| Create Clock Enable for DDR Input Register | ブロックにクロックイネーブル入力を作成する。                             | On / Off                          | Off      |

|                                            | DDRデータ出力レジスタ用のトライステート制<br>御を作成する。                  | On / Off                          | On       |

| DDR Tristate enable for the DQS output     | DQS出力のためにトライステート制御を作成す<br>る                        | On / Off                          | On       |

LatticeECP2/M 12-36 高速 IO I/F UGJ

| 表12-15 DDR2 モードの | Pexpress GUIのユーザパラメータ | 7 |

|------------------|-----------------------|---|

|------------------|-----------------------|---|

| ユーザパラメータ                                      | 記述                                                        | 値 / 範囲              | デフォルト    |

|-----------------------------------------------|-----------------------------------------------------------|---------------------|----------|

| I/O Buffer Configuration                      | インターフェイスに用いられるI/O規格。これも選択されたモードに依存する                      | SSTL18_I, SSTL18_II | SSTL18_I |

| Data Width                                    | データバス幅                                                    | 8 ~ 64              | 8        |

| Number of DQS                                 | DQS本数はDQSグループ数を決定する                                       | 1, 2, 4, 8          | 1        |

| Frequency of DQS                              | DDRインターフェイス周波数。またこれはDDR<br>DLLに入力される。値は選択されたモードに依存<br>する。 | 1661/107 2001/107   | 200MHz   |

| Lock/Jitter Sensitivity                       | DLLのジッタに対する感度                                             | High, Low           | High     |

| i (Cgiotci                                    | LSR制御                                                     | RESET, SET          | RESET    |

| Create Clock Enable for<br>DDR Input Register | ブロックにクロックイネーブル入力を作成する。                                    | On / Off            | Off      |

|                                               | DDRデータ出力レジスタ用のトライステート制<br>御を作成する。                         | On / Off            | On       |

| DDR Tristate enable for the DQS output        | DQS出力のためにトライステート制御を作成す<br>る                               | On / Off            | On       |

| DQS Buffer Configuration for DDR2             | DQSバッファを差動として構成する                                         | On / Off            | Off      |

### FCRAM (Fast Cycle Random Access Memory) インターフェイス

FCRAMはDDRタイプのDRAMで、データ出力をクロックの立ち上がりと立ち下がりエッジ両方で行います。FCRAMデバイスは2.5Vのコア電圧で動作し、SSTLクラスII I/Oです。それは、SDRAMのコアと周囲ロジック両方が機能拡充されました。FCRAMではアドレスとコマンド信号はクロック入力と同期し、データピンはDQS信号と同期します。データ出力はDQSの立ち上がりと立ち下がりエッジ両方で行われます。DQSがデバイスのクロック入力と同位相です。DDR SDRAMとDDR FCRAMコントローラは異なるピン配置です。

LatticeECP2/Mデバイスは、専用DQSロジック、入力DDRレジスタ、および出力DDRレジスタを用いることでFCRAMインターフェイスを実装することができます。本ドキュメントの"メモリ・インターフェイスの実装"セクションで説明されています。FCRAMのアドレスと制御信号の生成はDDR SDRAMデバイスと異なっています。詳細な仕様については、FCRAMデータシートを参照してください。東芝や富士通などが256Mb規模のFCRAMデバイスを提供しています。それらはx8やx16構成で入手できます。

### ボード設計ガイドライン

DDRにメモリ・インターフェイスを実装することに関連する一般的に最も困難なことはボード設計とレイアウトです。ユーザは、メモリデバイス・ベンダが推奨するガイドラインに厳密に従うことが必要です。

一般的な推薦事項の幾つかには次が含まれます。即ち、スキューを避けるためにインターフェイス信号の配線長を同一にすること、適切なDQ-DQS信号のグループ化、SSTL2やSSTL18 I/Oの適切な終端、適切な $V_{REF}$ と $V_{TT}$ の生成とデカップリング、そして適切なPCBの配線などです。

以下のドキュメントはボード設計ガイドラインを含んでいます。

- · www.idt.com, IDT, PCB Design for Double Data Rate Memory.

- · www.motorola.com, AN2582, Hardware and Layout Design Considerations for DDR Interfaces.

#### 参考文献

• www.jedec.org, JEDEC Standard 79, Double Data Rate (DDR) SDRAM Specification

LatticeECP2/M 12-37 高速 IO I/F UGJ

- www.micron.com, DDR SDRAM Data Sheets

- www.infinion.com, DDR SDRAM Data Sheets

- www.samsung.com, DDR SDRAM Data Sheets

- www.latticesemi.com, RD1019, QDR Memory Controller Reference Design for Lattice ECP/EC Devices

- www.toshiba.com, DDR FCRAM Data Sheet

- www.fujitsu.com, DDR FCRAM Data Sheet

- www.latticesemi.com, LatticeEC Advanced Evaluation Board User's Guide

- www.latticesemi.com, DDR SDRAM Controller (Pipelined Version for Lattice ECP/EC and LatticeXP™ Devices) User's Guide

# テクニカル・サポート支援

ホットライン: 1-800-LATTICE (North America)

+1-503-268-8001 (Outside North America)

e-mail: techsupport@latticesemi.com インターネット: http://www.latticesemi.com

# 変更履歴(日本語版)

| Rev.# | 日付         | 変更箇所                     |

|-------|------------|--------------------------|

| 1.4J  | Apr.2007   |                          |

| 1.5J  | Jan.5,2008 | 図12-34 を更新。全面的に文章・用語を校正。 |

|       |            |                          |

|       |            |                          |

LatticeECP2/M 12-38 高速 IO I/F UGJ