# **LatticeSCM XAUI to SPI4.2**

July 2008 Reference Design RD1033

### Introduction

The XAUI to SPI4.2 (X2S4) Bridge reference design is a cost-effective system solution for bridging SPI4.2 based network processors and 10G/10G+ Ethernet switching devices. On the XAUI side, the X2S4 optionally supports the HiGig™ protocol from Broadcom® and an over-clocked mode of operation supports the Broadcom HiGig+™ protocol with throughput rates of up to 12Gbps at the link layer. This solution leverages existing proven IP cores that include the LatticeSCM™ SPI4.2 hard IP block and the Ten-Gigabit Plus Ethernet Media Access Controller soft IP core as major building blocks of the design. This solution also takes advantage of LatticeSCM built-in features such as System Bus for microprocessor access and PCS SERDES high-speed serial I/O. These IP components are fixed entities for all bridging applications and are delivered in a IP protected format (encrypted). They can be altered in terms of behavior only so far as the existing supported programming options for those IP cores allow. The Bridge Interface Logic (BIL) that glues all of the IP together forming the bridge is, however, expected to be customized for each user application realizing that each has its own unique methods for achieving similar end results. This part of the design, as well as a comprehensive test-bench, is delivered in unprotected rtl format.

The X2S4 reference design package includes a full development level infrastructure starting from relevant documentation to "ready-to-load" bitstream including everything in between such as completed directories loaded with source rtl, IP, test-bench source, rtl simulation scripts and results, gate simulation scripts and results, ispLEVER® place and route, etc. Users will find the comprehensive simulation environment (control and data planes) especially useful in supporting verification of customizations they wish to make to the reference design.

As indicated previously, the X2S4 Bridge reference design incorporates the LatticeSCM SPI4.2 MACO hard IP core and the 10G+ Ethernet MAC (10G+MAC) IP core. The reference design package includes pre-generated versions of these cores to implement a fully functional solution. An IP license for the LatticeSCM SPI4.2 hard IP, available free of charge, is required to fully evaluate the complete reference design. An IP license for the 10G+MAC is required to use the reference design in a final design. Additional information on the licensing requirements is provided in the IP Licensing section of this document.

The X2S4 Bridge was developed specifically for the LatticeSCM series FPGA family with particular focus on the LFSCM15 device matched with a small-sized 256-pin package. It targets two specific network processors (EZChip and Intel) and Ethernet switch manufacturers (Broadcom and Marvell) and as such draws heavily upon their architectures in establishing bridge functionality.

### **Features**

- SPI4.2 IP Core Features:

- Fully compliant with the OIF System Packet Interface Level 4 Phase 2 Revision 1 (SPI4.2.1) interface standard

- Support for up to 256 independent channels (single channel for this X2S4 Bridge).

- 156 to 500MHz DDR Dynamic timing mode operations.

- Requires only 865 slices for a full 256-channel Dynamic mode core.

- Parity error checking/generation on all receive and transmit control and data words (DIP4) and status (DIP2) interfaces. Also includes SPI4.2 protocol checking and error reporting.

- Parity error force capabilities on data (independent controls: control word and data) and status interfaces.

- Various run-time user controls: Individual receiver/transmitter resets, De-skew only reset, Adaptive Input Logic only reset, Force idles (transmitter), Enable/Disable Packing (transmitter)

- Complete run-time programmability of all internal FIFO thresholds for efficient management of SPI4.2 line in terms of L (max) and packing.

- Supports minimum transmit burst sizes in increments of 16 bytes from 16 bytes up to 1008 bytes for optimized Network Processor applications.

- Fully configurable 512-location calendar RAM for Rx and Tx directions and associated 256-location status

RAMs

- 8K-byte shared buffer space for both transmit and receive directions.

#### 10G+MAC IP Core Features:

- Compliant to IEEE 802.3-2005 standard

- Optional Broadcom HiGig and HiGig+ format support.

- 64-bit wide internal data path operating at 156.25-187 MHz supporting up to 12Gbps of throughput.

- XAUI interface to the PHY layer (using PCS/SERDES external to the core)

- Optional Multicast address filtering

- Transmit and Receive statistics vector

- Programmable Inter Frame Gap (including reduced HiGig IFG)

- Supports:

- Full duplex operation

- Flow control using PAUSE frames (detect and act upon in receive direction, pause frame creation on command in transmit direction)

- Optional Pause Frame drop (egress)

- Automatic padding of short frames

- Optional FCS generation during transmission

- Optional FCS stripping during reception

- Jumbo frames up to 16k

- Interframe Stretch Mode during transmission

- 2K transmit and receive buffers

- Complete statistics support (reduced set for X2S4 Bridging)

### · System Bus Features:

- Full LatticeSCM built-in hard block System Bus resources operating in User Master mode. Two external

interface styles ("External UMI" and JTAG) are provided as part of the reference design. An optional PowerPC style external interface (not available in the 256 fpBGA package) is not part of the standard package

but can be easily added by the user).

- SPI4.2 IP core supported by System Bus and Serial Management Interface (SMI) for in-circuit controllability and observability without using general logic resources.

- PCS SERDES supported by the SMI for in-circuit controllability and observability without using general logic resources.

- Provides full read/write access to all programmable registers for the SPI4.2 IP core, 10G+MAC IP core, and Bridge.

### • Bridge Features:

- Limited MAC and PCS statistics collection (MAC supports complete statistics data profile collection addition/subtractions can easily be customized by the user).

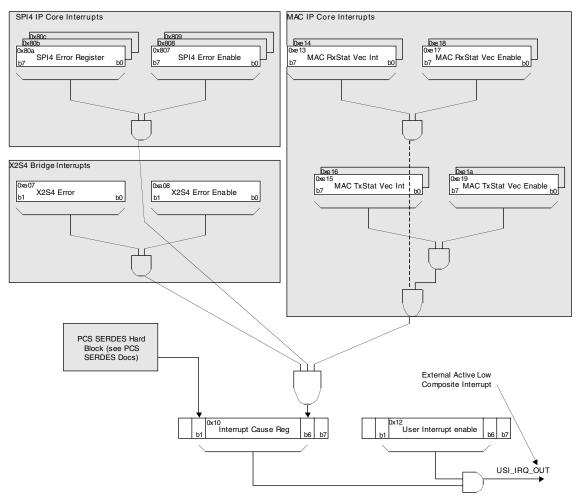

- Fully maskable interrupt structure and composite interrupt I/O signal pin for error notification and reporting.

- User-configurable Shared Ingress and Egress FIFOs size (default = 32K byte each).

- Store & Forward architecture used in the Ingress direction. Store & Forward or Cut-Thru is user selectable in the Egress direction.

- Several options for error handling including error drop, packet filtering / correction (missing sop or eop), and mark and pass.

- Graceful overflow drop dropping only the packet that causes an overflow.

- Translation between Ethernet Pause based flow control and SPI4.2 Status based flow control

- Two types of flow control (two-tiered, pass thru) offered.

- Full bandwidth (10G/12G) Bridging

# Scope

This document focuses on the Bridge Interface Logic (BIL) and control infrastructure of the Bridge leaving details of the major IP blocks to their respective stand-alone documents. These documents are listed in the Reference Information section below.

### **Reference Information**

IP core documentation is available now on the Lattice Semiconductor website at www.latticesemi.com.

Information for the following system components are contained in the following documents:

- IPUG44 LatticeSCM SPI4.2 MACO™ Core User's Guide

- IPUG39 Ten-Gigabit Ethernet Plus Media Access Controller (10G+MAC) User's Guide

- TN1085 Lattice SC/MPI System Bus

- DS1005 LatticeSC/M Family flexiPCS™ Data Sheet

- RD1034 Lattice XAUI To SPI4.2 Simulation Plan

- RD1035 Lattice XAUI To SPI4.2 Hardware Evaluation Report

# **System-Level Block Diagram**

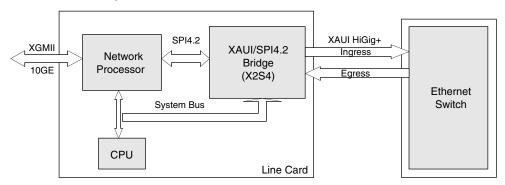

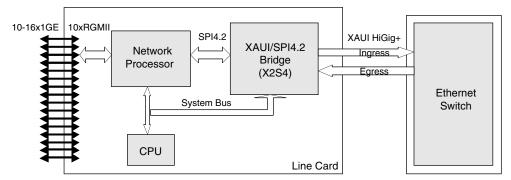

Figures 1 and 2 show system level diagrams of the typical line card to Ethernet switch applications for which the X2S4 Bridge is intended. In these cases, the X2S4 design provides a bridging function between an SPI4.2 based Network Processor (NP) and Ethernet-based switching device allowing for efficient flow of data packets in either direction across both interface types.

The implementation chosen is based on the premise that direct connection between the NPU and the switch devices would be the ideal connection method if it were possible. It is with this thought that the X2S4 bridge design is constructed to appear as transparent as is possible in its action of exchanging data between the SPI4.2 and Ethernet endpoints.

Figure 1. 10GE Line Card Example

Figure 2. 10 - 16x 1GE Line Card Example

# X2S4 Bridge Overview and Background Information

Inherent, and in some ways limiting, characteristics of the XAUI 10/12G Ethernet interface dictate many design aspects of this version of the X2S4 Bridge, ranging from channelization, to buffer configurations, and to flow control that extend across the bridge to the operational mode of the SPI4.2 interface. In particular, the absence of a multichannel packet inter-leave capability in the Ethernet protocol means that the SPI4.2 bus does not need to interleave (i.e., it can transmit full packets, like Ethernet, instead of fragments from multiple packets on multiple channels). Because packets are transferred in whole, there is no need for a multi-channel buffer configuration to reconstitute full packets. Instead, a shared buffer arrangement works fine. The absence of a multi-channel flow control capability in Ethernet means that the SPI4.2 bus will also operate in a single channel context as it relates to flow control. This means that, like Ethernet Pause (X\_On/X\_Off), when the SPI4.2 bus is flow controlled, data transmission stops completely; not on a per-channel basis.

Flow control at the individual MPHY port level shown in Figure 2 is addressed outside of the bridge through alternative line-card-to-line-card communication. It is possible, based on user needs, to operate the SPI4.2 data interface in multi-channel mode for the purposes of channel identification (but still operating non-interleaved). The SPI4.2 channel number can then be translated and used in support of VLAN tagging for example as a possible customer based customization - this is not currently part of the design.

Lastly, line card to line-card flow control is supported in the HiGig2 version that would allow translation of SPI4.2 status channel number to flow control messaging. This may be addressed in a future version of the Bridge.

### Flow Control

### **Two Tiered Approach**

Flow control is viewed in the context of the full 10Gbps pipe as it relates to the exchange of data across the bridge in either direction. There are actually two independent "end-to-end" flow control segments, the first between NPU and Bridge, and the second between Bridge and Ethernet device. A two-tiered flow control structure is used where it is possible to flow control only one segment without flow controlling the other due to the internal Bridge FIFOs. For this configuration, the second segment would be flow controlled only if the internal Bridge FIFO has reached high water on the first segment. Within this approach, the X2S4 Bridge offers an option to either pass flow control information across the bridge immediately as it is encountered, or wait until the programmable FIFO threshold is reached. In either case, the X2S4 Bridge stops data transmission at the Bridge immediately when flow control is encountered. In terms of system analysis and setting of FIFO threshold values, the X2S4 Bridge will therefore need to be able to absorb all committed data from the transmitting end from the point where it passes flow control information to the transmitting end.

#### **Translation**

The standard Ethernet based Pause (X\_On, X\_Off) flow control scheme is indirectly translated into SPI4.2 based status and vice versa via the X2S4 internal Bridge FIFOs high and low water marks. Simple two state X\_On (starved)/X\_Off (satisfied) signaling is used for both the Ethernet and SPI4.2 interfaces. SPI4.2 Credit accounting through MaxBurst1 and MaxBurst2 parameters is not supported.

In the Ingress direction, as the MAC responds to Pause frames it receives by inhibiting Ingress transmit data flow, the X2S4 Ingress FIFO fill level builds resulting in SPI4.2 Status flow control. The MAC IP core provides Pause Quanta timing and clearing via X\_On as well as a composite Pause signal revealing the Pause state of the MAC transmitter to the Bridge Interface Logic. In addition, Pause flow control frames received via the MAC can be optionally dropped inside the MAC so that they are not passed to the NPU. The X2S4 Bridge also offers a path into the SPI4.2 Status channel from the local Microprocessor interface.

In the Egress direction, when the SPI4.2 status channel is active (Satisfied), it inhibits the movement of data from the internal Egress FIFO to the SPI4.2 transmit FIFO. As the fill level builds inside the Egress FIFO, a programmable high-water mark is reached and results in the creation of a Pause control frame loaded with a Pause Quanta value from a locally programmed register. The 10Gbps MAC IP core contains the Pause Frame Generator but is controlled through an Egress Status Controller (ESC) outside the IP core. Extra long periods of flow control will result in the creation and transmission of multiple Pause control frames in order to maintain the flow control state.

### **Bridge Initiated Flow Control**

The SPI4.2 interface is expected to have, in most cases, considerable over-speed relative to the Ethernet link. An SPI4.2 interface operating with a 400-500MHz DDR clock will yield between ~12.8Gbps and 16Gbps of bandwidth. The Ethernet link operating over an over-clocked XAUI+ interface is expected to yield at most, 12Gbps of bandwidth. This being the case, the X2S4 Bridge is not able get rid of data fast enough in the Ingress direction and requires periodic flow control during sustained periods of NPU data transmission. Bridge initiated flow control is based on the Ingress FIFO fill level. Thresholds for all FIFOs are completely programmable in order to smooth out data transmission.

In the Egress direction, the normal segmentation capabilities of the SPI4.2 protocol address the over-speed issue. In this direction, once the Bridge Interface Logic begins loading a packet into the SPI4.2 transmit FIFO, the SPI4.2 over-speed will quickly over-run the data source and appropriately segment the SPI4.2 line when it runs out of data (see SPI4.2 Burst Mode described in the LatticeSCM SPI4.2 IP Core User's Guide).

### **QoS Considerations**

When considering transmitter functionality at both the NPU and Fabric ends of the bridge, the data has already been shaped in terms of QoS priority and so there was no compelling reason to implement any type of additional QoS scheduling capability inside the bridge.

### **Packet Drop**

It is believed that all error'ed packets entering the network through line cards will be dropped by the NPU and therefore any error'ed packets detected in the bridge (Ethernet CRC, SPI4 DIP4, and Abort) are device-to-device errors on the same board/system. For this topology, error'ed packets are expected to occur at extremely low rates due to bad hardware. Bad packets detected in the bridge can, however, be optionally dropped or they can be marked and passed as they occur so they can be dropped at the next device node in the data path. Both the SPI4 and Ethernet protocols allow for marking all transmitted packets as bad and is useful in cut-thru modes since drop is not possible.

## **CRC Generation / Checking**

Several options exist for CRC generating and checking inside the MAC in support of the XAUI interface. See the 10G+MAC User's Guide for details.

### Store & Forward - Cut Thru

In the Ingress direction, full packets must be stored before beginning Ethernet transmission due to the burst capability of the SPI4 interface. Store & Forward architecture is therefore used in the Ingress direction and is not user-selectable without rtl modification of the Bridge logic. In the Egress direction, either mode can be selected via a parameter based on user needs. Cut-thru architectures are preferred in many cases due to low latency. Store & Forward is sometimes preferred because packet drop can be supported.

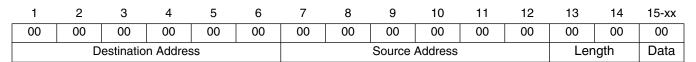

### Packet Formats - HiGig Header Overlay

All packets received on the SPI4.2 interface from the NPU must also be in standard Ethernet or HiGig format depending upon bridge mode selected and CRC programming options selected in the MAC (see section - "Packet/Frame Formats").

In this version of the Bridge, HiGig header overlays are supported only on control frames (pause). These frames originate inside the MAC since the MAC is responsible for generating pause frames. Future versions of the Bridge may support insertion/deletion of the HiGig header on data frames but the initial version does not. Customers are free to add this capability to the Bridge given that the area of the circuit most likely to add the feature is not security protected.

# **X2S4 Bridge Operational Description**

Figure 3 provides a block diagram of the X2S4 Bridge. Refer to this figure as well as Figure 4 (Bridge Interface Logic Block Diagram) in the next section while reading the Operational Overview.

X2S4 Bridge (x2s4\_top\_sb\_umi.v) SPI4 Hard Bridge Inerface Logic - BIL MAC Soft IP Core IP Core EBC SPI4 TxDATA SPI4 TX XAUI\_RX RX MAC\_RX SATISFIED ESC SPI4\_Tx\_STATUS UP\_PAUSE\_REQ Egress Direction PAUSE\_ CS SERDES ᅻ Ingress Direction IBC SPI4 RX DATA SPI4 RX MAC TX XAUI\_TX ΤX SATISFIED ISC SPI4\_RX\_STATUS UP PAUSE REQ X2S4\_REGS SPI4\_REGS MAC\_REGS & STATS UMI Bus PCSA\_360 SYSTEM BUS (comp interupt) SMI SPI4\_TX\_PLL SPI4\_RX\_PLL SDCK PLL

Figure 3. X2S4 Bridge Block Diagram

## **Data Flow - Ingress Direction**

In the ingress direction, data packets are transferred from the Network Processor (NP) to the Ethernet Switch (ES). When the NPU has a complete packet ready for transmission to the ES, it interrogates the status of the SPI4.2 interface via its input Status Channel. For this application, a single status channel is employed to convey status for the entire 10G+ SPI4.2 data interface and only two (Starved and Satisfied) of the three state signaling possibilities (Hungry, Starved, Satisfied) supported by SPI4.2 standard are used. An Ingress Status Controller (ISC) determines the final status state delivered to the NPU and it takes into consideration two sources of flow control information in its determination: 1) the Ingress Bridge FIFO Almost Full Flag, 2) Microprocessor requested flow control through local register programming. Assuming none of these sources are currently requesting flow control, the status received at the NPU end will reflect the Starved state and the NPU will begin transmission of the packet to the X2S4 bridge.

As the packet enters the bridge and begins to fill the SPI4.2 receive FIFOs, the bridge logic responds very quickly and starts moving the packet into the Ingress Bridge FIFO (IBF) keeping the SPI4.2 FIFOs very shallow throughout the transfer. Shortly after the start of moving the packet into the IBF, the Transmit Empty ('tx\_aem') flag is removed causing the MAC to start reading data, assuming it is not currently in the Pause state, under control of the Ingress MAC Controller (IMC) and transferring it from the IBF into the MAC. As the data is read, it is transferred to the Bus Conversion block where the 128b bus is converted to a 64b bus for presentation to the 10G+MAC. Once the EOP is written into the IBF, the Ingress MAC Controller (IMC) checks the state of the ISC to ensure that the bridge is not currently flow controlled and if not, asserts the 'tx\_data\_avail' signal informing the MAC that it may begin transmis-

sion. The MAC will continue to read from the IBF until the Transmit Empty ('tx\_aem') signal is again asserted or its internal FIFO fills to a pre-determined level transmitting the entire packet. After the packet is completely transmitted, the transmit Status Vector is available for collection by the Statistics collection logic.

The MAC contains only a small 4K-byte internal buffer that is kept very shallow under normal traffic conditions. This FIFO will build however under both microprocessor and Pause based flow control conditions. For microprocessor-initiated flow control, the IMC does not assert the data available signal ('tx\_data\_avail') and so the MAC does not transmit. The MAC is however allowed to move data from the IBF to the MAC internal FIFO until a predetermined fill level is reached. For Pause uninitiated flow control inside the MAC, the transmitter is not allowed to send data but it can load its internal FIFO.

For sustained periods of data transmission from the NPU to ES, the IBF will build quickly given that there must be at least one full packet in the IBF before it is allowed to be transmitted and because of the over-speed of the SPI4.2 interface relative to the XAUI interface. User programmable Almost Full and Almost Empty thresholds associated with the IBF are used to control the point at which flow control begins and then ends for this condition. Assuming that the user application supports Jumbo frames and has a desire to keep storage in the bridge to a minimum, the Almost Full threshold could be set to somewhere between 11 and 21Kbytes which are the 1/3, 2/3 points of a 32K Byte IBF. Combined total storage of all three FIFOs is 32K(IBF) + 8K(SPI4) + 4K(MAC) = 44Kbytes. This should be more than enough to absorb in-flight and committed data.

### **Data Flow - Egress Direction**

In the egress direction, data packets are transferred from the Ethernet Switch (ES) to the Network Processor (NP). Once a valid start of frame is detected in the MAC, the destination address field of the incoming frame is analyzed along with a variety of IP programmable options having to do with specifying the types of packets that may be passed across the bridge. These options can be configured on an application-by-application basis and do not have material impact on the behavior of the X2S4 Bridge. If the beginning part of the packet meets the address filtering criteria in the MAC, data transfer begins unconditionally and almost immediately towards the Bridge Interface Logic (BIL). The MAC does contain a 4K-byte Egress buffer but only ~64 bytes are actually used for address filtering allowing the MAC to drop packets inside the IP core when necessary. This FIFO never builds.

As packet data moves into the BIL, it is first converted from 64-bit format to 128-bit format in preparation for later delivery to the SPI4.2 IP core. Data is then written into the EBF unconditionally as it is received. As the EBF fill level builds, the Egress Read FIFO control logic will first interrogate the status of the SPI4.2 interface via its input Status Channel. Like the Ingress direction, a single status channel is employed to convey status for the entire 10G+ SPI4.2 data interface and only two (Starved and Satisfied) of the three state signaling possibilities (Hungry, Starved, Satisfied) are supported. An Egress Status Controller (ESC) determines the final status state reported to the FIFO read control logic and takes into consideration two sources of flow control information in its determination: status received from the NPU, and Microprocessor requested flow control through local register programming. Assuming none of these sources are currently requesting flow control, the status received by the FIFO read control logic will reflect the Starved state and data will quickly start to move into the SPI4.2 transmit FIFO committing it to the SPI4.2 line (EOP must exist for Store & Forward mode). Note that due to the 64b to 128b bus conversion, writes to the EBF will occur every other cycle at 156-187MHz (over-clock) whereas the EBF can be read every 150MHz clock cycle as the Egress MAC Controller (EMC) moves data into the SPI4.2 IP core. This over-speed results in the EBF running very shallow during the absence of flow control. Under these conditions, packet data will be written into the SPI4.2 transmit FIFO for a clock cycle or two, stop and then restart continuously but will be smoothed out once it hits the SPI4.2 line using the Burst Mode capability of the SPI4.2 IP core. Burst sizes can be set to from 1 to 63 Credits. Setting this value to 8 for example guarantees that there will be no bursts smaller than 8 \* 16 bytes = 128 bytes transmitted on the SPI4.2 line without an EOP. Building of the SPI4.2 transmit FIFO will occur only up to the point where the minimum burst size has been received. After a packet is completely transmitted, the receive Status Vector is available for collection by the Statistics collection logic.

If either the NPU, via the SPI4.2 status interface, or local microprocessor has requested flow control, a Satisfied state is reported to the FIFO read control logic and the movement of data from the EBF to the SPI4.2 transmit FIFO stops. Inside the SPI4.2 core, the transmitter will completely empty any data in the input FIFO and appropriately

segment the line mid-packet and resume the packet when the flow control state is lifted and data again enters the FIFO (once in the SPI4.2 FIFO its committed). If Burst-Mode is enabled, the FIFO will only be emptied up to the point where there is less than the programmed burst size left in the FIFO. Unlike the Ingress direction where all three FIFOs (SPI4.2, Bridge, and MAC) sum to provide larger over-all storage during flow control, in the Egress direction, only the EBF is capable of providing this function. Unfortunately, the Egress direction FIFO storage is the most critical due to the fact that flow control is in-band rather than out-of-band like the SPI4.2 interface. The worst case scenario is when the EBF hits the high-water mark and makes a request of the MAC to generate a flow control frame to relieve the traffic condition but the MAC has just started sending a Jumbo frame. In this case Pause frame transmission must wait. When the Pause frame finally arrives at the switch end, it too may have just started sending a Jumbo frame.

In addition to flow controlling locally, the ESC also causes the MAC to generate and transmit a Pause control frame with a locally programmed Pause Quanta value over the Ethernet interface. The ESC starts a counter in order to time the flow control state. If the original source of flow control is still requesting the flow control state near the end of the timed value, the ESC directs the MAC to send another Pause frame in order to maintain the flow control state. When the source of flow control removes the flow controlled state, the ESC directs the MAC to send another Pause frame (X On) removing the flow control.

### Bridge Interface Logic (BIL) Block Diagram

Figure 4 shows a block diagram view of the Bridge Interface Logic (BIL) used to bridge SPI4.2 and Ethernet functions together.

RST NI Bridge Interface Logic - BIL S4SDCk MAC C ING RST RxFRD IBF\_FULL Ingress Bridge SINE\_TX\_AEM -ibf full Controller - (IBC) Ingress MAC SINE\_TX\_READ ibf empty Controller - (IMC) RxDATA[128] SINE\_TX\_DATA\_AVAIL Ingress Bridge FIFO (IBF) 32KB RxSOP,RxEOP rxrdata[128] SINE\_TX\_DATA[64] Conversion [128:64] RxREM[4] rxsop, rxeop (2048x144) SINE\_TX\_EOF RxABT SINE\_TX\_BYTEN[3] rxrem[4] EOP Counter RxPA[8]\*1 rxabt, rxdp4e SINE\_TX\_ERR BxDP4E RxDVAL ING\_AFE\_THRHD[10:0] EG AFE THRHD[10:0] RxSTAT[1:0] Ingress Status SINE\_TX\_PAUSE\_STATUS Controller RxSTCK(txs4ls4\_cl ING\_PASS\_FCTL (ISC) ING\_UP\_PAUSE\_REQ SPI4 Interface MAC Interface EG\_RST Egress Bridge EBF\_FULL TxF1AF Egress Bridge FIFO TxFWR Read Control Egress MAC IGNORE\_NXT\_PKT ebf empty Controller (EMC) Earess Bridge TxDATA[128] rx\_write SINE RX WRITE FIFO (EBF) TxSOP,TxEOP S Conversion [64:128] rx data[128] SINE RX DATA[64] 32KB TxPA[8]\*1 (2048x144) SINE\_RX\_BYTEN[3] rx byten[4] TxREM[4] rx\_eof SINE\_RX\_EOF TxERR rx err Bus SINE\_RX\_SOF SINE\_RX\_ERROR EG PASS FCTL EG\_UP\_PAUSE\_REQ satisfied EG PASS\_FCTL EG UP PAUSE REQ TxSTPA[7:0]\*1 Egress Status EG\_UP\_PAUSE\_TIME[15:0] TxSTPA VAL\*1 Controller (ESC) TX\_PAUSE\_TIME[15:0] TxSTAERR TX\_PAUSE\_REQ TxSTATUS\_CK (line

Figure 4. Bridge Interface Logic (BIL) Block Diagram

### Packet Error Handling

There is a packet error-checking/correcting module on the input side of the bridge buffers that controls writing of packet data into the buffer. This module is always operating in the circuit and behaves differently based on whether Drop is enabled.

### **DROP Inactive**

Depending upon the type of error and where it is detected, different handling takes place when Drop is inactive. Errors that are received with the payload such as SPI4 abort and DIP4 or MAC CRC errors are simply passed through the buffer and are used to mark the packet as bad before it leaves the device so that the far-end can properly dispose of it. Other errors detected inside the bridge, such as missing SOP and missing EOP, are handled as follows:

- Missing EOP: SOP followed by SOP. Insert an EOP and mark the packet as bad. It is best to get rid of packet fragments from the system as soon as possible.

- Missing SOP: EOP followed by EOP. Drop all data up to the next valid SOP.

- FIFO Full/Overflow: Drop only the packet, up to the reception of the EOP, that caused the FIFO to fill and then start writing the next packet into the buffer. If it results in full, drop it also and repeat forever. Note that the FIFO is not allowed to actually overflow. Note also that this overflow drop feature is present regardless of control signal drop.

### **Drop Active**

When drop is active, all error'ed packets are dropped before the buffer as follows:

- Missing EOP: SOP followed by SOP. Drop SOP encapsulated data and begin writing data from second SOP into the buffer. If another SOP is received, drop it also. Repeat forever.

- Missing SOP: EOP followed by EOP. Drop all data up to the next valid SOP.

- SPI4 Abort (Ingress): Drop packet.

- SPI4 DIP4 (Ingress) and MAC CRC (Egress) Errors: Drop packet.

### **XAUI Overview**

Standard XAUI supports a 10Gbps client side payload over a 12.5Gbps SERDES interface after the payload is 8b10b encoded requiring 25% over-speed. A group of four SERDES each operating at 3.125Gbps is used to provide the interface. This translates into a 156.25MHz client side clock over a 64-bit wide data bus.

Some Ethernet switch manufacturers offer an "over-clocked" XAUI mode that affords a full 12Gbps to the client side. This mode is also supported by the X2S4 reference design. In the over-clocked mode, the SERDES operate at 3.75Gbps providing ~20% over-speed (15Gbps). For this mode of operation, the client side interface operates at ~187MHz over a 64-bit interface in order to support the higher rate.

### HiGig and HiGig+ - Broadcom

The X2S4 Bridge optionally supports Broadcom's proprietary method of Ethernet switch stacking. Contact your local Lattice sales office for additional information.

### HyperG.Stack - Marvell

The X2S4 Bridge supports Marvell's method of Ethernet switch stacking where XAUI ports can be run in 10 or 12G modes. The over-clocked mode used at Marvell does not include a proprietary protocol - standard Ethernet frames are used.

### **External UMI Bus**

This section describes the User Master Interface (UMI) implementation strategy for an external microprocessor interface. It pays particular attention to the topic of Big/Little Endian as it relates to the address and data buses.

### **Big Endian Data Bus Format**

The X2S4 reference design utilizes many of the LatticeSC embedded System Bus capabilities to support external read/write access of various registers and memory inside the bridge. Some of the endpoints are FPGA hard blocks such as the system bus block itself, the PCS SERDES block and the MACO blocks while others are soft FPGA based register modules associated with the SPI4.2, 10G+MAC, and Bridge level IP. Because the system bus and PCS SERDES blocks are designed (both silicon and register documentation) to support a Big Endian data interface format and can not be changed, the other soft read/write end-points also conform to the Big Endian format in order to maintain consistency.

Therefore, the external UMI data bus format requires that the lsb of a given read/write item be carried over the wire/pin labeled D7. For example, the first byte of the LatticeSCM device ID register located in the System Bus hard

block is documented to contain a value of 0xEA. In the PCS block, Quad Interface Register (QIR) 0x16 is defined to carry the lower bits of the comma character 0x7c. In big endian format, the data for these accesses are carried as follows across the external UMI data bus.

Table 1. Big Endian

|                                      | Pin/Wire<br>D7 | Pin/Wire<br>D6 | Pin/Wire<br>D5 | Pin/Wire<br>D4 | Pin/Wire<br>D3 | Pin/Wire<br>D2 | Pin/Wire<br>D1 | Pin/Wire<br>D0 | Numeric |

|--------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---------|

|                                      | LSB            |                |                |                |                |                |                | MSB            | Value   |

| System Bus<br>DEVICE ID<br>0x00000   | 0              | 1              | 0              | 1              | 0              | 1              | 1              | 1              | 0xEA    |

| QIR Defined<br>Comma Char<br>0x36016 | 0              | 0              | 1              | 1              | 1              | 1              | 1              | 0              | 0x7C    |

### Simulation Models - UMI Driver/Monitor

The current jtag\_drv (driver including display) / orcastra.v (jtag/umi convert) combination flips the data bus before receiving/presenting to/from the Big Endian based UMI interface converting it into a traditional Little Endian format. Therefore when writing a given register in simulation, the value presented to the simulation driver must be in Little Endian format. For example, if one wanted to enable User Slave Interrupt (USI\_IRQ, bit6) via the System Bus Interrupt Enable Register (IER) using the simulation driver provided, a write would need to be performed to UMI address 0x00012 according to the format conveyed in Table 2. This action results in the format conveyed in Table 3 at the external UMI interface boundary because the driver flips the bus.

Table 2. Simulation Driver - Little Endian View Setting Of USI\_IRQ Bit 6

|                                     | Pin/Wire<br>D7 | Pin/Wire<br>D6 | Pin/Wire<br>D5 | Pin/Wire<br>D4 | Pin/Wire<br>D3 | Pin/Wire<br>D2 | Pin/Wire<br>D1 | Pin/Wire<br>D0 | Numeric |

|-------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---------|

|                                     | LSB            |                |                |                |                |                |                | MSB            | Value   |

| System Bus<br>Int Enable<br>0x00012 | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0x2     |

Table 3. UMI Interface Setting Of USI IRQ Bit 6

|                                     | Pin/Wire<br>D7 | Pin/Wire<br>D6 | Pin/Wire<br>D5 | Pin/Wire<br>D4 | Pin/Wire<br>D3 | Pin/Wire<br>D2 | Pin/Wire<br>D1 | Pin/Wire<br>D0 | Numeric |

|-------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---------|

|                                     | LSB            |                |                |                |                |                |                | MSB            | Value   |

| System Bus<br>Int Enable<br>0x00012 | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0x2     |

# **Soft Registers**

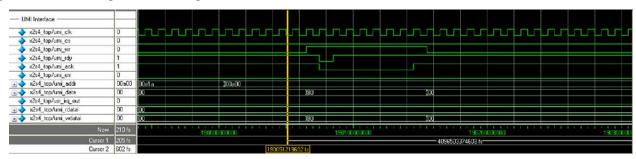

For FPGA soft registers, the approach is the same as for the hard block registers. They are defined in the register map conforming to Big Endian format rules and this is also the view at the external UMI interface of the device. The simulation driver view is Little Endian and so the user must make the conversion. Figure 6 shows a write operation to the Bridge Control register. In order to set b7, a value of 0x1 must be used inside the driver and a value 0f 0x80 appears at the UMI interface.

#### **Little Endian Address Bus Format**

The 18-bit UMI address bus operates in Little Endian format for all targets and accesses.

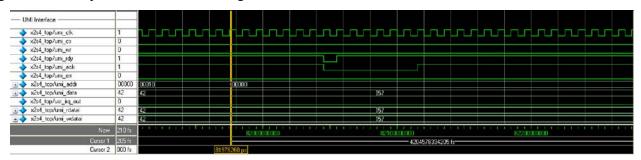

# **Simulation Timing Diagrams**

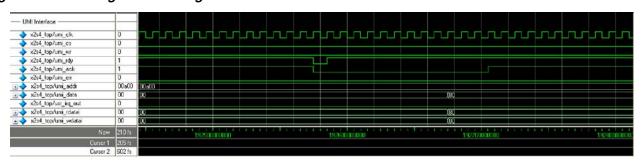

**UMI External Interface view.**

Figure 5. Read System Bus Device ID register - 0xEA

# Write Bridge Control Register - 0x01 Figure 6. Write Bridge Control Register

# Read Bridge Control Register - 0x01 Figure 7. Read Bridge Control Register

# X2S4 Reference Design Registers

Table 4. X2S4 Register Map Summary

| UMI_ADDR[17:0]    | Size Bytes | Description                       |

|-------------------|------------|-----------------------------------|

| 0x00000 - 0x0003f | 64         | System Bus internal registers     |

| 0x00410 - 0x0041f | 16         | SPI4 Transmit PLL                 |

| 0x00420 - 0x0042f | 16         | SPI4 System Data Clock (SDCK) PLL |

| 0x00430 - 0x0043f | 16         | SPI4 Receive PLL                  |

| 0x00440 - 0x0044f | 16         | SPI4 Hard Block registers         |

| 0x00800 - 0x008ff | 16         | SPI4 Soft registers               |

| 0x00900 - 0x009ff | 256        | Unused                            |

| 0x00a00 - 0x00bff | 512        | Bridge registers                  |

| 0x00e00 - 0x00fff | 2048       | MAC registers                     |

# **X2S4 Register Descriptions**

### **System Bus Internal Registers**

See Technical Note TN1085 - LatticeSC MPI/System Bus document for details regarding use and access of System Bus internal registers. Most of the System Bus internal registers do not require explicit initialization but two of the registers (Interrupt Cause Register - ICR, and Interrupt Enable Register - IER) are used in the interrupt scheme of the design and must be initialized if an external interrupt is expected.

For this X2S4 Bridging application, bits 1 (PCS\_IRQ) and 6 (USI\_IRQ) in the interrupt enable Register should be set and the remaining bits cleared. This is the highest level of interrupt consolidation in the design and results in I/O pin usr\_irq\_out being active if either of the two interrupts associated with these enable bits are active (see section "Interrupt Structure").

### **PLL Registers**

For descriptions of PLL internal registers see LatticeSC sysCLOCK PLL/DLL User's Guide - TN1098.

### SPI4.2 Hard Block Registers

For descriptions of SPI4.2 hard block internal registers see LatticeSC SPI4.2 Core MACO User's Guide - IPUG44.

### **SPI4.2 Soft Registers**

Table 5. SPI4.2 Soft Register Map Summary

| Register Description        | Mnemonic     | I/O Address | Reset Value |

|-----------------------------|--------------|-------------|-------------|

| SPI4 Rx Control             | S4RX_CTL     | 0x800       | 0x0C        |

| SPI4 Tx Control             | S4TX_CTL     | 0x801       | 0x0C        |

| SPI4 Status Threshold       | S4STAT_THRSH | 0x802       | 0x62        |

| SPI4 Rx Calendar Repetition | S4RXCAL_M    | 0x803       | 0x04        |

| SPI4 Rx Calendar Length     | S4RXCAL_LEN  | 0x804       | 0x01        |

| SPI4 Tx Calendar Repetition | S4TXCAL_M    | 0x805       | 0x04        |

| SPI4 Tx Calendar Length     | S4TXCAL_LEN  | 0x806       | 0x01        |

| SPI4 Error Enable Register  | S4EENREG     | 0x807-0x809 | 0x00        |

| SPI4 Error Register         | S4ERRREG     | 0x80a-0x80c | 0x00        |

### **SPI4.2 Register Descriptions**

Table 6. SPI4.2 Rx Control Registers

|     | S4RX_C       | TL   |         | Address: 0x800                                                                                                        |

|-----|--------------|------|---------|-----------------------------------------------------------------------------------------------------------------------|

| Bit | Name         | Туре | Default | Description                                                                                                           |

| 0   | S4RXRST      | R/W  | 0       | Receive Reset - Active high level sensitive reset resetting the entire SPI4 receiver.                                 |

| 1   | S4RXRST_AIL  | R/W  | 0       | Receive Reset AIL - Active high edge sensitive reset of the Adaptive Input Logic functions in the input DDR gear-box. |

| 2   | S4RXRST_DSKW | R/W  | 0       | Receive Reset Deskew - Active high level sensitive reset of the Deskew block.                                         |

| 3   | S4RXFDIP2E   | R/W  | 0       | Receive Force DIP2 Error - Active high DIP2 force error control.                                                      |

| 4   | S4RXLOOP     | R/W  | 0       | Receive Loop - Unused.                                                                                                |

| 5   | S4RXINTSTC   | R/W  | 0       | Receive Internal Status Control - Unused.                                                                             |

| 6   | S4RXRUN_AIL  | R/W  | 1       | Receive Run AIL - Active High control allowing AIL to track data edges.                                               |

| 7   | S4RXSTEN     | R/W  | 1       | Receive Status Enable - Active high enable for the Status Channel logic.                                              |

Table 7. SPI4.2 Tx Control Registers

|     | S4TXCTL     |      |         | Address: 0x801                                                                                                                                                                                                                          |

|-----|-------------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Name        | Туре | Default | Description                                                                                                                                                                                                                             |

| 0   | S4TXRST     | R/W  | 0       | Transmit Reset - Active high level sensitive reset resetting the entire SPI4 Transmit.                                                                                                                                                  |

| 1   | S4TXFIDLE   | R/W  | 0       | Transmit Force Idles - Active high control forcing the Tx to send SPI4 Idles.                                                                                                                                                           |

| 2:3 | S4TXFDIP4E  | R/W  | ОН      | Transmit Force DIP4 Error - Active high control forcing the Tx to send DIP4 errors. Bit 2 causes all control words to be sent with bad parity and bit 3 causes only control words ending data segments to be generated with bad parity. |

| 4   | S4TXEN_PACK | R/W  | 1       | Transmit Enable Packing - Active high control allowing the Tx to pack the SPI4 line.                                                                                                                                                    |

| 5   | S4TXSTEN    | R/W  | 1       | Transmit Status Enable - Active high enable for the Status Channel logic.                                                                                                                                                               |

| 6   | S4TXINTSTC  | R/W  | 0       | Transmit Internal Status Control - Unused.                                                                                                                                                                                              |

| 7   | Unused      | -    | -       | -                                                                                                                                                                                                                                       |

# Table 8. SPI4.2 Status Threshold Registers

|     | S4STAT_TH    | IRSH |         | Address: 0x802                                                                                                                          |

|-----|--------------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Name         | Туре | Default | Description                                                                                                                             |

| 0:2 | S4TXNUMDIP2  | R/W  | 011B    | Transmit Number Of DIP2 - Specifies the number of correct DIP2 code words that are required before declaring alignment.                 |

| 3   | Unused       | -    | -       | -                                                                                                                                       |

| 4:6 | S4TXNUMDIP2E | R/W  | 010B    | Transmit Number Of DIP2 Errors - Specifies the number of incorrect DIP2 code words that are required before declaring out of alignment. |

| 7   | Unused       | -    | -       | -                                                                                                                                       |

### Table 9. SPI4.2 Rx Calendar Repetition Register

|     | S4RXCAL   | _M   |         | Address: 0x803                                                                                                                                         |

|-----|-----------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Name      | Туре | Default | Description                                                                                                                                            |

| 0:7 | S4RXCAL_M | R/W  | 04H     | Receive Calendar Repetition - Specifies the number of times that the calendar sequence is repeated before the DIP2 code word and framing are inserted. |

### Table 10. SPI4.2 Rx Calendar Length Register

|     | S4RXCAL_    | LEN  |         | Address: 0x804                                                                                 |

|-----|-------------|------|---------|------------------------------------------------------------------------------------------------|

| Bit | Name        | Type | Default | Description                                                                                    |

| 0:7 | S4RXCAL_LEN | R/W  |         | Receive Calendar Length - Specifies the length of calendar sequence. This should be left at 1. |

# Table 11. SPI4.2 Tx Calendar Repetition Register

|     | S4TXCAL   | _M   |         | Address: 0x805                                                                                                                                          |

|-----|-----------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Name      | Type | Default | Description                                                                                                                                             |

| 0:7 | S4TXCAL_M | R/W  | 04H     | Transmit Calendar Repetition - Specifies the number of times that the calendar sequence is repeated before the DIP2 code word and framing are inserted. |

Table 12. SPI4.2 Calendar Length Register

|     | S4TXCAL_LEN |      |         | Address: 0x806                                                                                  |

|-----|-------------|------|---------|-------------------------------------------------------------------------------------------------|

| Bit | Name        | Туре | Default | Description                                                                                     |

| 0:7 | S4TXCAL_LEN | R/W  | 01H     | Transmit Calendar Length - Specifies the length of calendar sequence. This should be left at 1. |

Table 13. SPI4.2 Error Enable Register

|                   |     | S4EENREG   | Base Address: 0x807 |         |                                                                                            |

|-------------------|-----|------------|---------------------|---------|--------------------------------------------------------------------------------------------|

| Address<br>Offset | Bit | Name       | Туре                | Default | Description                                                                                |

| 0                 | 0:7 | S4EENREG_0 | R/W                 | ОH      | ODI4 E E II D''.( I '' I' I' I' I' I' I' I                                                 |

| 1                 | 0:7 | S4EENREG_1 | R/W                 | ОH      | SPI4 Error Enable - Bit for bit active high interrupt enables for the SPI4 error register. |

| 2                 | 0:5 | S4EENREG_2 | R/W                 | 0H      |                                                                                            |

| 2                 | 6:7 | Unused     | -                   | -       | -                                                                                          |

Table 14. SPI4.2 Error Registers

|                   |      | S4ERRREG       |      |         | Base Address: 0x80a                                                                                                                                                                                                                                 |

|-------------------|------|----------------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address<br>Offset | Bits | Name           | Туре | Default | Description                                                                                                                                                                                                                                         |

| 0                 | 0    | S4RXF1_PARERR  | COR  | 0       | Receive FIFO1 Parity Error - Unused.                                                                                                                                                                                                                |

| 0                 | 1    | S4RXF1FERR     | COR  | 0       | Enable Receive FIFO1 Full Error - Active high error indicating that RxFIFO1 has reached the full state (this should never occur).                                                                                                                   |

| 0                 | 2    | S4RXDSKWD      | COR  | 0       | Receive Deskewed - Active high error indicating that the deskew block has lost, or has not achieved a deskewed state.                                                                                                                               |

| 0                 | 3    | S4RXLT40_TRERR | COR  | 0       | Rx Less Than 40 Training Pattern Error - Active high error indicating that the Deskew block received less than 40 repetitions of the Training pattern during a time when it had previously not been deskewed.                                       |

| 0                 | 4    | S4RXLT10_TRERR | COR  | 0       | Receive Less Than 10 Training Pattern Error - Active high error indicating that the Deskew block received less than 10 repetitions of the Training pattern during a time when it was in the deskewed state.                                         |

| 0                 | 5    | S4RXAERR       | COR  | 0       | Receive Alignment Error - Active high error indicating that the receiver is out of alignment.                                                                                                                                                       |

| 0                 | 6    | S4RXD4ERR      | COR  | 0       | Receive RXDIP4 Error - Active high error indicating that the receiver has detected a DIP4 error.                                                                                                                                                    |

| 0                 | 7    | S4RXAIL_LOCK   | COR  | 0       | Receive AIL Lock Error - Active high error indicating that the AIL logic in the gear-boxes (IDDRX2A) have not locked on to a safe clock/data relationship.                                                                                          |

| 1                 | 0    | S4TXSDP2ERR    | COR  | 0       | Transmit Status DIP2 Error - Active high error indicating the transmit status block has detected a DIP2 error on status received on the status channel.                                                                                             |

| 1                 | 1    | S4TXSTAERR     | COR  | 0       | Transmit Status Alignment Error - Active high error indicating that the transmit status block is out-of-alignment.                                                                                                                                  |

| 1                 | 2    | S4TXF2_PARERR  | COR  | 0       | Transmit FIFO2 Parity Error - Unused.                                                                                                                                                                                                               |

| 1                 | 3    | S4TXBURST_ERR  | COR  | 0       | Transmit Burst Error - Active high error indicating transmitter has segmented a burst different than the burst size set through TxBLEN[5:0]. Ensures correct programming of TxF1AEBTHRSH[] which must be set to a value 2 greater than TxBLEN[5:0]. |

Table 14. SPI4.2 Error Registers (Continued)

|                   |      | S4ERRREG    |      |         | Base Address: 0x80a                                                                                                                                                                                                           |

|-------------------|------|-------------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address<br>Offset | Bits | Name        | Туре | Default | Description                                                                                                                                                                                                                   |

| 1                 | 4    | S4TXREM_ERR | COR  | 0       | Transmit Remainder Error - Active high error indicating that TxFIFO1 was written with a remainder of other than 4'b1111 during a cycle when 'TXEOP' was not active; a clear error condition.                                  |

| 1                 | 5    | S4TXF2FE    | COR  | 0       | Transmit FIFO2 Full Error - Active high error indicating that Tx FIFO2 has hit the full error state.                                                                                                                          |

| 1                 | 6    | S4TXF2E     | COR  | 0       | Transmit FIFO2 Empty Error - Active high error indicating that Tx FIFO2 has hit the empty error state (empty is also an error condition for this FIFO)                                                                        |

| 1                 | 7    | S4TXF1FE    | COR  | 0       | Transmit FIFO1 Full Error - Active high error indicating that Tx FIFO1 has hit the full error state.                                                                                                                          |

| 2                 | 0    | S4RXF2FE    | COR  | 0       | Receive FIFO2 Full Error - Active high error signal indicating that receive FIFO2 has reached the Full error state.                                                                                                           |

|                   |      |             |      |         | Receive SPI4 Protocol Errors - Active high error signals indicating that the receiver has seen a sequence of data and control words that are in violation of the SPI4 protocol.                                               |

| 2                 | 1:5  | 5 S4RS4ERR  | COR  | ОН      | RS4ERR[4] - A valid write to RxFIFO2 where less than 16 bytes are marked valid without an EOP active. SPI4 burst aligned and "or"ed into the 'RXDP4E' error lane through RxFIFO2 and is activated to mark the segment as bad. |

|                   |      |             |      |         | RS4ERR[3] - Data preceded by an idle. Error flag is raised.                                                                                                                                                                   |

|                   |      |             |      |         | RS4ERR[2] - Reserved Control Word. Error flag is raised.                                                                                                                                                                      |

|                   |      |             |      |         | RS4ERR[1] - Any EOP preceded by an idle.                                                                                                                                                                                      |

|                   |      |             |      |         | RS4ERR[0] - Any control word preceded by a payload control word.                                                                                                                                                              |

| 2                 | 6:7  | Unused      | -    | -       | -                                                                                                                                                                                                                             |

# **Bridge Registers**

Table 15. Bridge Register Map Summary

| Register Description                                    | Mnemonic        | I/O Address | Reset Value |

|---------------------------------------------------------|-----------------|-------------|-------------|

| Bridge Control Register 1                               | BRCREG          | 0xa00       | 0x02        |

| Bridge Ingress Almost Empty Threshold Register          | BRINGAETHRSH_L  | 0xa01       | 0xA0        |

| Bridge Ingress Almost Full Threshold Register           | BRINGAFTHRSH_L  | 0xa02       | 0x80        |

| Bridge Ingress Almost Empty/Full Threshold Register     | BRINGAEFTHRSH_H | 0xa03       | 0x54        |

| Bridge Egress Almost Empty Threshold Register           | BREGAETHRSH_L   | 0xa04       | 0xA0        |

| Bridge Egress Almost Full Threshold Register            | BREGAFTHRSH_L   | 0xa05       | 0x80        |

| Bridge Egress Almost Empty/Full Threshold Register      | BREGAEFTHRSH_H  | 0xa06       | 0x54        |

| Bridge Error Enable Register                            | BREENREG        | 0xa07       | 0x00        |

| Bridge Error Register                                   | BRERRREG        | 0xa08       | 0x00        |

| Bridge Control Register 2                               | BRCREG          | 0xa09       | 0xC0        |

| Bridge Statistics Counter 0 (pause packets received)    | BRSTATCTR0      | 0xb00-0xb07 | 0x00        |

| Bridge Statistics Counter 1 (packets received)          | BRSTATCTR1      | 0xb08-0xb0f | 0x00        |

| Bridge Statistics Counter 2 (pause packets transmitted) | BRSTATCTR2      | 0xb10-0xb17 | 0x00        |

| Bridge Statistics Counter 3 (packets transmitted)       | BRSTATCTR3      | 0xb18-0xb1f | 0x00        |

| Bridge Statistics Counter 4 (mac Tx paused)             | BRSTATCTR4      | 0xb20-0xb27 | 0x00        |

| Register Description                           | Mnemonic   | I/O Address | Reset Value |

|------------------------------------------------|------------|-------------|-------------|

| Bridge Statistics Counter 5 (spi4rx satisfied) | BRSTATCTR5 | 0xb28-0xb2f | 0x00        |

| Bridge Statistics Counter 6 (spi4tx satisfied) | BRSTATCTR6 | 0xb30-0xb37 | 0x00        |

# **Bridge Register Descriptions**

# Table 16. Bridge Control Register 1

|      | BCREG              |      |         | Address: 0xa00                                                                                                                                                                                   |

|------|--------------------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits | Name               | Туре | Default | Description                                                                                                                                                                                      |

| 0    | BRINGRST           | R/W  | 0       | Ingress FIFO Reset - Active high level sensitive reset resetting the Ingress FIFO.                                                                                                               |

| 1    | BREGRST            | R/W  | 0       | Egress FIFO Reset - Active high level sensitive reset resetting the Egress FIFO.                                                                                                                 |

| 2    | BRING_UP_PAUSE_REQ | R/W  | 0       | Ingress Microprocessor Pause Request - Active high level sensitive control forcing a pause for the ingress direction data flow (spi4 status output).                                             |

| 3    | BREG_UP_PAUSE_REQ  | R/W  | 0       | Egress Microprocessor Pause Request - Active high level sensitive control forcing a pause for the egress direction data flow (generates mac ctl pause frame).                                    |

| 4    | BRING_PASS_FCTL    | R/W  | 0       | Ingress Pass Flow Control - Active high signal that causes ingress direction flow control to be passed directly across the Bridge without waiting for a specific ingress bridge FIFO fill level. |

| 5    | BREG_PASS_FCTL     | R/W  | 0       | Egress Pass Flow Control - Active high signal that causes egress direction flow control to be passed directly across the Bridge without waiting for a specific egress bridge FIFO fill level.    |

| 6    | BRING_DROP         | R/W  | 1       | Ingress Drop - Active high control signal that causes ingress packets to be dropped when they are found to be received in error (spi4 dip4 and abort or internally detected missing sop or eop.  |

| 7    | BREG_DROP          | R/W  | 0       | Egress Drop - Active high control signal that causes egress packets to be dropped when they are found to be received in error (mac CRC error or internally detected missing sop or eop.          |

## Table 17. Bridge Ingress Almost Empty Threshold Register Low Byte

|      | BRINGAETHRS       | H_L | Address: 0xa01 |                                                  |

|------|-------------------|-----|----------------|--------------------------------------------------|

| Bits | Name Type Default |     |                | Description                                      |

| 0:7  | BRINGAETHRSH_L    | R/W | A0H            | Ingress Almost Empty Threshold Register Low Byte |

### Table 18. Bridge Ingress Almost Full Threshold Register Low Byte

|      | BRINGAFTHRSI      | H_L | Address: 0xa02 |                                                 |

|------|-------------------|-----|----------------|-------------------------------------------------|

| Bits | Name Type Default |     |                | Description                                     |

| 0:7  | BRINGAFTHRSH_L    | R/W | 80H            | Ingress Almost Full Threshold Register Low Byte |

### Table 19. Bridge Ingress Almost Empty/Full Threshold Register High Bits

|      | BRINGAEFTHRS   | H_H  | Address: 0xa03 |                                                        |

|------|----------------|------|----------------|--------------------------------------------------------|

| Bits | Name           | Туре | Default        | Description                                            |

| 0:2  | BRINGAETHRSH_H | R/W  | 010B           | Ingress Almost Empty Threshold Register High Bits 10:8 |

| 3:5  | BRINGAFTHRSH_H | R/W  | 101B           | Ingress Almost Full Threshold Register High Bits 10:8  |

| 6:7  | Unused         | -    | -              | -                                                      |

# Table 20. Bridge Egress Almost Empty Threshold Register Low Byte

|      | BREGAETHRS    | H_L  | Address: 0xa04 |                                                 |

|------|---------------|------|----------------|-------------------------------------------------|

| Bits | Name          | Туре | Default        | Description                                     |

| 0:7  | BREGAETHRSH_L | R/W  | A0H            | Egress Almost Empty Threshold Register Low Byte |

### Table 21. Bridge Egress Almost Full Threshold Register Low Byte

|      | BREGAFTHRS    | 1_L  | Address: 0xa05 |                                                |

|------|---------------|------|----------------|------------------------------------------------|

| Bits | Name          | Туре | Description    |                                                |

| 0:7  | BREGAFTHRSH_L | R/W  | 80H            | Egress Almost Full Threshold Register Low Byte |

# Table 22. Bridge Egress Almost Empty/Full Threshold Register High Bits

|      | BREGAEFTHRS   | H_H  | Address: 0xa06 |                                                         |

|------|---------------|------|----------------|---------------------------------------------------------|

| Bits | Name          | Туре | Default        | Description                                             |

| 0:2  | BREGAETHRSH_H | R/W  | 010B           | Egress Almost Empty Threshold Register High Bits (10:8) |

| 3:5  | BREGAFTHRSH_H | R/W  | 101B           | Egress Almost Full Threshold Register High Bits (10:8)  |

| 6:7  | Unused        | -    | -              | -                                                       |

# Table 23. Bridge Error Enable Register

|      | BREENREG             |      | Address: 0xa07 |                                                                  |

|------|----------------------|------|----------------|------------------------------------------------------------------|

| Bits | Name                 | Туре | Default        | Description                                                      |

| 0    | BRIBFE_EN            | R/W  | 0              | Ingress Buffer Full Error Enable - Active high interrupt enable. |

| 1    | BREBFE_EN            | R/W  | 0              | Egress Buffer Full Error Enable - Active high interrupt enable.  |

| 2    | BRING_MSOP_EN        | R/W  | 0              | Ingress Missing SOP Error - Active high interrupt enable.        |

| 3    | BRING_MEOP_EN        | R/W  | 0              | Ingress Missing EOP Error - Active high interrupt enable.        |

| 4    | BRING_PKT_DROPPED_EN | R/W  | 0              | Ingress Packet Dropped - Active high interrupt enable.           |

| 5    | BREG_MSOP_EN         | R/W  | 0              | Egress Missing SOP Error - Active high interrupt enable.         |

| 6    | BREG_MEOP_EN         | R/W  | 0              | Egress Missing EOP Error - Active high interrupt enable.         |

| 7    | BREG_PKT_DROPPED_EN  | R/W  | 0              | Egress Packet Dropped - Active high interrupt enable.            |

# Table 24. Bridge Error Register

|      | BRERREG           |      | Address: 0xa08 |                                                                                                                                                                                                               |

|------|-------------------|------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits | Name              | Туре | Default        | Description                                                                                                                                                                                                   |

| 0    | BRIBFE            | COR  | 0              | Ingress Buffer Full Error - Active high error indicating that the Ingress Buffer has reached the full level.                                                                                                  |

| 1    | BREBFE            | COR  | 0              | Egress Buffer Full Error - Active high error indicating that the Egress Buffer has reached the full level.                                                                                                    |

| 2    | BRING_MSOP        | COR  | 0              | Ingress Missing SOP Error - Active high error indicating that a packet was received without an SOP. All data is dropped up to the next valid SOP.                                                             |

| 3    | BRING_MEOP        | COR  | 0              | Ingress Missing EOP Error - Active high error indicating that a packet was received without an EOP. If DROP is enabled, the packet is dropped. Otherwise, an EOP is inserted and the packet is marked as bad. |

| 4    | BRING_PKT_DROPPED | COR  | 0              | Ingress Packet Dropped - Active high error indicating that a packet has been dropped.                                                                                                                         |

# **Lattice Semiconductor**

|      | BRERREG          |      | Address: 0xa08 |                                                                                                                                                                                                            |

|------|------------------|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits | Name             | Туре | Default        | Description                                                                                                                                                                                                |

| 5    | BREG_MSOP        | COR  | 0              | Egress Missing SOP Error - Active high error indicating that a packet was received without an SOP. All data is dropped up to the next valid SOP.                                                           |

| 6    | BREG_MEOP        | COR  | 0              | Egress Missing EOP Error - Active high error indicating that a packet was received without an EOP. If DROP is enabled, the packet is dropped otherwise an EOP is inserted and the packet is marked as bad. |

| 7    | BREG_PKT_DROPPED | COR  | 0              | Egress Packet Dropped - Active high error indicating that a packet has been dropped.                                                                                                                       |

# Table 25. Bridge Control Register

|      | BCREG2        |      | Address: 0xa09 |                                                                                                                                               |

|------|---------------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Bits | Name          | Type | Default        | Description                                                                                                                                   |

| 0    | BRING_EN_FCTL | R/W  | 1              | Ingress Enable Flow Control - Active high control signal that enables the Ingress Buffer Controller to flow control the SPI4 input interface. |

| 1    | BREGRST       | R/W  | 1              | Egress Enable Flow Control - Active high control signal that enables the Ingress Buffer Controller to flow control the MAC input interface.   |

| 2:7  | Unused        | -    | -              | -                                                                                                                                             |

# Table 26. Bridge Statistics Counter 0

|                   |      | BRSTATCTR0   | Base Address: 0xb00 |         |                                                                                      |

|-------------------|------|--------------|---------------------|---------|--------------------------------------------------------------------------------------|

| Address<br>Offset | Bits | Name         | Туре                | Default | Description                                                                          |

| 0                 | 0:7  | BRSTATCTR0_0 | R                   | 0H      | Statistics Counter 0 - A 48b rollover counter                                        |

| 1                 | 0:7  | BRSTATCTR0_1 | R                   | 0H      | that counts the number of Pause packets received. A read of the base address latches |

| 2                 | 0:7  | BRSTATCTR0_2 | R                   | 0H      | the entire 48b counter for subsequent read-                                          |

| 3                 | 0:7  | BRSTATCTR0_3 | R                   | 0H      | ing of the remaining bytes of the counter.                                           |

| 4                 | 0:7  | BRSTATCTR0_4 | R                   | 0H      |                                                                                      |

| 5                 | 0:7  | BRSTATCTR0_5 | R                   | 0H      |                                                                                      |

# Table 27. Bridge Statistics Counter 1

|                   |      | BRSTATCTR1   | Base Address: 0xb08 |         |                                                                                        |

|-------------------|------|--------------|---------------------|---------|----------------------------------------------------------------------------------------|

| Address<br>Offset | Bits | Name         | Туре                | Default | Description                                                                            |

| 0                 | 0:7  | BRSTATCTR1_0 | R                   | 0       | Statistics Counter 1 - A 48b rollover counter                                          |

| 1                 | 0:7  | BRSTATCTR1_1 | R                   | 0       | that counts the number of packets received excluding pause packets. A read of the base |

| 2                 | 0:7  | BRSTATCTR1_2 | R                   | 0       | address latches the entire 48b counter for                                             |

| 3                 | 0:7  | BRSTATCTR1_3 | R                   | 0       | subsequent reading of the remaining bytes of the counter.                              |

| 4                 | 0:7  | BRSTATCTR1_4 | R                   | 0       |                                                                                        |

| 5                 | 0:7  | BRSTATCTR1_5 | R                   | 0       |                                                                                        |

Table 28. Bridge Statistics Counter 2

|                   |      | BRSTATCTR2   | Base Address: 0xb10 |         |                                                                                 |

|-------------------|------|--------------|---------------------|---------|---------------------------------------------------------------------------------|

| Address<br>Offset | Bits | Name         | Туре                | Default | Description                                                                     |

| 0                 | 0:7  | BRSTATCTR2_0 | R                   | 0       | Statistics Counter 2 - A 48b rollover counter                                   |

| 1                 | 0:7  | BRSTATCTR2_1 | R                   | 0       | that counts the number of pause packets transmitted. A read of the base address |

| 2                 | 0:7  | BRSTATCTR2_2 | R                   | 0       | latches the entire 48b counter for subsequent                                   |

| 3                 | 0:7  | BRSTATCTR2_3 | R                   | 0       | reading of the remaining bytes of the counter.                                  |