# LatticeECP2/M SERDES/PCS Usage Guide

July 2021 Technical Note FPGA-TN-02254

#### Introduction to PCS

The LatticeECP2M<sup>™</sup> FPGA family combines a high-performance FPGA fabric, high-performance I/Os and large embedded RAM in a single industry-leading architecture. All LatticeECP2M devices also feature up to 16 channels of embedded SERDES with associated Physical Coding Sublayer (PCS) logic. The PCS logic can be configured to support numerous industry-standard, high-speed data transfer protocols.

Each channel of PCS logic contains dedicated transmit and receive SERDES for high-speed full-duplex serial data transfers at data rates up to 3.125 Gbps. The PCS logic in each channel can be configured to support an array of popular data protocols including Ethernet (1GbE and SGMII), PCI Express, CPRI, and OBSAI. In addition, the protocol-based logic can be fully or partially bypassed in a number of configurations to allow users flexibility in designing their own high-speed data interface.

The PCS also provides bypass modes that allow for a direct 8-bit or 10-bit interface from the SERDES to the FPGA logic. Each SERDES pin can be independently DC-coupled and can allow for both high-speed and low-speed operation on the same SERDES pin for such applications as Serial Digital Video.

#### **Features**

- Up to 16 Channels of High-Speed SERDES

- 250 Mbps to 3.125 Gbps per channel

- 3.125Gbps operation with low 100mW power per channel

- Receive equalization and transmit pre-emphasis for small form factor backplane operation

- Supports PCI Express, Ethernet (1GbE and SGMII) plus multiple other standards

- Supports user specified generic 8b10b mode

- Beacon support for PCI Express

- Out-of-band signal interface for low speed inputs (video application)

- Multiple Clock Rate Support

- Separate reference clocks for each PCS quad allow easy handling of multiple protocol rates on a single device

- Full Function Embedded Physical Coding Sub-layer (PCS) Logic Supporting Industry Standard Protocols

- Up to 16 channels of full-duplex data supported per device

- Multiple protocol support on one chip

- Supports popular 8b10b based packet protocols

- SERDES Only mode allows direct 8- or 10-bit interface to FPGA logic

- Gigabit Ethernet Support

- IEEE 1000BASE-X compliant

- 8b10b encoding/decoding

- Insertion of /I2/ symbols into the receive data stream for auto-negotiation support

- Comma character word alignment

- Clock Tolerance Compensation circuit

- PCI Express Support

- x1 to x4 support in one PCS quad

- Integrated Word aligner

- 8b10b encoding/decoding

- Clock Tolerance Compensation circuit

- Electrical Idle and Receiver Detection support

- Support for Beacon Transmission and Beacon Detection

© 2021 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

- Multiple Protocol Compliant Clock Tolerance Compensation (CTC) Logic

- Compensates for frequency differential between reference clock and received data rate

- Allows user defined Skip pattern of 1, 2, or 4 bytes in length

- Integrated Loopback Modes for System Debugging

- Three loopback modes are provided for system debugging

### **Supported Standards**

The supported standards are listed in Table 18-1.

Table 18-1. Supported SERDES Standards (Fully Supported)

| Standard                        | Rates (Mbps)       | REFCLK (MHz)       | FPGA CLK (MHz)     | Encoding        | Signal Type |

|---------------------------------|--------------------|--------------------|--------------------|-----------------|-------------|

| PCI Express                     | 2500               | 100                | 250                | 8b10b           | CML         |

| GbE/SGMII                       | 1250               | 125                | 125                | 8b10b           | CML         |

| Generic 8b10b                   | 250 to 3125        | 25 to 312.5        | 25 to 312.5        | 8b10b/None      | CML         |

| 10-bit SERDES Only <sup>1</sup> | 250 to 3125        | 25 to 312.5        | 25 to 312.5        | None            | CML         |

| 8-bit SERDES Only1              | 250 to 3125        | 25 to 312.5        | 25 to 312.5        | None            | CML         |

| SD-SDI <sup>2</sup>             | 143, 177, 270, 360 | 14.3, 17.7, 27, 36 | 143, 177, 135, 180 | SMPTE scrambled | CML         |

| HD-SDI                          | 1483.5, 1485       | 148.35, 148.5      | 148.35, 148.5      | SMPTE scrambled | CML         |

| CPRI                            | 614.4<br>1228.8    | 61.44<br>122.88    | 61.44<br>122.88    | 8b10b           | CML         |

<sup>8-</sup>bit SERDES Only Mode and 10-bit SERDES Only Mode bypass the Link Align/Comma Align, 8b10b encoder/decoder and the CTC. It does not bypass the CDR.

It is possible to support XAUI, SRIO, OBSAI, CPRI, 1XFC, 2XFC, PICMG 3.1, PICMG 3.4, PICMG 3.5 and 3G-SDI standards with the SERDES modes specified above. Contact Lattice Semiconductor Technical Support Group for additional information.

#### **Architecture Overview**

The PCS logic is arranged in quads containing logic for four independent full-duplex data channels. Table 18-2 shows the availability of SERDES/PCS quads for each device in the LatticeECP2M family.

Table 18-2. SERDES/PCS Quads per LatticeECP2M Device

| Device   | ECP2M20 | ECP2M35 | ECP2M50 | ECP2M70 | ECP2M100 |

|----------|---------|---------|---------|---------|----------|

| Quad URC | Yes     | Yes     | Yes     | Yes     | Yes      |

| Quad LRC | _       | _       | Yes     | Yes     | Yes      |

| Quad ULC | _       | _       | _       | Yes     | Yes      |

| Quad LLC | _       | _       | _       | Yes     | Yes      |

#### **PCS Quad**

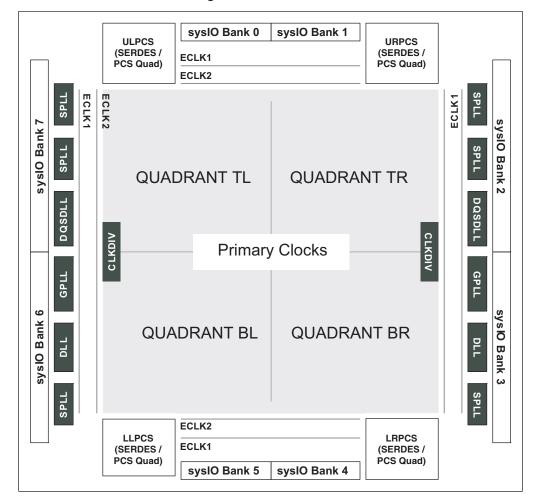

Figure 18-1 is a layout of a LatticeECP2M device showing the arrangement of PCS quads on the device (the largest array containing 4 quads is shown. Other devices have fewer quads).

<sup>2.</sup> Serial Digital Interface (SDI) for Standard Definition (SD): 143Mbps, 177Mbps bypasses the SERDES/PCS Block. The clock and data come in to the FPGA through the RX pins but get into the FPGA core via the BSCAN path. CDR is done in the FPGA core. In the transmit direction, decimation is used for these "low" bit rates. To do the CDR in the FPGA, reference clock of 14.3MHz and 17.7MHz are required respectively. 270Mbps is the most common frequency. This will go through the 10-bit data path.

Figure 18-1. LatticeECP2M70/100 Block Diagram

Every quad can be programmed into one of several protocol based modes. Each quad requires its own reference clock which can be sourced externally from package pins or internally from the FPGA logic.

Since each quad has its own reference clock, different quads can support different standards on the same chip. This feature makes the LatticeECP2M family of devices ideal for bridging between different standards.

PCS quads are not dedicated solely to industry standard protocols. Each quad (and each channel within a quad) can be programmed for many user defined data manipulation modes. For example, modes governing user-defined word alignment, and clock tolerance compensation can be programmed for non-protocol operation.

#### **PCS Quad and Channels**

Each quad on a device supports up to four channels of full-duplex data. The user can utilize anywhere from one to four channels in a quad depending on the application. Many options can be set by the user for each channel independently within a given quad.

Figure 18-1 also shows an example of a device with four PCS quads which contain a total of 16 PCS channels. Quads are named according to the location of the respective quad on the LatticeECP2M array: URPCS (Upper Right PCS), ULPCS (Upper Left PCS), LRPCS (Lower Right PCS), LLPCS (Lower Left PCS).

#### Per Channel PCS/FPGA Interface Ports

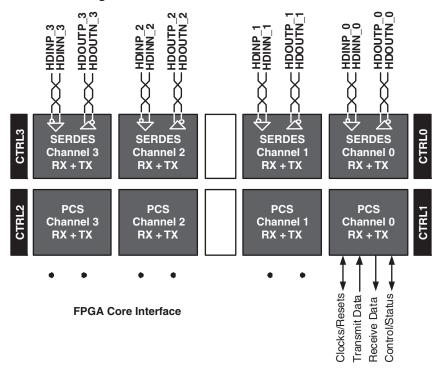

All PCS quads regardless of chosen mode have the same external high speed serial interface at the package pins. However, every PCS mode has its own unique list of input/output ports from/to the FPGA logic appropriate to the protocol chosen for the quad. A detailed description of the quad input/output signals for each mode is provided in this document. A simplified diagram showing the channels within a single quad is shown in Figure 18-2.

Figure 18-2. PCS Quad Block Diagram

#### Locating a PCS Quad

LatticeECP2M-50 and larger devices include two to four PCS Quads.

Users can locate each PCS Quad in a desired location using the LOCATE preference in the preference file. Below is an example of the preference, LOCATE.

LOCATE COMP "PCS instantiation 1" SITE URPCS ;

#### **Detailed Channel Block Diagram**

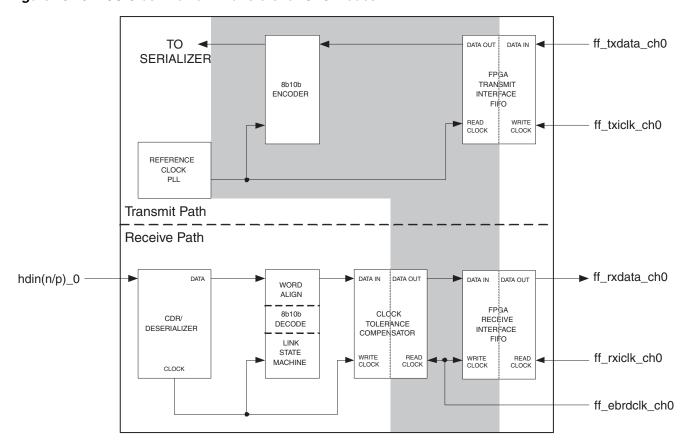

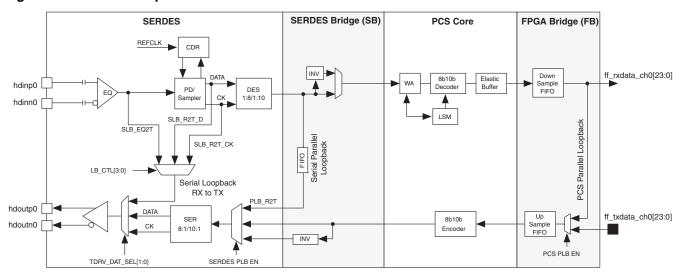

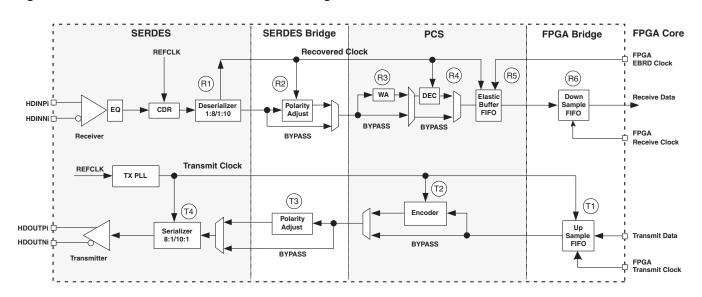

Figure 18-3 is a detailed block diagram representation of the major functionality in a single channel of the LatticeECP2M SERDES/PCS. This diagram shows all the major blocks and the majority of the control and status signals that are visible to the user logic in the FPGA. This diagram also shows the major sub-blocks in the channel-SERDES, SERDES Bridge, PCS Core and the FPGA Bridge.

SERDES SERDES Bridge PCS Core FPGA Bridge (FB) FPGA Core (SB) oob out ch0 BSRPAD Logic rx sdi en ch0 LOS ff\_rlos\_lo\_ch0 Recovered (Byte) Clock ffc\_sb\_inv\_rx\_ch0 REFCLK ff rxfullclk ch0 U p/Dn ff\_rxhalfclk\_ch0 INV 1/4 ff rxatrclk ch0 hdinn0 PD/ DES Down 8B/10B ff rxdata[23:0] ch0 Sample FIFO SB\_BYPASS LSM ff rxiclk ch0 ff\_ebrd\_clk\_ch0 ffs\_cc\_overrun\_ch0 ffs\_cc\_underrun\_ch0 FB\_LOOF \_DAT\_SEU1 TXPLL ffc\_signal\_detect\_ch0 ffs\_ls\_sync\_status\_ch0 enable\_cg\_align\_ch0 ff txfullclk **LDRV** ff\_txhalfclk ff\_txqtrclk hdoutp0 [ 8b/10b ff txdata[23:0] ch0 SER hdoutn0 INV < ff\_txiclk\_ch0 BYPASS tx sdi en ■ BSTPAD ffc pcie det en ch0 ffc pcie ct ch0 ffc pcie con ch0 ffc\_pcie\_done\_ch0

Figure 18-3. LatticeECP2M SERDES/PCS Detailed Channel Block Diagram

A general description of the FPGA interface signals follows.

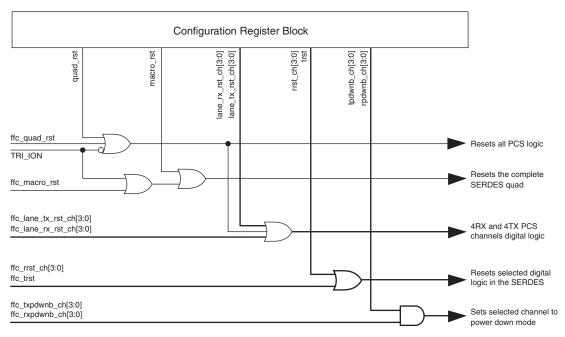

#### **Clocks and Resets**

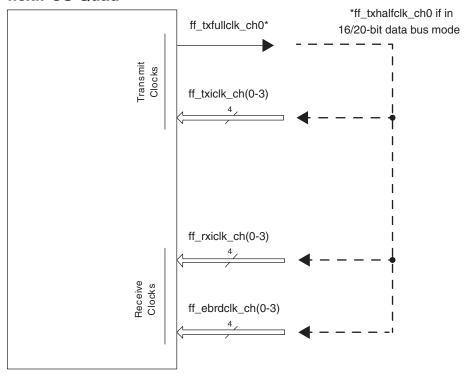

A PCS quad supplies per channel locked reference clocks and per channel recovered receive clocks to the FPGA logic interface. Each PCS quad provides these clocks on both primary and secondary FPGA clock routing. The PCS/FPGA interface also has ports for the transmit and receive clocks supplied from the FPGA fabric for all four channels in each quad.

Each quad has reset inputs to force reset of both the SERDES and PCS logic in a quad or just the SERDES. In addition, separate resets dedicated for the PCS logic are provided for each channel for both the transmit and receive directions.

#### **Transmit Data Bus**

The signals for the transmit data path are from the FPGA to the FPGA Bridge in the PCS Block. For high-speed standards, the datapath can be geared 2:1 to the internal PCS data path, which is 8 bits wide (+ control/status signals). The highest speed of the interface for PCI Express x1 is 250MHz in non-geared mode. With gearing (i.e. a 16-bit wide data path), the maximum speed is 156.25MHz (for XAUI 4x channel mode). The SERDES and PCS will support data rates up to 3.125Gbps data that correspond to an interface speed of 156.25MHz (with 2:1 gearing).

#### **Receive Data Bus**

The signals for the receive path are from the FPGA Bridge in the PCS Block to the FPGA. The data path may be geared 2:1 to the internal PCS data path which is 8 bits wide. It is possible to disable the gearing via a software register bit, in which case, the bus widths are halved. When the data is geared, the lower bits (ff\_rx\_d[9:0]) are the octet that has been received first and the higher bits (ff\_rx\_d[19:10]) are the octet that has been received second. If the data is not geared, the lower bits ((ff\_rx\_d[9:0]) are the active bits and the higher bits should not be used.

Table 18-3. Data Bus Usage by Mode

| Data Bus       |                                                         |                                    |                         |                               |       |                   |          |  |

|----------------|---------------------------------------------------------|------------------------------------|-------------------------|-------------------------------|-------|-------------------|----------|--|

| PCS Cell Name⁵ | G8B10B                                                  | CPRI                               | PCI Express             | GIGE                          | 8BSER | 10BSER            | SDI      |  |

| FF_TX_D_0_0    |                                                         |                                    |                         | ff_txdata_ch0[0]              |       |                   |          |  |

| FF_TX_D_0_1    |                                                         | ff_txdata_ch0[1]                   |                         |                               |       |                   |          |  |

| FF_TX_D_0_2    |                                                         |                                    |                         | ff_txdata_ch0[2]              |       |                   |          |  |

| FF_TX_D_0_3    |                                                         |                                    |                         | ff_txdata_ch0[3]              |       |                   |          |  |

| FF_TX_D_0_4    |                                                         |                                    |                         | ff_txdata_ch0[4]              |       |                   |          |  |

| FF_TX_D_0_5    |                                                         |                                    |                         | ff_txdata_ch0[5]              |       |                   |          |  |

| FF_TX_D_0_6    |                                                         |                                    |                         | ff_txdata_ch0[6]              |       |                   |          |  |

| FF_TX_D_0_7    |                                                         |                                    |                         | ff_txdata_ch0[7]              |       |                   |          |  |

| FF_TX_D_0_8    |                                                         |                                    | ff_tx_k_cntrl_ch0[0]    |                               | GND   | ff_txdata         | _ch0[8]  |  |

| FF_TX_D_0_9    |                                                         | ff_force_disp                      | o_ch0[0] ] <sup>1</sup> | GND                           |       | ff_txdata         | _ch0[9]  |  |

| FF_TX_D_0_10   |                                                         | ff_disp_sel_                       | _ch0[0] ] <sup>1</sup>  | ff_xmit_ch0[0] ] <sup>2</sup> |       | GND               |          |  |

| FF_TX_D_0_11   | G                                                       | iND                                | ff_pci_ei_en_ch0[0]     | ff_correct_disp_ch0[0]        |       | GND               |          |  |

| FF_TX_D_0_12   |                                                         |                                    | ff_txdata_ch            | 0[8]                          |       | ff_txdata         | _ch0[10] |  |

| FF_TX_D_0_13   |                                                         |                                    | ff_txdata_ch            | 0[9]                          |       | ff_txdata         | _ch0[11] |  |

| FF_TX_D_0_14   |                                                         |                                    | ff_txdata_ch(           | 0[10]                         |       | ff_txdata         | _ch0[12] |  |

| FF_TX_D_0_15   |                                                         |                                    | ff_txdata_ch(           | • •                           |       | ff_txdata         | _ch0[13] |  |

| FF_TX_D_0_16   |                                                         | ff_txdata_ch0[12] ff_txdat         |                         |                               |       |                   |          |  |

| FF_TX_D_0_17   |                                                         | ff_txdata_ch0[13] ff_txda          |                         |                               |       |                   |          |  |

| FF_TX_D_0_18   |                                                         | ff_txdata_ch0[14] ff_tx            |                         |                               |       |                   |          |  |

| FF_TX_D_0_19   |                                                         |                                    | ff_txdata               | _ch0[17]                      |       |                   |          |  |

| FF_TX_D_0_20   |                                                         |                                    | ff_tx_k_cntrl_ch0[1]    |                               | GND   | ff_txdata         | _ch0[18] |  |

| FF_TX_D_0_21   |                                                         | ff_force_disp                      | o_ch0[1] ] <sup>1</sup> | GND                           |       | ff_txdata_ch0[19] |          |  |

| FF_TX_D_0_22   |                                                         | ff_disp_sel_                       |                         | ff_xmit_ch0[1]] <sup>2</sup>  |       | GND               |          |  |

| FF_TX_D_0_23   | G                                                       | iND                                | ff_pci_ei_en_ch0[1]     | ff_correct_disp_ch0[1]        |       | GND               |          |  |

| FF_RX_D_0_0    |                                                         |                                    |                         | ff_rxdata_ch0[0]              |       |                   |          |  |

| FF_RX_D_0_1    |                                                         |                                    |                         | ff_rxdata_ch0[1]              |       |                   |          |  |

| FF_RX_D_0_2    |                                                         |                                    |                         | ff_rxdata_ch0[2]              |       |                   |          |  |

| FF_RX_D_0_3    |                                                         |                                    |                         | ff_rxdata_ch0[3]              |       |                   |          |  |

| FF_RX_D_0_4    |                                                         |                                    |                         | ff_rxdata_ch0[4]              |       |                   |          |  |

| FF_RX_D_0_5    |                                                         |                                    |                         | ff_rxdata_ch0[5]              |       |                   |          |  |

| FF_RX_D_0_6    |                                                         |                                    |                         | ff_rxdata_ch0[6]              |       |                   |          |  |

| FF_RX_D_0_7    |                                                         | ff_rxdata_ch0[7]                   |                         |                               |       |                   |          |  |

| FF_RX_D_0_8    | ff_rx_k_cntrl_ch0[0] NC                                 |                                    |                         |                               |       | ff_rxdata         |          |  |

| FF_RX_D_0_9    | ff_disp_err_ch0[0] ff_rxstatus0_ch0[0]                  |                                    |                         | ff_disp_err_ch0[0]            | NC    | ff_rxdata         | _ch0[9]  |  |

| FF_RX_D_0_10   | ff_cv_ch0[0] ] <sup>3</sup>                             |                                    |                         |                               | NC    |                   |          |  |

| FF_RX_D_0_11   | NC ff_rxstatus2_ch0[0] ff_rx_even_ch0[0] ] <sup>4</sup> |                                    |                         |                               |       |                   |          |  |

| FF_RX_D_0_12   |                                                         | ff_rxdata_ch0[8]                   |                         |                               |       |                   |          |  |

| FF_RX_D_0_13   |                                                         | ff_rxdata_ch0[9] ff_rxdata_ch0[11] |                         |                               |       |                   |          |  |

| FF_RX_D_0_14   |                                                         |                                    | ff_rxdata_ch(           |                               |       | ff_rxdata         |          |  |

| FF_RX_D_0_15   |                                                         |                                    | ff_rxdata_ch(           |                               |       | ff_rxdata         |          |  |

| FF_RX_D_0_16   |                                                         |                                    | ff_rxdata_ch(           |                               |       | ff_rxdata         |          |  |

| FF_RX_D_0_17   |                                                         |                                    | ff_rxdata_ch(           | 0[13]                         |       | ff_rxdata         | _ch0[15] |  |

#### Table 18-3. Data Bus Usage by Mode (Continued)

| Data Bus<br>PCS Cell Name⁵ | G8B10B                      | CPRI              | PCI Express         | GIGE                | 8BSER | 10BSER    | SDI      |

|----------------------------|-----------------------------|-------------------|---------------------|---------------------|-------|-----------|----------|

| FF_RX_D_0_18               |                             |                   | ff_rxdata           | _ch0[16]            |       |           |          |

| FF_RX_D_0_19               |                             | ff_rxdata_ch0[15] |                     |                     |       |           |          |

| FF_RX_D_0_20               |                             |                   | ff_rxdata           | _ch0[18]            |       |           |          |

| FF_RX_D_0_21               | ff_disp_                    | err_ch0[1]        | ff_rxstatus0_ch0[1] | ff_disp_err_ch0[1]  | NC    | ff_rxdata | _ch0[19] |

| FF_RX_D_0_22               | ff_cv_ch0[1] ] <sup>3</sup> |                   |                     |                     |       | NC        |          |

| FF_RX_D_0_23               | 1                           | VC                | ff_rxstatus2_ch0[1] | ff_rx_even_ch0[1]]4 |       | NC        |          |

- 1. The force\_disp signal will force the disparity for the associated data word on bits [7:0] to the column selected by the tx\_disp\_sel signal. If disp\_sel is a one, the 10-bit code is taken from the 'current RD+' column (positive disparity). If the tx\_disp\_sel is a zero, the 10-bit code is taken from the 'current RD-' (negative disparity) column.

- 2. The auto-negotiation state machine generates the signal xmit. It is used to interact with the GIGE Idle State Machine in the hard logic.

- 3. When there is a code violation, the packet PCS 8b10b decoder will replace the output from the decoder with hex EE and K asserted (K=1 and d=EE is not part of the 8b10b coding space).

- 4. rx\_even is a signal generated by the GIGE Link State Machine for the use of the GIGE Auto-negotiation and Receive State Machines (which is part of the IP core).

- 5. FF\_TX\_D\_0\_0: FPGA Fabric Transmit Data Bus Channel 0 Bit 0.

#### Control

Each mode has its own set of control signals which allows direct control of various PCS features from the FPGA logic. In general, each of these control inputs duplicate the effect of writing to a corresponding control register bit or bits. The ispLEVER® design tools give the user the option to bring these ports out to the FPGA interface.

#### **Status**

Each mode has its own set of status or alarm signals that can be monitored by the FPGA logic. In general, each of these status outputs correspond to a specific status register bit or bits. The ispLEVER design tools give the user the option to bring these port out to the PCS FPGA interface. Refer to the Mode Specific Control/Status Signals section for detailed information about control and status signals.

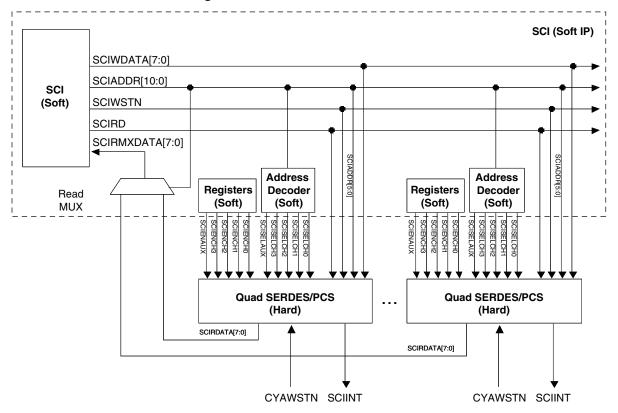

#### SCI (SERDES Client Interface) Bus

The SERDES Client Interface (SCI) is a soft IP that allow the SERDES/PCS Quad block to be controlled by registers as oppose to the configuration memory cells. It is a simple register configuration interface.

#### **Using This Technical Note**

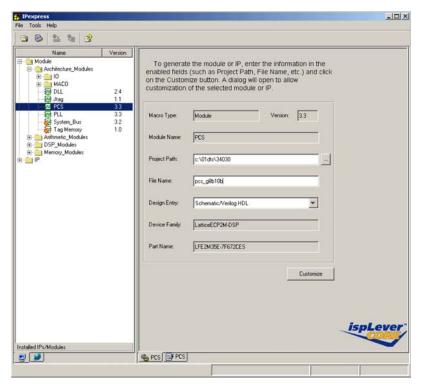

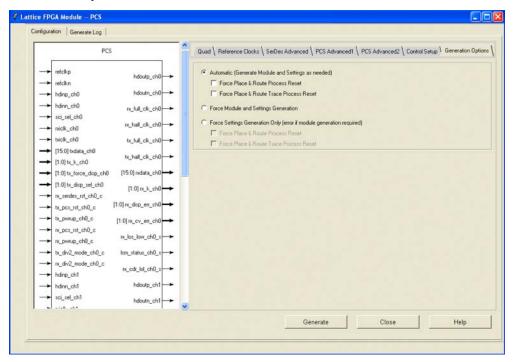

The ispLEVER design tools from Lattice support all modes of the PCS. Most modes are dedicated to applications for a specific industry standard data protocol. Other modes are more general purpose modes which allow a user to define their own custom application settings. ispLEVER design tools allow the user to define the mode for each quad in their design. This document describes operation of the SERDES and PCS for all modes supported by isp-LEVER. If you are using Lattice Diamond™ design software, see Appendix E.

This document provides a thorough description of the complete functionality of the embedded SERDES and associated PCS logic. Electrical and Timing Characteristics of the embedded SERDES are provided in the LatticeECP2/M Family Data Sheet. Operation of the PCS logic is provided in the PCS section. A table of all status and control registers associated with the SERDES and PCS logic which can be accessed via the SCI Bus is provided in the Memory Map section. Package pinout information is provided in the Architecture section of the LatticeECP2/M Family Data Sheet.

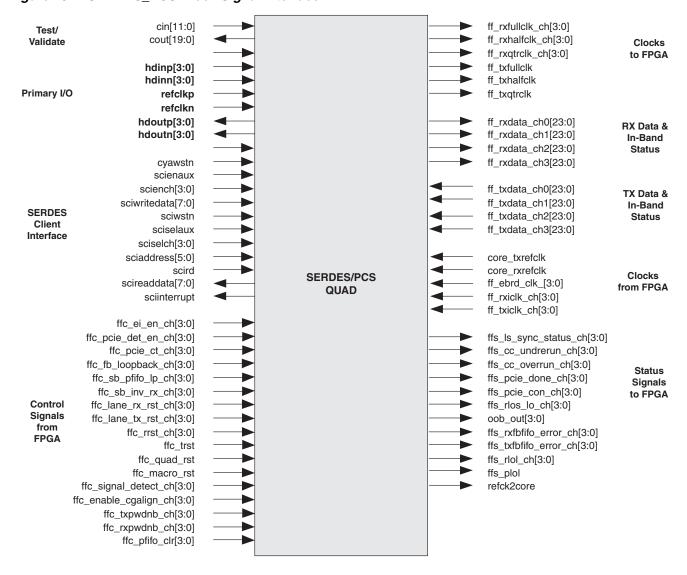

#### SERDES/PCS

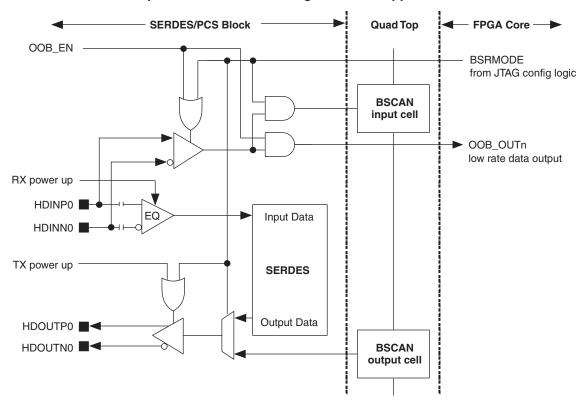

The quad contains four channels with both Rx and Tx circuits, and an auxiliary channel that contains the Tx PLL. The reference clock to the Tx PLL can be provided either by the primary differential reference clock pins or by the FPGA core. The quad SERDES/PCS macro performs the serialization and de-serialization function for four lanes

of data. In addition, the PLL within the SERDES/PCS block provides the system clock for the FPGA logic. The quad also supports both full-data-rate and half-data-rate modes of operation on each Tx and Rx circuit independently.

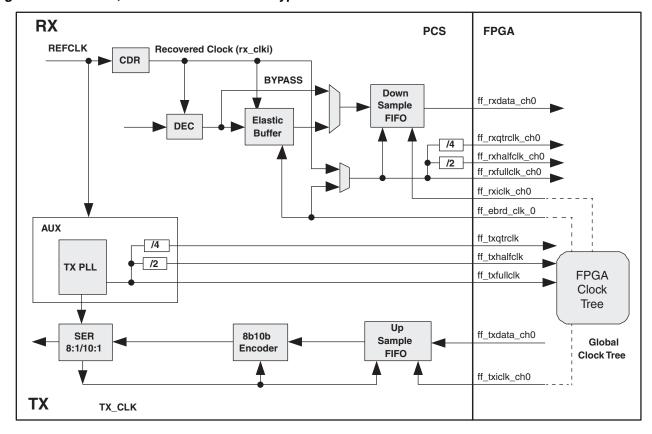

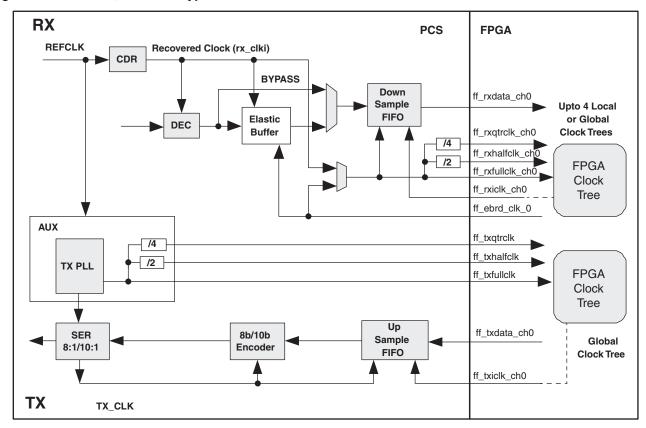

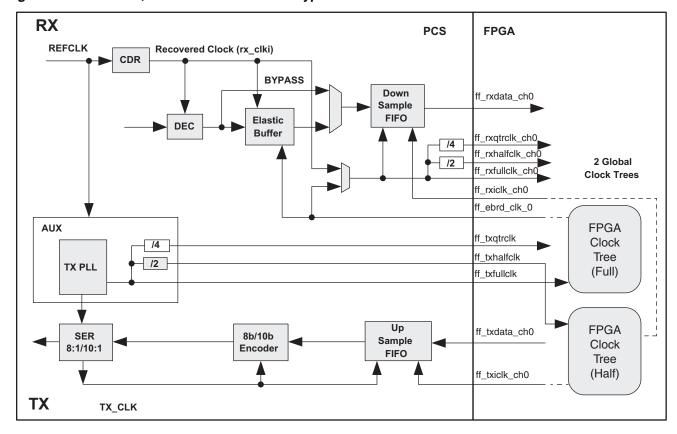

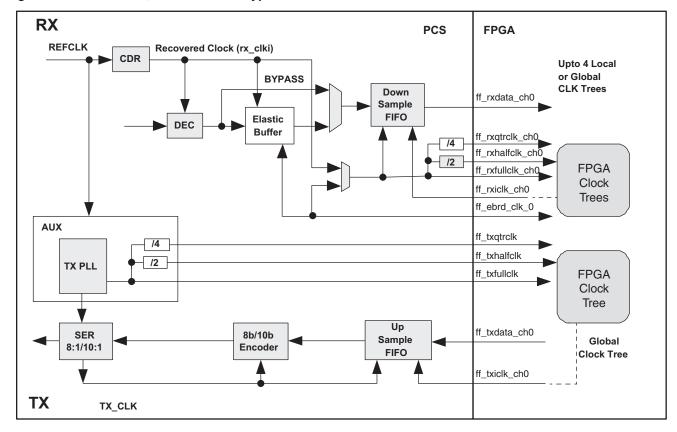

The block level diagram is shown in Figure 18-4.

Figure 18-4. SERDES PCS Block Signal Interface

## I/O Definitions

Table 18-4 lists all default and optional input and outputs to/from a PCS quad. Users can choose optional ports for a PCS quad using the  $IPexpress^{TM}$  GUI.

Table 18-4. SERDES\_PCS I/O Descriptions

| Signal Name                             | I/O      | Туре         | Description                                                                                   | Default/<br>Optional |

|-----------------------------------------|----------|--------------|-----------------------------------------------------------------------------------------------|----------------------|

| Primary I/O, SERDES Quad                |          |              |                                                                                               |                      |

| hdinp0                                  | I        | Channel      | High-speed CML input, positive, channel 0                                                     | D                    |

| hdinn0                                  | I        | Channel      | High-speed CML input, negative, channel 0                                                     | D                    |

| hdinp1                                  | I        | Channel      | High-speed CML input, positive, channel 1                                                     | D                    |

| hdinn1                                  | I        | Channel      | High-speed CML input, negative, channel 1                                                     | D                    |

| hdinp2                                  | I        | Channel      | High-speed CML input, positive, channel 2                                                     | D                    |

| hdinn2                                  | I        | Channel      | High-speed CML input, negative, channel 2                                                     | D                    |

| hdinp3                                  | I        | Channel      | High-speed CML input, positive, channel 3                                                     | D                    |

| hdinn3                                  | ı        | Channel      | High-speed CML input, negative, channel 3                                                     | D                    |

| hdoutp0                                 | 0        | Channel      | High-speed CML output, positive, channel 0                                                    | D                    |

| hdoutn0                                 | 0        | Channel      | High-speed CML output, negative, channel 0                                                    | D                    |

| hdoutp1                                 | 0        | Channel      | High-speed CML output, positive, channel 1                                                    | D                    |

| hdoutn1                                 | 0        | Channel      | High-speed CML output, negative, channel 1                                                    | D                    |

| hdoutp2                                 | 0        | Channel      | High-speed CML output, positive, channel 2                                                    | D                    |

| hdoutn2                                 | 0        | Channel      | High-speed CML output, negative, channel 2                                                    | D                    |

| hdoutp3                                 | 0        | Channel      | High-speed CML output, positive, channel 3                                                    | D                    |

| hdoutn3                                 | 0        | Channel      | High-speed CML output, negative, channel 3                                                    | D                    |

| refclkp                                 | ı        | Quad         | Reference Clock input, positive, Dedicated CML input                                          | D                    |

| refclkn                                 | I        | Quad         | Reference Clock input, negative, Dedicated CML input                                          | D                    |

| Receive / Transmit Data Bus             | (See Tab | le for Detai | led Data Bus Usage)                                                                           | •                    |

| ff_rxdata_ch0[23:0]                     | 0        | Channel      | Data Signals for the channel 0 receive path                                                   | D                    |

| ff_rxdata_ch1[23:0]                     | 0        | Channel      | Data Signals for the channel 1 receive path                                                   | D                    |

| ff_rxdata_ch2[23:0]                     | 0        | Channel      | Data Signals for the channel 2 receive path                                                   | D                    |

| ff_rxdata_ch3[23:0]                     | 0        | Channel      | Data Signals for the channel 3 receive path                                                   | D                    |

| ff_txdata_ch0[23:0]                     | I        | Channel      | Data Signals for the channel 0 transmit path                                                  | D                    |

| ff_txdata_ch1[23:0]                     | I        | Channel      | Data Signals for the channel 1 transmit path                                                  | D                    |

| ff_txdata_ch2[23:0]                     | I        | Channel      | Data Signals for the channel 2 transmit path                                                  | D                    |

| ff_txdata_ch3[23:0]                     | I        | Channel      | Data Signals for the channel 3 transmit path                                                  | D                    |

| Control Signals                         | •        |              |                                                                                               | •                    |

| ffc_sb_inv_rx_ch[3:0]                   | 1        | Channel      | Control the inversion of received data.  1 = Invert the data  0 = Do not invert the data      | 0                    |

| ffc_enable_cgalign_ch[3:0] <sup>4</sup> | 1        | Channel      | Control comma aligner.  1 = Enable comma aligner  0 = Lock comma aligner at current position. | 0                    |

| ffc_signal_detect_ch[3:0] <sup>4</sup>  | 1        | Channel      | Control Link State Machine 1 = Enable Link State Machine 0 = Disable Link State Machine       | 0                    |

| ffc_fb_loopback_ch[3:0]                 | I        | Channel      | FPGA Bridge Loopback.  1 = Enable loopback from Rx to Tx  0 = Normal data operation           | 0                    |

# Table 18-4. SERDES\_PCS I/O Descriptions (Continued)

| Signal Name                          | I/O      | Туре    | Description                                                                                                                                                                         | Default/<br>Optional |

|--------------------------------------|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| ffc_sb_pfifo_lp_ch[3:0]              | I        | Channel | SERDES Bridge Parallel Loopback 1 = Enable loopback from Rx to Tx, 0 = Normal data operation                                                                                        | 0                    |

| ffc_pfifo_clr_ch[3:0]                | I        | Channel | SERDES Bridge Parallel Loopback FIFO Clear<br>1 = Reset Loopback FIFO<br>0 = Normal Loopback operation                                                                              | D                    |

| rx_sdi_en                            | I        | Channel | These signals are used in BSCAN mode only.                                                                                                                                          | 0                    |

| tx_sdi_en                            | I        | Quad    | ,                                                                                                                                                                                   |                      |

| Reset Signals                        | 1        |         | <u> </u>                                                                                                                                                                            | <del> </del>         |

| ffc_lane_rx_rst_ch[3:0]              | I        | Channel | Active high, asynchronous input. Resets individual Rx channel logic only in PCS.                                                                                                    | D                    |

| ffc_lane_rx_tst_ch[3:0]              | ı        | Channel | Active high, asynchronous input. Resets individual Tx channel logic only in PCS.                                                                                                    | D                    |

| ffc_rrst_ch[3:0]                     | ı        | Channel | Active high. Resets selected digital logic in the SERDES Receive channel                                                                                                            | D                    |

| ffc_trst                             | I        | Quad    | Active high, resets selected digital logic in all SERDES Transmit channels.                                                                                                         | D                    |

| ffc_quad_rst                         | I        | Quad    | Active high, asynchronous input. Resets all SERDES channels including the auxiliary channel and PCS.                                                                                | D                    |

| ffc_macro_rst                        | I        | Quad    | Active high, asynchronous input to SERDES quad. Resets all SERDES channels including the AUX channel but not PCS logic.                                                             | D                    |

| ffc_txpwdnb_ch[3:0]                  | I        | Channel | Active low transmit channel power down. 0 = Transmit Channel Power Down.                                                                                                            | D                    |

| ffc_rxpwdnb_ch[3:0]                  | I        | Channel | Active low receive channel power down. 0 = Receive Channel Power Down.                                                                                                              | D                    |

| Status Signals                       | <b>.</b> |         |                                                                                                                                                                                     |                      |

| ffs_rlos_lo_ch[3:0]                  | 0        | Channel | Loss of signal detection for each channel. Register bits rlos_hset[2:0] are used to set the threshold. Low threshold is not user accessible. 1 = Loss of signal 0 = Signal detected | D                    |

| ffs_ls_sync_status_ch[3:0]           | 0        | Channel | 1 = Lane is synchronous to commas.<br>0 = Lane has not found comma.                                                                                                                 | D                    |

| ffs_cc_underrun_ch[3:0] <sup>6</sup> | 0        | Channel | 1 = Receive clock compensator FIFO underrun error,<br>0 = No FFIFO errors.                                                                                                          | 0                    |

| ffs_cc_overrun_ch[3:0] <sup>6</sup>  | 0        | Channel | 1 = Receive clock compensator FIFO overrun error 0 = No FIFO errors.                                                                                                                | 0                    |

| ffs_rxfbfifo_error_ch[3:0]           | 0        | Channel | 1 = Receive FPGA bridge FIFO error<br>0 = No FIFO errors                                                                                                                            | D                    |

| ffs_txfbfifo_error_ch[3:0]           | 0        | Channel | 1 = Transmit FPGA bridge FIFO error<br>0 = No FIFO errors.                                                                                                                          | D                    |

| ffs_rlol_ch[3:0]                     | 0        | Channel | 1 = Receive CDR loss of lock<br>0 = Lock maintained                                                                                                                                 | D                    |

| ffs_ploI                             | 0        | Quad    | 1 = Transmit PLL loss of lock<br>0 = Lock maintained                                                                                                                                | D                    |

| oob_out_ch[3:0] <sup>3</sup>         | 0        | Channel | Single ended outputs to video SERDES (in FPGA).                                                                                                                                     | D                    |

| refck2core                           | 0        | Quad    | Reference clock to FPGA core.                                                                                                                                                       | 0                    |

# Table 18-4. SERDES\_PCS I/O Descriptions (Continued)

| Signal Name                  | I/O     | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                                 | Default/<br>Optional |

|------------------------------|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Clock Signals to FPGA        |         |         |                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |

| ff_rxfullclk_ch[3:0]         | 0       | Channel | Receive channel recovered clock. In user mode, the source is always the channel's recovered clock. For standards such as GbE, 10 GbE that support clock compensation, the source is the respective transmit channel's system clock. For PCS bypass modes, it is also the Tx system clock, thus requiring raw mode to actually be done using either 8b10b mode with the 8b10b decoder disabled (10-bit or 20-bit data path). | D                    |

| ff_rxhalfclk_ch[3:0]         | 0       | Channel | Receive channel recovered half clock. In 2:1 gearing mode, it is a divide-by-2 output.                                                                                                                                                                                                                                                                                                                                      | D                    |

| ff_rxqtrclk_ch[3:0]          | 0       | Channel | Receive channel recovered quarter clock. Available for further 2:1 gearing.                                                                                                                                                                                                                                                                                                                                                 | 0                    |

| ff_txfullclk                 | 0       | Quad    | Tx PLL full rate clock.                                                                                                                                                                                                                                                                                                                                                                                                     | D                    |

| ff_txhalfclk                 | 0       | Quad    | Tx PLL half clock.                                                                                                                                                                                                                                                                                                                                                                                                          | D                    |

| ff_txqtrclk                  | 0       | Quad    | Tx PLL quarter clock                                                                                                                                                                                                                                                                                                                                                                                                        | 0                    |

| Clock Signals from FPGA      | 1       | I       | 1                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |

| core_rxrefclk                | I       | Quad    | Rx Reference clock from FPGA logic, for CDR PLL                                                                                                                                                                                                                                                                                                                                                                             | D                    |

| core_txrefclk                | I       | Quad    | Tx Reference clock from FPGA logic, for Tx SERDES PLL                                                                                                                                                                                                                                                                                                                                                                       | D                    |

| ff_ebrd_clk_[3:0]            | I       | Channel | Receive channel clock input from FPGA for CTC FIFO (Elastic Buffer) read                                                                                                                                                                                                                                                                                                                                                    | D                    |

| ff_rxiclk_ch[3:0]            | 1       | Channel | Receive channel clock input from FPGA. Used to clock the Rx FPGA Interface FIFO with a clock synchronous to the reference and/or receive reference clock.                                                                                                                                                                                                                                                                   | D                    |

| ff_txiclk_ch[3:0]            | I       | Channel | Transmit channel clock input from FPGA.Per channel transmit clock inputs from FPGA. Used to clock the Tx FPGA. Interface FIFO with clock synchronous to the reference clock. Also used to clock the Rx FPGA Interface FIFO with a clock synchronous to the reference clock when CTC is used.                                                                                                                                | D                    |

| SERDES Client Interface (SCI | )       |         |                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |

| scienaux                     | I       | R       | sciwdata is written to the quad control registers     memory data is written to the quad control registers                                                                                                                                                                                                                                                                                                                  | 0                    |

| scien_ch[3:0]                | I       | R       | sciwdata is written to the channel control registers     memory data is written to the channel control registers                                                                                                                                                                                                                                                                                                            | 0                    |

| sciselaux                    | I       | R       | 1: select quad registers                                                                                                                                                                                                                                                                                                                                                                                                    | 0                    |

| scisel_ch[3:0]               | I       | R       | 1: select channel registers                                                                                                                                                                                                                                                                                                                                                                                                 | 0                    |

| sciaddress[5:0]              | I       | R       | Address bus input                                                                                                                                                                                                                                                                                                                                                                                                           | 0                    |

| scireaddata[7:0]             | 0       | R       | Read data output                                                                                                                                                                                                                                                                                                                                                                                                            | 0                    |

| sciwritedata[7:0]            | I       | R       | Write data input                                                                                                                                                                                                                                                                                                                                                                                                            | 0                    |

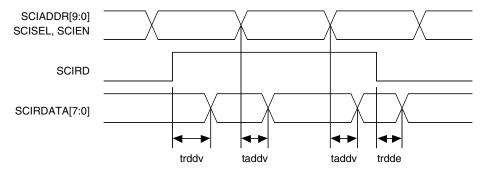

| scird                        | I       | R       | Read data select     Read data not selected                                                                                                                                                                                                                                                                                                                                                                                 | 0                    |

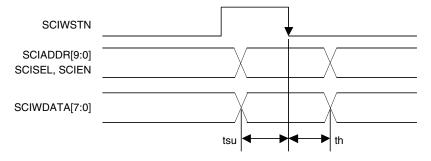

| sciwstn                      | I       | R       | Write strobe                                                                                                                                                                                                                                                                                                                                                                                                                | 0                    |

| sciinterrupt                 | 0       | R       | Interrupt output                                                                                                                                                                                                                                                                                                                                                                                                            | 0                    |

| cyawstn <sup>5</sup>         | 1       | R       | 1: Copy all memory cells to registers if sciwstn = 0 0: Default                                                                                                                                                                                                                                                                                                                                                             | 0                    |

| SERDES Characterization / Te | est Bus |         |                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |

| cin[11:0]                    | I       | R       | Characterization test bus logic data input                                                                                                                                                                                                                                                                                                                                                                                  | D                    |

|                              | 1       | I .     |                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |

#### Table 18-4. SERDES\_PCS I/O Descriptions (Continued)

| Signal Name | I/O | Туре | Description                                 | Default/<br>Optional |

|-------------|-----|------|---------------------------------------------|----------------------|

| cout[19:0]] | 0   | R    | Characterization test bus logic data output | D                    |

- 1. During configuration, both HDOUTP and HDOUTN are pulled high to VCCOB.

- 2. The Generic 8b10b PCS module includes four PCI control and status signals as options. If not used, the control signals may be tied to GND and the status signals may be left float.

- 3. The only way to get a signal out without using the CDR is to use the OOB\_OUT signal. This signal is available in SDI mode only.

- 4. These signals appear in the PCS port list when the external link state machine is selected. Refer to Figure 18-28.

- 5. For factory use only.

- 6. These signals are pulses. In order to properly monitor these status signals, they must be latched.

# **SERDES/PCS Functional Description**

Devices in the LatticeECP2M family have from one to four quads of embedded SERDES/PCS logic. Each quad, in turn, supports four independent full-duplex data channels. A single channel can support a data link and each quad can support up to four such channels. Note that mode selection is done on a per quad basis. For example, the selection of Gigabit Ethernet mode for a quad dedicates all four channels in that quad to Gigabit Ethernet mode.

The embedded SERDES CDR PLLs and Tx PLLs support data rates which cover a wide range of industry standard protocols.

Figure describes the major blocks and sub-blocks in a SERDES/PCS channel.

- SERDES

- Equalizer

- CDR (Clock and Data Recovery)

- Deserializer

- PreEmphasis

- Serializer

- Serial Loopback

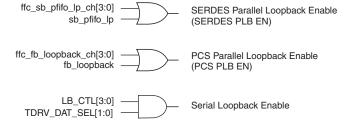

- SERDES Bridge (SB)

- Inverter: inverts receive data. Required by PCI Express

- SERDES Bridge Parallel Loopback

- PCS Core

- Word Alignment

- 8b10b Decoder

- 8b10b Encoder

- Link State Machine

- Elastic Buffer (CTC)

- FPGA Bridge (FB)

- Down-sample FIFO

- Up-sample FIFO

- PCS Parallel Loopback

#### **SERDES**

#### **Equalizer**

As the data rate of digital transmission advances over Gbps, frequency-dependent attenuation results in severe intersymbol interference in the received signal and makes it mandatory to use equalizer in the data transceiver to recover data correctly. Three pole positions are provided: low, medium and high frequency range.

#### **Pre-Emphasis**

Pre-emphasis refers to a system process designed to increase the magnitude of some frequencies with respect to the magnitude of other frequencies. The goal is to improve the overall signal-to-noise ratio by minimizing the adverse effects of such phenomena as attenuation differences or saturation of recording media in subsequent parts of the system. User can select up to 80% of pre-emphasis.

#### **Reference Clock Usage**

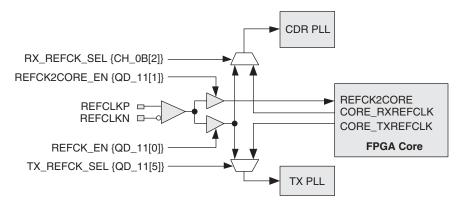

One reference clock (REFCLK) is supported in the LatticeECP2M family. The Tx PLL and the four Rx PLLs all run at the same frequency, which is a multiple of the reference clock frequency. The Tx serializer in each channel can be independently programmed to run at this rate (full-data-rate mode) or half of this rate (half-data-rate mode). Similarly, the Rx deserializer in each channel can be independently programmed to run at this rate (full-data-rate mode) or half of this rate (half-data-rate mode). If all Tx and Rx are programmed in the same mode (normally this will be full-rate) then all four channels in the quad will run at the same frequency, both Tx and Rx.

The transmit PLL in the SERDES is able to lock to either an external reference clock from the pins, or a reference clock provided from the FPGA core (core\_txrefclk). The receive CDRs in the SERDES is able to lock to either an external reference clock from the pins, or a reference clock provided by the FPGA core (core\_rxrefclk).

HDIN0 CDR0/ DES<sub>0</sub> **RX PLL** HDIN1 CDR1/ DES1 1/2 **RX PLL** Data to PCS HDIN2 CDR2/ 1/2 DES<sub>2</sub> **RX PLL** HDIN3 CDR3/ 1/2 DES<sub>3</sub> **RX PLL** REFCK2CORE REFCLKP □ CORE\_RXREFCLK REFCLKN □ CORE\_TXREFCLK **FPGA CORE** TX PLL HDOUT0 SER0 1/2 HDOUT1 SER1 Data from **PCS** HDOUT2 SER2 1/2

Figure 18-5. Block Diagram, Reference Clock Usage

#### **Reference Clock Sources**

HDOUT3

refclkp, refclkn

Dedicated CML input. This is the first choice unless different clock sources for rx and tx are used. The clock signal may be CML, LVDS or LVPECL. Refer to FPGA-TN-02077, <u>Electrical Recommendations for Lattice SERDES</u>, for example interface circuits.

SER3

1/2

core rxrefclk, core txrefclk

Reference clock from FPGA logic. The Primary Clock pad (PCLK) should be used as the clock input pin to the FPGA. The clock signal may be CML, LVDS, LVPECL or single-ended.

#### **FPGA PLL**

When an FPGA PLL is used as the reference clock, the reference clock to PLL should be assigned to a dedicated PLL input pad. The FPGA PLL output jitter may not meet system specifications at higher data rates. Use of an FPGA PLL is not recommended in jitter-sensitive applications.

#### Full-Data-Rate and Half-Data-Rate

Each Tx Serializer and Rx Deserializer can be split into full-data-rate and half-data-rate, allowing two different data rates in each direction and in each channel.

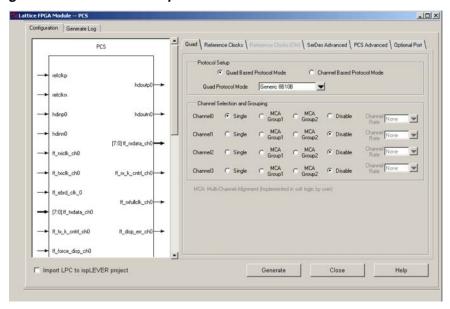

The Channel Based Protocol Mode must be selected to use this dual rate feature.

#### Example:

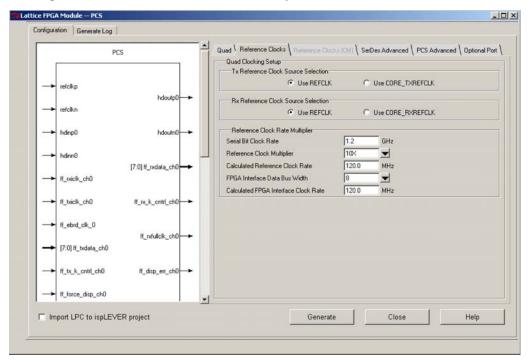

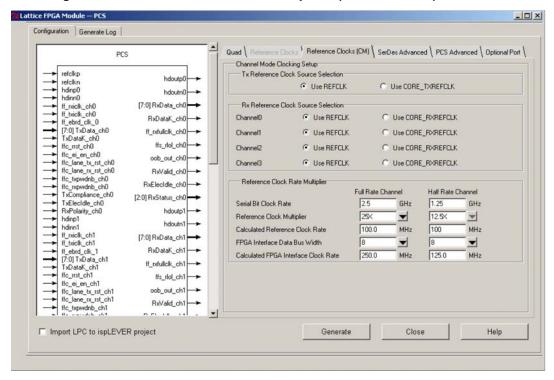

- 1. In the Quad Tab window of IPexpress (Figure 18-22), G8B10B Mode, Channel Based Protocol Mode, Channel 0 (Full Rate) and Channel 1 (Half Rate) are selected.

- 2. In the **Reference Clock (CM) window** (Figure 18-24), under the **Full Rate Channel** column, enter the following:

Serial Bit Clock Rate: 2.5 GHz

Reference Clock Multiplier: 10X

Leave the other three entries

3. The Half Rate Channel column will display calculated values for Half Rate:

|                                      | <b>Full Rate Channel</b> | <b>Half Rate Channel</b> |

|--------------------------------------|--------------------------|--------------------------|

| Serial Bit Clock Rate                | 2.5 GHz                  | 1.25 GHz                 |

| Reference Clock Multiplier           | 10X                      | 5X                       |

| Calculated Reference Clock Rate      | 250 MHz                  | 250 MHz                  |

| FPGA Interface Data Bus Width        | 8                        | 8                        |

| Calculated FPGA Interface Clock Rate | 250 MHz                  | 125 MHz                  |

#### Full Clock, Half Clock and Quarter Clock Usage

In most cases, txfullclk is used for ff\_rxiclk\_chx, ff\_txiclk\_chx, ff\_ebrd\_clk\_x as illustrated in Figure 18-32.

The IPexpress GUI automatically calculates the FPGA Interface Clock Frequency when Reference Clock Multiplier and FPGA Interface Data Bus Width is selected.

Table 18-5 illustrates clock usage examples in all possible combinations of the refclk\_multiplier modes and 8-bit or 16-bit interface Data Bus widths.

Table 18-5. Clock Usage Example - G8B10B Mode, REFCLK = 120MHz

| Reference Clock Multiplier | 10xH               | 10x      | 20xH     | 20x      |

|----------------------------|--------------------|----------|----------|----------|

| Bit Rate                   | 600 Mbps           | 1.2 Gbps | 1.2 Gbps | 2.4 Gbps |

| 8-Bit Interface Example    |                    |          |          |          |

| rxfullclk1                 | 60                 | 120      | 120      | 240      |

| rxhalfclk                  | 30                 | 60       | 60       | 120      |

| txfullclk                  | 120                | 120      | 240      | 240      |

| txhalfclk                  | 60                 | 60       | 120      | 120      |

| txqtrclk                   | 30                 | 30       | 60       | 60       |

| 16-Bit Interface Example   |                    |          |          |          |

| rxfullclk                  | 60                 | 120      | 120      | 240      |

| rxhalfclk1                 | 30                 | 60       | 60       | 120      |

| txfullclk                  | 120                | 120      | 240      | 240      |

| txhalfclk                  | 60                 | 60       | 120      | 120      |

| txqtrclk                   | 30 <sup>2, 3</sup> | 30       | 60       | 60       |

These recovered clocks are used as the source of rxiclk in CTC BYPASS mode. See Figures 18-34 and 18-36.

The VCO in the Full Data Rate Channel is the same as the bit clock. In Half Data Rate Channel, the bit clock is half of the VCO.

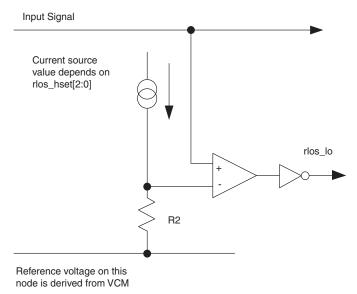

#### Loss Of Signal (LOS)

Each channel contains a programmable loss-of-signal detector as shown in Figure 18-6. The loss-of-signal threshold depends on the value of the programmable current source. The current source value is chosen using the rlos\_hset[2:0] control bits.

Figure 18-6. Loss-of Signal Detector

Note: rlos\_lset[2:0] control bits and associated status bits are internal use only.

#### **Loss Of Lock**

Both the transmit PLL and the individual channel CDRs have digital counter-based, loss-of-lock detectors. If the transmit PLL loses lock, the loss-of-lock for the PLL is asserted and remains asserted until the PLL reacquires lock.

<sup>2.</sup> The clocks in the shaded cells are used as the FPGA interface clocks in each mode.

<sup>3.</sup> When this mode is selected, the 'PLL Quarter Clock' must be checked in the Optional Port tab window of the configuration GUI (see Figure 18-28).

If a CDR loses lock, the loss-of-lock for that channel is asserted and locking to the reference clock retrains the VCO in the CDR. When this is achieved, loss-of-lock for that channel is de-asserted and the CDR is switched back over to lock to the incoming data. The CDR will either remain locked to the data, or will go back out of lock again in which case the re-training cycle will repeat.

#### Tx Lane-to-Lane Skew

A control bit, sync\_toggle, has been added to reset all the active Tx channels to start serialization with bit0. Most multi-channel protocol standards have requirements to ensure that the Tx lane-to-lane skew is within a certain specification. This is to ensure that most of the Rx De-skew (Multi-channel alignment, which is not supported in hard PCS by Lattice ECP2M) is for channel (trace) de-skewing.

The reset to the Tx serializers is generated either by toggling the sync\_toggle control bit or by a transition in PLL Loss of Lock. The reset is applied to all active Tx serializers. If both these source signals are level, then the Tx serializers are operating normally.

#### **PCS Functional Setup**

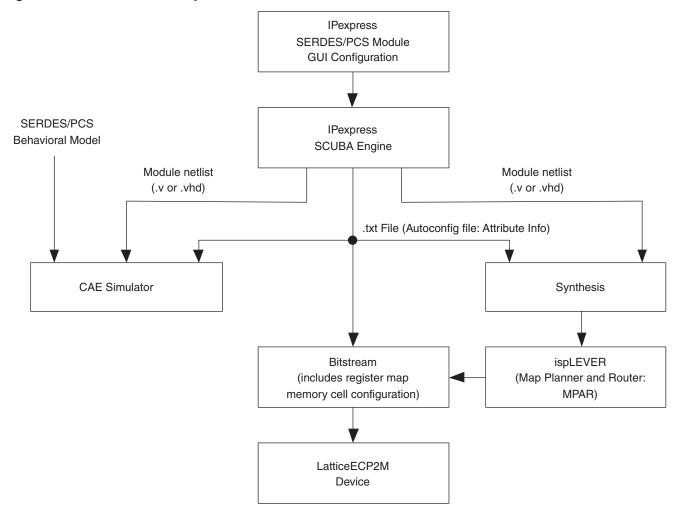

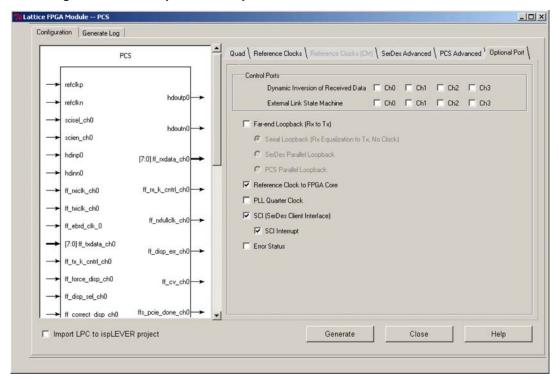

The LatticeECP2M PCS can be configured for use in various applications. Setup is chosen with the ispLEVER® IPexpress module generation tool which allows the user to select the mode and feature options for the PCS. Option selections are saved in an auto-configuration file which is subsequently used by the ispLEVER bitstream generator to write the user selections into the bitstream. To change PCS option selections it is recommended that the user rerun IPexpress to regenerate a PCS module and create a new auto-configuration file. Some options can be changed by manually editing the auto-configuration file before running the bitstream generator.

After configuration, PCS options can be changed dynamically by writing to PCS registers via the optional SERDES Client Interface (SCI) bus. The SERDES Client Interface is soft IP that allows the SERDES/PCS quad to be controlled by registers as opposed to configuration memory cells. A table of control and status registers accessible through the SCI is provided in the Memory Map section of this document.

#### **Auto-Configuration File**

Initial register setup for each PCS mode can be performed by using the autoconfiguration feature in ispLEVER. The module generator provides an auto-configuration file which contains the quad and channel register settings for the chosen mode. This file can be referred to for front-end simulation and also can be integrated into the bitstream. When an auto-configuration file is integrated into the bitstream all the quad and channel registers will be set to values defined in the auto-configuration file during configuration. The SCI (SERDES Client Interface) is therefore not needed if all quads are to be set via auto-configuration files. However, the SCI must be included in a design if the user needs to change control registers or monitor status registers during operation.

#### **Transmit Data**

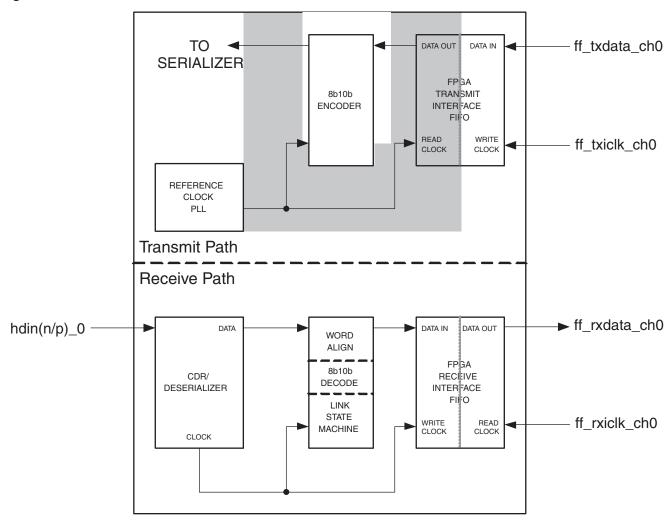

The PCS quad transmit data path consists of 8b10b Encoder and Serializer per channel.

#### 8b10b Encoder

This module implements an 8b10b encoder as described within the IEEE 802.3ae-2002 1000BASE-X specification. The encoder performs the 8-bit to 10-bit code conversion as described in the specification, along with maintaining the running disparity rules as specified. The 8b10b encoder can be bypassed on a per channel basis by setting the attribute CHx\_8B10B to "BYPASS" where x is the channel number.

#### Serializer

The 8b10b encoded data undergoes parallel to serial conversion and is transmitted off chip via the embedded SERDES.

#### **Receive Data**

The PCS quad receive data path consists of the following sub-blocks per channel: Deserializer, Word Aligner, 8b10b Decoder, Optional Link State Machine, and Optional Receive Clock Tolerance Compensation (CTC) FIFO.

#### Deserializer

Data is brought on-chip to the embedded SERDES where it goes from serial to parallel.

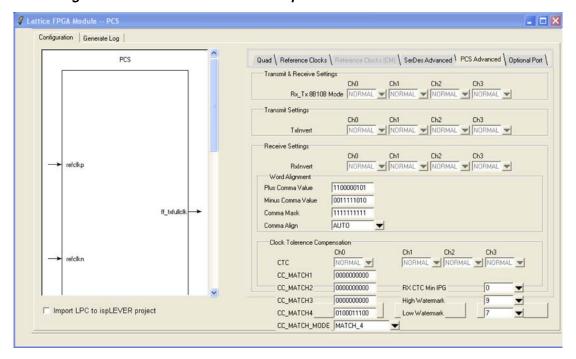

#### **Word Alignment (Byte Boundary Detect)**

This module performs the comma codeword detection and alignment operation. The comma character is used by the receive logic to perform 10-bit word alignment upon the incoming data stream. The word aligner can be bypassed on a per channel basis by setting attribute CHx\_COMMA\_ALIGN to "BYPASS" where x is the channel number. The comma description can be found in section 36.2.4.9 of the 802.3.2002 1000BASE-X specification as well as section 48.2.6.3, Figure 48-7 of the 10GBASE-X specification.

A number of programmable options are supported within the word alignment module:

• Software enable control (in User Configured - UC mode).

Note: UC\_Mode refers to 8-bit SERDES Only, 10-bit SERDES Only, SD-SDI, HD-SDI.

- Ability to set two programmable word alignment characters (typically one for positive and one for negative disparity) and a programmable per bit mask register for alignment compare. Alignment characters and the mask register is set on a per quad basis. For many protocols, the word alignment characters can be set to "XXX0000011" (jhgfiedcba bits for positive running disparity comma character matching code groups K28.1, K28.5, and K28.7) and "XXX1111100" (jhgfiedcba bits for negative running disparity comma character matching code groups K28.1, K28.5, and K28.7). However the user can define any bit pattern up to 10 bits long.

- The first alignment character is defined by the 10-bit value assigned to attribute COMMA\_A. This value applies to all channels in a PCS quad.

- The second alignment character is defined by the 10-bit value assigned to attribute COMMA\_B. This value applies to all channels in a PCS quad.

- The mask register defines which word alignment bits to compare (a '1' in a bit of the mask register means check the corresponding bit in the word alignment character register). The mask registers defined by the 10-bit value assigned to attribute COMMA M. This value applies to all channels in a PCS quad.

When attribute CHx\_COMMA\_ALIGN is set to 'AUTO', one of the protocol based Link State machines will control word alignment. For more information on the operation of the protocol based Link State Machines, see the Protocol Specific Link State Machine description below.

#### 8b10b Decoder

The 8b10b decoder implements an 8b10b decoder operation as described with the IEEE 802.3-2002 specification. The decoder performs the 10-bit to 8-bit code conversion along with verifying the running disparity. The 8b10b decoder can be bypassed on a per channel basis by setting attribute CHx\_8B10B to "BYPASS" where x is the channel number.

When a code violation is detected, the ff\_rxdata receive data is set to 0xEE with ff\_rx\_k\_cntrl\_ch set to '1'.

#### **Protocol Specific Link State Machine**

The PCS implements link state machines for various protocols that are used in various quad modes.

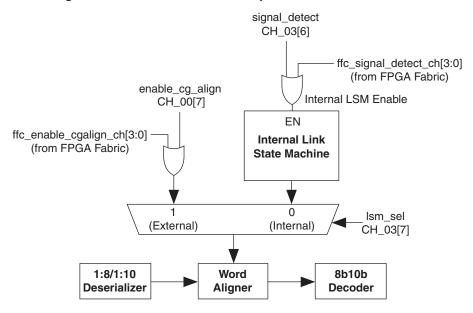

When a protocol specific Link State Machine is selected, that channel's Link State Machine must be enabled by setting the protocol CH(0-3)\_COMMA\_ALIGN to "AUTO". Selection of the specific Link State Machine that is enabled in each mode is described below and summarized in Figure 18-7.

The Link State Machine for Gigabit Ethernet is selected when attribute PROTOCOL is "GIGE". Link synchronization is achieved after the successful detection and alignment of the required number of consecutive aligned code words. The Gigabit Ethernet link synchronization state machine implements the Synchronization State Diagram shown in Figure 36-9 of the 802.3- 2002 1000BASE-X specification.

In 'G8B10B' and '10-bit SERDES Only' protocols, the Gigabit Ethernet Link State Machine is used when COMMA ALIGN is set to 'AUTO'.

#### **External Link State Machine Option**

When attribute CHx\_COMMA\_ALIGN is set to "DYNAMIC", the protocol specific Link State Machines are bypassed. When ffc\_enable\_cgalign\_ch(0-3) is high, the word aligner will lock alignment and stay locked. It will stop comparing incoming data to the user-defined word alignment characters and will maintain current alignment on the first successful compare to either the COMMA\_A or COMMA\_B. When ffc\_enable\_cgalign\_ch(0-3) is pulsed low, the word aligner will re-lock on the next match to one of the user-defined word alignment characters. If desired, ffc\_enable\_cgalign\_ch(0-3) can be controlled by a Link State Machine implemented externally to the PCS quad to allow a change in word alignment only under specific conditions.

Figure 18-7 illustrates the link state machine options.

Figure 18-7. PCS Word Aligner and Link State Machine Options

Table 18-6. Link State Machine and Word Aligner Selection

| COMMA ALIGN Mode | Description                                                                                                                                                                                                                              |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AUTO             | WA enabled, LSM enabled (GbE LSM: default).                                                                                                                                                                                              |

| DYNAMIC          | WA enabled, LSM disabled. The cg_align and sig_detect signals are set to 0 so that the potential external LSM to control both signals. The External Link State Machine option in the Optional Port tab of the GUI must be also selected. |

| BYPASS           | WA bypassed, LSM disabled. Users may develop word aligner in the FPGA core and provide their own cg_align and sig_detect signals to the logic.                                                                                           |

When a Link State Machine is selected and enabled, for a particular channel, that channel's ffs\_ls\_sync\_status\_ch(0-3) status signal will go high upon successful link synchronization.

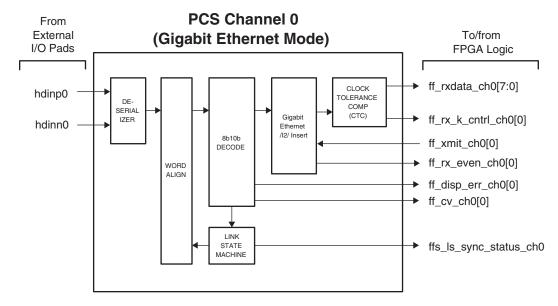

#### Idle Insert for Gigabit Ethernet Mode

Generic 8b10b mode also has the option to select the Link State Machine for word alignment. The PCS set to Gigabit Ethernet Mode provides for insertion of /l2/ symbols into the receive data stream for auto-negotiation. Gigabit Ethernet auto-negotiation is performed in soft logic. This function inserts a sequence of 8 /l2/ ordered sets every 2048 clock cycles. /l2/ insertion is controlled by the ff\_xmit\_ch(0-3) input to the PCS which is driven from the auto-negotiation soft logic. The signal ff\_rx\_even\_ch(0-3)[0] from the PCS to the auto-negotiation soft logic is also provided. Figure 18-8 shows one channel (channel 0 in this example) of receive logic when the PCS is set to Gigabit Ethernet Mode showing these control/status signals.

Figure 18-8. PCS Receive path for Gigabit Ethernet Mode (Channel 0 Example)

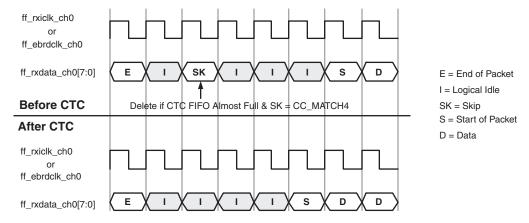

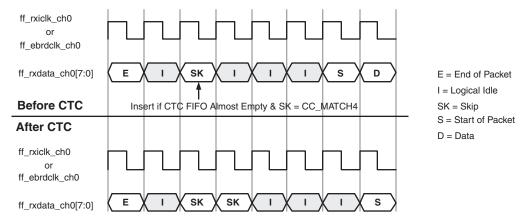

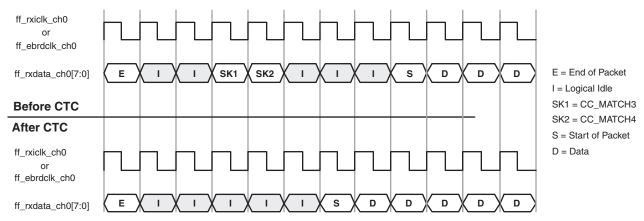

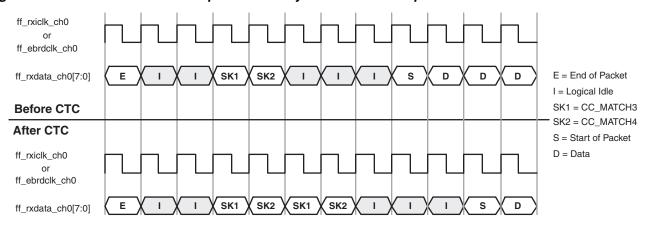

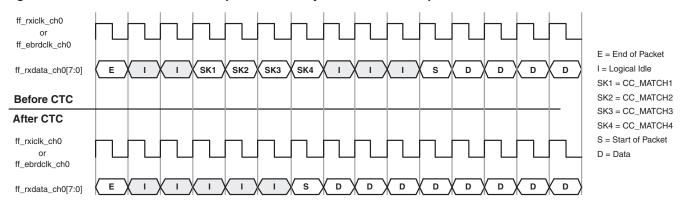

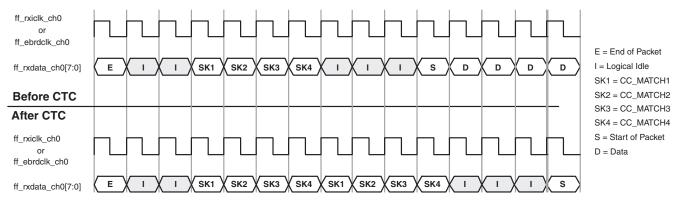

#### **Clock Tolerance Compensation**

The Clock Tolerance Compensation module performs clock rate adjustment between the recovered receive clocks and the locked reference clock. Clock compensation is performed by inserting or deleting bytes at pre-defined positions, without causing loss of packet data. A 16-Byte elasticity FIFO is used to transfer data between the two clock domains and will accommodate clock differences of up to the specified ppm tolerance for the LatticeECP2M SERDES (See DC and Switching Characteristics section of the LatticeECP2/M Family Data Sheet).

A channel has the Clock Tolerance Compensation block enable when that channel's attribute CHx\_CTC\_BYP is set to "NORMAL". The CTC is bypassed when that channel's attribute CHx\_CTC\_BYP is set to "BYPASS".

A diagram illustrating 1 byte deletion is shown in Figure 18-9:

Figure 18-9. Clock Tolerance Compensation 1 Byte Deletion Example

A diagram illustrating 1 byte insertion is shown in Figure 18-10:

Figure 18-10. Clock Tolerance Compensation 1 Byte Insertion Example

A diagram illustrating 2 byte deletion is shown in Figure 18-11:

Figure 18-11. Clock Tolerance Compensation 2 Byte Deletion Example

A diagram illustrating 2 byte insertion is shown in Figure 18-12:

Figure 18-12. Clock Tolerance Compensation 2 Byte Insertion Example

A diagram illustrating 4 byte deletion is shown in Figure 18-13:

Figure 18-13. Clock Tolerance Compensation 4 Byte Deletion Example

A diagram illustrating 4 byte insertion is shown in Figure 18-14:

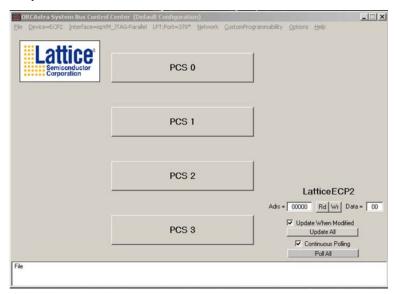

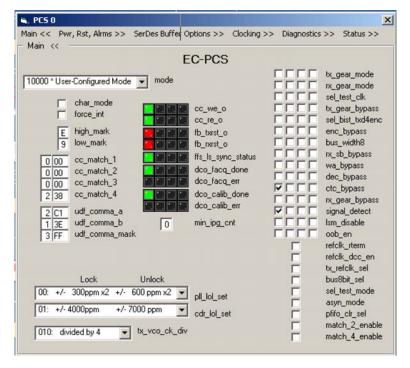

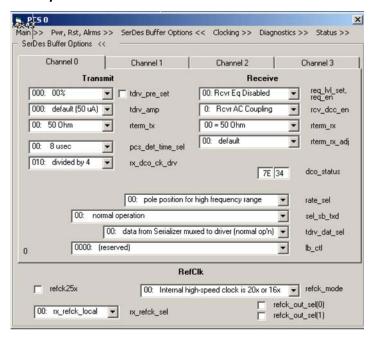

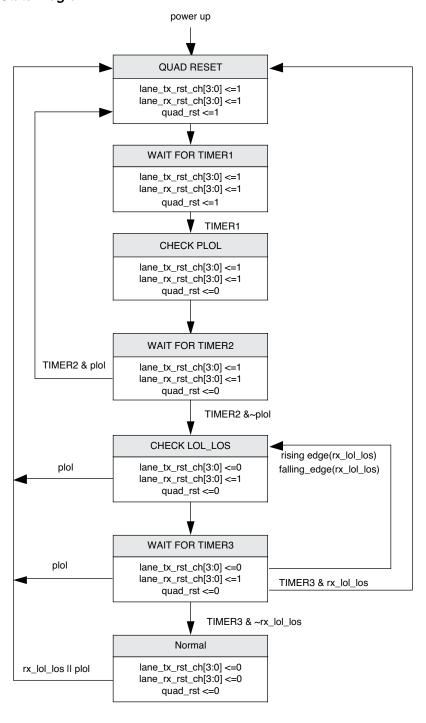

Figure 18-14. Clock Tolerance Compensation 4 Byte Insertion Example