# LatticeMico32 Tutorial

Lattice Semiconductor Corporation 5555 NE Moore Court Hillsboro, OR 97124 (503) 268-8000

December 2011

### Copyright

Copyright © 2011 Lattice Semiconductor Corporation.

This document may not, in whole or part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine-readable form without prior written consent from Lattice Semiconductor Corporation.

#### **Trademarks**

Lattice Semiconductor Corporation, L Lattice Semiconductor Corporation (logo), L (stylized), L (design), Lattice (design), LSC, CleanClock, E<sup>2</sup>CMOS, Extreme Performance, FlashBAK, FlexiClock, flexiFlash, flexiMAC, flexiPCS, FreedomChip, GAL, GDX, Generic Array Logic, HDL Explorer, IPexpress, ISP, ispATE, ispClock, ispDOWNLOAD, ispGAL, ispGDS, ispGDX, ispGDXV, ispGDX2, ispGENERATOR, ispJTAG, ispLEVER, ispLeverCORE, ispLSI, ispMACH, ispPAC, ispTRACY, ispTURBO, ispVIRTUAL MACHINE, ispVM, ispXP, ispXPGA, ispXPLD, Lattice Diamond, LatticeCORE, LatticeEC, LatticeECP, LatticeECP-DSP, LatticeECP2, LatticeECP2M, LatticeECP3, LatticeMico, LatticeMico8, LatticeMico32, LatticeSC, LatticeSCM, LatticeXP, LatticeXP2, MACH, MachXO, MachXO2, MACO, ORCA, PAC, PAC-Designer, PAL, Performance Analyst, Platform Manager, ProcessorPM, PURESPEED, Reveal, Silicon Forest, Speedlocked, Speed Locking, SuperBIG, SuperCOOL, SuperFAST, SuperWIDE, sysCLOCK, sysCONFIG, sysDSP, sysHSI, sysI/O, sysMEM, The Simple Machine for Complex Design, TraceID, TransFR, UltraMOS, and specific product designations are either registered trademarks or trademarks of Lattice Semiconductor Corporation or its subsidiaries in the United States and/or other countries. ISP, Bringing the Best Together, and More of the Best are service marks of Lattice Semiconductor Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

## **Type Conventions Used in This Document**

| i           | Items in the user interface that you select or click. Text that you type into the user interface.  Variables in commands, code syntax, and path names. |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre></pre> | Variables in commands, code syntax, and path names                                                                                                     |

| \rtanc>     | variables in seminaries, seed syriax, and pain names.                                                                                                  |

| Ctrl+L      | Press the two keys at the same time.                                                                                                                   |

| Courier (   | Code examples. Messages, reports, and prompts from the software.                                                                                       |

|             | Omitted material in a line of code.                                                                                                                    |

|             | Omitted lines in code and report examples.                                                                                                             |

|             | Optional items in syntax descriptions. In bus specifications, the brackets are required.                                                               |

| ( )         | Grouped items in syntax descriptions.                                                                                                                  |

| { } I       | Repeatable items in syntax descriptions.                                                                                                               |

|             | A choice between items in syntax descriptions.                                                                                                         |

## Contents

LatticeMico32 Tutorial 1

| Introduction 1 Learning Objectives 2 Time to Complete This Tutorial 2 System Requirements 2 Accessing Online Help 4                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| About the Tutorial Design <b>4</b> Tutorial Data Flow <b>5</b>                                                                                                                                                                                                                                                                                                                          |

| LatticeMico32/DSP Development Board 8                                                                                                                                                                                                                                                                                                                                                   |

| Task 1: Create a New Lattice Diamond Project 9                                                                                                                                                                                                                                                                                                                                          |

| Task 2: Create the Development Microprocessor Platform 13 Create a New MSB Platform 13 Add the Microprocessor Core 17 Add the Off-Chip Memory 22 Add the Peripheral Components 25 Specify the Connections Between Master and Slave Ports 27 Assign Component Addresses 30 Assign Interrupt Request Priorities 32 Perform a Design Rule Check 32 Generate the Microprocessor Platform 32 |

| Task 3: Create the Software Application Code 37 Create a New C/C++ SPE Project 38 Linker Configuration 40 Build the Project 43                                                                                                                                                                                                                                                          |

| Task 4: Synthesize the Platform to Create an EDIF File (Linux Only) 46 Using Synopsys Synplify Pro 46 Using Mentor Graphics Precision RTL Synthesis 46 Create the EDIF File 46                                                                                                                                                                                                          |

| Task 5: Generate the Microprocessor Bitstream 47 Import the MSB Output File 47 Connect the Microprocessor to the FPGA Pins 48                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                         |

Perform Functional Simulation 49

Perform Timing Simulation 50

Generate the Bitstream 50

Task 6: Download the Hardware Bitstream to the FPGA 50

Task 7: Debug and Execute the Software Application Code on the Development Board 53

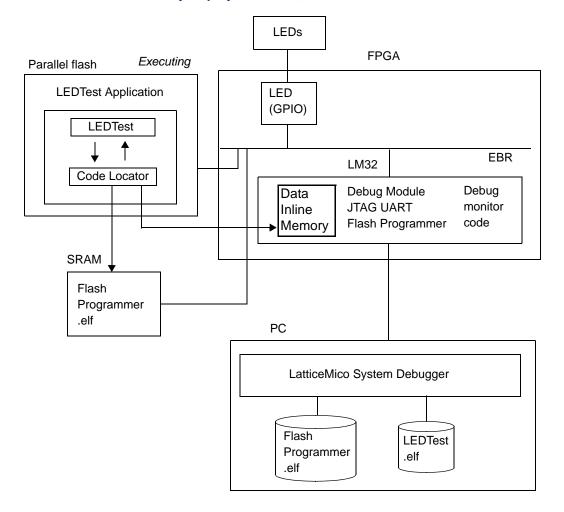

Software Application Code Execution Flow 53

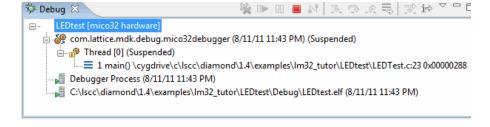

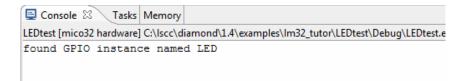

Debug the Software Application Code on the Board 54

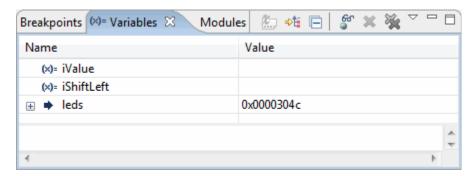

Insert Breakpoints 61

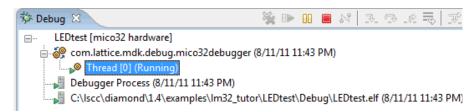

Execute the Software Application Code 62

Modify and Re-execute the Software Application Code 64

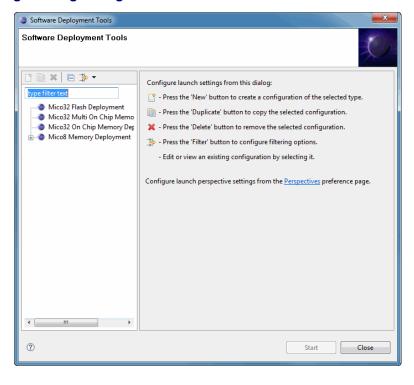

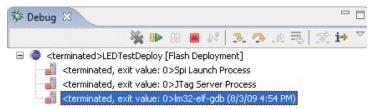

Task 8: Deploy the Software Code to Parallel Flash Memory 65

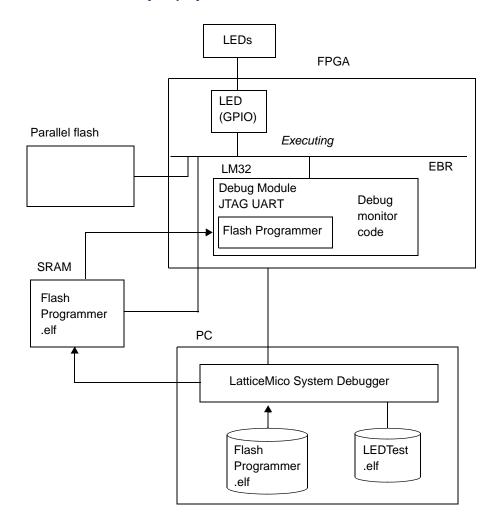

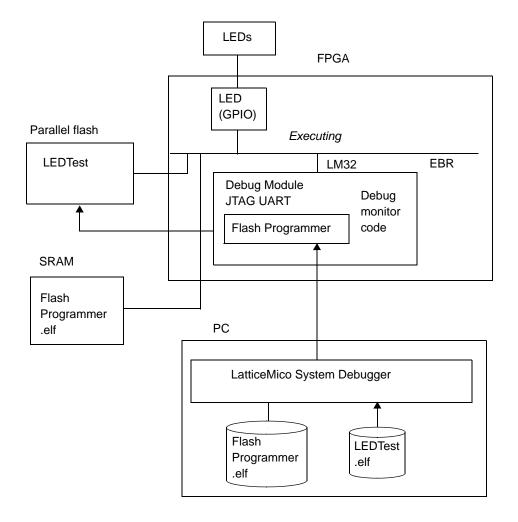

Parallel Flash Memory Deployment Flow 66

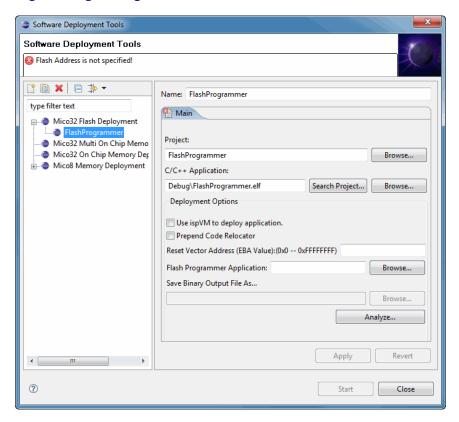

Create a CFI Flash Programmer Application 68

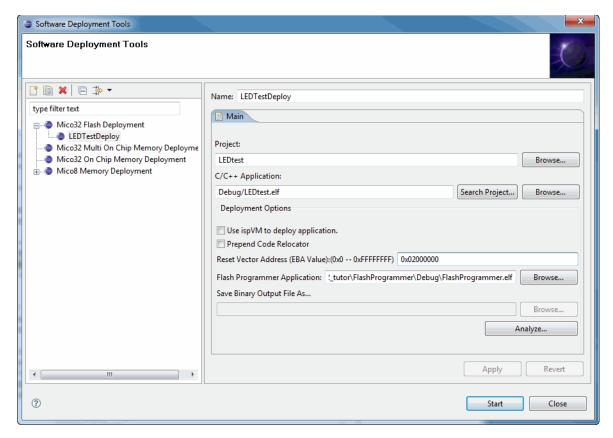

Prepare LEDTest for Flash Deployment 70

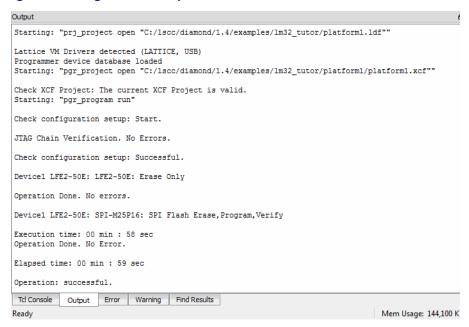

Task 9: Deploy the Production Microprocessor Bitstream to SPI Flash Memory **79**

Summary 82

Glossary 84

Recommended References 86

## LatticeMico32 Tutorial

## Introduction

This tutorial steps you through the basic process involved in using the LatticeMico System software to implement a LatticeMico32 32-bit soft microprocessor and attached components in a Lattice Semiconductor device for the LatticeMico32/DSP development board. LatticeMico System encompasses three tools: the Mico System Builder (MSB), the C/C++ Software Project Environment (C/C++ SPE), and the Debugger. Together, they enable you to build an embedded microprocessor system on a single FPGA device and to write and debug the software that drives it. Such a microprocessor lowers cost by saving board space and increases performance by reducing the number of external wires.

The LatticeMico System interface is based on the Eclipse environment, which is an open-source development and application framework for building software.

Although you can install LatticeMico System as a stand-alone tool, this tutorial assumes that you have installed Lattice Diamond before installing LatticeMico System. After you have created a project in Lattice Diamond, the tutorial shows you how to use MSB to choose a Lattice Semiconductor 32-bit microprocessor, attach components to it, and generate a top-level design, including the microprocessor and the chosen components. Next you will use Lattice Diamond to synthesize, map, place, and route the design and generate a bitstream for it. You will then download this bitstream to the FPGA on the board. The tutorial then changes to the Lattice Software Project Environment (C/C++ SPE) and shows how to use C/C++ SPE to write and compile the software application code that exercises the microprocessor and components. Finally, it shows how to download and debug the code on the board and deploy it in the parallel flash chips on the LatticeMico32/DSP development board.

This tutorial is intended for a new or infrequent user of the LatticeMico System software and covers only the basic aspects of it. The tutorial assumes that you have reviewed the *LatticeMico32 Development Kit User's Guide for LatticeECP2* to familiarize yourself with the product and to set up your board correctly.

For more detailed information on the LatticeMico System software, see the sources listed in "Recommended References" on page 86.

## **Learning Objectives**

When you have completed this tutorial, you should be able to do the following:

- Use MSB to configure a Lattice Semiconductor 32-bit microprocessor for your design, select the desired components, and connect the selected components to the microprocessor with a shared-bus arbitration scheme, which is the default.

- Use The Lattice Software Project Environment to create the C/C++ software application code that drives the microprocessor and components.

- Import the Verilog or Verilog/VHDL files generated by MSB in Windows or the EDIF file generated by a synthesis tool in Linux.

- Import an .lpf file containing the pinout.

- Synthesize, map, place, and route the design.

- Generate a bitstream of the microprocessor and download it to an FPGA on the board.

- Compile, download, and debug the software application code on the LatticeMico32/DSP development board.

- Program the Common Flash Interface (CFI) parallel flash memory with the software application code.

- Debug the hardware and software on the board.

## **Time to Complete This Tutorial**

The time to complete this tutorial is about two hours.

## **System Requirements**

You can run this tutorial on Windows or Linux.

#### **Windows**

If you will be running this tutorial on Windows on a PC, your system must meet the following minimum system requirements:

- Pentium II PC running at 400 MHz or faster

- Microsoft Windows 2000<sup>®</sup>, Windows XP<sup>®</sup> Professional, Windows 7, or Windows Vista<sup>®</sup>

- USB port for use with the LatticeMico32/DSP development board

The following software is required to complete the tutorial:

Lattice Diamond 1.3 software or later with device support for the device used with your build of the LatticeMico32/DSP development board

LatticeMico System version 1.3 or later

See the *Lattice Diamond Installation Notice* for the current release for information on installing software on the Windows platform.

#### Linux

If you will be running this tutorial on Linux on a PC, your system must meet the following minimum system requirements:

- Red Hat Enterprise Linux operating system Version 4.0 or 5.0

- Lattice Diamond version 1.0

- For mixed Verilog/VHDL support: Synopsys<sup>®</sup> Synplify Pro<sup>®</sup> 8.9 or Synplify Pro 8.9.1 for Linux

- Linux system with USB port

See the *Lattice Diamond Installation Guide* for the current release for information on installing software on the Linux platform.

#### **Hardware**

This tutorial requires the following hardware:

- A LatticeMico32/DSP development board for LatticeECP2

- USB cable

- AC adapter cord

#### Note

If you want to perform functional simulation for the mixed Verilog/VHDL flow, you must have access to a simulator that supports mixed-mode Verilog and VHDL simulation.

### **Accessing Online Help**

You can access the online Help for MSB, C/C++ SPE, the Debugger, or Eclipse Workbench by choosing Help > Help Contents in the LatticeMico System graphical user interface.

## **About the Tutorial Design**

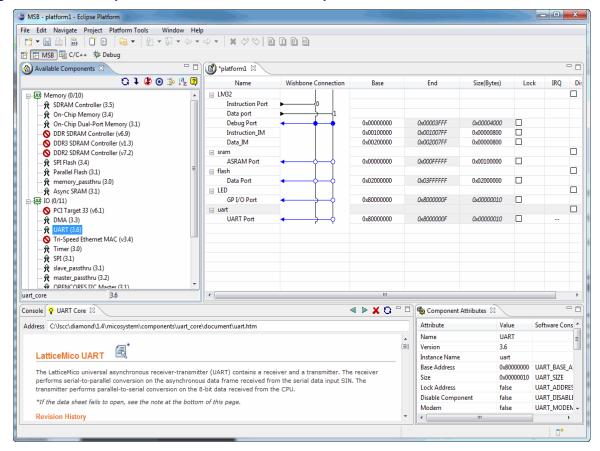

This tutorial uses a LatticeECP2 device, and all references are based on the LatticeECP2 device. The tutorial design consists of the LatticeMico32 embedded microprocessor, an asynchronous SRAM controller, a GPIO, a parallel flash memory, and a UART. After you add these components, you will specify the connections between the master and slave ports on these components, as shown in Figure 1.

SRAM slave device (memory for code and data) **GPIO** slave device (for controlling LEDs) Instruction port LM32 CPU Parallel flash (master ports) memory (for Data port deploying the application code) **UART** slave device (for host communication)

Figure 1: Desired Connections Between Master and Slave Ports

In this design, the instruction port and the data port of the CPU are the master ports. All other ports are slave ports. The instruction port will access the LatticeMico asynchronous SRAM controller and the LatticeMico parallel flash memory. The data port will access the LatticeMico asynchronous SRAM controller, the LatticeMico GPIO, the LatticeMico parallel flash memory, and the LatticeMico UART.

#### **Tutorial Data Flow**

You will perform the following major steps to create an embedded microprocessor system:

- 1. Create a new project in Lattice Diamond.

- Create a microprocessor platform for the LatticeMico32 microprocessor in MSB with a shared-bus arbitration scheme, which is the default.

- Write the software application code for the microprocessor platform in C/C++ SPE.

- For Linux only, synthesize the platform in a synthesis tool, such as Synopsys<sup>®</sup> Synplify Pro<sup>®</sup> or Mentor Graphics<sup>®</sup> Precision RTL Synthesis, to generate an EDIF file.

- 5. Generate a bitstream of the microprocessor platform in Diamond.

- 6. Download the hardware bitstream to the FPGA using Diamond Programmer.

- 7. Debug and execute the software application code on the board.

- 8. Deploy the software application code into the parallel flash memory.

- 9. Deploy the microprocessor bitstream.

#### Note

This tutorial does not show you how to debug your software application code on the instruction set simulator, but it does show you how to debug the design by downloading the bitstream and the application code to the board.

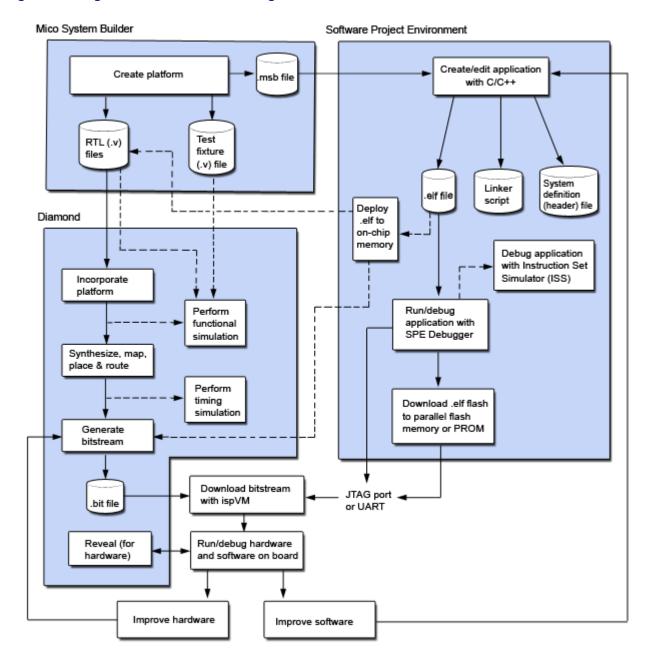

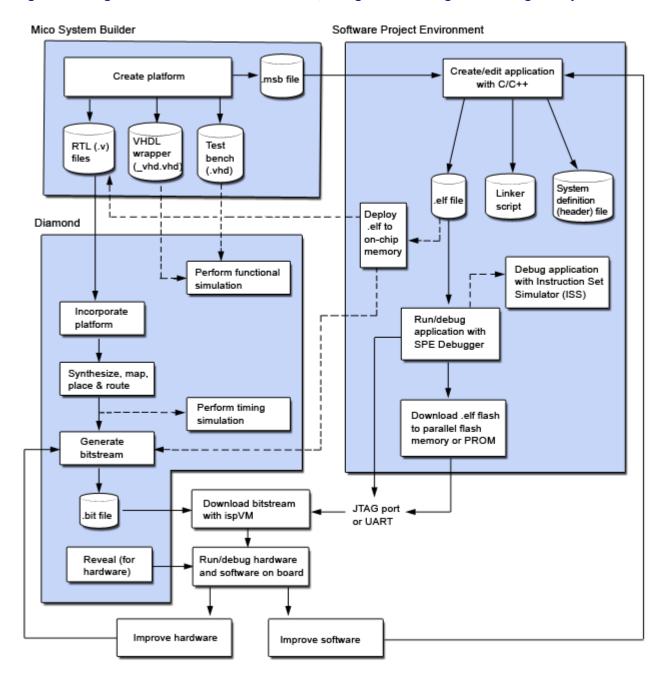

This tutorial supports both Verilog and mixed Verilog/VHDL design flows in Diamond for Windows and Linux users. The Windows Verilog design flow for using LatticeMico System to create an embedded microprocessor and the software code for it is shown in Figure 2 on page 6. The Windows mixed Verilog/VHDL design flow is shown in Figure 3 on page 7. The difference between the two methods is that mixed verilog/VHDL designs have a VHDL wrapper as an output from MSB. The VHDL wrapper is an input to Synthesis and Functional Simulation in the Diamond flow.

For Linux, the design flows are the same as those for Windows except for synthesis and simulation. For Linux, you must synthesize the Verilog or Verilog/VHDL source files in a synthesis tool, such as Synopsys Synplify Pro or Mentor Graphics Precision RTL Synthesis, and import the EDIF file into Diamond. Functional and timing simulation are performed in third-party and simulation tools outside of Diamond.

Figure 2: Design Flow for Windows Verilog Users

Figure 3: Design Flow for Windows VHDL Users, Using Mixed Verilog/VHDL Design Entry

## LatticeMico32/DSP Development Board

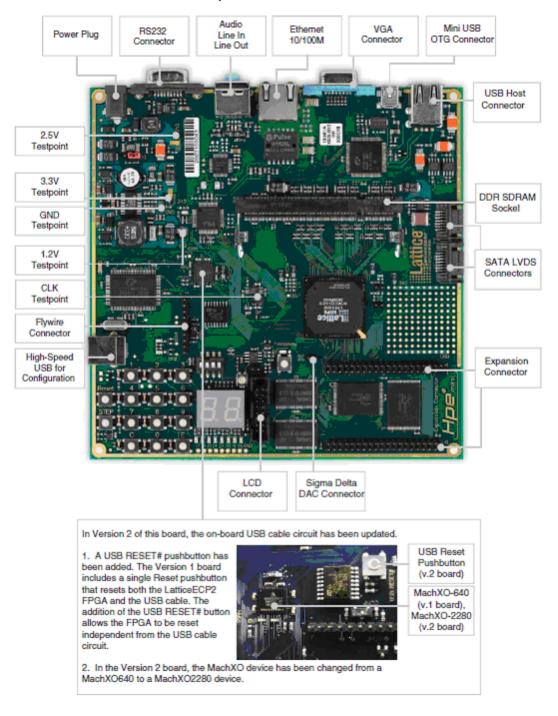

Figure 4 shows where some of the components mentioned in this tutorial reside on the LatticeMico32/DSP development board.

Figure 4: The LatticeMico32/DSP Development Board

## **Task 1: Create a New Lattice Diamond Project**

As a first step, you will create a new project in Diamond.

#### **Note**

If you are going to run this tutorial on the Linux platform and use Verilog, you must install a stand-alone version of Synopsys Synplify Pro or Mentor Graphics Precision RTL Synthesis before you create a Lattice Diamond project.

If you are going to use mixed Verilog/VHDL on the Linux platform, you must install Synopsys Synplify Pro.

#### Note

In this tutorial, the directory paths follow the Windows nomenclature. For Linux, replace the "\" character with the "/" character.

To create a new Lattice Diamond project:

- 1. Create a folder called **Im32 tutor** in the following directory:

- For Windows, < Diamond\_install\_path>\examples

- ◆ For Linux, ~/LatticeMico32

- 2. Start Lattice Diamond:

- On the Windows desktop, choose Start > Programs > Lattice Diamond > Lattice Diamond.

- On the Linux command line, run the following script:

- < Diamond install path>/ispcpld/bin/ispgui.

- Choose File > New > Project, and then click Next in the New Project wizard.

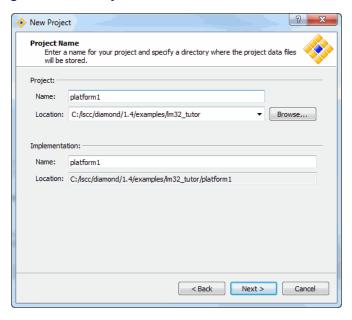

- 4. In the New Project wizard dialog box, shown in Figure 5 on page 10, select or specify the following:

- a. In the Project Name box, enter platform1.

- b. In the Location box, enter the path for the lm32\_tutor directory:

- For Windows, <Diamond\_install\_path>\examples\Im32\_tutor

- For Linux, ~/LatticeMico32/Im32\_tutor

By default, Diamond uses the Project name and location for the implementation and fills in this information. Although you can change to a different name and directory for the first implementation, you will use the default settings for this tutorial.

5. Click **Next** to proceed to the Add Source dialog box, and then click **Next**. You will add the source later.

**Figure 5: New Project Wizard**

- 6. In Select Device dialog box, shown in Figure 6 on page 11, make the following selections:

- a. In the Family box, select LatticeECP2.

- b. In the Device box, select LFE2-50E.

- c. In the Speed grade box, select 6.

- d. In the Package Type box, select **FPBGA672**.

- e. In the Operating Conditions box, select **Commercial**.

The dialog box should now resemble the illustration in Figure 6

New Project Select Device Specify a target device for the project. Select Device: Device Information: Family: Device: Voltage: 1.2V LUT: ▲ LFE2-6E LatticeEC Registers: 35964 LatticeECP LFE2-12E LatticeECP2 LFE2-20E EBR Bits: 387K LatticeECP2M LFE2-35E FBR Blocks: 21 LatticeECP3 LFE2-50E Dist RAM: 96K LFE2-70E DSP: 18 Speed grade:(\_) Package type: PLL: ▼ FPBGA672 DLL: PCS: Operating conditions: PIO Cells: 604 Commercial PIO Pins: 500 Part Names: LFE2-50E-6F672C Online Data Sheet for Device < Back Next > Cancel

Figure 6: New Project Wizard – Select a Device Dialog Box

#### 7. Click **Next**, and then click **Finish**.

In the File List, shown in Figure 7, the project name is shown at the top. The implementation name, which has the same name as the project name, is displayed in bold type, with the implementation icon project is assigned a default strategy, Strategy1, which is also displayed in bold type with the strategy icon . A strategy is a collection of settings for logic synthesis, place, and route. You can view these settings by

double-clicking the strategy name. The platform1 project is also assigned a logical preference file, platform1.lpf.

Figure 7: Diamond File List

## Task 2: Create the Development Microprocessor Platform

In Task 1, you created a blank Diamond project. The Diamond project is a placeholder for the LatticeMico32 microprocessor platform. You use LatticeMico System Builder (MSB) to create the microprocessor platform. MSB allows you to select components to attach to the microprocessor. Additionally, MSB allows you to customize each of the attached components. After all components are attached to the microprocessor, you use MSB to generate Verilog or VHDL source code that describes a microprocessor-based System-on-a-Chip (SOC). You then enter the HDL source code into the Diamond project in order to create the bitstream used to configure the FPGA.

The steps in this section describe how to build a LatticeMico32 microprocessor SOC that is intended for developing and debugging LatticeMico based systems. During system development, the FPGA resources and the firmware are in a state of flux, undergoing many changes. When you deploy a LatticeMico32 microprocessor, as described here, you reduce the impact the of on-going changes in the development environment.

### **Create a New MSB Platform**

Now you will create a new platform in MSB.

If you are going to be using LatticeMico System on the Linux platform, set up the environment to point to the location where the stand-alone synthesis tool is installed before starting LatticeMico System, as in this example:

```

setenv IPEXPRESS_SYN_PATH /install/synplify/fpga_89/bin/

synplify_pro

```

To create a new platform:

From the Start menu, choose Programs > Lattice Diamond > Accessories > LatticeMico System.

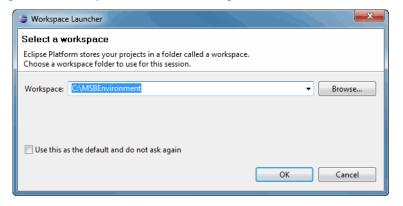

The Workspace Launcher dialog box, shown in Figure 8, displays a default workspace location for the platform.

Figure 8: Workspace Launcher Dialog Box

- 2. Accept the default location, or click the Browse button to select a different location. To keep the same workspace for future sessions, select the "Use this as the default and do not ask again" option.

- 3. Click OK.

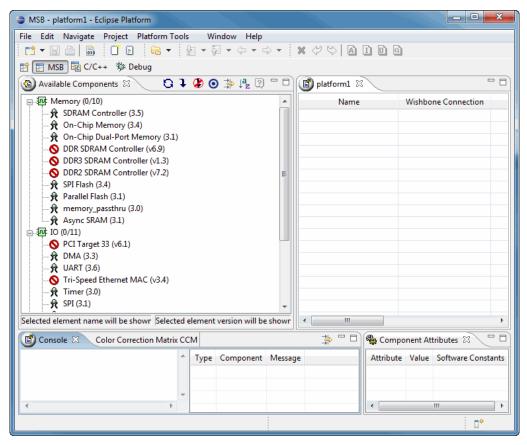

The LatticeMico System interface now appears, as shown in Figure 9.

Figure 9: LatticeMico System Interface

- 4. In the upper left-hand corner of the graphical user interface, select **MSB**, if it is not already selected, to open the MSB perspective.

- 5. Choose File > New Platform.

- 6. In the New Platform Wizard dialog box, make the following selections:

- a. In the Platform Name box, enter platform1.

- b. In the Directory box, browse to the lm32 tutor directory and click **OK**:

- For Windows, <Diamond\_install\_path>\examples\Im32\_tutor

- For Linux, ~/LatticeMico32/Im32\_tutor

- c. Do one of the following:

- If you are generating a platform in Verilog, leave the Create VHDL Wrapper unselected.

- If you are generating a platform in mixed Verilog/VHDL, select only Create VHDL Wrapper.

- d. In the Arbitration scheme box, select **Shared Bus (Default)** from the drop-down menu, if it is not already selected.

- e. In the Device Family section, select **LatticeECP2** from the Family menu and **LFE2-50E** from the Device menu.

- f. In the Platform Templates box, select blank.

Templates are pre-created platforms that facilitate rapid development. They target the LatticeMico32/DSP Development Board for LatticeECP2. Each platform also has an associated constraint file that you can import into Diamond to avoid the effort of creating a constraints file. MSB gives you the flexibility of creating and adding your own custom templates and associated constraints files for the LatticeMico32/DSP development board or a custom board, in addition to using the templates provided as part of the installation package.

The New Platform Wizard dialog box should look like the illustration in Figure 10.

Figure 10: New Platform Wizard Dialog Box

7. Click Finish.

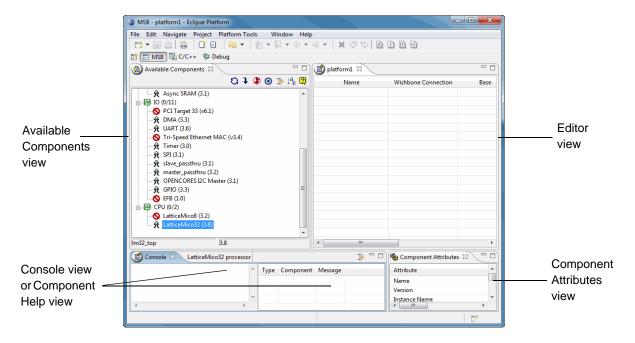

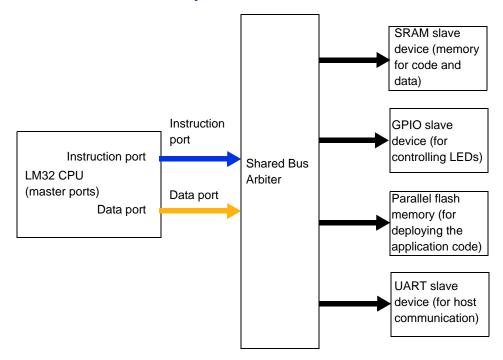

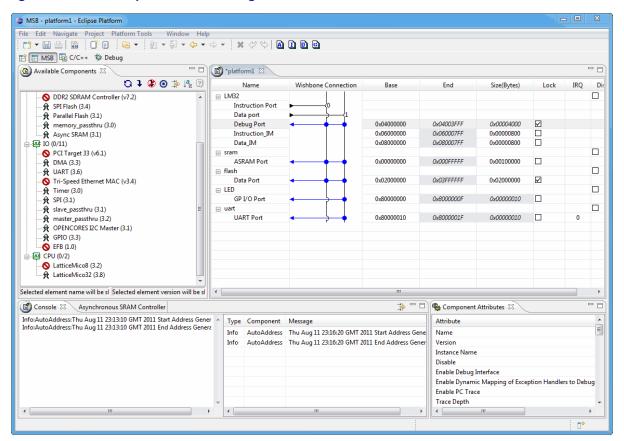

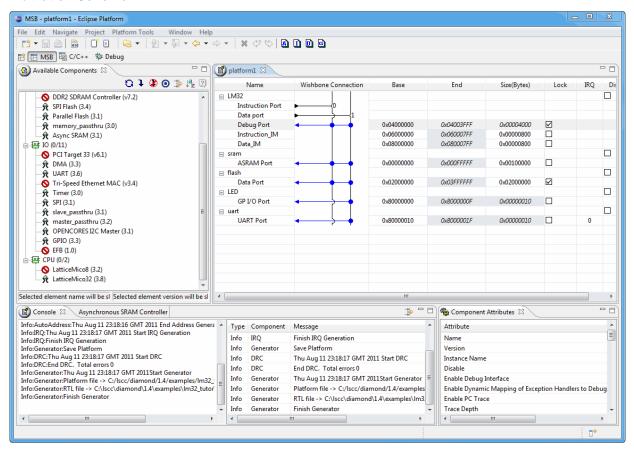

The MSB perspective now appears, as shown in Figure 11.

Figure 11: MSB Perspective

The MSB perspective consists of the following views:

- Available Components view, which displays all the available components that you can use to create the design:

- A list of hardware components: microprocessor, memories, components, and bus interfaces. Bus interfaces can be masters or slaves (see "Specify the Connections Between Master and Slave Ports" on page 27 for more information on masters and slaves). The component list shown in Figure 11 is the standard list that is given for each new platform.

- A list of preconfigured systems: demonstrations and pre-verified configurations for a given development board or a configuration that you previously built

You can double-click on a component to open a dialog box that enables you to customize the component before it is added to the design. The component is then shown in the Editor view.

- Editor view, which is a table that displays the components that you have chosen in the Available Components view. It includes the following columns:

- Name, which displays the names of the chosen components and their ports

- Wishbone Connection, which displays the connectivity between master and slave ports

- Base, which displays the start addresses for components with slave ports. This field is editable.

- End, which displays the end addresses for components with slave ports. This field is not editable. The value of the end address is equivalent to the value of the base address plus the value of the size.

- Size (Bytes), which displays the number of addresses available for component access. This field is editable for the LatticeMico on-chip memory (EBR) and the LatticeMico asynchronous SRAM controller components only.

- Lock, which indicates whether addresses are locked from any assignments. If you lock a component, its address will not change when you select Platform Tools > Generate Address.

- IRQ, which displays the interrupt priorities of all components that have interrupt lines connected to the LatticeMico32 microprocessor. The LatticeMico32 microprocessor can accept up to 32 external interrupt lines.

- Disable, which indicates whether components are temporarily excluded from the design

- ◆ Component Help view, which displays information about the component that you selected in the Available Components view. The Help page displays the name of the component—for example, "LatticeMico Timer" or "LatticeMico UART—and gives a brief description of the function of the component. It also provides a list and explanation of the parameters that appear in the dialog box when you double-click the component. If you click the icon next to the component name, you can view a complete description of the component in a PDF file.

- Console view, which displays informational and error messages output by MSB

- Component Attributes view, which displays the name, parameters, and values of the component selected in the Available Components view or the Editor view. This view is read-only.

## **Add the Microprocessor Core**

The first step in building the platform is to add the microprocessor core. In this release, only the LatticeMico32 microprocessor is available.

You will be using the default cache setting for this task. Refer to the LatticeMico32 Processor Reference Manual for more information on caches.

To add the microprocessor core:

1. Under CPU in the Available Components view, click **LatticeMico32** to view the information available about the LatticeMico32 microprocessor.

Information about the LatticeMico32 microprocessor, including the parameters that you can set for it, now appears in the Component Help view and in the Component Attributes view in the lower third of the screen. If you click the icon in the Component Help view, you can view the LatticeMico32 Processor Reference Manual, which provides a complete description of the microprocessor.

- Similarly, if you click this icon for a memory or a peripheral component, you can view the data sheet about that component.

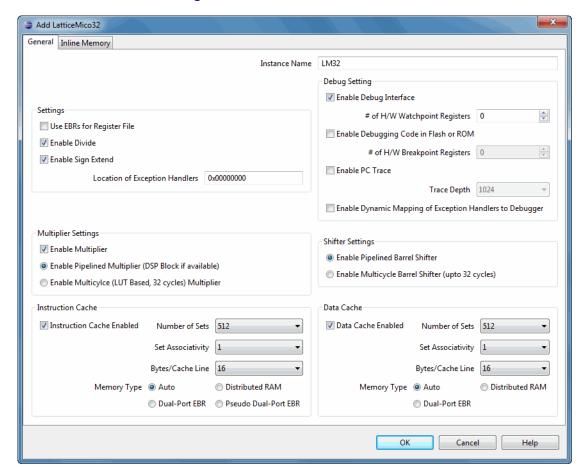

- 2. Double-click **LatticeMico32** to open the Add LatticeMico32 dialog box. Alternatively, you can select **LatticeMico32**, and then click the Add Component button ( ).

The parameters in the dialog box, shown in Figure 12 on page 19, correspond to those in the table in the Component Help view.

You are defining a development LatticeMico32 microprocessor. The LatticeMico32 microprocessor component, when the Enable Debug Interface option is selected, has an internal Embedded Block RAM memory attached to the Wishbone bus. This memory is automatically initialized with LatticeMico opcodes. This means that when the LatticeMico32 microprocessor comes out of reset, it has a valid set of opcodes to execute. The LatticeMico32 microprocessor needs only a few key elements to operate correctly: a good input clock, a reset strobe assertion and de-assertion, and a set of known good opcodes. During the development process, the Debug Monitor memory attached to the LatticeMico32 Wishbone bus is the only guaranteed source of known good opcodes. It is of vital importance for the Reset Exception Address to point to this memory. By default, the Debug Port Base Address is assigned to 0x00000000. This address can be changed, but it is important that the Reset Exception Address be updated to match the Debug Port Base Address.

This tutorial will leave the Debug Port Base Address set to 0x00000000.

- 3. In the Add LatticeMico32 dialog box, do the following:

- a. Select the **General** tab. If it is not already set as default, type **0x0000000** in the "Location of Exception Handlers" box to set the LatticeMico32 reset vector, as shown in Figure 12 on page 19. This step sets the reset exception address, which is the address from where the microprocessor will begin fetching instructions at power-up. This address must be aligned to a 256-byte boundary.

Under the section Instruction Cache, select Instruction Cache Enabled.

Figure 12: Add LatticeMico32 Dialog Box - General Tab

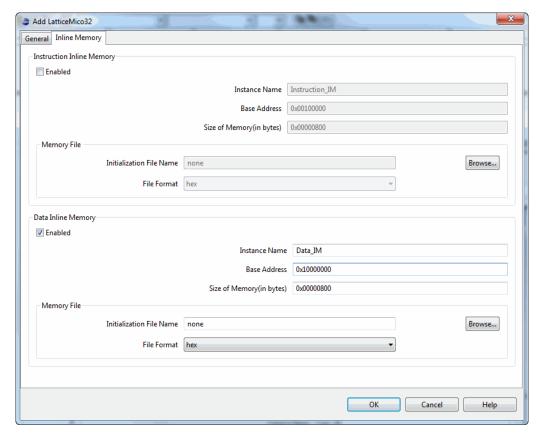

- c. Select the Inline Memory tab. Under the section Data Inline Memory, select Enabled. If it is not already set as default, type 0x1000000 in the Base Address text box, as shown in Figure 13 on page 20.

- d. Click **OK** to accept the default settings for the rest of the options. Information about the microprocessor now appears in the Name, Wishbone Connection, Base, End, and Size columns of the table in the Editor view.

Figure 13: Add LatticeMico32 Dialog Box – Inline Memory Tab

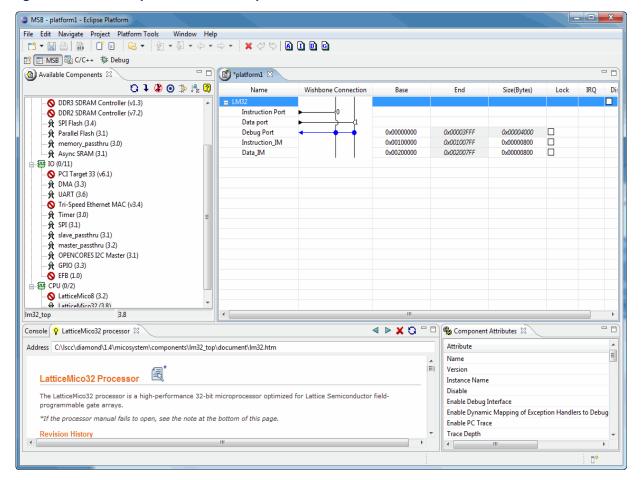

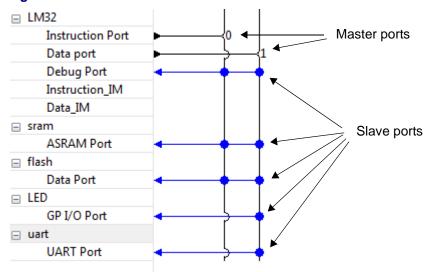

The MSB perspective now shows the LatticeMico32 microprocessor in the Editor View, as shown in Figure 14.

Figure 14: MSB Perspective with Microprocessor

The Wishbone Connection column graphically displays the types of ports and connections. Black horizontal lines with outbound arrows indicate master ports, whereas blue horizontal lines with inbound arrows indicate slave ports. The vertical lines are associated with master ports, and the filled circles indicate connections between master and slave ports. The illustration shows that the microprocessor's slave Debug Port is connected to the master Instruction Port and Data Port.

### Add the Off-Chip Memory

Next you will add the LatticeMico asynchronous SRAM controller and the parallel flash memory.

#### Add the Asynchronous SRAM Controller

The LatticeMico asynchronous SRAM controller is required to download and execute the software application code. The LatticeMico32/DSP development board has two 4-megabit asynchronous SRAM modules organized as 256K x 32, giving a total of 1 megabyte of asynchronous SRAM memory. This SRAM shares the data and address buses with the on-board parallel flash memory chips that are organized as 8M x 32. The wen and oen common control signals are also shared, although each memory type (SRAM, parallel flash memory) has its own chip select.

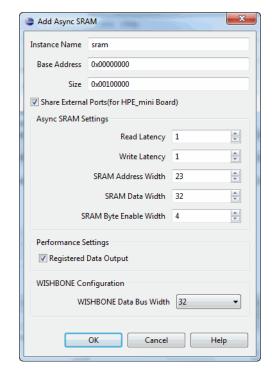

To add the asynchronous SRAM memory to the platform:

Under Memory in the Available Components view, double-click Async SRAM to open the dialog box. Alternatively, you can select Async SRAM, and then click the Add Component button .

In the Add Async SRAM dialog box, shown in Figure 15, the SRAM size is 1 megabyte. However, it shares the address bus with the flash device pair. The address bus size will be adjusted to the correct width when the flash memory peripheral is configured next in the tutorial. When "Share External Ports" is selected, the asynchronous memory component with the largest Address Width entry defines the size of the address bus.

Figure 15: Add Async SRAM Dialog Box

#### Note

You can delete a component from the Editor view by right-clicking the component in the Editor view and selecting **Remove Component** from the pop-up menu. If you cannot remove a component, this command will be unavailable on the menu.

2. Accept the default settings in the dialog box, and click **OK**.

#### Note

The read and write latencies of the Async SRAM controller are based on the read and write latencies of the Async SRAM on the board. They are measured in WISHBONE clock cycles and therefore the clock frequency of the design. The current design operates at 25 MHz and a read/write latency of 1 is sufficient for the Async SRAM on the board. For every 25 Mhz increase in clock frequency, the read/write latencies must be increased by 1. For example, if the design were operating at 50 MHz, the read/write latencies would be set to 2.

#### **Add the Parallel Flash Memory**

The LatticeMico32/DSP development board has two 16-bit-wide, 16-megabyte Common Flash Interface (CFI) parallel flash components. These two flash devices together appear as a 8M x 32 flash component. This flash pair will be used for software deployment.

To add the parallel flash component to the platform:

- Under Memory in the Available Components view, double-click Parallel Flash to open the dialog box. Alternatively, you can select Parallel Flash, then click the Add Component button .

- 2. In the Add Parallel Flash dialog box, shown in Figure 16 on page 24, do the following:

- a. In the Base Address box, change the address to **0x02000000**.

- b. In the Size box, change the size to 0x02000000.

The parallel Flash memory is placed at address 0x02000000 because of the address decode scheme used by the LatticeMico system. All components in a LatticeMico32 platform must be aligned to an address that corresponds to the largest Size(Bytes) entry. The LatticeMico32 address space is divided into two 2GByte ranges. Addresses below the 2GB boundary are memory components. Addresses above the 2GB boundary are I/O components. The alignment of components are based on the memory range in which they reside. In this tutorial, the largest memory block is the 32MByte parallel Flash component. This means that all memory components must be 32MB-aligned. Therefore, valid base addresses for memory components are 0x000000000, 0x20000000, 0x40000000, 0x60000000, and so forth.

The flash address bus is shared with the SRAM address bus. The flash is addressed as 8Mx32, but the address width must be wide enough to address 32Mx8, so 25 address bits are required. Make sure that the FLASH Address Width option is set to 25 bits wide to ensure that there are enough address bits to access the 1Mx8 SRAM block and the 32Mx8 flash memory block.

Figure 16: Add Parallel Flash Dialog Box

c. Click **OK** to accept the default settings for the rest of the options.

#### **Note**

NOTE: The read and write latencies of the Parallel Flash controller are based on the read and write latencies of the Parallel Flash on the board. They are measured in WISHBONE clock cycles and therefore the clock frequency of the design. The current design operates at 25 MHz and a read/write latency of 1 is sufficient for the Parallel Flash on the board. For every 25 Mhz increase in clock frequency, the read/write latencies must be increased by 1. For example, if the design were operating at 50 MHz, the read/write latencies would be set to 2.

## **Add the Peripheral Components**

Now you will add the peripheral components to the platform.

#### **Add the GPIO**

The first peripheral component that you will add is the LatticeMico GPIO component, which provides a memory-mapped interface between a WISHBONE port and general-purpose I/O ports. The I/O ports connect either to on-chip user logic or to I/O pins that connect to devices external to the FPGA.

#### To add the GPIO to the platform:

- Under IO in the Available Components view, double-click GPIO.

Alternatively, you can select GPIO, then click the Add Component button

- 2. In the Add GPIO dialog box, shown in Figure 17 on page 25, do the following:

- a. In the Instance Name box, change the name of the GPIO to LED.

For this tutorial, the GPIO block must be named LED. Failure to name the GPIO block LED will cause mismatches in the FPGA I/O pin names. The example C source code uses this instance name to access the GPIO registers.

- b. Change the setting of the Data Width option to 8.

Figure 17: Add GPIO Dialog Box

c. Click **OK** to accept the default settings for the rest of the options.

#### Add the UART

The final component that you will add is a LatticeMico universal asynchronous receiver-transmitter (UART), a core that contains a receiver and a transmitter. The receiver performs serial-to-parallel conversion of the asynchronous data frame received at its serial data input pin. The transmitter performs parallel-toserial conversion on the 8-bit data received from the CPU.

To add the UART to the platform:

- 1. Under IO in the Available Components view, double-click **UART** to open the dialog box. Alternatively, you can select UART, and then click the Add Component button (1).

- 2. In the Add UART dialog box, shown in Figure 18, click OK to accept the default settings.

Figure 18: Add UART Dialog Box

The MSB perspective now resembles the illustration in Figure 19.

Figure 19: MSB Perspective After Addition of All Components in a Shared-Bus Arbitration Scheme

# **Specify the Connections Between Master and Slave Ports**

The connections that you will make between the master and slave ports in the Editor view will reflect the access scheme shown in Figure 1 on page 4.

The following information applies to master and slave ports in the Editor view:

- There are two types of ports: master ports and slave ports.

- A master port can initiate read and write transactions.

- A slave port cannot initiate transactions but can respond to transactions initiated by a master port if it determines that it is the targeted component for the initiated transaction.

- A master port can be connected to one or more slave ports.

- A component can have one or more master ports, one or more slave ports, or both.

- Horizontal lines with outbound arrows sourced from a component port indicate a master port.

- Horizontal lines with inbound arrows targeting a component port indicate a slave port.

- The vertical lines are associated with horizontal lines with outbound arrows (that is, master ports) to facilitate "connectivity" from a master port to a slave port. A circle represents the intersection of the vertical line and a horizontal line associated with a slave port.

- A filled circle indicates a connection between the master port represented by the vertical line and the slave port represented by the horizontal line associated with the filled circle.

- A hollow circle indicates an absence of connection between the master port represented by the vertical line and the slave port represented by the horizontal line associated with the hollow circle. This can be seen in Figure 19 on page 27, where only the LatticeMico32 microprocessor Wishbone ports are connected.

- The numbers next to the lines representing the master ports are the priorities in which the master ports can access the slave ports. You can change the priority of these connections by following the instructions in the online Help for LatticeMico System.

To specify the connections between master and slave ports:

- Connect the instruction and data ports to the LatticeMico asynchronous SRAM controller slave port by clicking both circles in the Wishbone Connection column of the ASRAM Port row.

- Connect the instruction and data ports to the LatticeMico parallel flash slave port by clicking both circles in the Wishbone Connection column of the Data Port row.

- 3. Connect the data port to the LatticeMico GPIO slave port by clicking the circle in the Wishbone Connection column of the GP I/O Port row.

- 4. Connect the data port to the LatticeMico UART slave port by clicking the circle in the Wishbone Connection column of the UART Port row.

- Figure 20 on page 29 shows the resulting connections in the Editor view.

This tutorial example uses the shared-bus arbitration scheme. For information about bus arbitration schemes, refer to the *LatticeMico32 Software Developer's User Guide*. The master ports are represented by black lines, and the slave ports are represented by blue lines. Both the instruction and data ports connect to the *LatticeMico* asynchronous SRAM controller and the

parallel flash controller, but only the data port connects to the LatticeMico GPIO and the LatticeMico UART.

Figure 20: Connections for Shared Bus Arbitration

Figure 21 shows the connections generated by MSB. MSB automatically generates the arbiter, depending on which arbitration scheme is selected. In the case of the shared-bus arbitration scheme, it generates the microprocessor platform to allow multiple master ports access to multiple slave ports over a single shared bus. In the diagram, the instruction port accesses the LatticeMico asynchronous SRAM controller and the flash controller. The data port accesses the LatticeMico asynchronous SRAM

controller, the LatticeMico GPIO, the LatticeMico parallel flash controller, and the LatticeMico UART.

Figure 21: Connections Generated by MSB

## **Assign Component Addresses**

The next step is for MSB to generate an address for each component with slave ports. Addresses are specified in hexadecimal notation. Components with master ports are not assigned addresses.

#### Note

You can only edit the addresses in the Base column in the Editor View. You cannot edit the addresses in the End column. The value of the end address is equivalent to the value of the base address plus the value of the size.

You will not assign individual addresses. There are only two addresses that need to be manually assigned: the Debug Memory and the Parallel Flash Memory.

During the creation of the Parallel Flash component, you explicitly assigned an address (0x02000000) to the parallel flash component and the Inline Data memory. You must lock the parallel flash address so that MSB will not automatically assign it a new address. You do not want the flash address to change for this example, because that is where the final software application code will reside.

To lock the address:

1. In the Lock column, select the box for the parallel flash (flash).

2. In the Lock column, select the box for the Debug Port.

To automatically assign component addresses:

Choose Platform Tools > Generate Address, or click the Generate

Base Address button (A), or right-click in the Editor view and choose

Generate Address from the pop-up menu.

The addresses now appear in the Base and End columns in the Editor view, in hexadecimal notation. Slave components that are not memories are assigned addresses within the 0x80000000-0xFFFFFFF memory range. The Generate Address command sets A31 of each of the I/O components to '1'.

#### Note

Address and size values that appear in italic font in the Editor view cannot be changed.

Your MSB perspective should now resemble the example shown in Figure 22. The base addresses that you see in your Editor view might be different from those shown.

Figure 22: MSB Perspective After Assignment of Addresses in a Shared-Bus Arbitration Scheme

## **Assign Interrupt Request Priorities**

The interrupt request priority is the order in which hardware components request computing time from the CPU. Now you will assign an interrupt request priority (IRQ) to all components that feature a dash in the IRQ column of the Editor view. You cannot assign interrupt priorities to components lacking this dash in the IRQ column, such as memories and CPUs.

To assign interrupt priorities for all components providing interrupt functionality:

Choose Platform Tools > Generate IRQ, or click the Generate IRQ button (II), or right-click in the Editor view and choose Generate IRQ from the pop-up menu.

#### **Note**

To reassign an interrupt priority for a specific component, go to the IRQ column in the row for the component, click on the current interrupt priority number, and choose the new priority number from the drop-down menu. Explicitly assigned interrupt priorities will not be overridden by the interrupt generator tool. The Lock control does not affect IRQ assignment; it only prevents auto-assignment of the Base Address.

If you accidentally assign duplicate priorities, MSB will issue an error message in the Console view when you select **Platform Tools > Generate IRQ**.

## Perform a Design Rule Check

You will want to perform a design rule check to verify that components in the platform have valid base addresses, interrupt request values, and other fundamental properties.

To perform a design rule check:

Choose Platform Tools > Run DRC, or click the Run DRC button (D), or right-click in the Editor view and choose Run DRC from the pop-up menu.

In the Console view, MSB shows that there are no errors in the platform.

## **Generate the Microprocessor Platform**

You are now ready to generate the microprocessor platform. During the generation process, MSB creates the following files in the ..\Tutorial\lm32 tutor\platform1\soc directory:

- A platform1.msb file, which describes the platform. It is in XML format and contains the configurable parameters and bus interface information for the components.

- A platform1.v (Verilog) file, which is used by both Verilog and mixed Verilog/VHDL users:

- For Verilog users, the platform1.v file is used in both simulation and implementation. It instantiates all the selected components and the

interconnect described in the MSB graphical user interface. This file is the top-level simulation and synthesis RTL file passed to Diamond. It includes the .v files for each component in the design. These .v files are used to synthesize and generate a bitstream to be downloaded to the FPGA. The first time Generate is run, the Verilog source for each component in the platform, which is located in <Diamond\_install\_path>/micosystem/components/<component>, is copied into a subdirectory called "components." The components subdirectory is a sibling to the *soc* subdirectory.

For mixed Verilog/VHDL users, the platform1.v file is used in simulation only.

A mixed-mode Verilog and VHDL simulator, such as Aldec<sup>®</sup> Active-HDL™, is needed for functional simulation.

- A platform1\_vhd.vhd (VHDL) file is created if you selected the "Create VHDL Wrapper" option in the New Platform Wizard dialog box. It is intended to be used only to incorporate the Verilog-based platform into a mixed Verilog/VHDL design. The platform1\_vhd.vhd contains the top-level design used for synthesis. This top-level design file instantiates the platform1 component.

- A platform1.ngo file, if you selected both the Create VHDL Wrapper and the Create VHDL NGO File options in the New Platform Wizard dialog box. The .ngo file is required for Linux Verilog/VHDL users. It is a synthesized version of platform1.v.

The contents of the platform1.msb file are used by the C/C++ development tools. The C/C++ source code build process extracts the base address information and the size of each component and uses the information to build GNU LD linker files. Each time the Generate function is run, it causes the C/C++ compiler to consider the C/C++ source code to be out of date. This means that the source code will be rebuilt from scratch after each Generate process.

To generate the microprocessor platform:

Click anywhere in the Editor view and choose Platform Tools > Run Generator, or click the Run Generator button (), or right-click and choose Run Generator from the pop-up menu.

The Console view displays the output as MSB processes the design.

If you are using Verilog, you will see Finish Generator in the Console view when the generator is finished. If the project was created with the "Create VHDL Wrapper" option selected, the project is a mixed Verilog/VHDL flow and the generator silently launches Synplify synthesis and Diamond to create the wrapper. If you are using mixed Verilog/VHDL, you must wait for the Finish VHDL Wrapper message to appear in the Console view.

The MSB perspective now looks like the illustration in Figure 23. The assigned addresses for the components other than the parallel flash might differ.

Figure 23: MSB Perspective After Building the Microprocessor Platform in a Shared-Bus Arbitration Scheme

As shown in Figure 24, MSB generates a platform1\_inst.v file, which contains the Verilog instantiation template for use in a design where the platform is not the top-level module. For a mixed Verilog/VHDL project, no equivalent file is generated.

#### Figure 24: Verilog Instantiation Template

```

platform1 platform1 u (

.clk i(clk i),

.reset n(reset n)

, .sramsram csn(sramsram csn) //

, .sramsram be(sramsram be) // [4-1:0]

, .flashsram_csn(flashsram_csn) //

.flashsram be(flashsram be) // [4-1:0]

`ifdef FLASH_BYTE_ENB

, .flashsram byten(flashsram byten) //

`endif // FLASH BYTE ENB

`ifdef FLASH WP ENB

, .flashsram_wpn(flashsram_wpn) //

`endif // FLASH WP ENB

`ifdef FLASH RST ENB

, .flashsram rstn(flashsram rstn) //

endif // FLASH RST ENB

, .LEDPIO OUT(LEDPIO OUT) // [10-1:0]

, .uartSIN(uartSIN) //

, .uartSOUT(uartSOUT) //

, .sramflashOEN(sramflashOEN)

, .sramflashWEN(sramflashWEN)

.sramflashADDR(sramflashADDR)// [24:0]

.sramflashDATA(sramflashDATA)// [31:0]

```

Figure 25 on page 36 shows the structure of the directory that MSB generates. The directory structure is created the first time the Generate process is run. The contents of the components subdirectory is only written the very first time the Generate function is run. After the first run it remains static. There is an exception: when a MSB project is opened after installing a new version of the LatticeMico System Builder, a new component version might exist. You are given an opportunity to update to the new component. Accepting the update will modify the components subdirectory.

#### Note

Figure 25 shows an example platform. The figure does not show the entire directory and file structure.

**Figure 25: MSB Directory Structure**

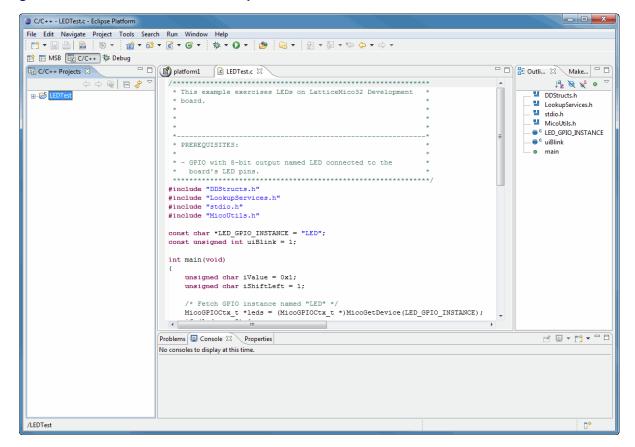

## Task 3: Create the Software Application Code

In this task, you create the software application by using C/C++ in the LatticeMico System Software Project Environment (C/C++ SPE). The software application is the code that runs on the LatticeMico32 microprocessor to control the components, the bus, and the memories. The application is written in C/C++.

C/C++ SPE is based on the Eclipse environment and provides an integrated development environment for developing, debugging, and deploying C/C++ applications. C/C++ SPE uses the GNU C/C++ tool chain (compiler, assembler, linker, debugger, and other necessary utilities) that has been customized for the LatticeMico32 microprocessor.

C/C++ SPE uses the same LatticeMico System interface as MSB, but it uses a different perspective called the C/C++ perspective.

To activate the C/C++ perspective:

◆In the upper left-hand corner of MSB graphical user interface, select C/C++.

The C/C++ perspective is shown in Figure 26.

File Edit Navigate Project Platform Tools □ B Outli... S Make... platform1 🗵 C/C++ Debug Por **Projects** Data\_IM view or m ΔSRΔM Por Navigator Outline view □ LED GP I/O Port UART Port Editor view of 🕒 • 👩 • 🖰 🗅 Problems Console S Properties lo consoles to display at this time.

Figure 26: C/C++ Perspective

Problems view, Console view, Properties view, Debug view, Tasks view, or Search view

The C/C++ perspective consists of the following views:

- C/C++ Projects view, which lists C/C++ SPE projects that have been created

- Navigator view, which shows all of the file system's files under the workspace directory

- Editor view, which is similar to the Editor view in the MSB perspective

- Outline view, which displays the structure of the file currently open in the Editor view

- Problems view, which displays any error, warning, or informational messages output by C/C++ SPE

- Console view, which displays informational messages output by the C/C++ SPE build process

- Properties view, which displays the attributes of the item currently selected in the C/C++ Projects view. This view is read-only.

- Search view, which displays the results of a search when you choose Search > File.

- Tasks view, which shows the tasks running concurrently in the background

- Make Targets view, which is not used in LatticeMico C/C++ projects

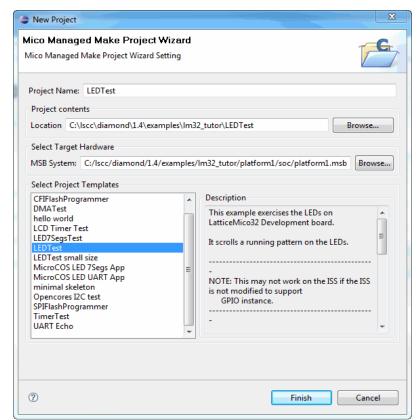

## Create a New C/C++ SPE Project

You will create a new project in C/C++ SPE, import the platform1.msb file into the project, select the application code template to use so that you do not have to write the code yourself, and compile the code.

To create a new C/C++ SPE project:

- In the C/C++ perspective, choose File > New > Mico Managed Make C Project.

- 2. In the New Project dialog box, make the following selections:

- a. In the Project Name box, enter **LEDTest**.

- b. In the Location box, browse to the following directory:

- For Windows, < Diamond\_install\_path>\examples\lm32\_tutor

- For Linux, ~/LatticeMico32/Im32\_tutor/platform1

- c. In the MSB System box, browse to the following location, select the **platform1.msb** file in the dialog box, and click **Open**.

- For Linux,

~/LatticeMico32/lm32 tutor/platform1/soc/platform1.msb

d. In the Select Project Templates box, select **LEDTest** as the template for the application code.

#### Note

Project templates are packaged software application files that are copied to the new project and provide a starting point for building an application. Some templates have specific requirements, as described in the description pane. If these hardware and software requirements are not met, the application built may not function correctly and may require you to debug the application by using the C/C++ SPE debug interface. C/C++ SPE enables you to create templates in addition to those included with the installation.

The New Project dialog box should resemble the figure shown in Figure 27.

Figure 27: New Project Dialog Box

#### **Note**

The directory shown in the Location box in the Project Contents field is where the software project directory will be created. Your user files will be placed in this directory.

Click Finish.

Now you see the source code in the middle pane of the C/C++ perspective, as shown in Figure 28.

Figure 28: Source Code in C/C++ Perspective

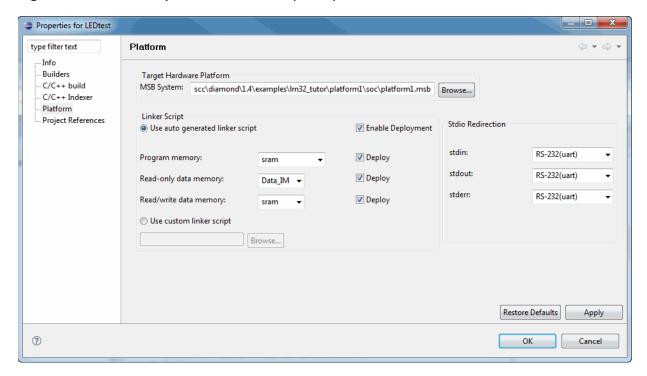

## **Linker Configuration**

A new C project is almost ready to be compiled and linked. Before you compile the source code, it is necessary to configure the linker. Every C/C++/ assembly file has, at a minimum, three fundamental sections that need to be placed.

The compiler splits the source code into an instruction section, a read-only data section, and a read-write section by default. The first two sections can be placed in either read-only or read-write memories, while the final section must be placed in a read-write memory. The C/C++ SPE provides you with an easy-to-use feature for selecting memories for each region.

Your platform contains three memory components: a data inline memory, a parallel flash memory, and an asynchronous SRAM memory. You will build the LEDTest application to run from the asynchronous SRAM memory and data inline memory.

The Properties dialog box enables you to select and change where the linker places each of the sections.

To modify how the linker assigns each section:

- 1. Make sure that the LEDTest is selected in the C/C++ Projects view.

- 2. Choose Project > Properties.

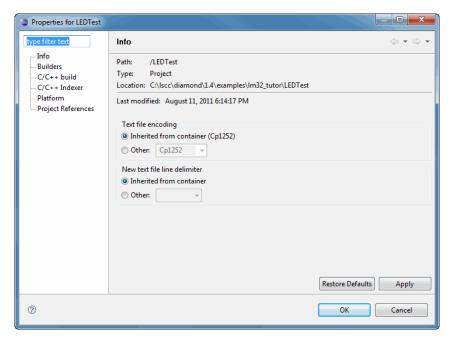

The Properties for LEDTest dialog box now appears, as shown in Figure 29.

Figure 29: Properties for LEDTest Dialog Box

You can select from the list on the left side of the Properties window to open one of the following panes:

- ◆ Info provides basic project location information.

- Builders provides information on the builder system used for this managed build project. It is preconfigured to use the LatticeMico builder system.

- C/C++ Build enables you to select and manage the compiler, assembler, and linker settings.

- C/C++ Indexer enables you to specify the indexing method for searches: fast, full, or no indexer.

- Platform provides information on the platform used by this project, in addition to other information such as the linker section setting.

- Project References enables you to manage other projects referenced by the current project. Project References cannot be used for the LatticeMico C/C++ SPE managed build environment.

- 3. Select the **Platform** pane.

OK

Cancel

?

The Target Hardware Platform text box shows the current MSB platform. You can change the hardware platform used by the software application, but you must rebuild the software application.

The options in the Linker Script section enable you to select your own linker script. However, for this tutorial you will use the auto-generated (default) linker script. For the auto-generated linker script, you can specify the memories that will be used for the linker sections. The C/C++ SPE managed build process inspects the specified MSB platform to determine the available memory regions. As a default, the C/C++ SPE managed build process selects the largest read/write memory available to contain all the sections. For this tutorial, you will select the SRAM for program and read/write data memory sections, and it will select Data Inline Memory for read-only data memory sections.

- 4. In the Linker Script section, make the following selections from the drop-down menus, as shown in Figure 30:

- For Program memory, select sram.

- For Read-only data memory, select Data\_IM.

- For Read/write data memory, select sram.

- - X Properties for LEDTest type filter text Platform Builders Target Hardware Platform C/C++ build MSB System: C:\lscc\diamond\1.4\examples\lm32\_tutor\platform1\soc\platform1.m Browse... C/C++ Indexer Platform Linker Script Project References Stdio Redirection Use auto generated linker script Enable Deployment JTAG UART(LM32) ▼ Deploy Program memory: stdout: JTAG UART(LM32) ▼ Deploy Read-only data memory: stderr: JTAG UART(LM32) ▼ Deploy Read/write data memory: Use custom linker script Browse... Restore Defaults

Figure 30: Platform Pane of the Properties for LEDTest Dialog Box

5. Click **OK** to return to the C/C++ perspective.

## **Build the Project**

The next step is to build the project, in which C/C++ SPE compiles, assembles, and links your application code, as well as the system library code provided by C/C++ SPE.

To compile the project:

In the C/C++ Projects view (left-hand pane), select LEDTest and choose Project > Build Project. Do not click on any of the buttons in the Build Project dialog box.

The compilation process generates the following files, among others, in the LEDTest\platform1 directory:

- A C header file, DDStructs.h, that describes the device-driver structures for the applicable devices, in addition to the relevant platform settings, such as the microprocessor clock frequency

- A C source file, DDStructs.c, that describes the component instance parameters required by the device drivers in appropriate structures

- A C source file, DDInit.c, that invokes specified device initialization routines for putting the relevant instantiated components in a known state

- A linker script, linker.Id (in LEDTest\platform1\Debug), that contains the location and size of the memory components and the rules for generating an executable file image, as required by the GNU linker. C/C++ SPE uses this information to ensure that the program code and data are located at the correct addresses. Although it is not covered in this tutorial, the LatticeMico C/C++ SPE enables you to easily specify a custom linker script to be used in lieu of the generated script for the managed build.

- ◆ A LatticeMico software executable linked formal file (.elf). The .elf file contains the Mico instructions, debug information, and information about the pre-initialized data. This tutorial generates a file called platform1.elf.

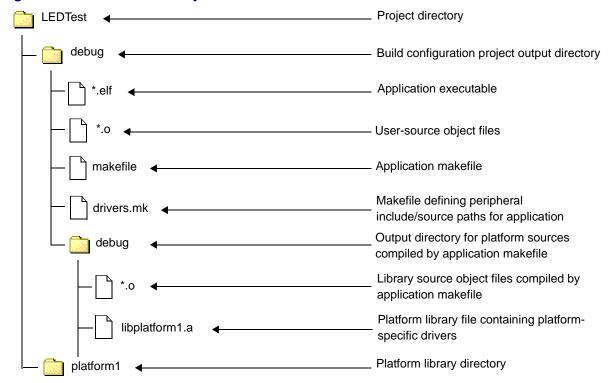

These files are included in the directory that C/C++ SPE generates in the background. The structure of this directory is shown in Figure 31 on page 44.

The contents of this directory are dynamically generated, and any changes to them are overwritten from build to build.

#### **Note**

Only the most important files are shown in Figure 31.

Figure 31: C/C++ SPE Directory Structure

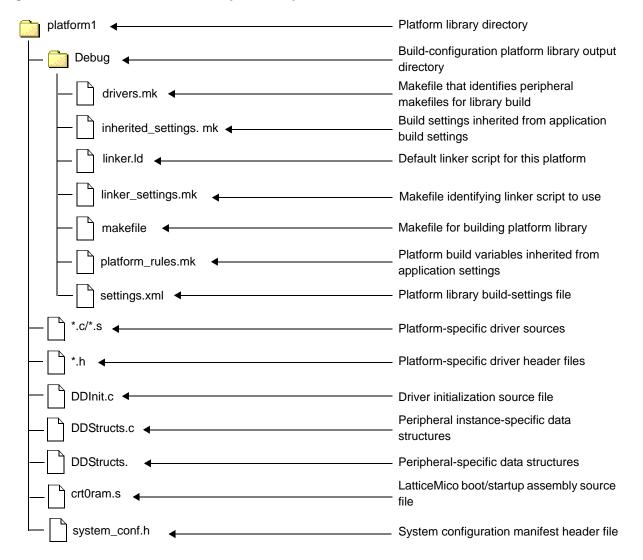

The platform1 library directory shown in Figure 31 contains platform-specific information for the building of an application.

Figure 32 shows the automatically generated files in this directory that are required to build an application. The contents of this directory are generated dynamically, and any changes to them are not preserved from build to build.

#### **Note**

Only the most important files are shown in Figure 32.

Figure 32: LEDTest\Platform1 Library Directory Structure

# Task 4: Synthesize the Platform to Create an EDIF File (Linux Only)

If you are performing this tutorial on Linux, you must now synthesize your platform to create an EDIF file. However, before you use Synopsys Synplify Pro or Mentor Graphics Precision RTL Synthesis to do this, you must take some preliminary steps.

## **Using Synopsys Synplify Pro**

Before you use Synopsys Synplify Pro to generate an EDIF file, add the platform1.v file to your Synplify Pro project. If you are generating a platform using mixed Verilog/VHDL, also add the platform1\_vhd.vhd file.

## **Using Mentor Graphics Precision RTL Synthesis**

Before you use Mentor Graphics Precision RTL Synthesis to generate an EDIF file, do the following:

- Add the platform1.v file to your Precision RTL Synthesis project If you are generating a platform using mixed Verilog/VHDL, also add the platform1\_vhd.vhd file.

- 2. Add the following directory paths to your Precision RTL Synthesis search path:

- <plantform name>/soc

- cplatform\_name>/components/lm32\_top/rtl/verilog

- /components/<uart\_core>/rtl/verilog, where

<uart\_core> is the name of the UART

- <pr

If your platform includes an OPENCORES I2CM component, you must add another directory to the search path as follows:

<platform\_name>/components/i2cm\_opencores/rtl/verilog

#### Create the EDIF File

Now you can create the EDIF file.

To create an EDIF file using your synthesis tool, follow these general steps:

- 1. Start the synthesis tool.

- 2. Create a new project in the tool.

- 3. Add the Verilog HDL file output by MSB to the project. If your platform uses mixed Verilog/VHDL, also add the <platform name>.vhd.vhd file.

- 4. If you are using Precision RTL Synthesis, add the search paths.

- 5. Set the target device and the options.

- 6. Compile the project and specify the timing objectives.

- 7. Synthesize the design to generate an EDIF (.edn or .edf) file.

See the *Synthesis Data Flow Tutorial* for step-by-step information about synthesizing designs in Precision RTL Synthesis and Synplify Pro.

## Task 5: Generate the Microprocessor Bitstream

The next step in the flow is to generate the microprocessor bitstream file. This bitstream file is then downloaded to the FPGA on the circuit board. To generate the bitstream file, return to Diamond.

## Import the MSB Output File

First, you must import the Verilog file output by MSB, the Verilog and VHDL files for mixed Verilog/VHDL, or the EDIF file created by the synthesis tool into Diamond.

The process of importing the generated platform file into Diamond is the same for Verilog and mixed Verilog/VHDL, except that you must import the VHDL wrapper file in addition to the Verilog file for mixed Verilog/VHDL.

#### **Configure the Lattice Diamond Environment**

The Diamond build process has the ability to operate in two different modes. One is to copy all HDL source files into the Diamond project directory, and the other is to reference them in their current directory structure. The LatticeMico build requires that the source files remain in the directory structure created by MSB. The default Diamond behavior is to leave the files where they are, but it is advisable to verify that Diamond is configured correctly.

- 1. In Diamond, choose Tools > Options.

- Under Environment, in the left pane of the Options dialog box, select General.

- 3. If the option "Copy file to Implementation's Source directory when adding existing file" is selected, clear this option and click **OK**.

#### Importing the Source Files on Windows

On Windows, you import the HDL source files generated by MSB into Diamond. If your design is in Verilog only, you will import the platform1.v file. If your design is a mixed Verilog/VHDL design, you will import both the platform1\_vhd.vhd file and the platform.v file.

To import the Verilog or Verilog/VHDL files for the tutorial example:

- 1. In Diamond, choose File > Add > Existing File.

- 2. In the dialog box, browse to the ..\platform1\soc directory:

- For Windows,<Diamond install path>\examples\lm32 tutor\platform1\soc

- For Linux, ~/LatticeMico32/lm32 tutor/platform1/soc/

- 3. Do one of the following:

- Select the platform1.v file (Verilog), and click Add.

- If your design is mixed Verilog/VHDL, select both the platform1.v file and the platform1\_vhd.vhd file and click Add.

- 4. If your design is mixed Verilog/VHDL, perform the following additional steps:

- a. Choose Project > Property Pages.

- c. In the right pane, click inside the Value cell for "Top-Level Unit" and select <*platform1*>\_vhd from the drop-down menu.

- d. Click inside the Value cell for "Verilog Include Search Path," and then click the browse button to open the "Verilog Include Search Path" dialog box.

- e. In the dialog box, click the New Search Path button , browse to the platform1>\soc directory, and click **OK**.

- f. Click **OK** to add the path to the Project Properties and close the "Verilog Include Search Path" dialog box.

- g. Click **OK** to return to the Diamond main window.

#### Importing the EDIF File on Linux

On Linux, you import the EDIF file generated by the synthesis tool into Diamond.

To import the EDIF (.edn or .edf) file:

- 1. If you generated your platform using the VHDL wrapper, perform the following steps before importing the EDIF file. If you generated your platform in Verilog, skip these steps and proceed to Step 2.

- a. Choose Project > Property Pages.

- b. In the **Macro Path** text box on the right, type **platform1\soc** and click **OK**.

- 2. Choose File > Add Existing File.

- 3. Navigate to the location of your .edn or .edf file and click Add.

## Connect the Microprocessor to the FPGA Pins

You have two options for connecting the microprocessor to the FPGA pins:

- Manually create the pin constraints and import them into Diamond.

- Import a preconfigured preference file into Diamond.

For this tutorial, you will import a preconfigured pin preference file into Diamond.

To import the preconfigured pin preference file:

- 1. In Diamond, select the File List tab and double-click **Strategy1**.

- 2. In the Strategies dialog box, select **Translate Design** in the left pane.

- 3. In the right pane, double-click the cell in the Value column for "Consistent Bus Name Conversion."

- 4. Choose **Lattice** from the drop-down menu and click **OK**.

- 5. In Diamond, choose File > Add > Existing File.

- 6. In the Add Existing File dialog box, do the following:

- a. Select Constraint Files (\*.lpf) from the Files of type menu.

- b. Select the option Copy file to Implementation's Source directory.

- c. Navigate to the following directory, select the PlatformE.lpf file for the File Name box, and click **Add**.

<Diamond\_install\_path>\micosystem\platforms\PlatformE\

ECP2\HPE\_MINI.lpf

Diamond adds the .lpf file to the project and displays file name and path in the File List.

- In the File List pane, right-click HPE\_MINI.lpf and choose Set as Active Preference File.

- 8. Diamond displays the HPE\_MINI .lpf file and path in bold type, indicating that the HPE\_MINI will now be used instead of the platform1.lpf file.

#### **Perform Functional Simulation**

You can optionally simulate the functionality of the output top-level platform1.v or platform1\_vhd.vhd module by using a simulator such as Active-HDL in Diamond. See the Active-HDL online Help in Diamond for more information on this procedure.

- For Verilog simulation, you use platform1.v and all the Verilog files for each attached component.

- For mixed Verilog/VHDL simulation, you use platform1\_vhd.vhd, platform1.v, and all the Verilog files for each attached component. You must use a mixed-language simulator such as ModelSim<sup>®</sup> SE or Aldec Active-HDL.

**See Also** "Performing HDL Functional Simulation of LatticeMico Platforms" in the *LatticeMico32 Software Developer User Guide*.

## **Perform Timing Simulation**

You can optionally validate the timing of your design by performing timing simulation. Because timing simulation is a complex topic, it is not addressed in this tutorial. For information on timing simulation, see the *Achieving Timing Closure in FPGA Designs Tutorial*, the "Design Verification" topic in the Diamond online Help, or the "Strategies for Timing Closure" chapter of the *FPGA Design Guide*.

The timing simulation process automatically builds a database and maps, places, and routes the design.

#### Generate the Bitstream

Now you will generate a bitstream to download the microprocessor platform to the FPGA. If you did not perform timing simulation, the bitstream generation process will automatically synthesize, map, place, and route the design before it generates the bitstream.

To generate a bitstream (.bit) file:

- 1. In Diamond, select the Process tab.

- 2. In the Export Files section, double-click **Bitstream File**.

Diamond now generates a bitstream data file, platform1.bit, that is ready to be downloaded into the device. This process takes several minutes.

## Task 6: Download the Hardware Bitstream to the FPGA

The bitstream file generated in the previous section contains all the information required to program the LatticeECP2 FPGA. Lattice Semiconductor provides the Diamond Programmer tool that sends the programming bitstream to the FPGA over a parallel port or USB port communications link. Now you will use Programmer to download the hardware bitstream that you generated in the previous section to the FPGA on the board. For instructions on connecting the USB cable to the board, refer to the *LatticeMico32 Development Kit User' Guide for LatticeECP2*.

To download the bitstream to the FPGA on the board:

- 1. Remove any Lattice USB Programming cables from your system.

- Connect the power supply to the development board.

- Connect a USB cable from your computer to the LatticeMico32/DSP for ECP2 development board. The USB cable must be connected to the USB target connector adjacent to the keypad. Give the computer a few seconds to detect the USB device on the LatticeMico32/DSP for ECP2 development board before moving to step 3.

#### Note

A USB cable is included with the board.

- 4. In Diamond, choose Tools > Programmer.

- 5. In the Getting Started dialog box, choose Create a new Blank Project. and click OK. Leave the Import File to Current Implementation box checked. Programmer scans the device database, and then the Programmer view displays in Diamond.

#### Note

If the Programmer output window displays "Cannot identify detected device on row 1. Please manually select correct device," choose **LFE2-50E** from the Device column drop down menu.

- 6. In the Cable Settings dialog box on the right side of the Programmer window, do the following:

- a. In the Cable box, select USB.

- b. In the Port box, choose the only setting available in the drop-down menu, **FTUSB-0**.

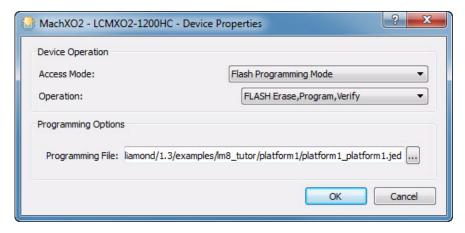

- 7. Double-click the Operation column to display the Device Properties dialog box, as shown in Figure 33, and choose the following settings:

- For Access Mode, choose JTAG 1532 Mode from the pull-down menu.

- For Operation, choose **Fast Program** from the pull-down menu,

- 8. Double-click the File Name column. Click \_\_\_\_ to display the Open File dialog box, and browse to the platform1\_platform1.bit file in the following directory:

- For Windows, <Diamond\_install\_path>\examples\lm32\_tutor\platform1\_platform 1.bit

- For Linux, ~/LatticeMico/lm32\_tutor/platform1\_platform1.bit

- 9. Click Open.

Figure 33: Device Properties Dialog Box.

10. Click OK.

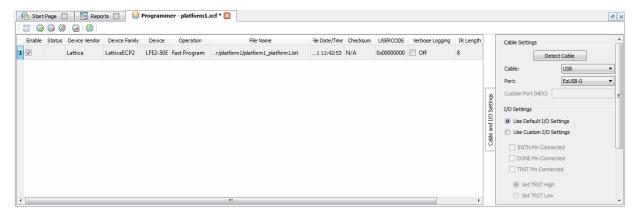

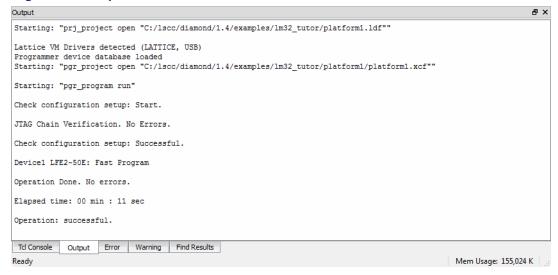

11. The Programmer view should look as shown in Figure 34.

- 12. Click the Program button on the Programmer toolbar to initiate the download.

- 13. Check the Programmer output console to see if the download passed, as shown in Figure 35. If the programming process succeeded, you will see a green-shaded PASS in the Programmer Status column.

**Figure 35: Programmer Output Console**

- 14. At the end of this process, the FPGA is loaded with the microcontroller hardware configuration.

- 15. In Diamond, choose File > Save platform1.xcf.

- 16. Exit Diamond by choosing File > Exit.

# Task 7: Debug and Execute the Software Application Code on the Development Board

In this task, you will use the debugger to download the executable file containing the software application code to the LatticeMico32/DSP development board. This enables the LatticeMico32 microprocessor, which is part of the FPGA bitstream you downloaded in Task 5, to execute the application code.

This task assumes that you have successfully downloaded the platform FPGA bitstream to the development board in "Task 6: Download the Hardware Bitstream to the FPGA" on page 50.

If you encounter any problems with the debug session, refer to "Debug Session Troubleshooting" in the *Lattice Software Project Environment* online Help. This troubleshooting topic describes the most common problems encountered in launching a debug session and the reasons the debugger sometimes fails to operate.

## **Software Application Code Execution Flow**

The FPGA is now configured with the LatticeMico32 Development microprocessor platform. The order in which the LatticeMico32 microprocessor executes the software application code images is as follows:

- 1. The LatticeMico32 microprocessor starts execution at the address contained in its exceptions base address (EBA).

- This is the address you specified when you added the LatticeMico32 microprocessor core in Task 2.

- 2. When you start the LatticeMico System debugger, it communicates with the microprocessor over the microprocessor's debug module.

- The debug module is a collection of files inside the Im32\_top\rtl\verilog directory, as shown in Figure 25 on page 36. The debug module, in turn, generates a debug exception that causes the microprocessor to execute the debug monitor code. The LatticeMico32 microprocessor, in order to respond to the debug exception, must be running valid opcodes and must not be stuck waiting for a bus cycle to complete. Upon successful execution of the debug exception, the debug monitor code then communicates with the LatticeMico System debugger running on the host computer.

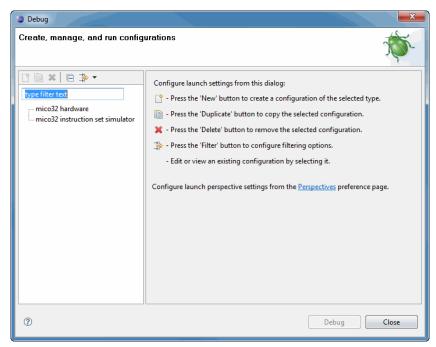

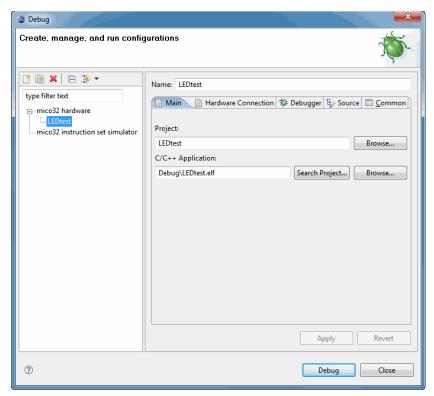

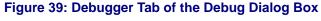

- 3. At this point, the debugger has control over the microprocessor and can access the platform's memory through the debug module or microprocessor to download the application to the selected memories.