# LatticeSC MPI/System Bus

April 2010 Technical Note TN1085

## Introduction

The embedded system bus on the LatticeSC™ ties all of the programmable elements together in a bus framework. There are two types of interfaces on the system bus, master and slave. A master interface has the ability to perform actions on the bus such as writes and reads to and from a specific address. A slave interface responds to the actions of a master by accepting data and address on a write and providing data on a read. The system bus has a memory map which describes each of the slave peripherals that is connected on the bus. Using the addresses listed in the memory map, a master interface can access each of the slave peripherals on the system bus. Any and all peripherals on the system bus can be used at the same time. Table 1 lists all of the available user peripherals on the system bus after device power-up.

Table 1. System Bus User Peripherals

| Peripheral                                         | Abbreviation | Interface Type |

|----------------------------------------------------|--------------|----------------|

| Micro Processor Interface                          | MPI          | Master         |

| User Master Interface                              | UMI          | Master         |

| User Slave Interface                               | USI          | Slave          |

| Serial Management Interface (PLL, DLL, User Logic) | SMI          | Slave          |

| flexiPCS™ Interface                                | PCS          | Slave          |

| Direct FPGA Access                                 | DFA          | Slave          |

The peripherals listed in Table 1 can be added when the system bus module is created using IPexpress™ (isp-LEVER® IPexpress).

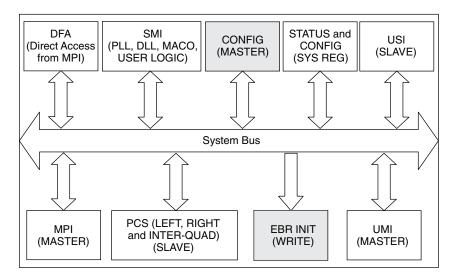

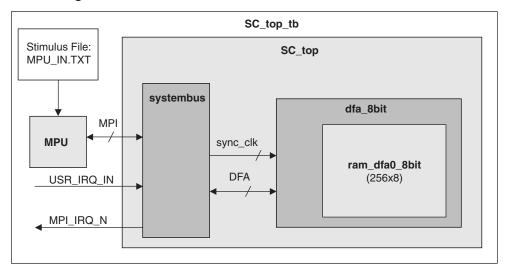

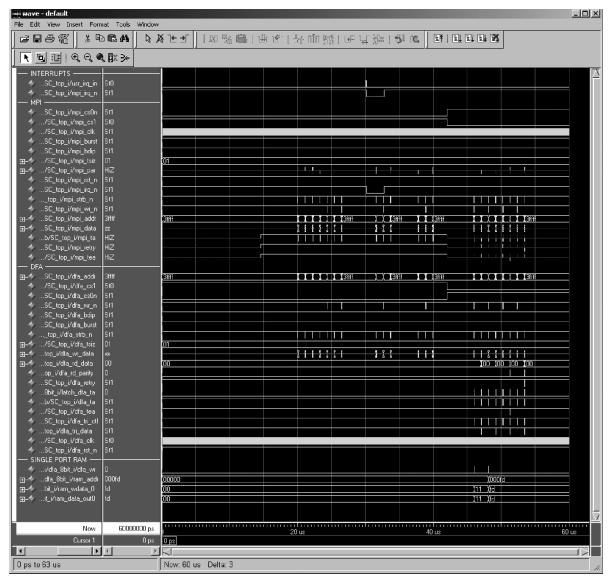

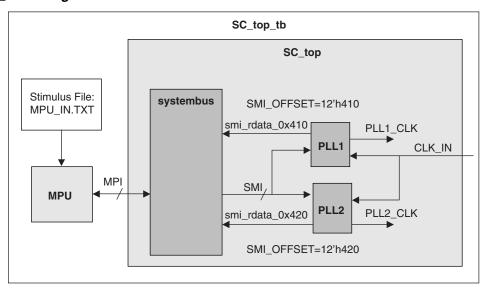

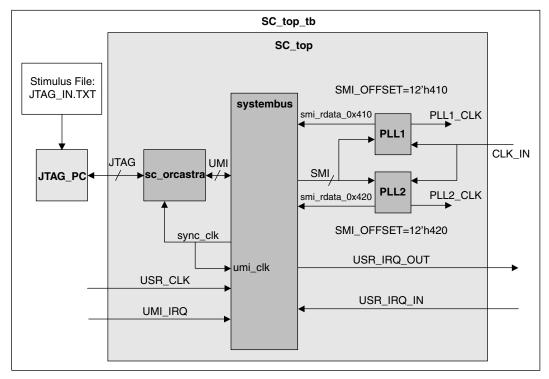

Figure 1 illustrates the existing peripherals on the system bus. The gray boxes are available only during configuration. The Status and Config box refers to internal system bus registers. Refer to TN1080, <u>LatticeSC sysCONFIGTM Usage Guide</u> for configuration options.

This document describes all the interfaces listed in Table 1 in detail to help the user utilize the desired functions of the system bus.

Figure 1. LatticeSC System Bus Interfaces

© 2010 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

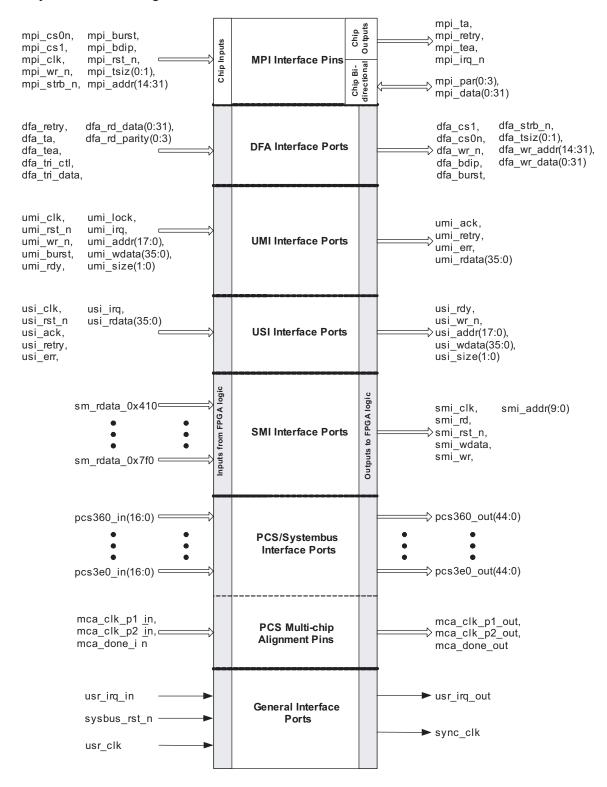

Figure 2 shows a complete system bus I/O diagram with all possible peripherals enabled in IPexpress. These interfaces and their corresponding I/Os are discussed in detail throughout the rest of this document.

Figure 2. System Bus I/O Diagram

| Definitions |                                    |

|-------------|------------------------------------|

| PCS         | Physical Coding Sublayer           |

| MACO        | Masked Array for Cost Optimization |

| MSB         | Most Significant Byte              |

| MSb         | Most Significant Bit               |

| LSB         | Least Significant Byte             |

| LSb         | Least Significant Bit              |

| MPI         | Microprocessor Interface           |

| UMI         | User Master Interface              |

| USI         | User Slave Interface               |

| SMI         | Serial Management Interface        |

| DFA         | Direct FPGA Access                 |

| EBR         | Embedded Block RAM                 |

| PLL         | Phase-Lock Loop                    |

| HDL         | Hardware Description Language      |

| DLL         | Delay Lock Loop                    |

| ASB         | Application Specific Block         |

| PPC         | PowerPC                            |

|             |                                    |

## **System Bus**

## **Multi Master Capability**

The system bus is a multiple master bus. This means that there can be more than one bus master present on the bus at the same time. A single bus arbiter controls the traffic on the bus by ensuring only one master has access to the bus at any time. This bus arbiter monitors a number of different requests to use the bus and decides which request is currently the highest priority. The configuration logic has the highest priority and overrides all normal user interfaces. By default, all master interfaces have equal priority when requesting the embedded system bus, and a fair round-robin scheme is used to rotate arbitration priority. Optionally, one can specify a priority of low=1, medium=2, or high=3 for each master interface in IPexpress. As a result, if more than one master interface is waiting for the system bus, an interface with higher priority will be granted the bus over one with a lower priority. If two requesting interfaces share the same priority, the round-robin scheme will rotate arbitration priority.

## **System Bus Address Range**

The system bus decodes 18 bits of byte addressable memory (256 Kbytes of addresses) in the device address space.

Table 2 describes the address range for the entire device address space.

Table 2. Entire System Bus Address Range

| Begin Address | End<br>Address | Size<br>(B=Bytes) | Description                                                                                                                                             |

|---------------|----------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00000       | 0x0003F        | 64 B              | System bus registers (see Table 20).                                                                                                                    |

| 0x00040       | 0x003FF        | 960 B             | Reserved.                                                                                                                                               |

| 0x00400       | 0x007FF        | 1 KB              | 64 Serial Memory Interfaces. For access to PLL/DLL configuration memory and user control/status registers in FPGA (64 SMIs, 128 bits each).             |

| 0x00800       | 0x2FFFF        | 190 KB            | User slave interface (USI) baseline. For pre-configuration usage of address range 0x10000-0x2FFFF, see TN1080, <u>LatticeSC sysCONFIG Usage Guide</u> . |

| 0x30000       | 0x364FF        | 25,856 B          | Left PCS slave interface. See the <u>LatticeSC/M Family flexiPCS Data Sheet</u> for more detail.                                                        |

| 0x36500       | 0x37FFF        | 6,912 B           | Reserved.                                                                                                                                               |

| 0x38000       | 0x3E4FF        | 25,856 B          | Right PCS slave interface. See the <u>LatticeSC/M Family flexiPCS Data Sheet</u> for more detail.                                                       |

| 0x3E500       | 0x3EEFF        | 2,560 B           | Reserved.                                                                                                                                               |

| 0x3EF00       | 0x3EFFF        | 256 B             | Inter-Quad PCS slave interface. See the <u>LatticeSC/M Family flexiPCS Data Sheet</u> for more detail.                                                  |

| 0x3F000       | 0x3FFFF        | 4 KB              | Reserved.                                                                                                                                               |

## System Bus Clock (HCLK)

The system bus is a synchronous element that has an internal clock. This clock is sometimes referred to as the HCLK. Each of the peripherals on the system is also synchronous and has an interface clock. This peripheral clock is the clock that the FPGA designer sources to the peripheral to clock data in and out of the user interface and eventually onto the system bus. The system bus itself needs to be sourced by a clock (HCLK). This main system bus clock is the clock on which all of the traffic will run through the system bus. As traffic is passed to and from each peripheral, a domain change will occur from the system bus clock domain to the peripheral domain. This domain change is handled inside the system bus. The internal system bus HCLK maximum frequency specification can be found in the LatticeSC/M Family Data Sheet.

Note that the system bus interface drives the SYNC\_CLK output port, which is synchronous to HCLK.

The system bus clock can be driven from several sources: CCLK, MPI or USER. At power-up, before the bitstream is loaded into the LatticeSC (pre-configuration) the system bus clock source is selected via the mode pins. After the bitstream has been successfully loaded into the LatticeSC, the system bus clock source is selected based on an IPexpress option.

#### CCLK

Before a bitstream is loaded and during device configuration and reconfiguration the system bus clock defaults to the configuration clock (CCLK). The CCLK is either an input or output of the LatticeSC, depending on the configuration mode pins state. The CCLK is driven internally on the system bus from the configuration logic block. There is no input or output pin associated with the CCLK on the system bus module. Using the CCLK is for configuration only and cannot be simulated.

#### MPI

If the user has selected to program the device via the MPI, then the microprocessor clock will drive the system bus during configuration. In post configuration, the MPI option is set via the bitstream (IPexpress option) and will select the clock on the MPI to drive the system bus. The MPI clock corresponds to the input MPI\_CLK on the system bus module.

#### **USER**

The USER clock allows the FPGA design to source a clock to drive the system bus clock. This USER clock is provided on the USR\_CLK input port of the system bus. Selecting the USR\_CLK as the source of HCLK is an IPexpress option.

The USER clock is driven from the FPGA design and thus can be driven by any signal in the user's design. If the USER clock is derived in any way from the output of a PLL, changing the PLL control register will not be allowed. When changing the PLL control register, the output clock from the PLL will stop for a period of time. If this clock stops, the USER clock will stop and thus the HCLK will stop. If the HCLK stops, the system bus will lock. The PLL control register will not be able to be changed and the FPGA will lock. To prevent this condition, do not drive this signal with a PLL output or do not change the PLL control register for this PLL.

#### Oscillator

The LatticeSC internal oscillator drives the CCLK during master mode bitstream configuration. To use the oscillator after configuration, set the source of the system bus clock to USER in IPexpress. Also instantiate the OSCA oscillator block in the design to drive the system bus USER clock pin. Various frequency rates can be selected for the oscillator via sysCONFIG. More information on the internal oscillator frequency rate selection can be found in TN1080, LatticeSC sysCONFIG Usage Guide. In simulation, however, the oscillator clock model driving the system bus HCLK has a fixed 100MHz frequency.

## **System Bus Interrupts**

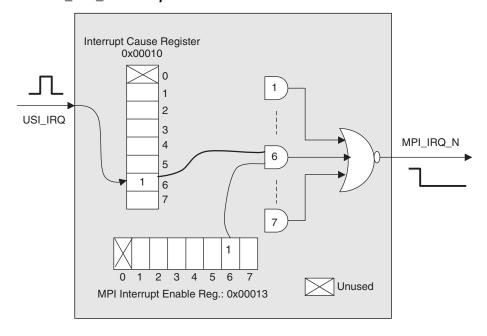

The system bus has the ability to generate and accept interrupt signals from several peripherals. These interrupts can then be used to alert either on-chip modules or external modules. An internal interrupt can be generated from the FPGA design, the configuration block during device configuration or from the PCS block. The interrupt cause register (0x00010) contains a bit for each source of an interrupt. When one of the peripherals sets an interrupt, the particular bit in the cause register will bet set to a 1. To clear the interrupt cause bit, a master interface will need to write a 1 to the particular bit to clear it. Note that clearing the interrupt cause bit does not remove the source of the interrupt.

Some peripherals on the system bus can pass interrupts found in the interrupt cause register to an interrupt output signal on their interface. For a peripheral to pass interrupts to its interrupt output signal, its corresponding interrupt enable register must be properly provisioned. There is an interrupt enable register for user (0x00012), and MPI (0x00013). When a bit is set to a 1 in the interrupt enable register, an interrupt will be passed to the corresponding interrupt output signal (active low MPI\_IRQ\_N output for MPI and active high USR\_IRQ\_OUT for user). When the interrupt output signal for the peripheral indicates an interrupt was created, a master should read the interrupt cause register to determine the source of the interrupt. Table 3 summarizes the interrupt enable register and output signal for both MPI and user.

Table 3. Interrupt Enable Registers and Outputs

| Interface | Interrupt Enable<br>Register | Interrupt Output<br>Signal | Notes                             |  |  |  |

|-----------|------------------------------|----------------------------|-----------------------------------|--|--|--|

| USER      | 0x00012                      | USR_IRQ_OUT                | Only the UMI can write to 0x00012 |  |  |  |

| MPI       | 0x00013                      | MPI_IRQ_N                  | Only the MPI can write to 0x00013 |  |  |  |

The interrupt cause register (0x00010), user interrupt enable register (0x00012) and MPI interrupt enable register (0x00013) are designed such that each bit corresponds to the same interrupt source across all three registers. Bit 1 of all three registers, for example, always corresponds to a PCS interrupt source. The correlation between bit number and interrupt source is illustrated in Table 4.

Interrupt Source/ Unused **PCS** MPI CFG\_ERR CGF\_DATA UMI\_IRQ USI IRQ USR IRQ IN Signal **Interrupt Cause** Unused Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 Bit 6 Bit 7 Register (0x00010) Unused Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 Bit 6 Bit 7 **USER Interrupt Enable Register** When any of the bits in 0x00012 is set high, a rising edge on the interrupt source/signal (as reflected in (0x00012)the corresponding interrupt cause bit in 0x00010) causes signal USR\_IRQ\_OUT to go high. Bit 3 **MPI Interrupt** Unused Bit 1 Bit 2 Bit 4 Bit 5 Bit 6 Bit 7 **Enable** When any of the bits in 0x00013 is set high, a rising edge on the interrupt source/signal (as reflected in Register (0x00013) the corresponding interrupt cause bit in 0x00010) causes MPI\_IRQ\_N to go low.

Table 4. Correlation Between Bit Number and Interrupt Source

For more information on the interrupt cause register and interrupt enable registers, refer to the system bus memory map in Table 20.

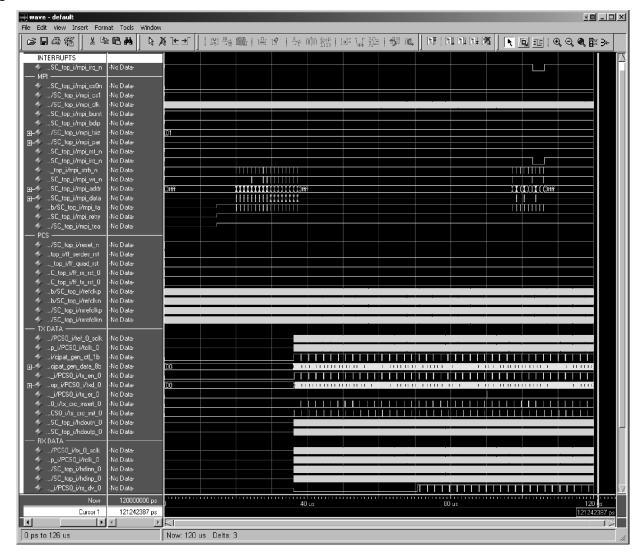

For example (as illustrated in Figure 3), to pass interrupts created by the USI interface to MPI\_IRQ\_N, the MPI must write a 1 to bit 6 of 0x00013. When the USI sends an interrupt via a USI\_IRQ pulse (larger than one USI\_CLK period), bit 6 of the interrupt cause register (0x00010) will go to a 1. This, combined with the 1 on bit 6 of 0x00013, will then drive MPI\_IRQ\_N pin low to indicate an interrupt to the microprocessor. The microprocessor should then read the interrupt cause register to determine that the interrupt came from the USI. Assuming no more interrupts are generated, the MPI can clear bit 6 of 0x00010 by writing a 1 to it. This also sets the MPI\_IRQ\_N signal back to 1.

Figure 3. USI\_IRQ to MPI\_IRQ\_N Interrupt

## **System Bus General Signals**

Table 5 describes the general interface signals on the system bus. These signals are not part of any of the specific peripherals mentioned in Table 1.

Table 5. System Bus General Interface Signals

| Signal       | Direction | Description                                  | Notes                                                                                                                           |

|--------------|-----------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| SYSBUS_RST_N | Input     | Active low system bus reset                  | Resets Internal system bus logic                                                                                                |

| USR_IRQ_IN   | Input     | Active high user interrupt                   |                                                                                                                                 |

| USR_IRQ_OUT  | Output    | Active high user output interrupt            | Signal responds to interrupt when interrupt enable register 0x00012 is set by UMI.                                              |

| USR_CLK      | Input     | USER clock                                   | This interface signal is generated only when the USER clock is selected as the system bus clock source (in ispLEVER IPexpress). |

| SYNC_CLK     | Output    | Clock synchronous to HCLK (system bus clock) |                                                                                                                                 |

### Address/Data Bus Ordering

The system bus handles bus transfers of address and data at all of its interfaces. The orientation of the address bus and the data bus may be different, depending on which peripheral is accessed. Internally on the bus, the address bus is always oriented the same way, whereas the data bus is dependent on the driving master/slave interface.

### **Address Bus Ordering**

There are 18 address bits on the system bus. These address lines can be driven by any of the master interfaces on the system bus. Except for the DFA interface, the address bus on a slave interface will always be provided to the slave with bit 0 as the LSb. For the master interfaces (MPI, UMI) the address bus is dependent on the master. The UMI will use bit 17 as the MSb and bit 0 as the LSb. The MPI will match the PowerPC address bus orientation, which is bit 0 as MSb and bit 31 as LSb, even though only bits 14 through 31 (18 bits) are available on the LatticeSC MPI interface (see Table 21). More information on this address bus and its connections is found in the MPI section of this document. Table 6 lists the address bus bit ordering of different interfaces.

Table 6. Address Bit Ordering for Different Master/Slave Interfaces

|           | Address Bus Bit Ordering<br>ADDRESS[MSb:LSb] |     |  |  |  |  |  |

|-----------|----------------------------------------------|-----|--|--|--|--|--|

| Interface | MSb                                          | LSb |  |  |  |  |  |

| MPI       | 14                                           | 31  |  |  |  |  |  |

| UMI       | 17                                           | 0   |  |  |  |  |  |

| USI       | 17                                           | 0   |  |  |  |  |  |

| DFA       | 14                                           | 31  |  |  |  |  |  |

| SMI       | 9                                            | 0   |  |  |  |  |  |

#### **Data Bus Bit Orientation**

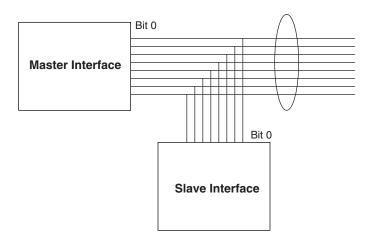

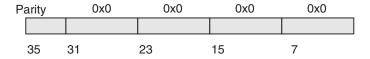

The data bus on the system bus is 36 bits wide: 32 bits for data and four bits for parity. On the system bus, the data bits are passed unchanged through the peripherals. So the orientation of the data on the system bus is dependent on the data driving master/slave interface. This means that bit 0 on the master interface will be bit 0 on the slave interface, bit 1 will be bit 1, etc. So if bit 0 is the LSb on the master interface then bit 0 will be the LSb on the slave interface as shown in Figure 4. Care must be taken when accessing an address location to make sure data bits are used properly in terms of LSb and MSb.

Figure 4. System Bus Data Bus Bit Mapping

Different data interfaces on the system bus do not all follow the same rule in terms of bus bit orientation. The value of the data bus can be interpreted with bit 0 being either the MSb or LSb. For example, for single byte accesses, the MPI interface is always oriented with bit 0 being the MSb (DATA[0:7]), whereas the UMI interface is oriented with bit 0 being the LSb (DATA[7:0]). Table 7 shows the data bus bit orientation for all user accessible interfaces, in addition to the MPI.

Table 7. Data Bus Bit Orientation for Different System Bus Interfaces

| Data Bus Bit Ordering DATA[MSb:LSb] |                    |                |      |      |        |    |  |  |  |  |

|-------------------------------------|--------------------|----------------|------|------|--------|----|--|--|--|--|

|                                     | 8-                 | Bit            | 16-  | Bit  | 32-Bit |    |  |  |  |  |

| Interface                           | ce MSb LSb MSb LSb |                |      | MSb  | LSb    |    |  |  |  |  |

| MPI                                 | 0                  | 7              | 0 15 |      | 0      | 31 |  |  |  |  |

| UMI                                 | 7                  | 0              | 15   | 15 0 |        | 0  |  |  |  |  |

| USI                                 |                    | Follows Master |      |      |        |    |  |  |  |  |

| DFA                                 | 0                  | 7              | 0    | 15   | 0      | 31 |  |  |  |  |

#### **Internal Data Bus**

The internal data bus is labeled D(35:0). Bits D(31:0) are used to carry the data between peripherals. Bits D(35:32) are used to carry parity to the peripherals. Except for MPI, parity is not checked internally by any of the peripherals on the system bus. Checking parity on the MPI is enabled via bit 5 of system bus address 0x0000A (MPI\_PAR\_CHK), and only checks the MPI parity on a write operation. An MPI parity error on a write always results in an MPI interrupt to the system bus interrupt cause register (0x00010, bit 2). Even or odd parity is set in isp-LEVER IPexpress. Internal system bus registers will generate parity for read operations. UMI/USI parity is only passed through the system bus and its interfaces. Parity is mapped to byte lanes as shown in Table 8. The orientation of the data bus D(31:0) depends on the master interface driving the data bus, but the parity bits are always stored on D(35:32).

Table 8. Internal Data Bus Bit Mapping

| Internal Data<br>Bus | MPI                                                            | User Master<br>Interface | Description                                                                                           |

|----------------------|----------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------|

| D(35)                | MPI_PAR(3)                                                     | UMI_W/R_DATA(35)         | Parity bit for D(31:24)                                                                               |

| D(34)                | MPI_PAR(2)                                                     | UMI_W/R_DATA(34)         | Parity bit for D(23:16)                                                                               |

| D(33)                | MPI_PAR (1)                                                    | UMI_W/R_DATA(33)         | Parity bit for D(15:8)                                                                                |

| D(32)                | MPI_PAR(0)                                                     | UMI_W/R_DATA(32)         | Parity bit for D(7:0)                                                                                 |

| D(31:24)             | MPI_DATA(31:24)<br>32-bit LSB<br>bit 31 = LSb                  | UMI_W/R_DATA(31:24)      | Data byte 31:24 - LSB of the MPI in 32-bit mode.                                                      |

| D(23:16)             | MPI_DATA(23:16)<br>bit 23 = LSb                                | UMI_W/R_DATA(23:16)      | Data byte 23:16                                                                                       |

| D(15:8)              | MPI_DATA(15:8)<br>16-bit LSB,<br>bit 15 = LSb                  | UMI_W/R_DATA(15:8)       | Data byte 15:8 - LSB of the MPI in 16-bit mode                                                        |

| D(7:0)               | MPI_DATA(7:0)<br>MSb=0<br>8-bit LSb=7<br>16-bit/32-bit 0:7=MSB | UMI_W/R_DATA(7:0)        | Data byte 7:0 - MSB of the MPI in 16/32-bit mode. In MPI 8-bit mode bit 0 is MSb and bit 7 is the LSb |

#### 32-bit Data Bus

When a master interface is configured for 32-bit operation, all 32 bits (D(31:0)) are used to carry the data. If the master interface is using parity, then the four parity bits will be carried on D(35:32) using the parity byte mapping previously described. Again, the orientation (MSb,LSb) of the data bus depends on which master/slave interface drives data onto the system bus. When using a 32-bit data bus the address resolution will be limited to 32-bit boundaries. Data will be carried on the bus such that the lowest address maps to byte lane D(7:0) and the highest address maps to byte D(31:24).

For example, a 32-bit read at address 0x00000 will read addresses 0x00000 - 0x00003. Address 0x00000 data will be on D(7:0), address 0x00001 data will be on D(15:8), address 0x00002 data will be on D(23:16), and address 0x00003 data will be on D(31:24) as shown in Figure 5.

Figure 5. 32-bit Data Bus

| P | arity | 0x3 | 0x2 | 0x1 | 0x0 |

|---|-------|-----|-----|-----|-----|

|   |       |     |     |     |     |

|   | 35    | 31  | 23  | 15  | 7   |

## 16-bit Data Bus

For 16-bit operation of a master interface, the data will be carried on D(15:0). The slave interface will only need to read data from D(15:0). The MSB and LSB of the data will be determined by how the data was driven onto the bus by the master/slave interface. When using a 16-bit data bus the address resolution will be limited to 16-bit boundaries. Data will be carried on the bus such that the lowest address maps to byte lane D(7:0) and the highest address maps to byte D(15:8). When using MPI, the same data will also be automatically replicated on D(31:16). When using UMI/USI, the user needs to replicate the data to the system bus on D(31:16).

For example a 16-bit read at address 0x00000 will read addresses 0x00000 - 0x00001. Address 0x00000 data will be on D(7:0) and address 0x00001 data will be on D(15:8) as shown in Figure 6.

Figure 6. 16-bit Data Bus

| Р | arity | 0x1 | 0x0 | 0x1 | 0x0 |

|---|-------|-----|-----|-----|-----|

|   |       |     |     |     |     |

|   | 35    | 31  | 23  | 15  | 7   |

Note that a 16-bit data access (from MPI or UMI) to the PCS slave registers is not supported. Please refer to the PCS section of this document for more information.

#### 8-bit Data Bus

For 8-bit operation of a master interface the data will be carried on D(7:0). The slave interface will only need to read and write data on D(7:0). When using MPI, the same data will also be automatically replicated on D(15:8), D(23:16), and D(31:24). When using UMI/USI, the user needs to replicate the data to the system bus on D(15:8), D(23:16), and D(31:24), as shown in Figure 7. The MSb and LSb of the data will be determined by the master/slave interface.

Figure 7. 8-Bit Data Bus

## Synchronous/Asynchronous Mode

The MPI, UMI and USI interfaces on the system bus can be generated (in ispLEVER IPexpress) either synchronously or asynchronously to the system bus HCLK domain.

By default, all three interfaces are generated asynchronously to the system bus HCLK domain. Asynchronous mode is required when the clock clocking the peripheral interface is assumed to run asynchronously (different frequency/phase) to HCLK. In this case, all three peripherals (MPI, UMI, USI) include an asynchronous FIFO to decouple the peripheral clock domain from the internal HCLK domain. This FIFO introduces extra cycles of delay during a read or a write access through the system bus.

In ispLEVER IPexpress, it is possible to independently bypass the MPI, UMI and USI asynchronous FIFOs. This mode, referred to as synchronous mode, reduces the amount of access latency as a result of bypassing the FIFO. For MPI, this mode only requires selecting the MPI clock as the source of the system bus clock. For UMI and USI, a specific ispLEVER IPexpress option to make the peripheral synchronous to the system bus clock needs to be selected. UMI and USI modes also require that the peripheral clock (UMI\_CLK or USI\_CLK) be driven by SYNC\_CLK in synchronous mode. Table 9 describes how to ensure that each of MPI, UMI or USI interface clocks is made synchronous to HCLK.

Table 9. Setting Synchronous clocks to HCLK

| Interface | Interface Clock | How to Make Synchronous to HCLK                                                             |

|-----------|-----------------|---------------------------------------------------------------------------------------------|

| MPI       | MPI_CLK         | Select MPI_CLK as source of system bus clock in ispLEVER IPexpress.                         |

| UMI       | 1               | Make UMI synchronous to system bus in ispLEVER IPexpress. Connect SYNC_CLK to UMI_CLK port. |

| USI       | USI_CLK         | Connect SYNC_CLK to USI_CLK port.                                                           |

## **System Bus Time Out**

Time out is a programmable feature that allows the system bus to interrupt current operation on the bus. There are two types of time out mechanisms that the system bus can exercise: Wait State time out, and Grant time out. In each case, an index is used to specify the length of time in HCLK cycles after which the system bus times out. Table 10 shows how an index relates to HCLK cycles. For example, if the index is at 5 and HCLK is running at 50 MHz, the system bus will timeout after  $2^{10} * 20$  ns  $\sim= 20$  microseconds. Note that a 0 index value means the system bus never times out.

Table 10. Time Out Index vs. HCLK Cycles Before Time Out

| Index          | 0                    | 1              | 2              | 3              | 4              | 5               | 6               | 7               | 8               | 9               | 10              | 11              | 12              | 13              | 14              | 15              |

|----------------|----------------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| HCLK<br>Cycles | Never<br>Time<br>Out | 2 <sup>2</sup> | 2 <sup>4</sup> | 2 <sup>6</sup> | 2 <sup>8</sup> | 2 <sup>10</sup> | 2 <sup>12</sup> | 2 <sup>14</sup> | 2 <sup>16</sup> | 2 <sup>18</sup> | 2 <sup>20</sup> | 2 <sup>22</sup> | 2 <sup>24</sup> | 2 <sup>26</sup> | 2 <sup>28</sup> | 2 <sup>31</sup> |

#### **Wait State Time Out**

This type of time out is designed to prevent the master on the bus from waiting indefinitely for the termination phase of an access (MPI\_TA or UMI\_ACK). Without a time out mechanism, the system bus could hang indefinitely. The Wait State time out index is independently set in both simulation and bitstream generation. Setting a value greater than 0 is recommended to avoid unintentional hanging of the system bus.

In simulation, the index is defined as a programmable parameter (WS\_TIME\_INDEX). The default value for WS\_TIME\_INDEX is 4 (256 cycles). The value of the parameter can be modified in the HDL code for simulation purpose. In Verilog, for example, assuming the system bus instance is "systembus\_i", the index can be set to 5 as follows:

defparam systembus\_i.SYSBUSA\_INST.SYSBUSA\_sim\_inst.WS\_TIME\_INDEX = 4'd5;

During bitstream generation, the index is defined as a sysCONFIG switch (WaitStateTimeOut). The default value of WaitStateTimeOut is 5 (2<sup>10</sup> HCLK cycles). Please see TN1080, <u>LatticeSC sysCONFIG Usage Guide</u> for more information.

When the system bus times out as a result of a Wait State condition, the system bus asserts a transfer error (MPI TEA or UMI ERR) along with the termination of access signal (MPI TA or UMI ACK).

#### **Grant Time Out**

This type of time out is designed to prevent one master from indefinitely owning the system bus when another master is also trying to access it. The Grant time out can only be used when the master currently accessing the system bus has not locked it.

In simulation, the index is defined as a programmable parameter (GRANT\_TIME\_INDEX). The default value for GRANT\_TIME\_INDEX is 0 (never time out). The value of the parameter can be modified in the HDL code for simulation purpose. In Verilog, for example, assuming the system bus instance is "systembus\_i", the index can be set to 5 as follows:

defparam systembus i.SYSBUSA INST.SYSBUSA sim inst.GRANT TIME INDEX = 4'd5;

During bitstream generation, the index is defined as a sysCONFIG switch (GrantTimeOut). The default value of GrantTimeOut is 0 (never time out). Please see TN1080, <u>LatticeSC sysCONFIG Usage Guide</u> for more information.

When the system bus times out as a result of a Grant condition, the system bus first waits for the current transfer to end, then grants ownership of the bus to the other master.

## **System Bus Peripherals**

The following section discusses each of the peripherals on the system bus in detail. Some of the peripherals on the system bus (e.g. Configuration) do not have FPGA design user ports and are fully contained inside the system bus. These peripherals' registers are described in the memory map and do not have any user inputs or outputs on the system bus.

#### MPI

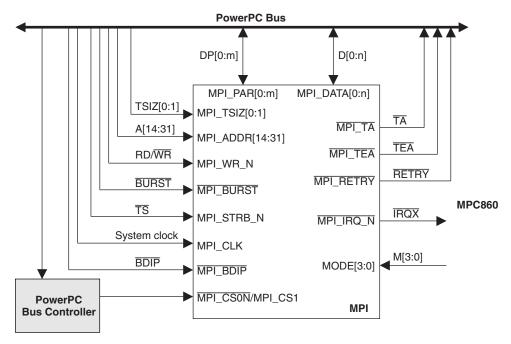

LatticeSC devices contain an embedded microprocessor interface (MPI) that can be used to interface any LatticeSC device to any MPC860/MPC8260 PowerPC microprocessor or compatible interface through the PowerPC peripheral bus. The MPI acts as a bridge between an external PowerPC processor and the embedded system bus.

Externally, the MPI acts as a slave peripheral interface through which a PowerPC can access the embedded features of the device. Internally the MPI acts as a master peripheral interface on the system bus to initiate data transfers as directed by the external processor.

Note: The MPI interface is not available on all LatticeSC packages. Also, some LatticeSC die/package combinations restrict the maximum allowable MPI DATA bus size. For full information on MPI restrictions for a die/package combination, please refer to the Pinout Information section of the <u>LatticeSC/M Family Data Sheet</u>.

The MPI is one element on the embedded system bus illustrated in Figure 1. The system bus provides multi-master/multi-slave communication between the MPI and the status and configuration interface, SMI, UMI, USI, and one or more PCS interface blocks as needed in each specific LatticeSC device.

The MPI is available prior to and optionally after configuration of the programmable logic in the LatticeSC. The MPI can be used prior to device configuration to identify, test, initialize, and download configuration data into the device. After configuration of the programmable logic, the MPI can be used to read back the configuration and internal status data, control parameters in the PLLs and the DLLs, access status and control registers for an embedded PCS block (if present), and interact with the user's design configured in programmable logic.

The MPI peripheral has two distinguishing characteristics from any other system bus interface:

- The MPI can be turned on at power-up, before device configuration, allowing the MPI to access the system bus control, status and configuration registers. All other peripherals can be present only after device configuration.

- When the user instantiates an system bus with MPI in a design, a register bit setting can keep MPI enabled even after the device is un-programmed.

#### **MPI Interface**

Table 11 shows the MPI signals used by the PowerPC to perform transactions with the LatticeSC device. The MPI is a fixed block on the LatticeSC array and the interface signals are mapped to dedicated pins on the LatticeSC device. PowerPC pins to LatticeSC pins mapping can be found in Appendix A.

Externally the MPI implements a 36-bit PowerPC bus slave, which internally drives the system bus as a master. Data bus width is selectable among 8 bits, 16 bits, and 32 bits with parity of 1, 2 or 4 bits, respectively (one parity bit for each active byte). Note that the MPI does not generate parity, but simply passes it from the PowerPC bus to the system bus and vice versa. The MPI interface can check parity on write, however, by setting bit 5 of system bus address 0x0000A (MPI\_PAR\_CHK), Any write parity error results in an MPI interrupt to the system bus interrupt cause register (0x00010, bit 2).

Table 11. MPI Signals to PowerPC Bus

| Name          | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPI_RST_N     | I   | Resets the MPI interface on the system bus                                                                                                                                                                                                                                                                                                                                                                                              |

| MPI_CLK       | ı   | This is the clock from the PowerPC. This clock input will clock the MPI. This clock may optionally clock the main system bus clock if selected. The MPI clock can be driven up to 66MHz operation.                                                                                                                                                                                                                                      |

| MPI_TSIZ[0:1] | I   | Transfer size ([0:1]: 00-double word, 10-word, 01-byte) The MPI_TSIZ pins connect directly up to the PowerPC TSIZ1 and TSIZ0. These pins select the size of the PowerPC data transaction. This is the transfer size of the data transaction from the microprocessor's perspective. This is different from the MODE pin selected size discussed later.                                                                                   |

| MPI_WR_N      | I   | Transfer type (0-write, 1-read) This signal indicates to the MPI whether the transaction initiated by the microprocessor is a read or a write. If the transaction is a read, data will be provided to the microprocessor from the address specified. If the transaction is a write, data will be written to the address specified by the microprocessor inside the LatticeSC device. This signal connects to the PowerPC RD//WR signal. |

| MPI_BURST     | I   | Indicates that a burst transfer is in progress when low. This signal informs the MPI that the PowerPC is performing a burst transaction using the PowerPC burst pin.                                                                                                                                                                                                                                                                    |

| MPI_BDIP      | I   | Burst Data In Progress. This signal from the PowerPC will go low on the first clock of data during a burst and go high on the last clock of data of the burst transfer.                                                                                                                                                                                                                                                                 |

Table 11. MPI Signals to PowerPC Bus

| Name              | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MPI_STRB_N        | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | This active low signal indicates the start of a transactions or the strobe. This pin is connected to the TS pin of the PowerPC.                                                                                                                                                                                                                                                      |  |  |

| MPI_CS0N/ MPI_CS1 | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Chip selects for active high (MPI_CS1) and active low (MPI_CS0N). Both of these chip selects must be active for the LatticeSC system bus logic to be selected. Typically CS1 is connected to logic 1 and CS0n is connected to a PowerPC CS pin. When selecting the DFA interface instead of the system bus, the values of these signals are inverted (MPI_CS1=0, MPI_CS0N=1).        |  |  |

| MPI_ADDR[14:31]   | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | The PowerPC address bus is 32 bits wide. The LatticeSC devices only support 18 bits of address space. The LatticeSC uses the least significant bits of the PowerPC address space using address bits 14:31.                                                                                                                                                                           |  |  |

| MPI_DATA[0:31]    | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | The PowerPC data bus can be up to 32 bits wide. Bit 0 is the MSb and bit 31 is the LSb. For multi-byte transfers, the most significant byte ([0:7]) has the lowest address. The PowerPC data pins D[0:31] connect directly to the LatticeSC pins MPI_DATA(0:31). Data pins not used by virtue of selecting 8-bit or 16-bit data widths are available as general-purpose user I/O.    |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Note: The MPI interface is not available on all LatticeSC packages. Also, some LatticeSC die/package combinations restrict the maximum allowable MPI DATA bus size. For full information on MPI restrictions for a die/package combination, please refer to the Pinout Information section of the <a href="LatticeSC/M Family Data Sheet"><u>LatticeSC/M Family Data Sheet</u></a> . |  |  |

| MPI_PAR[0:3]      | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Parity can be up to 4 bits wide (one bit per byte of data) depending on the data bus size. Parity connects directly to the PowerPC DP[0:3] pins. Parity pins not used by virtue of selecting 8-bit or 16-bit data widths are available as general-purpose user I/O.                                                                                                                  |  |  |

| MPI_TA            | This active low signal indicates the transfer acknowledge from the pin is connected to the TA pin of the PowerPC. For a single MPI will come back on the next clock. See the Consecutive Will of this document. For an MPI read transaction the MPI_TA will consider a slave responds. The difference in time it takes to complete a translave that is accessed. Other dependencies are the clock rate of clock rate of the slave interface, and slave acknowledge protocol. |                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| MPI_TEA           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | This active low signal indicates a transfer error acknowledge during the current transaction. More information on cause of this error can be found under the MPI Exceptions section of this document.                                                                                                                                                                                |  |  |

| MPI_IRQ_N         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Active-low interrupt request from the LatticeSC device. See the System Bus Interrupts section of this document.                                                                                                                                                                                                                                                                      |  |  |

| MPI_RETRY         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Active-low request for processor to relinquish the bus and retry the cycle. Exception signal indicating the LatticeSC device is not ready to accept the requested transaction. More information on the cause of this error can be found under MPI exceptions.                                                                                                                        |  |  |

| MODE[3:0]         | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MPI data width ([3:0]: 1010, 1011, 1110 = 8, 16, 32 bits, respectively) The MODE pinsused to select the type of bitstream configuration the LatticeSC device will utilize. More information on the MODE pins can be found in the Enabling the MPI section of this doment. These pins do not appear on the system bus HDL model out of ispLEVER IPer press.                           |  |  |

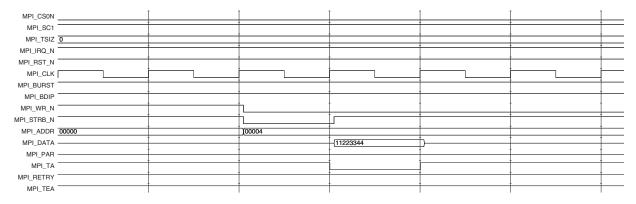

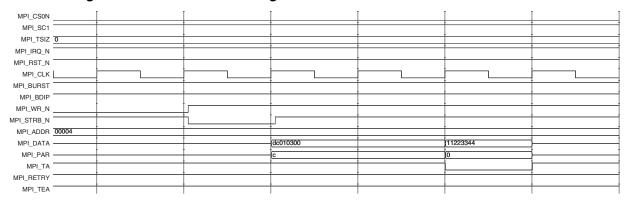

## **MPI Single Beat Data Transfers**

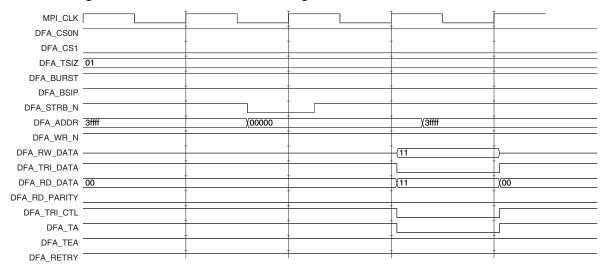

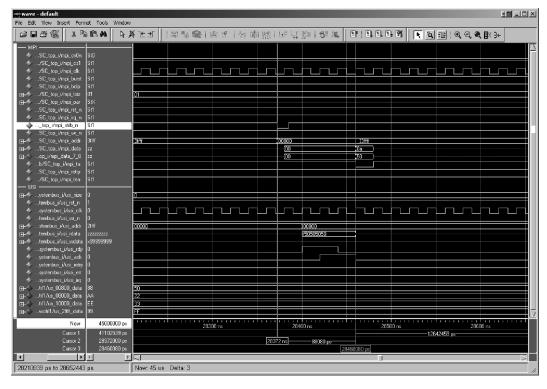

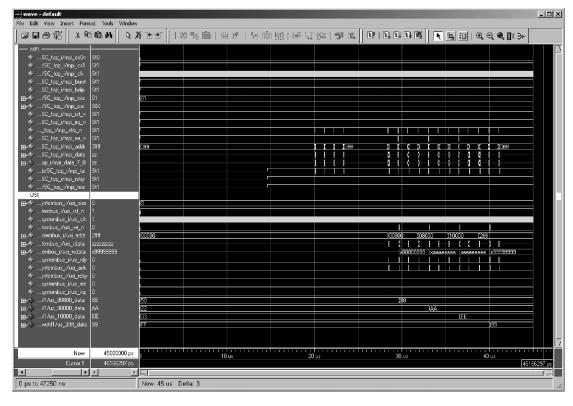

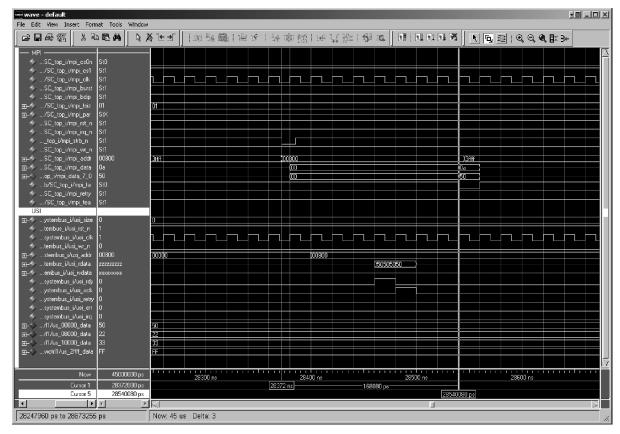

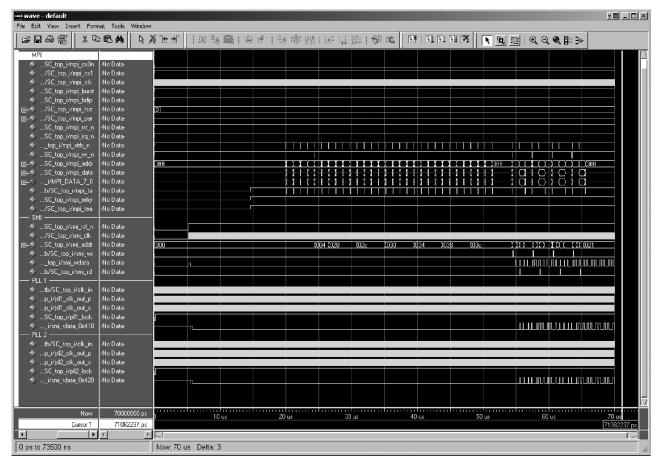

Any data transfer on the PowerPC bus has four phases: arbitration, address, data and termination. During the arbitration phase the processor initiates the transaction with a MPI\_STRB\_N pulse. The MPI samples the address and control inputs during the address phase, receives or provides data and asserts transfer acknowledge during the data phase, and de-assert signals during the termination phase. Figure 8 shows the PowerPC bus timing for a 32-bit wide data single beat MPI write transfer. Figure 9 shows the PowerPC bus timing for a 32-bit wide data single beat MPI read transfer. MPI\_DATA [0:31]=0x11223344 is written/read to/from address 0x00004 in each case.

Figure 8. MPI Single Write Data Transfer Timing

Figure 9. MPI Single Read Data Transfer Timing

#### **MPI Burst Transfers**

The MPI will support burst transfers of exactly 4 beats (32-bit width), 8 beats (16-bit width) or 16 beats (8-bit width), depending upon the selected data bus width. Burst transfers can be of any size that is compatible with the selected data bus width given the limitation that the MPI will handle 4, 8, or 16 beats as indicated.

The burst mechanism uses MPI\_BURST to indicate that the transfer is a burst transfer and MPI\_BDIP to indicate the duration of the burst.

Along with the address and transfer control signals, the PowerPC asserts MPI\_BURST during the address phase of the transfer. In the data phase, the microprocessor asserts MPI\_BDIP until the next to the last word is sent/received. The MPI continues to send/receive data until it detects MPI\_BDIP de-asserted at the rising edge of MPI\_CLK while MPI\_TA is asserted.

Figure 10 shows the signal timing for a 32-bit wide data 4-beat burst write:

- The first write access is to 0x08000-0x08003 (MPI\_DATA [0:31]=0x111111111).

- The second write access is to 0x08004-0x08007 (MPI\_DATA [0:31]=0x22222222).

- The third write access is to 0x08008-0x0800B (MPI\_DATA [0:31]=0x33333333).

- The fourth write access is to 0x0800C-0x0800F (MPI\_DATA [0:31]=0x44444444).

MPI CS0N MPI\_SC1 MPI TSIZ C MPI IRQ N MPI RST N MPI\_CLK MPI\_BURST MPI\_BDIP MPI\_WR\_N MPI STRB N MPI\_ADDR 08000 <del>(11111111</del> 122222222 V33333333 MPI DATA MPI PAR MPI\_TA MPI\_RETRY MPI TEA

Figure 10. MPI Burst Write Transfer Timing

Figure 11 shows the signal timing for a 32-bit wide data 4-beat burst read:

- The first read access is to 0x00030-0x00033 (MPI\_DATA [0:31]=0x0C8C4CCC).

- The second read access is to 0x00034-0x00037 (MPI\_DATA [0:31]=0x2CAC6CEC).

- The third read access is to 0x00038-0x0003B (MPI\_DATA [0:31]=0x1C9C5CDC).

- The fourth read access is to 0x0003C-0x0003F (MPI\_DATA [0:31]=0x3CBC7CFC).

MPI CS0N MPI\_SC1 MPI\_TSIZ 0 MPI IRQ N MPI RST N MPI\_CLK MPI\_BURST MPI\_BDIP MPI WR N MPI\_STRB\_N MPI ADDR 00004 100030 11223344 0c8c4ccc 2cac6cec 1c9c5cdc 3cbc7cfc MPI\_DATA MPI PAR MPI\_TA MPI RETRY MPI\_TEA

Figure 11. MPI Burst Read Transfer Timing

## **Consecutive Writes with the MPI**

The MPI uses a single write post buffer implementation. This means that on each MPI write, the MPI\_TA comes back on the next clock cycle to terminate the PowerPC transaction. Internally on the MPI and system bus, the data is not yet transmitted to the target. It will take several HCLK clock cycles before the target receives the data and terminates the transaction. Until this termination takes place any additional writes from the MPI will issue a retry (MPI\_RETRY).

During consecutive write cycles, the number of PowerPC clock cycles (MPI\_CLK) it takes until the next write can take place without a retry is variable. The variables include the source of the HCLK, whether the MPI interface is in synchronous or asynchronous mode, the target being accessed, and the target's termination protocol and clock. The user should add appropriate delay based on their board and system behavior.

### **MPI Exceptions**

Three signals, MPI\_TEA, MPI\_RETRY and MPI\_TA are monitored during the termination phase of a transfer. A normal termination is indicated when MPI\_TA is asserted and both MPI\_TEA and MPI\_RETRY are de-asserted. If either MPI\_TEA or MPI\_RETRY are asserted, an MPI bus exception is indicated.

MPI\_TEA is asserted for one MPI\_CLK cycle to indicate either an internal system bus error, or a transfer with MPI\_TSIZ larger than the data bus size, or physical data size selected by the MODE[3:0] inputs.

MPI\_RETRY is asserted for one MPI\_CLK cycle when the MPI is busy to request that the PowerPC relinquish the bus and reissue the current transfer. A retry is issued when the following occurs:

- · The MPI gets a read transaction while its write FIFOs are not empty.

- · The MPI gets a write transfer while its write FIFOs are full.

- The MPI receives a retry indication from the embedded system bus during a read transfer.

For burst transfers, the MPI should issue retry before acknowledging the first data phase; if MPI\_RETRY is asserted after the first data phase of a burst transfer, it should be treated as a transfer error (MPI\_TEA).

## **MPI Interrupts**

The MPI logic on the system bus can generate an MPI interrupt to the system bus as a response to certain MPI write accesses. When an MPI interrupt occurs, it sets the MPI\_IRQ bit of the Interrupt Cause Register (bit 2 of 0x00010). The interrupt can then be passed to either the MPI or USER output interrupt (as discussed in the system bus Interrupts section of this document).

There are three possible causes for an MPI interrupt during an MPI write access:

- The MPI logic on the system bus times out as a result of too many system bus slave RETRY responses.

- The system bus slave generates an internal error response to the access.

- The MPI logic on the system bus detects a parity check error (when MPI write parity checking is enabled).

### MPI Synchronous vs. Asynchronous MPI Mode Latency

Table 12 shows the best case MPI to system bus access latency for both synchronous and asynchronous modes. The latency is defined as the number of cycles the MPI\_TA signal stays high after MPI\_STRBN goes low.

Table 12. MPI Sync/Asynchronous Best Case Latency<sup>1</sup>

| Ī | Synchron     | ous Mode | Asynchronous Mode |              |               |              |              |

|---|--------------|----------|-------------------|--------------|---------------|--------------|--------------|

| ĺ | Single Burst |          | Single Read       | Single Write | 16-Beat Burst | 8-Beat Burst | 4-Beat Burst |

| ĺ | 2            | 3        | 7                 | 6            | 7             | 7            | 7            |

<sup>1.</sup> Note that the first access in a series of MPI write cycles has zero latency. Subsequent write cycles may cause retries. When retries are present, the write latency is then the earliest cycle without a retry from the original MPI\_STRB\_N low.

## **Enabling the MPI**

There are three conditions under which the MPI interface can be enabled: at power-up, via a register bit setting, and via user instantiation. If the MPI is not utilized at all in the LatticeSC design, the dedicated MPI pins can be used as general I/O pins for the user's design.

MPI at Power-up: To enable the MPI at power-up, prior to device configuration, the external MODE pins (see Table 13) must be set to specify one of the three MPI configuration modes, as specified in TN1080, <u>LatticeSC sys-CONFIG Usage Guide</u>. If the MPI is not used, all of the MPI pins (MPI\_TA, MPI\_DATA, etc.) are tri-stated to a pull-up resistance during configuration. In any of the three MPI configuration modes, the MPI can access the registers in the system bus, PCS left, PCS right, and PCS inter-quad address ranges shown in Table 2.

Table 13. LatticeSC MPI Device Configuration Modes

| М3 | M2 | M1 | MO | Description   |

|----|----|----|----|---------------|

| 1  | 0  | 1  | 0  | MPC860 8-bit  |

| 1  | 0  | 1  | 1  | MPC860 16-bit |

| 1  | 1  | 1  | 0  | MPC860 32-bit |

Data bus width is determined at power-up by the value presented on the MODE pins during the low-to-high transition of the INIT signal. The MODE pins select the data size of the transaction including the parity bits. MPC860 8-

bit mode will also use MPI\_PAR(0) along with the data. MPC860 16-bit will use MPI\_PAR(0:1) and MPC860 32-bit will use MPI\_PAR(0:4). Unused MPI\_PAR bits will be 3-stated to a pull-up resistance during configuration. All of the other MPI signals connect directly to the PowerPC bus. Pad locations vary depending upon device type, size, and package.

The data bus width selected by the MODE[3:0] pins is not related to the transfer size specified by MPI\_TSIZ[0:1]. The bus width selected by the MODE[3:0] pins determines how many data pins are used by the MPI, while the transfer size is determined by the master interface on the PowerPC bus. The transfer size used by an external master must not exceed the selected data bus width; otherwise, the higher-order data bits will be lost and a bus exception is issued by the MPI.

In order to configure the LatticeSC device at power-up via MPI, the MPI PowerPC interface requires two different file types:

- The first file is a PowerPC PROM image for device configuration. ispVM<sup>®</sup> converts a sysCONFIG-generated bitstream to a PROM image.

- The second file is a configuration-time initialization file generated by sysCONFIG. This file contains initialization values for EBRs, PCS auto-configuration, and SMI memories. This initialization file is not needed for device configuration modes other than MPI.

More information on MPI configuration of the LatticeSC devices can be found in TN1080, <u>LatticeSC sysCONFIG</u> Usage Guide.

**MPI via User Instantiation:** To enable the MPI for use after device configuration and during normal operation, the user must instantiate the system bus with an MPI peripheral in the LatticeSC design. The system bus element along with the MPI and other peripherals is created using ispLEVER IPexpress.

**MPI via a Register Bit Setting:** When the user enables the MPI, as described in the MPI via User Instantiation section of this document, setting the MPI\_USR\_ENABLE bit (control register 0x00008, bit 2) will keep the MPI mode enabled even after the device is un-programmed. Un-programming the device still sets the programming mode to MPI (as defined by the user), independently of what the MODE pins are set to.

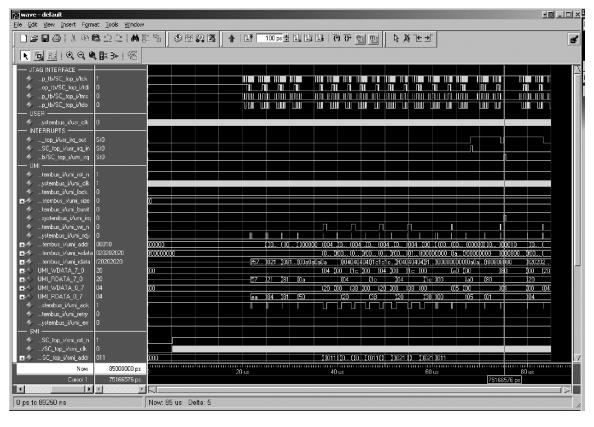

## **User Master Interface (UMI)**

The User Master Interface (UMI) allows the FPGA design to perform transactions on the system bus. Through the UMI, the FPGA design has access to any and all of the slave peripherals on the system bus. Signals for the UMI are listed in Table 14.

Table 14. UMI Interface Signals

| Signal          | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UMI_CLK         | I    | The main clock for the user master interface. This clock only clocks the interface registers. A domain change is made from the UMI_CLK domain to the system bus clock domain in asynchronous mode. The user master interface and the system bus can be made synchronous through an ispLEVER IPexpress option (synchronous mode). A frequency preference on this signal will constrain all of the inputs and outputs of the UMI.                                                        |

| UMI_RST_N       | I    | This active-low reset resets all of the controls in the user master interface. This should be pulsed once before any transactions can occur on the UMI. This is typically connected to the same reset as the GSR and pulsed at power up.                                                                                                                                                                                                                                               |

| UMI_WDATA[35:0] | I    | 36-bit write data bus to system bus. This data bus is oriented with bits 35:32 used for parity while bits 31:0 are used for data. Parity is not calculated by any of the peripherals on the system bus, it is only carried. For less than 32-bit writes, the data must be replicated on the UMI_WDATA bus to fill the entire 32 bits. For a 16-bit transaction, bits 15:0 must be replicated on 31:16. For an 8-bit transaction, bits 7:0 must be replicated on 31:24, 23:16 and 15:8. |

| UMI_RDATA[35:0] | 0    | 36-bit read data bus from system bus. This data bus is oriented with bits 35:32 used for parity while bits 31:0 are used for data. Parity is not calculated by any of the peripherals on the system bus, it is only carried.                                                                                                                                                                                                                                                           |

Table 14. UMI Interface Signals (Continued)

| Signal         | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| UMI_ADDR[17:0] | I    | This 18-bit address bus is used to select the address that a user master transaction wil target. Bit 17 of the UMI_ADDR bus is the MSb while bit 0 is the LSb.                                                                                                                                                                                                                                 |  |  |

| UMI_WR_N       | ı    | This bit indicates whether the current transaction is a read or a write cycle. A low value indicates the current transaction is a read. Data is expected on the UMI_RDATA bus. A high value indicates the current transaction is a write. Data is driven onto UMI_WDATA bus.                                                                                                                   |  |  |

| UMI_LOCK       | I    | This active-high signal will be used to request ownership of the system bus.                                                                                                                                                                                                                                                                                                                   |  |  |

| UMI_BURST      | I    | Indicates this operation is a burst transfer.                                                                                                                                                                                                                                                                                                                                                  |  |  |

| UMI_SIZE[1:0]  | I    | Data width for transfer ([1:0]: 10-double word, 01-word, 00-byte, 11-invalid). Selects the size of the data transfer being done on the UMI. For 32-bit transactions all bits 31:0 will carry valid data. For 16-bit transactions only bits 15:0 will carry valid data. For 8-bit transactions only bits 7:0 will carry valid data.                                                             |  |  |

| UMI_RDY        | I    | Data strobe indicates address and data ready. Should be driven high when valid address is provided for read and valid address and data is present for write.                                                                                                                                                                                                                                   |  |  |

| UMI_ACK        | 0    | Acknowledge from master interface to indicate that it is ready for another operation.                                                                                                                                                                                                                                                                                                          |  |  |

| UMI_RETRY      | 0    | Asserted for one UMI_CLK cycle when the UMI is busy to request that the master relinquish the bus and reissue the current transfer. A retry is issued when the following occurs:  • The UMI gets a read transaction while its write FIFOs are not empty.  • The UMI gets a write transfer while its write FIFOs are full.  • The UMI receives a retry indication from the embedded system bus. |  |  |

| UMI_ERR        | 0    | Bus error response is asserted for one clock cycle when UMI_RDY is asserted. Indicates an internal system bus error.                                                                                                                                                                                                                                                                           |  |  |

| UMI_IRQ        | I    | User logic master interface interrupt request. Active-high signal to indicate an interrupt to the system bus. This signal will map to the interrupt cause register UMI bit.                                                                                                                                                                                                                    |  |  |

## Locking the UMI

The system bus is a multi master bus and the UMI\_LOCK signal will request ownership of the bus. In a multi master system bus application the UMI must be locked to guarantee uninterrupted multiple transactions through the UMI. Ownership of the bus is granted based on the priority of the master interface. If two masters request the bus at the same time, the interface with higher priority will obtain the bus. Once the UMI has locked the bus, the UMI\_ACK will stay high indicating the interface is ready for a transaction.

To release the lock on the system bus, a UMI\_RDY pulse must be given after UMI\_LOCK is driven low. The UMI\_RDY pulse will allow the system bus to sample UMI\_LOCK and release the bus lock.

For a single UMI transaction, or non-continuous transactions where ownership of the bus is not required, UMI\_LOCK is not necessary.

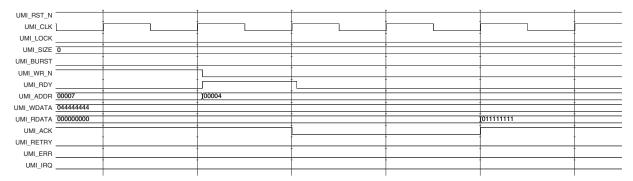

## **UMI Single Access**

A typical 8-bit wide data, single access write transaction is shown in Figure 12. UMI\_WDATA [7:0]=0x11 is written to 0x00004. For this description the UMI\_LOCK signal is not used to lock the system bus.

Figure 12. Single Access Write from User Master Interface

A single write access is initiated with the assertion UMI\_RDY with valid data and address on UMI\_ADDR and UMI\_WDATA. UMI\_RDY is the gating signal for valid data and address and is to be asserted for every single access write transaction. On the next cycle, UMI\_ACK is de-asserted. When the write transaction is complete, UMI\_ACK is asserted by the UMI. UMI\_ACK will go low during the transfer for two cycles in synchronous mode and 6-7 cycles in asynchronous mode at best conditions.

UMI\_ACK is a synchronous signal and stays asserted after the single write is completed. One cycle before UMI\_ACK goes high again, the UMI\_ERR or UMI\_RETRY will go high if the current transfer gets ERROR or RETRY response from the system bus. The master interface itself may or may not do any retry by itself depending on configuration. UMI\_ACK, UMI\_ERR and UMI\_RETRY will remain high until UMI\_RDY is asserted again to begin the next transfer.

Consecutive single writes may be performed with the assertion of UMI\_RDY along with new data and address. UMI\_WR\_N is to be asserted for the entire period of the transaction. UMI\_ACK gets de-asserted on the clock cycle after UMI\_RDY and gets asserted when the transaction is complete and ready for the next transaction.

A typical 8-bit wide data, single access read transaction is show in Figure 13. UMI\_RDATA [7:0]=0x11 is read from 0x00004. Again, the UMI\_LOCK signal is not used to lock the system bus.

Figure 13. Single Access Read from User Master Interface

A single access read is initiated with the assertion of UMI\_RDY with a valid read address on UMI\_ADDR. UMI\_RDY is the gating signal for valid address and is to be asserted for only one UMI\_CLK cycle for every single read transaction. On the next cycle, UMI\_ACK is de-asserted. When the read data is ready at the UMI\_RDATA ports, UMI\_ACK is asserted by the UMI. UMI\_ACK is a synchronous signal and stays asserted after the single read is completed. UMI\_ACK will go low during the transfer for two cycles in synchronous mode and 6-7 cycles in asynchronous mode at best conditions.

In case of an ERROR or RETRY response from the system bus, UMI\_ERR or UMI\_RETRY will be asserted one cycle before UMI\_ACK goes high. UMI\_ERR and UMI\_RETRY will be de-asserted once UMI\_ACK goes low again at the onset of the next transaction.

Consecutive signal reads may be performed with the assertion of UMI\_RDY along with the new address. UMI\_WR\_N is to be de-asserted for the entire period of the transaction. On the next UMI\_CLK with UMI\_RDY high, UMI\_ACK is de-asserted. UMI\_ACK is re-asserted when the transaction is complete and ready for the next transaction. Signal UMI\_RDY should only be high for one UMI\_CLK cycle.

#### **UMI Burst Access**

Burst access is initiated by asserting the UMI\_BURST signal along with UMI\_WR\_N. The UMI handles bursts that are exactly four beats deep. It employs a 4-beat deep FIFO that is 36 bits wide. It handles and generates burst writes and reads that are four deep regardless of the size of the bus chosen by UMI\_SIZE. All address and data mapping is retained across the master interface.

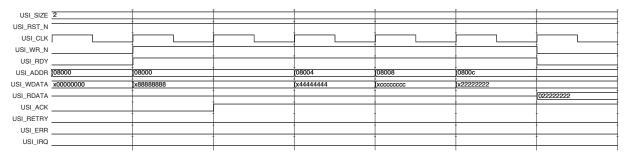

For a write burst, when UMI\_ACK is high, a high on UMI\_WR\_N, UMI\_RDY and UMI\_BURST for one cycle will result in an exact 4-beat burst write transfer. UMI\_ACK will go low after this cycle until the transfer is finished. The UMI\_ADDR and the first of the 4-burst data on UMI\_WDATA have to be valid for this cycle. The UMI\_WR\_N and UMI\_ADDR/UMI\_SIZE may be valid for only this one cycle. However, UMI\_RDY has to be high for three more cycles. Note that it is not necessary for UMI\_RDY to be high for four continuous cycles and there could be lows in between, but UMI\_BURST must be high during this period. If UMI\_BURST is de-asserted before the fourth high on UMI\_RDY, UMI\_ERR will be asserted one or more cycles before UMI\_ACK is asserted and the burst transfer is aborted. One cycle before UMI\_ACK goes high again, the UMI\_ERR or UMI\_RETRY may also go high if the transfer gets ERROR or RETRY response from the slave or the master interface loses mastership during the 4-beat transfer. UMI\_ACK will go low before going high again for six cycles in synchronous mode and 10-11 cycles in asynchronous mode at best conditions. Figure 14 illustrates an 8-bit wide data 4-beat UMI burst write cycle.

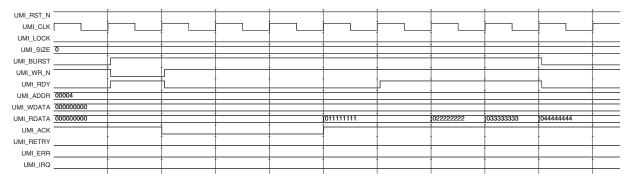

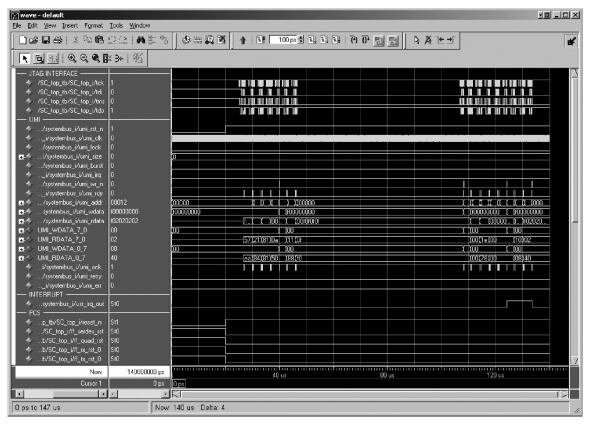

UMI BST N UMI\_CLK UMI\_LOCK UMI SIZE 0 UMI BURST UMI\_WR\_N UMI\_RDY UMI ADDR 00004 UMI WDATA 00000000 (011111111 02222222 (033333333 04444444 000000000 UMI\_RDATA 00000000 UMI ACK UMI RETRY UMI\_ERR

Figure 14. UMI BURST WRITE

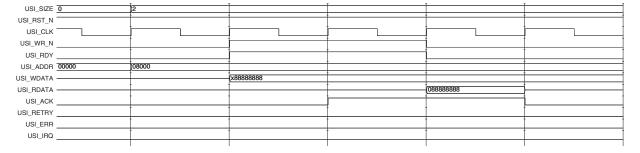

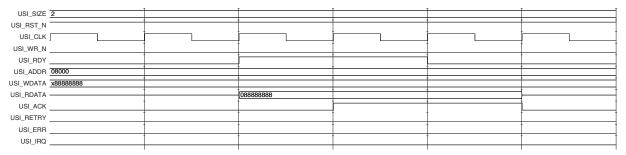

A read burst access is initiated with the assertion of input high on UMI\_RDY and UMI\_BURST and input low on UMI\_WR\_N for one cycle. This results in a 4-beat (4-byte, 4-halfword or 4-word) burst read transfer. UMI\_ACK will go low after this cycle. The UMI\_ADDR/UMI\_SIZE must be valid for this cycle, too, and the UMI\_ADDR is the beginning address for four data reads. There may be a wrap operation on burst address calculation. The transfer finishes after UMI\_ACK goes high again for four more active cycles, which may not be continuous four cycles. One of the four read data on UMI\_RDATA is valid for each active cycle of UMI\_ACK. Each of the four active cycles terminates after a cycle of high on UMI\_RDY. Note that it is possible for UMI\_ACK to be low between active cycles due to burst FIFO operation. It is necessary for UMI\_RDY to be high for three cycles during UMI\_ACK high, but UMI\_BURST has to be always high until the third active cycle. If UMI\_BURST is de-asserted before the third active cycle, UMI\_ERR will be asserted one or more cycles before UMI\_ACK is asserted and the burst transfer is aborted. UMI\_ACK will go low before going high again for three cycles in synchronous mode and eight to nine cycles in asynchronous mode at best conditions. Figure 15 illustrates an 8-bit wide data 4-beat UMI burst read cycle.

Figure 15. UMI Burst Read

Note that in both Figure 14 and Figure 15:

- The first write/read access is to 0x00004 (UMI\_W/RDATA [7:0]= 0x11).

- The second write/read access is to 0x00005 (UMI\_W/RDATA [7:0]= 0x22).

- The third write/read access is to 0x00006 (UMI\_W/RDATA [7:0]= 0x33).

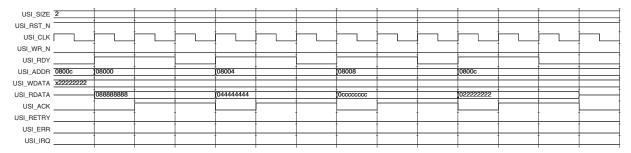

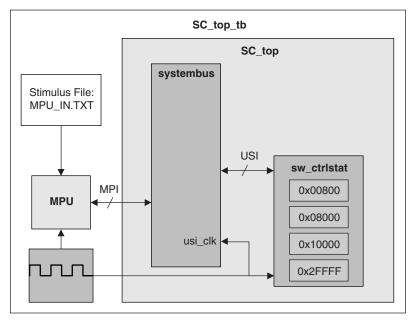

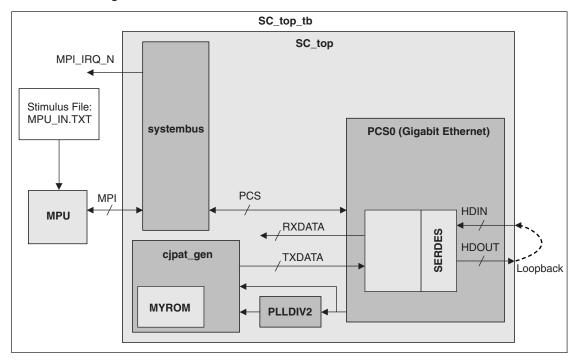

- The fourth write/read access is to 0x00007 (UMI\_W/RDATA [7:0]= 0x44).