# LatticeSC sysCONFIG Usage Guide

October 2008 Technical Note TN1080

#### Introduction

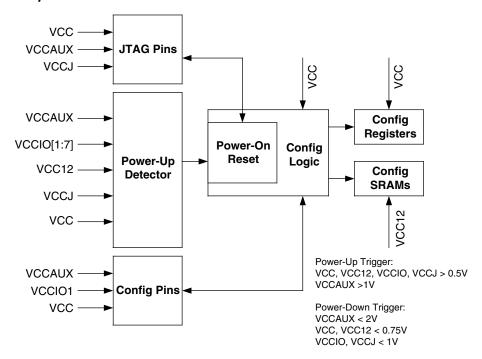

Configuration is the process of loading or programming a design into volatile memory of an SRAM-based FPGA. This is accomplished via a bitstream file, representing the logical states, that is loaded into the FPGA internal configuration SRAM memory. The device's functional operation after being programmed is determined by these internal configuration RAM settings. The SRAM cells must be loaded with configuration data each time the device powers up.

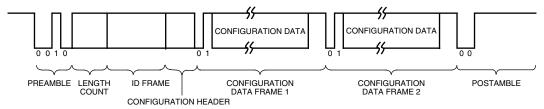

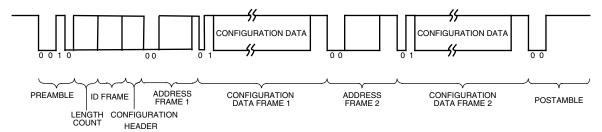

This technical note is segmented into three main sections: Configuration Modes, Bitstream Generation, and Configuration Process & Flow. The Configuration Modes section shows all the different modes with pin information, schematic diagrams, functional timing waveforms and descriptions. The Bitstream Generation section describes the options available when creating a bitstream file with the ispLEVER® Bitstream Data Generator software program; this section also shows the configuration frame format and content. The Configuration Process & Flow section details the states of operation of the device during configuration, miscellaneous configuration options, configuration frame sizes and bitstream file contents. This document does not contain any configuration performance specifications for devices. Waveforms are presented for reference, however AC timing is not included. Refer to the <a href="LatticeSC/M Family Data Sheet">LatticeSC/M Family Data Sheet</a> for this information.

## **Configuration Modes**

The LatticeSC<sup>™</sup> configuration RAM can be loaded in a number of different modes. In these configuration modes, the FPGA can act as a master, a peripheral to a CPU, or a slave of other system devices. It also supports in-system configuration via the JTAG port.

The decision as to which configuration mode to use is a system design concern. There are many methods for configuring the FPGA utilizing four basic schemes.

**Master** – As a master, the FPGA is the source of the clock, which addresses an external PROM or EPROM storage device through either a serial or parallel data connection, with no additional timing or control signals used. This scheme includes Serial Programming Interface (SPI) that supports a seamless connection for programming using industry-standard external Flash-based memory devices.

**Peripheral** – In the peripheral mode, the FPGA acts as a CPU peripheral and accepts parallel data and interacts with the source of data, usually with a Ready/Busy handshake. This includes MPI (microprocessor interface) mode where the FPGA receives bus wide data (8, 16, 32-bit), control and a clock from a microprocessor as a direct extension to the processor bus.

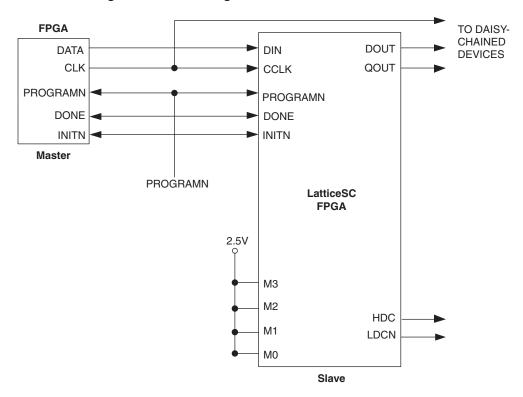

**Slave** – FPGA receives bit-serial or byte-wide data and a clock from an external data and timing source, either from a microprocessor, or from the lead device in an FPGA-daisy chain. As a slave device, a clock is generated externally and provided into the CCLK input.

**JTAG** – The device can be configured through the ispJTAG $^{\text{TM}}$  port. The JTAG port is always on and available regardless of the configuration mode selected.

The system designer should determine the requirements for configuration very early in the design. Many factors must be considered when deciding which configuration mode is best suited for the design. The flexible features for configuration can provide a seamless design to the system.

The following table will assist the user in deciding which configuration mode is best suited for a particular design. The table queries the system features that may help the user understand which programming mode may be best suited for the design.

Table 1. Configuration Mode Overview

| Configuration<br>Mode      | Microprocessor<br>Support | Programming<br>Latency Cost | Required<br>Interconnection<br>Cost | Supports<br>Bitstream<br>Compression | Key Features                                            |

|----------------------------|---------------------------|-----------------------------|-------------------------------------|--------------------------------------|---------------------------------------------------------|

| Master Serial              | No                        | High                        | Low                                 | Yes                                  |                                                         |

| Master Parallel            | No                        | High                        | Medium                              | Yes                                  |                                                         |

| Master Byte                | No                        | Low                         | Medium                              | Yes                                  | Supports 8-bit parallel daisy-chaining                  |

| Asynchronous<br>Peripheral | Yes                       | High                        | Medium                              | Yes                                  | Support for micro-controller and other 8-bit interfaces |

| MPI -8, -16, -32           | Yes                       | Low                         | High                                | Yes                                  | Glue-less interface to PowerPC micro-<br>processors     |

| Slave Serial               | No                        | High                        | Low                                 | No                                   |                                                         |

| Slave Parallel             | No                        | Low                         | Medium                              | Yes                                  |                                                         |

| SPI                        | No                        | High                        | Low                                 | Yes                                  | Inexpensive Flash memory support                        |

| SPIX                       | No                        | High                        | Low                                 | Yes                                  | Inexpensive Flash memory support                        |

| JTAG                       | No                        | High                        | Low                                 | No                                   | IEEE 1532                                               |

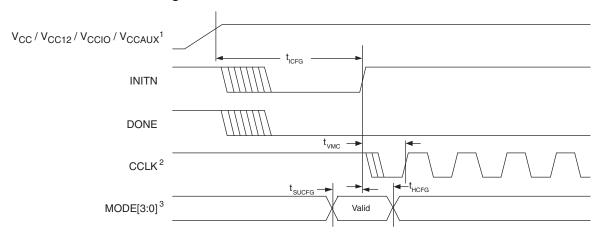

All the programming interfaces except JTAG require an initial setting of the Mode[3:0] input pins prior to power up or re-initialization. This setting is latched on the rising edge of INITN and is used by the configuration logic to determine the appropriate clock, data, and control handshake signaling. Table 2 lists the functions of the configuration mode pins.

Table 2. Mode Pin Logic Settings

| Configuration | Mode       | M[3] | M[2] | M[1] | M[0] | CCLK   | Data       | Daisy<br>Chaining |

|---------------|------------|------|------|------|------|--------|------------|-------------------|

| Master        | Serial     | 1    | 0    | 0    | 0    | Output | 1-bit      | Serial            |

| Master        | Parallel   | 1    | 1    | 0    | 0    | Output | 8-bit      | Serial            |

| Master        | Byte       | 0    | 1    | 1    | 0    | Output | 8-bit      | 8-bit             |

| Asynchronous  | Peripheral | 1    | 1    | 0    | 1    | Output | 8-bit      | Serial            |

| Slave         | Serial     | 1    | 1    | 1    | 1    | Input  | 1-bit      | Serial            |

| Slave         | Parallel   | 1    | 0    | 0    | 1    | Input  | 8-bit      | None              |

| SPI           | Serial     | 0    | 1    | 0    | 1    | Output | 1 or 8-bit | Serial            |

| SPIX          | Serial     | 0    | 1    | 0    | 0    | Output | 1 or 8-bit | Serial            |

| MPI           | 8-bit      | 1    | 0    | 1    | 0    | Output | 8-bit      | Serial            |

| MPI           | 16-bit     | 1    | 0    | 1    | 1    | Output | 16-bit     | Serial            |

| MPI           | 32-bit     | 1    | 1    | 1    | 0    | Output | 32-bit     | Serial            |

| JTAG 1532     | Serial     | Χ    | Х    | Х    | Х    | NA     | 1-bit      | Serial            |

## **Configuration Pins**

The LatticeSC devices support two types of sysCONFIG™ pins, dedicated and dual-purpose. This document will use names based on the purpose used by a specified configuration mode. There are many pins used for various functions across many modes. There are some dedicated device pins that are defined exclusively for configuration functions. The dual-purpose pins are available as extra user-defined I/O pins when not being used for configuration. A programmable option controls the dual-purpose configuration pins. This option is made via a preference in Lattice ispLEVER software or as an HDL source file attribute. The LatticeSC devices also support the ispJTAG port for configuration, including transparent read back and JTAG testing. Appendix A describes the functionality of the sysCONFIG and ispJTAG pins.

Most of the LatticeSC configuration pins are considered dual purpose; they are used as configuration pins during configuration, and then are user I/Os after configuration. Both the dedicated and dual-purpose configuration pins are physically located in VCCIO1 (bank 1). JTAG pins are powered by a dedicated VCCJ supply. Table 3 highlights the use of each pin per configuration mode. VCCO1 can be 1.8V, 2.5V or 3.3V for configuration.

Upon power up or during re-initialization of the FPGA, configuration is done using default LVCMOS buffers (which operate between 1.8V and 3.3V). As configuration is taking place, the buffer type will change to the user-specified buffer type in the FPGA design in all banks except bank 1. Bank 1 buffer types will change only after the configuration is completed. The LatticeSC FPGA offers many high-speed PURESPEED™ I/O types having many different operation levels that may lead to improper behavior after configuration is completed. It is recommended not to use the PURESPEED I/O buffer types that are utilized for a particular programming mode except on these dual-use configuration pins for LVCMOS applications. Consequently, we do not recommend using the configuration pins as dual-use pins in order to avoid potential conflicts during the configuration process. A specific software control is available to the designer to prevent this type of conflict. This will be discussed later in this document.

Table 3. sysCONFIG Pin Usage

|                               |      |                 |                   | С                | onfigura           | tion Mod       | le                |               |     |                         |                         |

|-------------------------------|------|-----------------|-------------------|------------------|--------------------|----------------|-------------------|---------------|-----|-------------------------|-------------------------|

| Signal Name                   | JTAG | Slave<br>Serial | Slave<br>Parallel | Master<br>Serial | Master<br>Parallel | Master<br>Byte | Asynch<br>Periph. | SPI /<br>SPIX | MPI | Serial<br>Read-<br>back | VCCIO<br>Bank 1<br>Type |

| RESETN                        | ~    | ~               | ~                 | ~                | ~                  | ~              | ~                 | ~             | ~   |                         |                         |

| CCLK                          |      | ~               | ~                 | ~                | ~                  | ~              | ~                 | ~             | ~   |                         |                         |

| DONE                          | ~    | ~               | ~                 | ~                | ~                  | ~              | ~                 | ~             | ~   |                         |                         |

| PROGRAMN                      | ~    | ~               | ~                 | ~                | ~                  | ~              | ~                 | ~             |     |                         | Dedicated               |

| RDCFGN                        | ~    | ~               | ~                 | ~                | ~                  | ~              | ~                 | ~             | ~   | ~                       | Dedicated               |

| INITN                         | ~    | ~               | ~                 | ~                | ~                  | ~              | ~                 | ~             | ~   |                         |                         |

| CFGIRQN/MPI_IRQ_N             |      | ~               | ~                 | ~                | ~                  | ~              | ~                 | ~             | ~   |                         |                         |

| M[3:0]                        |      | ~               | ~                 | ~                | ~                  | ~              | ~                 | ~             | ~   |                         |                         |

| TDO/RDDATA                    | ~    |                 |                   |                  |                    |                |                   |               |     | ~                       |                         |

| TCK                           | ~    |                 |                   |                  |                    |                |                   |               |     |                         | VCCJ                    |

| TDI                           | ~    |                 |                   |                  |                    |                |                   |               |     |                         | - VCC3                  |

| TMS                           | ~    |                 |                   |                  |                    |                |                   |               |     |                         |                         |

| QOUT/CEON                     |      | ~               | ~                 | ~                | ~                  | ~              | ~                 | ~             | ~   |                         |                         |

| DOUT                          |      | ~               | ~                 | ~                | ~                  |                | ~                 | ~             | ~   |                         |                         |

| RDY/BUSYN/RCLK                |      |                 | ~                 | ~                | ~                  |                | ~                 | ~             | ~   |                         |                         |

| HDC                           |      | ~               | ~                 | ~                | ~                  | ~              | ~                 | ~             | ~   |                         |                         |

| LDCN                          |      | ~               | ~                 | ~                | ~                  | ~              | ~                 | ~             | V   |                         |                         |

| CS0N, CS1                     |      |                 | ~                 |                  | ~                  |                | ~                 | ~             | ~   |                         |                         |

| RDN                           |      |                 |                   |                  |                    |                | ~                 |               | ~   |                         |                         |

| WRN                           |      |                 |                   |                  |                    |                | ~                 | ~             | V   |                         | Dual Use                |

| D[0]                          |      | ~               | ~                 | ~                |                    | ~              | ~                 | ~             | V   |                         |                         |

| D[7:1]                        |      |                 | ~                 |                  | ~                  |                | ~                 | ~             | ~   |                         |                         |

| A[21:0]                       |      |                 |                   |                  | ~                  |                |                   |               | ~   |                         |                         |

| MPI_TA, MPI_TEA,<br>MPI_RETRY |      |                 |                   |                  |                    |                |                   |               | ~   |                         |                         |

| MPI_CLK                       |      |                 |                   |                  |                    |                |                   |               | ~   |                         | 1                       |

| D[31:8], DP[3:0]              |      |                 |                   |                  |                    |                |                   |               | ~   |                         |                         |

#### **Master Serial Mode**

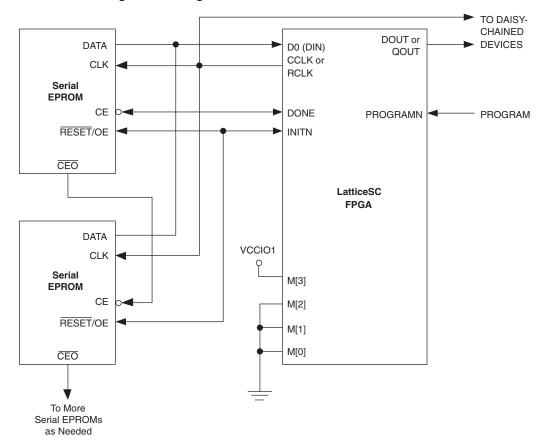

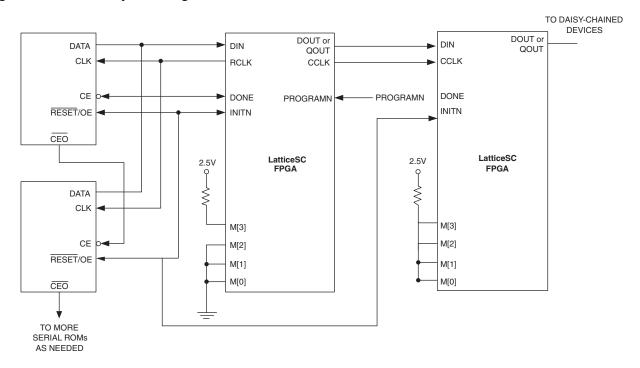

In the master serial mode, the FPGA loads the configuration data from an external serial ROM. The configuration data is either loaded automatically at start-up or on a command using the PROGRAMN pin to reconfigure. Serial PROMs can be used to configure the FPGA in the master serial mode and is shown in Figure 1.

Figure 1. Master Serial Configuration Diagram

| Dedicated Master<br>Serial Pins | I/O | Description                                                                                                                                                                                     |

|---------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESETN                          | ı   | Active low input prior to configuration done, forces the restart of configuration. An internal active pull up is defaulted prior to configuration. This can be deactivated after configuration. |

|                                 |     | Optionally user-programmed to connect to GSR after configuration.                                                                                                                               |

| CCLK                            | 0   | CCLK is an output which strobes configuration data into daisy-chained devices. CCLK is output for daisy-chaining operation when the lead FPGA is a master.                                      |

| DONE                            | I/O | As an input, a low level on DONE delays FPGA wake-up after configuration if the appropriate wake-up options are set.                                                                            |

|                                 |     | As an active-high, open-drain output, a high level on this signal indicates that configuration is complete. Optional user programmable 100K internal pull up                                    |

| PROGRAMN                        | I   | PROGRAMN is an active-low input that forces the restart of configuration. This pin always has an active pull-up.                                                                                |

| <b>Dedicated Master</b> |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial Pins             | I/O      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RDCFGN                  | I        | This pin must be held high during device initialization until the INITN pin goes high. This pin always has an active pull-up.  During configuration, RDCFGN is an active-low input that activates the TSALL function and 3-states all of the I/O. After configuration, it can be selected to activate the TSALL function as described above, or, if read-back is enabled via a bitstream option, a high-to-low transition on it will initiate read-back of the configuration data starting with frame address 0. |

| INITN                   | I/O      | INITN is a dedicated bidirectional signal before and during configuration. A pull-up is always enabled, but an external 10K ohm pull-up resistor is recommended. As an active-low opendrain output, INITN is held low during power stabilization and internal clearing of memory. As an active-low input, INITN holds the FPGA in the wait-state before the start of configuration.                                                                                                                              |

| CFGIRQN                 | 0        | During JTAG, slave, master, and asynch. peripheral configuration, assertion on this CFGIRQN (active low) indicates error(s) for block RAM or MACO™ initialization. A programmable pull-up resistor is available on this pin.                                                                                                                                                                                                                                                                                     |

| M[3:0]                  | I        | During power-up and initialization, M[3:0] are used to select the configuration mode with their values latched on the rising edge of INITN. After configuration these pins are available as user defined inputs. Mode Pin Setting: M[3]=1, M[2]=0, M[1]=0, M[0]=0                                                                                                                                                                                                                                                |

| Dual-Purpose Pins:      | After co | onfiguration, these pins are user-programmable I/O pins                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DOUT                    | 0        | DOUT is the serial data output that can drive the D0/DIN of daisy-chained slave devices. The data-stream from this output will propagate preamble bits of the bitstream to daisy-chained devices. Data out on DOUT changes on the rising edge of CCLK.                                                                                                                                                                                                                                                           |

| QOUT                    | 0        | During daisy-chaining configuration, QOUT is the serial data output that can drive the D0/DIN of daisy-chained slave devices that do NOT propagate preamble bits. Data out on QOUT changes on the rising edge of CCLK.                                                                                                                                                                                                                                                                                           |

| RCLK                    | 0        | RCLK is a read clock output signal to an external memory. The RCLK frequency is the same as CCLK when used with uncompressed bitstreams. However, RCLK will be 1/8 the frequency of CCLK when the bitstream is compressed.                                                                                                                                                                                                                                                                                       |

| HDC                     | 0        | High During Configuration is output high until configuration is complete. It is used as a control output, indicating that configuration is not complete.                                                                                                                                                                                                                                                                                                                                                         |

| LDCN                    | 0        | Low During Configuration is output low until configuration is complete. It is used as a control output, indicating that configuration is not complete.                                                                                                                                                                                                                                                                                                                                                           |

| D0(DIN)                 | I        | D[0](DIN) receives configuration data, and the pin is pull-up enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

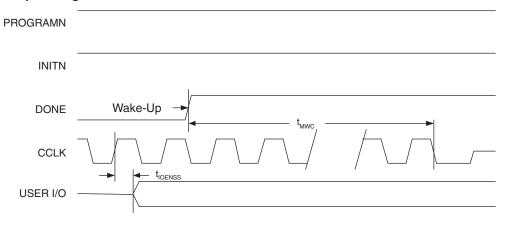

Configuration in the master serial mode can be done at power-up and/or on command. The system or the FPGA must activate the serial ROM's RESET/OE and CE inputs. At power-up, the FPGA and serial ROM each contain internal power-on reset circuitry that allows the FPGA to be configured without the system providing an external signal. The power-on reset circuitry causes the serial ROM's internal address pointer to be reset. After power up, the FPGA automatically enters its initialization phase. The serial ROM/FPGA interface used depends on such factors as the availability of a system reset pulse, availability of an intelligent host to generate a configure command, whether a single serial ROM is used or multiple serial ROMs are cascaded, whether the serial ROM contains a single or multiple configuration programs, etc. Because of differing system requirements and capabilities, a single FPGA/serial ROM interface is not appropriate for all applications.

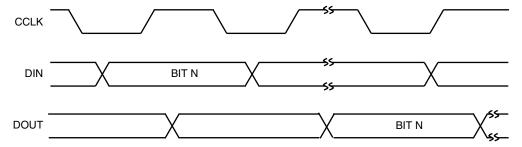

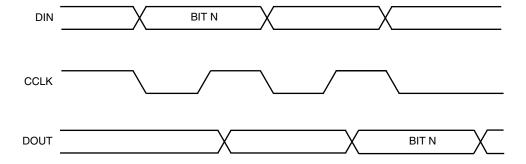

Data is read by the FPGA sequentially from the serial ROM. The DATA output from the serial ROM is connected directly into the DIN input of the FPGA. The CCLK output from the FPGA is connected to the CLK input of the serial ROM. During the configuration process, CCLK clocks one data bit on each rising edge.

Since the data and clock are direct connects, the FPGA/serial ROM design task is to use the system or FPGA to enable the RESET/OE and CE of the serial ROM(s). There are several methods for enabling the serial ROM's RESET/OE and CE inputs. The serial ROM's RESET/OE is programmable to function with RESET active-high and OE active-low or RESET active-low and OE active-high.

With the before-mentioned PROM options, the FPGA's INITN pin is connected to the serial ROMs' RESET/OE input, which has been programmed to function with RESET active-low and OE active-high. The control host gener-

ates a 500 ns low pulse to the FPGA's PROGRAMN input pin; this will cause INITN to output pulse low to high. The FPGA DONE is connected to the CE pin. The low on DONE enables the serial ROMs. At the completion of configuration, the high on the FPGAs DONE disables the serial ROM.

Serial ROMs can also be cascaded to support the configuration of multiple FPGAs or to load a single FPGA when configuration data requirements exceed the capacity of a single serial ROM. After the last bit from the first serial ROM is read, the serial ROM outputs CEO low and 3-states the DATA output. The next serial ROM recognizes the low on CE input and outputs configuration data on the DATA output. After configuration is complete, the FPGA's DONE output into CE disables the serial ROMs. This FPGA/serial ROM interface is not used in applications in which a serial ROM stores multiple configuration programs. In these applications, the next configuration program to be loaded is stored at the ROM location that follows the last address for the previous configuration program. In some applications, there can be contention on the FPGA's DIN pin. During configuration, DIN receives configuration data, and after configuration, it is a user I/O. If there is contention, an early DONE at start-up (selected with the ispLEVER Bitgen program) may correct the problem.

In master serial mode, the CCLK output of the master device is used for both the external PROM device and daisy-chained devices. The two clocks required for compressed bitstream loading are accomplished by adding the use of the RCLK output, which is a common output pin with master parallel mode and asynchronous peripheral modes. In normal uncompressed daisy-chained devices, the CCLK output is used to provide a clock during loading. However if the bitstream is compressed, the PROM device has to use the RCLK output. If the bitstream is uncompressed, the RCLK follows CCLK.

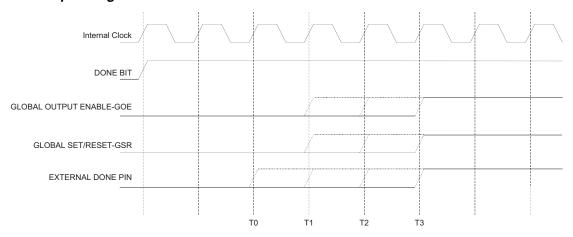

Figure 2. Master Serial Configuration Timing Waveform

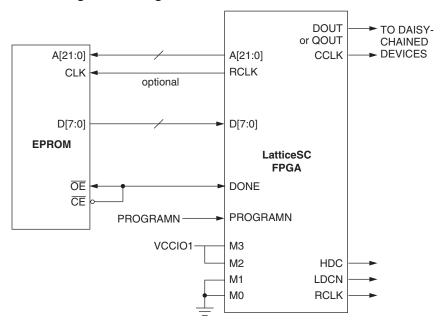

#### **Master Parallel Mode**

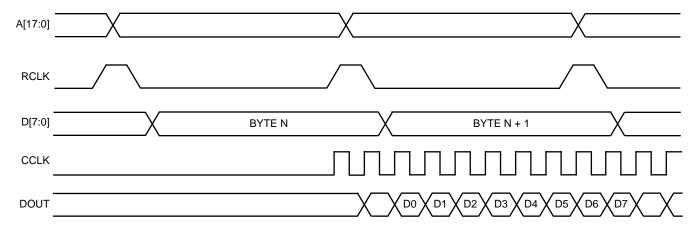

The master parallel configuration mode is generally used to interface to industry-standard, byte-wide memory devices. Figure 3 depicts the interface connections to an EPROM device. The FPGA outputs up to a 22-bit address on A[21:0] to the memory device and reads one byte of configuration data on the rising edge of RCLK. Optionally, RCLK can be driven by the FPGA to the PROM. The parallel bytes are internally serialized starting with the least significant bit, D0. Serial data can be daisy-chained to downstream devices. The 8-bit data bus D[7:0] of the FPGA can be connected to data bus D[7:0] of the microprocessor if a standard PROM file format is used

Figure 3. Master Parallel Configuration Diagram

| Dedicated Master<br>Parallel Pins | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESETN                            | ı   | Active low input prior to configuration done, forces the restart of configuration. An internal active pull up is defaulted prior to configuration. This can be deactivated after configuration.                                                                                                                                                                                                                                                                                                                  |

|                                   |     | Optionally user-programmed to connect to GSR after configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CCLK                              | 0   | CCLK is an output which strobes configuration data into daisy-chained devices. CCLK is output for daisy-chaining operation when the lead FPGA is a master.                                                                                                                                                                                                                                                                                                                                                       |

| DONE                              | I/O | As an input, a low level on DONE delays FPGA wake-up after configuration if the appropriate wake-up options are set. As an active-high, open-drain output, a high level on this signal indicates that configuration is complete.  Optional user programmable 100K internal pull up                                                                                                                                                                                                                               |

| PROGRAMN                          | ı   | Active-low input forces the restart of configuration. This pin always has an active pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RDCFGN                            | I   | This pin must be held high during device initialization until the INITN pin goes high. This pin always has an active pull-up.  During configuration, RDCFGN is an active-low input that activates the TSALL function and 3-states all of the I/O. After configuration, it can be selected to activate the TSALL function as described above, or, if read-back is enabled via a bitstream option, a high-to-low transition on it will initiate read-back of the configuration data starting with frame address 0. |

| INITN                             | I/O | INITN is a dedicated bidirectional signal before and during configuration. A pull-up is always enabled, but an external 10K ohm pull-up resistor is recommended. As an active-low opendrain output, INITN is held low during power stabilization and internal clearing of memory. As an active-low input, INITN holds the FPGA in the wait-state before the start of configuration.                                                                                                                              |

| CFGIRQN                           | 0   | During JTAG, slave, master, and asynch. peripheral configuration, assertion on this CFGIRQN (active low) indicates error(s) for block RAM or MACO initialization. A programmable pull-up resistor is available on this pin.                                                                                                                                                                                                                                                                                      |

| M[3:0]                            | I   | During power-up and initialization, M[3:0] are used to select the configuration mode with their values latched on the rising edge of INITN. After configuration these pins are available as user defined inputs. Mode Pin Setting: M[3]=1, M[2]=1, M[1]=0, M[0]=0                                                                                                                                                                                                                                                |

| Dedicated Master Parallel Pins | 1/0      | Description                                                                                                                                                                                                                                                                  |

|--------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                |          | •                                                                                                                                                                                                                                                                            |

| Dual-Purpose Pins:             | After co | onfiguration, these pins are user-programmable I/O pins                                                                                                                                                                                                                      |

| DOUT                           | 0        | During configuration, DOUT is the serial data output that can drive the D0/DIN of daisy-chained slave devices. The data-stream from this output will propagate preamble bits of the bitstream to daisy-chained devices. Data out on DOUT changes on the rising edge of CCLK. |

| QOUT                           | 0        | During daisy-chaining configuration, QOUT is the serial data output that can drive the D0/DIN of daisy-chained slave devices that do NOT propagate preamble bits. Data out on QOUT changes on the rising edge of CCLK.                                                       |

| RCLK                           | 0        | RCLK is a read clock output signal to an external memory. The RCLK frequency is the same as CCLK when used with uncompressed bitstreams. However, RCLK will be 1/8 the frequency of CCLK when the bitstream is compressed.                                                   |

| HDC                            | 0        | High During Configuration is output high until configuration is complete. It is used as a control output, indicating that configuration is not complete.                                                                                                                     |

| LDCN                           | 0        | Low During Configuration is output low until configuration is complete. It is used as a control output, indicating that configuration is not complete.                                                                                                                       |

| D[7:0]                         | I        | D[7:0] receives configuration data, and each pin is pull-up enabled.                                                                                                                                                                                                         |

| A[21:0]                        | 0        | A[21:0] are optional outputs and will address the configuration PROMs up to 4MB space.                                                                                                                                                                                       |

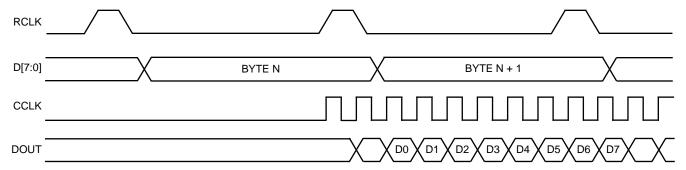

In master parallel mode, the starting memory address is 00000 Hex, and the FPGA increments the address for each byte loaded. One master FPGA can interface to the memory and provide configuration data on DOUT or QOUT to additional FPGAs in a daisy chain. The configuration data on DOUT or QOUT is provided synchronously with the rising edge of CCLK. The frequency of the CCLK output is eight times that of RCLK.

Figure 4. Master Parallel Timing Configuration Waveform

## **Master Byte Mode**

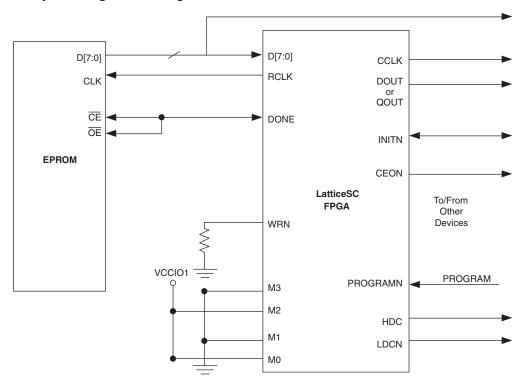

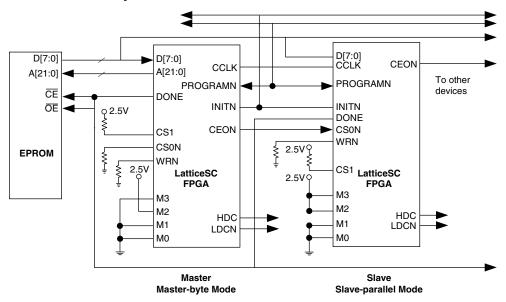

Master byte mode supports byte-wide parallel configuration daisy chaining. In master byte mode the incoming 8-bit data is shifted directly into the FPGA in one clock cycle. The data bus is connected one-to-one with D[7:0] of the device being read. This mode allows for byte wide data and clock to be transmitted to all devices in a chain. The parallel chaining will be discussed later in the document. Figure 5 depicts the connections between the FPGA and a parallel EPROM device.

Figure 5. Master Byte Configuration Diagram

| Dedicated Master<br>Byte Pins | I/O | Description                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESETN                        | I   | Active low input prior to configuration done, forces the restart of configuration. An internal active pull up is defaulted prior to configuration. This can be deactivated after configuration.                                                                                                                                                                                     |

|                               |     | Optionally user-programmed to connect to GSR after configuration.                                                                                                                                                                                                                                                                                                                   |

| CCLK                          | 0   | CCLK is an output which strobes configuration data into daisy-chained devices. CCLK is output for daisy-chaining operation when the lead FPGA is a master.                                                                                                                                                                                                                          |

| DONE                          | I/O | As an input, a low level on DONE delays FPGA wake-up after configuration if the appropriate wake-up options are set. As an active-high, open-drain output, a high level on this signal indicates that configuration is complete.                                                                                                                                                    |

|                               |     | Optional user programmable 100K internal pull up                                                                                                                                                                                                                                                                                                                                    |

| PROGRAMN                      | I   | Active-low input forces the restart of configuration. This pin always has an active pull-up.                                                                                                                                                                                                                                                                                        |

|                               |     | This pin must be held high during device initialization until the INITN pin goes high. This pin always has an active pull-up.                                                                                                                                                                                                                                                       |

| RDCFGN                        | I   | During configuration, RDCFGN is an active-low input that activates the TSALL function and 3-states all of the I/O. After configuration, it can be selected to activate the TSALL function as described above, or, if read-back is enabled via a bitstream option, a high-to-low transition on it will initiate read-back of the configuration data starting with frame address 0.   |

| INITN                         | I/O | INITN is a dedicated bidirectional signal before and during configuration. A pull-up is always enabled, but an external 10K ohm pull-up resistor is recommended. As an active-low opendrain output, INITN is held low during power stabilization and internal clearing of memory. As an active-low input, INITN holds the FPGA in the wait-state before the start of configuration. |

| CFGIRQN                       | 0   | During JTAG, slave, master, and asynch. peripheral configuration, assertion on this CFGIRQN (active low) indicates error(s) for block RAM or MACO initialization. A programmable pull-up resistor is available on this pin.                                                                                                                                                         |

| Dedicated Master<br>Byte Pins | I/O      | Description                                                                                                                                                                                                                                                                  |

|-------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M[3:0]                        | I        | During power-up and initialization, M[3:0] are used to select the configuration mode with their values latched on the rising edge of INITN. After configuration these pins are available as user defined inputs.Mode Pin Setting: M[3]=0, M[2]=1, M[1]=0, M[0]=1             |

| <b>Dual-Purpose Pins:</b>     | After co | onfiguration, these pins are user-programmable I/O pins                                                                                                                                                                                                                      |

| DOUT                          | 0        | During configuration, DOUT is the serial data output that can drive the D0/DIN of daisy-chained slave devices. The data-stream from this output will propagate preamble bits of the bitstream to daisy-chained devices. Data out on DOUT changes on the rising edge of CCLK. |

| CEON                          | 0        | During parallel-chaining configuration, active low CEON enables the cascaded slave device to receive bitstream data. Can be connected to CS0N of daisy-chained slave device.                                                                                                 |

| RCLK                          | 0        | RCLK is a read clock output signal to an external memory.                                                                                                                                                                                                                    |

| HDC                           | 0        | High During Configuration is output high until configuration is complete. It is used as a control output, indicating that configuration is not complete.                                                                                                                     |

| LDCN                          | 0        | Low During Configuration is output low until configuration is complete. It is used as a control output, indicating that configuration is not complete.                                                                                                                       |

| WRN                           | I        | A low on the write strobe, WRN, loads the data on D[7:0] inputs into an internal data buffer.                                                                                                                                                                                |

| D[7:0]                        | I        | D[7:0] receives configuration data, and each pin is pull-up enabled.                                                                                                                                                                                                         |

The leading master device must be in master byte mode while the down chain slave devices must be in the slave parallel mode. The CEON pin is needed for parallel chaining so that the leading device can enable the following device(s) to receive bitstream data after it completes configuration and asserts CEON output low.

The master byte mode can also support standalone decompression if it uses RCLK to drive the parallel PROM while using CCLK for internal shifting. However, both master byte and slave parallel modes cannot support decompression in parallel chaining configuration. Therefore, if decompression is used, CCLK and DOUT or QOUT must be sent to downstream devices.

The CS1 and WRN inputs for slave parallel mode should be tied to high and low, respectively, in a parallel chaining configuration. This permits CEON output and CS0N input to be linked in a chain.

Figure 6. Master Byte Timing Configuration Waveform

#### **Asynchronous Peripheral Mode**

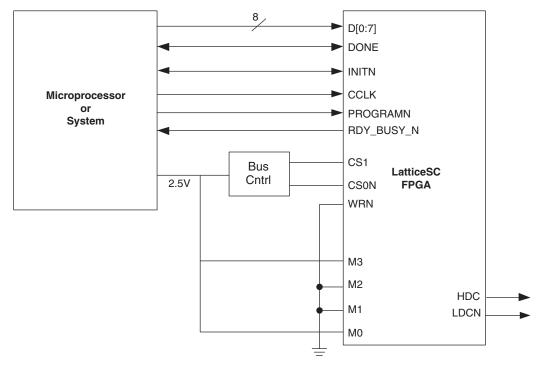

In Asynchronous Peripheral mode shown in Figure 7, the FPGA system interface is similar to that of a microprocessor-peripheral interface. This interface is suited for the system that may use any other processor other than the PowerPC or any other microcontroller based system. The microprocessor generates the control signals to write an 8-bit byte into the FPGA. The FPGA control inputs include active-low CS0N and active-high CS1 chip selects and WRN and RDN inputs. The chip selects can be cycled or maintained at a static level during the configuration cycle. Each byte of data is written into the FPGA's D[7:0] input pins. D[7:0] of the FPGA can be connected to D[7:0] of the microprocessor if a standard PROM file format is used.

Pigure 7. Asynchronous Peripheral Configuration Diagram

D[7:0] D[7:0] DC CC

| Dedicated<br>Asynchronous<br>Peripheral Pins | I/O | Description                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESETN                                       | I   | Active low input prior to configuration done, forces the restart of configuration. An internal active pull up is defaulted prior to configuration. This can be deactivated after configuration.                                                                                                                                                                                     |

|                                              |     | Optionally user-programmed to connect to GSR after configuration.                                                                                                                                                                                                                                                                                                                   |

| CCLK                                         | 0   | CCLK is an output which strobes configuration data into daisy-chained devices.                                                                                                                                                                                                                                                                                                      |

|                                              |     | As an input, a low level on DONE delays FPGA wake-up after configuration if the appropriate wake-up options are set.                                                                                                                                                                                                                                                                |

| DONE                                         | I/O | As an active-high, open-drain output, a high level on this signal indicates that configuration is complete.                                                                                                                                                                                                                                                                         |

|                                              |     | Optional user programmable 100K internal pull up                                                                                                                                                                                                                                                                                                                                    |

| PROGRAMN                                     | I   | PROGRAMN is an active-low input that forces the restart of configuration. This pin always has an active pull-up.                                                                                                                                                                                                                                                                    |

|                                              |     | This pin must be held high during device initialization until the INITN pin goes high. This pin always has an active pull-up.                                                                                                                                                                                                                                                       |

| RDCFGN                                       | I   | During configuration, RDCFGN is an active-low input that activates the TSALL function and 3-states all of the I/O. After configuration, it can be selected to activate the TSALL function as described above, or, if read-back is enabled via a bitstream option, a high-to-low transition on it will initiate read-back of the configuration data starting with frame address 0.   |

| INITN                                        | I/O | INITN is a dedicated bidirectional signal before and during configuration. A pull-up is always enabled, but an external 10K ohm pull-up resistor is recommended. As an active-low opendrain output, INITN is held low during power stabilization and internal clearing of memory. As an active-low input, INITN holds the FPGA in the wait-state before the start of configuration. |

| CFGIRQN                                      | 0   | Assertion on this CFGIRQN (active low) indicates error(s) for block RAM or MACO initialization. A programmable pull-up resistor is available on this pin.                                                                                                                                                                                                                           |

| Dedicated<br>Asynchronous<br>Peripheral Pins | I/O      | Description                                                                                                                                                                                                                                                                  |

|----------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M[3:0]                                       | I        | During power-up and initialization, M[3:0] are used to select the configuration mode with their values latched on the rising edge of INITN. After configuration these pins are available as user defined inputs. Mode Pin Setting: M[3]=1, M[2]=1, M[1]=0, M[0]=1            |

| Dual-Purpose Pins:                           | After co | onfiguration, these pins are user-programmable I/O pins                                                                                                                                                                                                                      |

| DOUT                                         | 0        | During configuration, DOUT is the serial data output that can drive the D0/DIN of daisy-chained slave devices. The data-stream from this output will propagate preamble bits of the bitstream to daisy-chained devices. Data out on DOUT changes on the rising edge of CCLK. |

| QOUT                                         | 0        | During daisy-chaining configuration, QOUT is the serial data output that can drive the D0/DIN of daisy-chained slave devices that do NOT propagate preamble bits. Data out on QOUT changes on the rising edge of CCLK.                                                       |

| BUSYN                                        | 0        | During configuration in peripheral mode, high on BUSYN indicates another byte can be written to the FPGA. If a read operation is done when the device is selected, the same status is also available on D[7] in asynchronous peripheral mode                                 |

| HDC                                          | 0        | High During Configuration is output high until configuration is complete. It is used as a control output, indicating that configuration is not complete.                                                                                                                     |

| LDCN                                         | 0        | Low During Configuration is output low until configuration is complete. It is used as a control output, indicating that configuration is not complete.                                                                                                                       |

| CS0N CS1                                     | I        | The FPGA is selected when CS0N is low and CS1 is high.                                                                                                                                                                                                                       |

| RDN                                          | I        | RDN is used in the asynchronous peripheral configuration mode. A low on RDN changes D[7:3] into status outputs. WRN and RDN should not be used simultaneously. If they are, the write strobe overrides.                                                                      |

| WRN                                          | I        | When the FPGA is selected, a low on the write strobe, WRN, loads the data on D[7:0] inputs into an internal data buffer                                                                                                                                                      |

| D[7:0]                                       | I/O      | D[7:0] receives configuration data, and each pin is pull-up enabled.D[7:3] output internal status for peripheral mode when RDN is low.                                                                                                                                       |

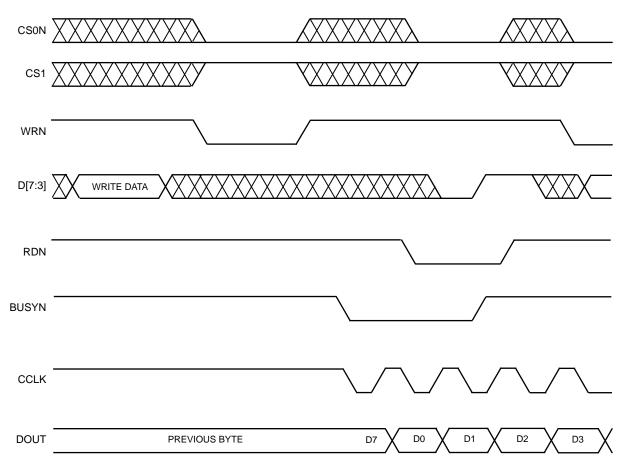

The FPGA provides a BUSYN status output to indicate that another byte can be loaded. A low on BUSYN indicates that the double-buffered hold/shift registers are not ready to receive data, and this pin must be monitored to go high before another byte of data can be written. The shortest time BUSYN is low occurs when a byte is loaded into the hold register and the shift register is empty. In this case, the byte is immediately transferred to the shift register. The longest time for BUSYN to remain low occurs when a byte is loaded into the holding register and the shift register has just started shifting configuration data into configuration RAM.

Status is also available on the D[7:3] pins by enabling the chip selects, setting WRN high, and applying RDN low, where the RDN input provides an output enable for the D[7:3] pins when RDN is low. The following status indicators are available.

```

D[7]=BUSYN

D[6:5]=ERR_FLAG[1:0], bitstream error flags.

00=No errors, 01=id error, 10= checksum error, 11= alignment error

D[4:3]=CFG_BUS_ERR[1:0], system bus error responses during configuration

00= None, 10=One Error, 11= Multiple Errors

```

The D[2:0] pins are not enabled to drive when RDN is low and, therefore, only act as input pins in asynchronous peripheral mode. Optionally, the user can monitor the RDY/BUSY status and simply wait until the RDY/BUSY pin to go high, indicating the FPGA is ready for more data, before writing the next data byte. The timing diagram Asynchronous Peripheral configuration is shown in Figure 8.

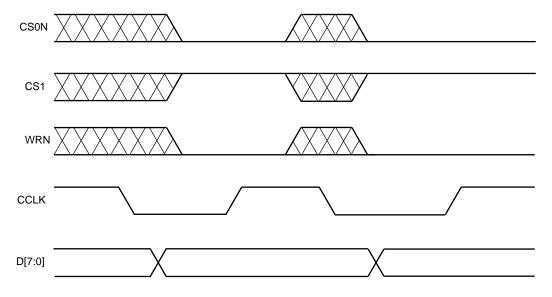

Figure 8. Asynchronous Peripheral Timing Waveform

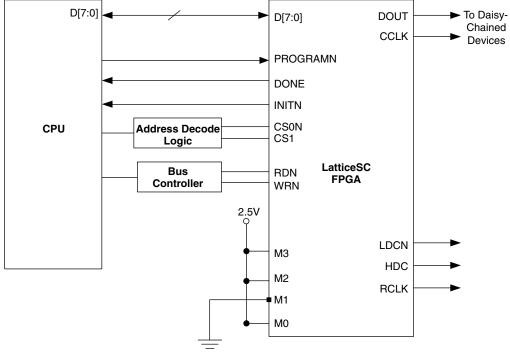

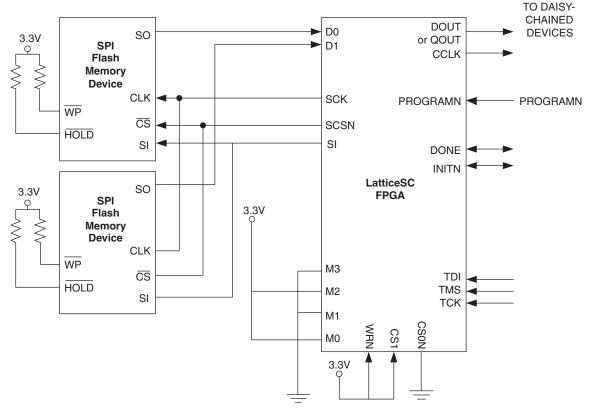

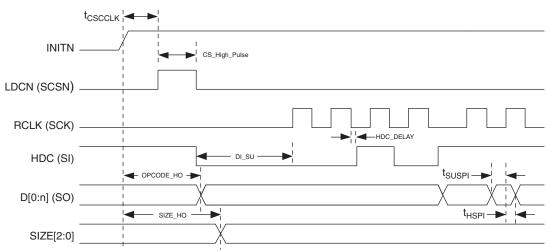

## **Microprocessor Interface Mode**

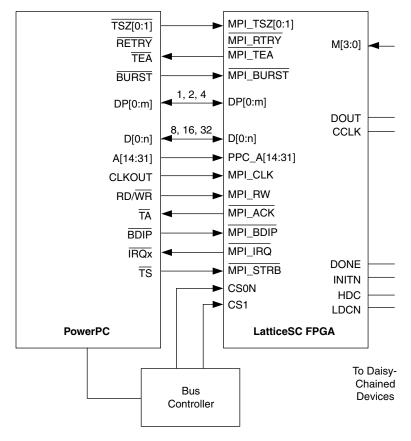

The built-in microprocessor interface is designed for use in configuring the FPGA and runtime access of system registers. The MPI permits glueless interface for FPGA configuration and readback from the PowerPC processor. When enabled by the mode pins, the MPI handles all configuration/readback control and handshaking with the host processor. The MPI transfers are clocked from the microprocessor bus via the FPGA MPI\_CLK input pin. This interface supports 8, 16 and 32-bit transfers.

Figure 9. Microprocessor Interface Configuration Diagram

| Dedicated<br>Microprocessor<br>Interface Pins | I/O | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESETN                                        | ı   | Active low input prior to configuration done, forces the restart of configuration. An internal active pull up is defaulted prior to configuration. This can be deactivated after configuration.                                                                                                                                                                                   |

|                                               |     | Optionally user-programmed to connect to GSR after configuration.                                                                                                                                                                                                                                                                                                                 |

| CCLK                                          | 0   | CCLK is an output which strobes configuration data into daisy-chained devices. CCLK is output for daisy-chaining operation when the lead FPGA is in any of the MPI modes.                                                                                                                                                                                                         |

|                                               |     | As an input, a low level on DONE delays FPGA wake-up after configuration if the appropriate wake-up options are set.                                                                                                                                                                                                                                                              |

| DONE                                          | I/O | As an active-high, open-drain output, a high level on this signal indicates that configuration is complete.                                                                                                                                                                                                                                                                       |

|                                               |     | Optional user programmable 100K internal pull up                                                                                                                                                                                                                                                                                                                                  |

| PROGRAMN                                      | ı   | PROGRAMN is an active-low input that forces the restart of configuration. This pin always has an active pull-up.                                                                                                                                                                                                                                                                  |

|                                               |     | This pin must be held high during device initialization until the INITN pin goes high. This pin always has an active pull-up.                                                                                                                                                                                                                                                     |

| RDCFGN                                        | I   | During configuration, RDCFGN is an active-low input that activates the TSALL function and 3-states all of the I/O. After configuration, it can be selected to activate the TSALL function as described above, or, if read-back is enabled via a bitstream option, a high-to-low transition on it will initiate read-back of the configuration data starting with frame address 0. |

| Dedicated                                           |          |                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|-----------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Microprocessor<br>Interface Pins                    | 1/0      | Description                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| interface Pins                                      | 1/0      | Description                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| INITN                                               | I/O      | INITN is a dedicated bidirectional signal before and during configuration. A pull-up is always enabled, but an external 10K ohm pull-up resistor is recommended. As an active-low opendrain output, INITN is held low during power stabilization and internal clearing of memory. As an active-low input, INITN holds the FPGA in the wait-state before the start of configuration. |  |  |  |

| MPI_IRQ_N                                           | 0        | It is the interrupt pin for MPI to external microprocessor. A programmable pull-up resistor is available on this pin.                                                                                                                                                                                                                                                               |  |  |  |

|                                                     |          | During power-up and initialization, M[3:0] are used to select the configuration mode with their values latched on the rising edge of INITN. After configuration these pins are available as user defined inputs.                                                                                                                                                                    |  |  |  |

| M[3:0]                                              | I        | Mode Pin Setting: 8-bit M[3]=1, M[2]=0, M[1]=1, M[0]=0 16-bit M[3]=1, M[2]=0, M[1]=1, M[0]=1 32-bit M[3]=1, M[2]=1, M[1]=1, M[0]=0                                                                                                                                                                                                                                                  |  |  |  |

| Dual-Purpose Pins:                                  | After co | onfiguration, these pins are user-programmable I/O pins                                                                                                                                                                                                                                                                                                                             |  |  |  |

| DOUT                                                | 0        | During configuration, DOUT is the serial data output that can drive the D0/DIN of daisy-chained slave devices. The data-stream from this output will propagate preamble bits of the bitstream to daisy-chained devices. Data out on DOUT changes on the rising edge of CCLK.                                                                                                        |  |  |  |

| QOUT                                                | 0        | During daisy-chaining configuration, QOUT is the serial data output that can drive the D0/DIN daisy-chained slave devices that do NOT propagate preamble bits. Data out on QOUT chang on the rising edge of CCLK.                                                                                                                                                                   |  |  |  |

| HDC                                                 | 0        | High During Configuration is output high until configuration is complete. It is used as a control output, indicating that configuration is not complete.                                                                                                                                                                                                                            |  |  |  |

| LDCN                                                | 0        | Low During Configuration is output low until configuration is complete. It is used as a control output, indicating that configuration is not complete.                                                                                                                                                                                                                              |  |  |  |

| CS0N<br>CS1                                         | I        | The FPGA is selected when CS0N is low and CS1 is high. During configuration, a pull-up is enabled on both except with MPI DMA access control (see TN1085, <u>LatticeSC MPI/System Bus</u> ).                                                                                                                                                                                        |  |  |  |

| MPI_STRB_N                                          | I        | MPI_STRB_N is MPI TS (transfer start) signal.                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| MPI_RW_N                                            | I        | MPI_RW_N is MPI read (high) / write (low) signal.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| MPI_DATA                                            | I/O      | D[7:0] is also the first byte of MPI data pins.                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| MPI_BURST_N,<br>MPI_BDIP_N,<br>MPI_TSZ,<br>MPI_ADDR | I        | Transfer size = MPI_TSZ Burst mode = MPI_BURST_N Burst in process = MPI_BDIP_N Address MPI_ADDR (connected to FPGA Address pin A[0:17)                                                                                                                                                                                                                                              |  |  |  |

| MPI_TA,<br>MPI_TEA,<br>MPI_RETRY                    | 0        | For MPI configuration modes, these active low signals indicate transfer success (MPI_TA), erro (MPI_TEA) or retry (MPI_RETRY).                                                                                                                                                                                                                                                      |  |  |  |

| MPI_CLK                                             | I        | Input for MPI clock.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

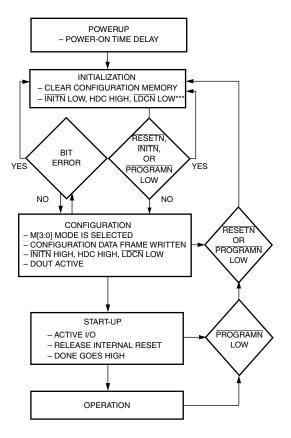

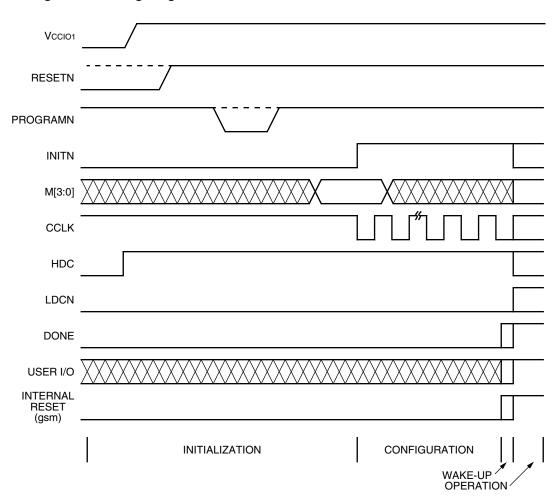

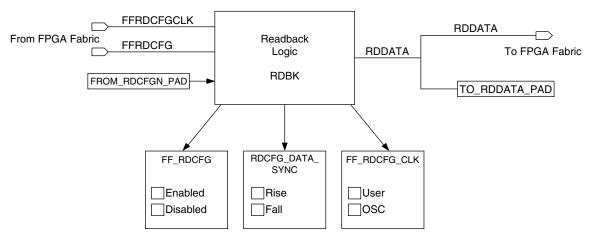

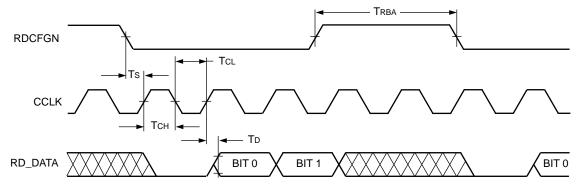

| D[0:#], DP[0:#]                                     | I/O      | MPI data and parity data buses.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |