# 多量生産アプリケーション用 FPGA の最適化

ラティスセミコンダクター ホワイト・ペーパー 2004年6月

ラティスセミコンダクター株式会社

http://www.latticesemi.co.jp

#### 多量生産アプリケーション用 FPGA の最適化

適度の数量を生産する機器は、コア・ネットワークや産業用、そして高性能コンピューティングなどの分野で典型的に見られますが、それらの設計者は、多年にわたり FPGA デバイスの低リスクと短い市場投入までの時間という利点を享受してきました。 民生機器や無線通信装置、ネットワーク・アクセス機器などの多量生産機器の設計は、そのコスト重視性とあいまって、一般的にロジック実装のために ASIC を採用してきました。 しかしながら、短くなる製品のライフ・サイクルと、経済的効果の出る ASIC の最少数量が増大していることが、このアプローチをますます挑戦的にしています。

後者は、マスク・セットがそれぞれの新しい世代の ASIC によって一層高価になる ことと、設計チップが幾何学的に小さくなりかつウェハー・サイズが大きくなるために ウェハー当たりのダイ数が増加するという事実を主にしています。

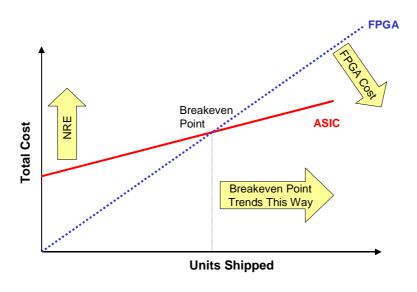

これらの傾向はプログラマブル・ロジック・ソリューションに有利に働いています。 チップが幾何学的により小さくなることと、ウェハーがより大きくなることはプログラ マブル・デバイスのコスト低下につながります。図1で例示されるように、FPGAのデ バイス・コストが改善し、ASICのNRE(Non-Recursive Engineering Charge; いわゆる マスク代などを含む開発費)が増大し続けるにつれ、より多くの多量生産機器の設計は FPGA テクノロジを活用することができます。

図1 - FPGA対 ASIC、損益分岐点

## 最適なプログラマブル・ロジック・ソリューションの達成

多量生産機器の設計への FPGA アーキテクチャの適用性を最大にするために、コスト、機能、および性能を最適化する必要があります。最適化は、この領域の FPGA に必

要な機能を明確に理解することから始まります。従って、アーキテクチャの定義、プロセス・テクノロジの選択から、シリコンの設計に至る開発過程の全ての段階で、こうした理解を中心にしなければなりません。

いくつかのベンダによる初期の試みは、必要とされる最適化を達成しませんでした。 1つのアプローチは、パッド・リングを定義して、次にロジックで埋戻し(backfill)を することです。低コストを達成する一方で、このアプローチは、正しい機能の組み合わ せが設計者に届けられるのを保証する訳ではありません。別のアプローチは、高性能な アーキテクチャから始めて、次に機能を取り除くものです。残念ながら、このアプロー チは多量生産マーケット向け機器の設計者によって要求されるコスト節減をもたらし ていません。

多量生産用 FPGA の設計に極めて重要な、最適化のもう一つの機会は、システム・コストの総合的な最適化です。低価格のコンフィグレーション・メモリの入手性、また DDR メモリや LVDS を採用するデバイスなど一般的な部品とのインターフェイスを簡素化する機能は、総合的な機器コストにすべて影響を与えます。

次にこのホワイト・ペーパーでは、ロジック・ブロック、入出力サポート、外部メモリ・インターフェイス、およびコンフィグレーション・メモリ・サポートという点から、FPGA アーキテクチャの最適化に影響を与える特定の要素を調べます。また、ECP(EConomy Plus)と EC(EConomy)デバイス・ファミリについて、ラティス・セミコンダクターがアーキテクチャを決定する元となった要素などを詳しく述べます。本ホワイト・ペーパーはLatticeECP/ECアーキテクチャの概観で締めくくります。

### <u> 論理ブロックと配線</u>

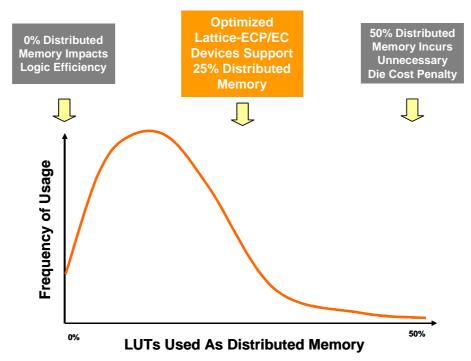

論理ブロックとそれに関連する配線はダイサイズに最も大きく影響を与えるため、デバイスを最適化する際にとても重要です。ルックアップ・テーブル(LUT)ベースのアーキテクチャに関して、最適化のために極めて重要な1つの要素は分散メモリのサポート、すなわちLUTを小さなメモリとして用いることができる機能です。これは、本機能のサポートで最大20%論理ブロック・サイズを増加させるからです。設計者との面談でわかったのは、ほとんどの設計者が、スクラッチ・パッド・メモリとレジスタ・ファイルの効率的な実装ができる少量の分散メモリがあるのを好むということです。しかしながら、ほんのわずかな設計事例は、少なからぬ割合以上のLUTがこの機能をサポートすることを必要としました。これは図2で概念的に示されています。

コストを制御しながらも分散メモリに関する要望を最良に満たすために、ラティスは ECP/EC デバイスの論理ブロックの 25%で分散メモリをサポートすることを選びました。これは多量生産アプリケーションのために意図される他のアーキテクチャとは対照的で大きく違います。それらは、分散メモリがないことで、小さなメモリを構築するた

めに設計者が多くのLUTを用いざるを得ないか、或いは50%の分散メモリが提供されることで、設計者は用いられそうにない機能のために追加オーバーヘッドを支払う必要が

あることになります。

図2 多量生産機器用デザインのための分散メモリ要件

アーキテクチャが含む配線の量は顕著な影響をコスト、性能、およびデバイスの有用性に与えます。プロセス・テクノロジの選択は、コスト、性能、および有用性という変数のバランスをとるのに強い影響があります。LatticeECP/ECデバイスのために、ラティスは、富士通の9メタル配線層を持つ130nmの低誘電体プロセスを用いる事を選びました。多層の高性能メタル配線層があることは、コスト効率がよい配線ファブリックを築き上げる素晴らしい基礎を提供しました。このプロセスを活用して、性能とコストのバランスをとりながらも、優れた配線性を提供するx1、x2、およびx6配線リソースの組み合わせが開発されました。配線は一貫して高速性を保つため完全にバッファリングされ、負荷に依存しません。

### 入出力標準のサポート

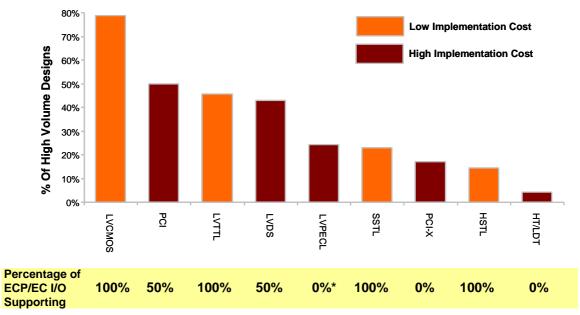

入出力バッファと、これに関連するインタフェース・ロジックは、(論理ブロック と配線の組み合わせの次に)ダイサイズに大きい影響を与えるため、この領域もアーキ テクチャの最適化の際、慎重な調査に値します。デバイスによってサポートされる入出 力標準は、I/O 領域のコストの第一の要因です。さまざまな入出力標準があり、それぞれ良く採用されています。ラティス・セミコンダクターの調査に基づいて、図 3 は 9 つの一般的な入出力標準の採用度合いを示しますが、同時にそれぞれの入出力タイプを実装する相対コストを高いか安いかを色分けして分類しています。

これらの入力に基づいて、ラティスは Lattice ECP/EC デバイスの I/0 サポート方針を決定しました。最もポピュラーな I/0 (LVCMOS、PCI、LVTTL、および LVDS) は Lattice ECP/EC デバイスで実装されました。しかしながら、ポピュラーな入出力タイプのうち高い実装コストとなるもの (PCI と LVDS) は、デバイスの半分のみに実装しました。これはシステム設計者がこれら標準のサポートを必要としたのは、一般的に限定された数の I/0 であったことによります。採用度の低い入出力標準 (LVPECL、SSTL、PCI-X、HSTL、および HT/LDT) は、それらがコストを大幅に増加しない場合だけ実装されました (SSTL と HSTL)。また、デバイスは外部抵抗を加えることで LVPECL をエミュレートすることができます。

\* Can be supported through emulation

図3 多量生産機器用デザインのための入出力標準サポート要件

他の低コスト・デバイスは、著しい場合は(真の)LVDSをサポートしないなど、最もポピュラーな標準すべてをオンチップでサポートしているとは限らないか、または入出力標準を過剰に実装して不必要に I/O コストを押し上げています。

#### 外部メモリ・インターフェイス・サポート

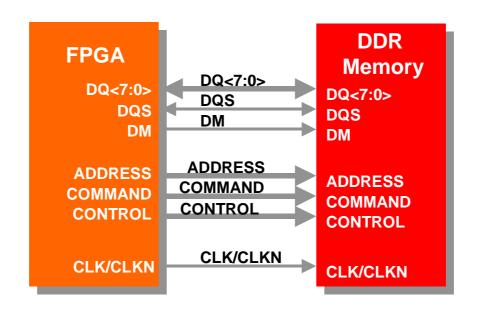

コスト重視の機器の設計者はそれらの技術的要求事項を考えて、当然1ビットあたりの最も低いコストを提供するメモリ・テクノロジを選択します。これまで、これはシンクロナス DRAM(SDRAM)をしばしば意味しました。しかしながらここ数年間で、Double Data Rate (DDR) DRAM の数量出荷は拡大しており、2004年には出荷された総ビット数の50%以上を示しています。いよいよ設計者は DDR DRAM が SDRAM より安いビットあたりのコストを提供する事に気が付いてきました。

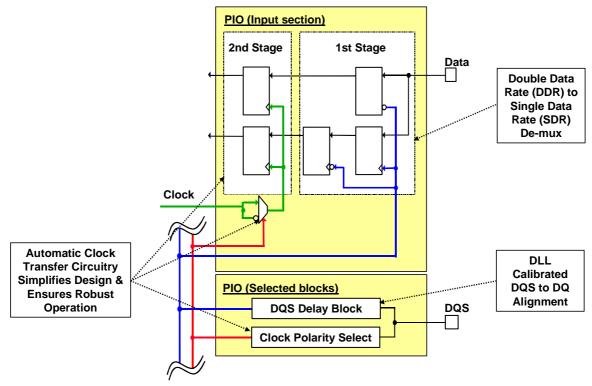

このように、多くの場合 DDR DRAM はより安価ですが、インターフェイスするには SDRAM よりかなり困難です。設計のチャレンジには、データ・ストローブ (DQS) 信号に データ (DQ) 位相を合わせること、クロックの両エッジで遷移するデータ・ストリームを クロックの片エッジで遷移する二系統に分けること、そして DQS クロック・ドメインか らシステム・クロック・ドメインにデータ転送を管理することを含んでいます。 DQS 信号が双方向という性質は、DQ と DQS のアライメント (位相合わせ) を一層挑戦的にします。図 4 は典型的な DDR メモリ・インターフェイスを示します。

図4 典型的な FPGA と DDR メモリのインターフェイス

従来の FPGA ロジックに DDR インターフェイスを実装するのは、特に性能が上がるとともに挑戦的となり、また多くのリソースを消費します。LatticeECP/EC デバイスは、DQ と DQS 信号の位相を合わせ、ダブル・データ・レートとのデータ多重化をし、DQS クロック・ドメインからシステム・クロック・ドメイン間のデータ転送するための、専用のリソースを持っています。図 5 は LatticeECP/EC デバイスにある DDR サポート・リソースのいくつかを示します。そのインパクトは劇的である場合があります。64 ビット幅のメモリ・インターフェイスを実装する場合、専用の DDR サポート・リソースによって、LatticeECP/EC デバイスは 500~1000 個のレジスタを節約します。これはファミ

リ内最小デバイスにある 1.5K の汎用レジスタを考慮した場合、かなりの部分に相当します。また、性能は他の低コスト FPGA に対して 25%向上しますので、仕様に対してよ

り多くのマージンをもって、あるいはより遅い速度グレードのデバイスを使用しながら も、高速動作することが可能になります。

図 5 LatticeECP/EC DDR 入力サポート回路

#### コンフィグレーション・メモリのコスト

ほとんどのFPGAがそれらのコンフィグレーション・データを保持するのにSRAMセルを利用します。従って、データはパワーアップ時に再ロードされる必要があります。伝統的に、これはFPGAサプライヤから調達された独自のコンフィグレーション格納用PROMの使用で達成されてきました。これらのメモリは、FPGA価格の3分の1まで及ぶなど、比較的高価である傾向がありました。総合的なコストを下げるために、多くの設計者は、プログラムの格納に用いられるはるかに安いフラッシュ・メモリにこのコンフィグレーション・データを一緒に格納して、マイクロプロセッサでFPGAをコンフィグレーションします。コストを削減する一方、このアプローチは2つの顕著な問題を引き起こします。マイクロプロセッサ・サポート・ロジックとしてFPGAを用いることができないので、しばしば第二の小さなプログラマブル・デバイスがボードに必要になり、コストの増大と部品点数の増加をもたらします。またマイクロプロセッサのプログラム

用メモリに FPGA のコンフィギュレーション・データを含めることによって、ハードウェアの構成とソフトウェアはからみ合うようになります。いくつかの場合、ハードウェアのマイナーチェンジを実施するために、ソフトウェア・リリースを必要とすることになります。

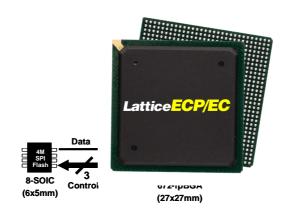

ここ数年間にわたって、複数のサプライヤがシリアル・ペリフェラル・インターフェイス (SPI) 標準を利用する小さい実装面積のフラッシュ・メモリを開発しています。サプライヤ間の活発な競争によって、FPGA メーカーによって供給された独自のブートメモリに比べ、これらの部品はビット当たり最大 4 分の 1 の価格で、妥当なレベルを保っています。システム・コスト全体を最適化するため、ラティス・セミコンダクターは、さまざまなパラレル、シリアル、および JTAG ベースのモードに加えて、直接 SPI メモリ (図 6) からコンフィグレーションをサポートするように、LatticeECP/EC デバイスのアーキテクチャを決定しました。

図 6 LatticeECP/EC の SPI フラッシュ・インターフェイス

### アーキテクチャの記述

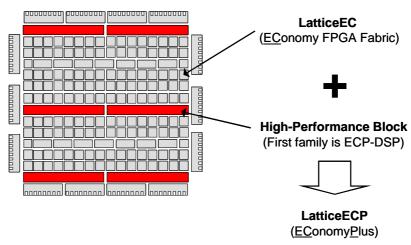

LatticeECP<sup>™</sup> の概念は最適化された FPGA ファブリックを高速の専用機能と組み合わせたものです。このアプローチを実装する最初のラティス・ファミリは ECP-DSP (EConomy Plus Digital Signal Processing)で、これは高性能なオンチップ DSP ブロックを提供します。より低いコストを達成するために、LatticeEC<sup>™</sup> ファミリは専用機能ブロックを除いた LatticeECP<sup>™</sup>デバイスの汎用機能のすべてをサポートします。図 7 は LatticeECP<sup>™</sup>の概念について図示します。

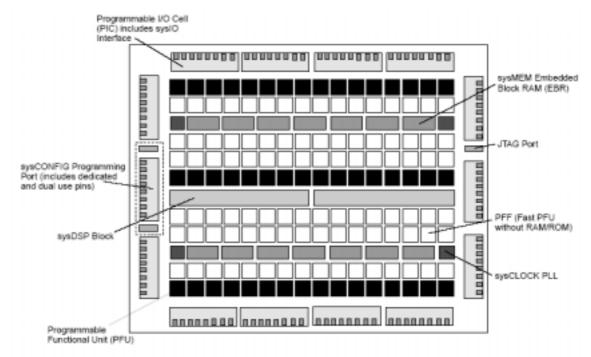

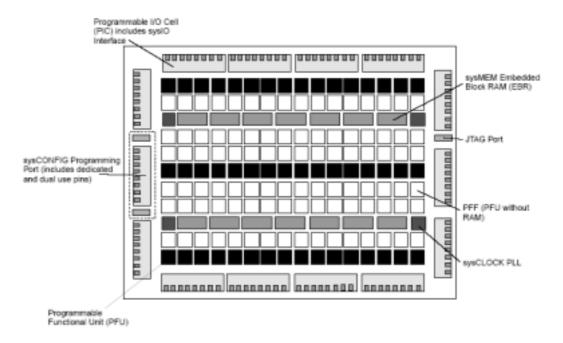

LatticeECP-DSP と EC デバイスはプログラマブル I/0 セル (PIC) によって囲まれた論理ブロックのアレイを含んでいます。論理ブロックの列の間に点在するのは、 $sysMEM^{TM}$  組み込みブロック RAM(EBR) の列です。LatticeECP-DSP は  $sysDSP^{TM}$  ブロックの列をサポートし、最大毎秒 10 ギガ積和演算 (10GMAC/s) の高性能 DSP 機能を効率的に実装できま

す(注 1)。DSP に機能を実装しないユーザがコストを一層低減できるように、LatticeEC<sup>™</sup> デバイスでは sysDSP<sup>™</sup>能力を取り除いています。図 8 と図 9 は LatticeECP-DSP と EC デバイスのブロック図です。

図7 LatticeECP™の概念

内部には2種類の論理ブロックがあり、それらはプログラマブル・ファンクション・ユニット (PFU)、およびプログラマブル・ファンクション・ユニット (PFF)です。PFU はロジック、演算、RAM、ROM、およびレジスタ機能のためのブロックを含みます。PFF ブロックはロジック、演算、および ROM 機能のためのブロックを含みます。複雑なデザインが速やかにかつ効率的に実装できるように、PFU と PFF ブロックは共に柔軟性のために最適化されています。論理ブロックは2次元配列でアレンジされています。1つのタイプのブロックだけが列単位で用いられます。PFU ブロックは外側の列で用いられます。コアの残りは PFU ブロックの列が点在する PFF ブロックの列から成ります。PFF ブロック3列ごとに、PFU ブロック 1列があります。

各 PIC ブロックは、それぞれの  $sysI0^{TM}$  インターフェイスで 2 つの PIO (PIO ペア) を 取り囲みます。すべての PIO は、LVDS、BLVDS、および LVPECL 用の差動レシーバと共に、 LVTTL、LVCMOS、HSTL、および SSTL 入出力をサポートします。デバイスの左右の I/O バンクにある PIO ペアは、LVDS ドライバーとして構成することができます。また、デバイスの上下 I/O バンクにある PIO ペアは、オプションとして PCI クランプ・ダイオードを提供します。また、PIO は高性能 DDR メモリ・インターフェイスの実装を簡素化するさまざまな回路を含んでいます。

sysMEM™ EBR は大サイズ、専用、かつ高速のメモリブロックです。それは 9K ビットのメモリで、デュアル・ポート、擬似デュアル・ポート、シングル・ポートまたは ROM として構成することができます。また、ユーザはデザイン内で FIFO として指定することができ、開発ツールが EBR と少量の PFU ロジックによって FIFO を構築します。メモ

リ・データ幅は1ビットから36ビットまでで、プログラマブルです。

PFU、PFF、PIC、および EBR ブロックは、図 8 と 9 で示されるように二次元グリッドに列とコラムで配置されます。ブロックは多くの縦方向と横方向の配線チャネルリソースに接続されます。配置配線ソフトウェア・ツールは自動的にこれらの配線リソースを割り当てます。

図 8 LatticeECP-DSP ブロック図

図9 LatticeEC™ブロック図

sysMEM<sup>™</sup>ブロックを含む列の終わりに、sysCLOCK<sup>™</sup>位相ロック・ループ (PLL) ブロックがあります。これらの PLL にはてい倍、分周、および位相シフトの能力があり、クロックの位相関係を管理するのに用いられます。LatticeECP/EC アーキテクチャは 1 デバイスあたり最大 4 個の PLL を提供します。

ファミリの全デバイスには、JTAG ポートがあります。内部をモニタするロジック・アナライザ機能 (ispTRACY™) のモジュールを設計に組み込めるように用意していますが、インターフェイスにはこの JTAG を用います。sysCONFIG™ポートは、シリアルあるいはパラレルのデバイス・コンフィグレーションが可能で、低コストの業界基準シリアル・ペリフェラル・インターフェイス (SPI) メモリのサポートも含んでいます。LatticeECP/EC デバイスはコア電圧として 1.2V を用います。表 1 は ECP-DSP/EC ファミリに関するロジック規模、入出力、および他のリソース情報を示します。

| デバイス                                   | EC1 | EC3 | EC6  | EC10  | EC15  | EC20  | EC40  |

|----------------------------------------|-----|-----|------|-------|-------|-------|-------|

|                                        |     |     | ECP6 | ECP10 | ECP15 | ECP20 | ECP40 |

| LUTs (K)                               | 1.5 | 3.1 | 6.1  | 10.2  | 15.4  | 19.7  | 41.0  |

| sysMEM <sup>TM</sup> ブロック              | 2   | 6   | 10   | 30    | 38    | 46    | 70    |

| sysMEM <sup>TM</sup> (Kbits)           | 18  | 55  | 92   | 276   | 350   | 424   | 645   |

| 分散 RAM (Kbits)                         | 6   | 12  | 25   | 41    | 61    | 79    | 164   |

| 電源電圧 (V)                               | 1.2 | 1.2 | 1.2  | 1.2   | 1.2   | 1.2   | 1.2   |

| sysDSP <sup>TM</sup> ブロック <sup>1</sup> |     |     | 4    | 5     | 6     | 7     | 10    |

| 18x18 乗算器 <sup>1</sup>                 |     |     | 16   | 20    | 24    | 28    | 40    |

| PLL                                    | 2   | 2   | 2    | 4     | 4     | 4     | 4     |

| 最大 I/O                                 | 112 | 160 | 224  | 288   | 352   | 400   | 576   |

表1 ECP-DSPとECファミリのメンバー

#### まとめ

ASIC アプローチがより挑戦的になり、FPGA の費用効果が向上しているため、FPGA を利用することは多量生産機器の設計には、より魅力的になっています。この傾向を加速するには、FPGA がこれら設計者の要件を的確に捕らえている必要があります。アーキテクチャ最適化のあらゆる局面が重要ですが、論理ブロック、入出力、外部メモリ・インターフェイス、およびコンフィグレーション・サポートは最も重要な領域の代表的なものです。LatticeECP/EC デバイスは、魅力的な価格で多量生産機器の設計に必要とされる機能ミックスを適確に提供するために、これら種々領域で慎重に最適化されまし

<sup>1.</sup> ECP-DSP デバイス.

た。

#### ###

(注1) このブロックに関する詳細については、ラティスのホワイト・ペーパー、「最適化された低コストFPGAアーキテクチャ内の高性能DSPの能力」を参照してください。