# 業界基準 SPI シリアル・フラッシュによる低価格 FPGA のコンフィグレーションと LatticeECP/EC FPGA

ラティスセミコンダクター ホワイト・ペーパー 2004年6月

ラティスセミコンダクター株式会社

http://www.latticesemi.co.jp

Preliminary Only

## はじめに

FPGA ファミリとサプライヤの選択をする前にシステム設計者が評価しなければならない多くの基準があります。その1つは FPGA「起動(ブートアップ)」コンフィグレーション手法です。システム設計が不揮発性を必要とするなら、ラティス ispXPGA®などの不揮発性 FPGA が選択されるでしょう。ispXPGA®ファミリはシングルチップで自動的にブートする FPGA ソリューションを提供します。しかしながら、システム設計の要求が揮発性 FPGA によって最も良く満たされる場合、設計者はその FPGA がシステム起動時にどう構成(コンフィグレーション)されるかも立案しなければなりません。

システム設計としてボード上のマイクロコントローラと利用可能なシステム・メモリにアクセスでき、かつ設計者が適切に FPGA を構成するためのソフトウェアを書いても構わないのであれば、全 FPGA ソリューションでのコンフィグレーション・コストの増加はわずかです。しかしながら、多くのシステム設計において、システム・パワーアップする毎に FPGA を構成するための、専用「ブート」メモリが用いられます。この状況の不幸な経済的な現実は、伝統的に FPGA ベンダ独自のブートメモリが総 FPGA ソリューション・コスト (FPGA+ブートメモリ)の最大 30%を占めるということです。

ラティスは、LatticeECP™ (低価格で高性能な専用機能がある)と LatticeEC™ (低価格用に最適化された)ファミリの新しい FPGA で、この多大な費用の問題に取り組みました。低価格で、業界基準、サード・パーティの SPI(シリアル・ペリフェラル・インターフェイス)フラッシュ・メモリから直接、ECP と EC ファミリの両方を構成することができます。

# SPI インターフェイスとは?

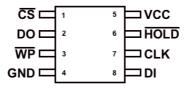

SPI インターフェイスは以下の信号から成る 4 線シリアル・インターフェイスです。

1. CS; チップ・セレクト

デバイス動作をイネーブルし、ディセーブルします。ディセーブルされると、デバイスはスタンバイ電力レベルになります。イネーブルされると、デバイスはパワーアップし、命令の書き込み、データの読み出しができます。

- 2. CLK; シリアルのクロック シリアル入力・出力動作のタイミングを提供します。

- 3. DI; シリアル・データ入力 デバイスがイネーブルされている時、命令、アドレス、およびデータがシリアル でデバイスに書き込まれるのを許可します。データはシリアル・クロックの立ち 上がりエッジでラッチされます。

- 4. DO; シリアル・データ出力

デバイスがイネーブルされていると、データとステータスがデバイスからシリアルに読み出されるのを許可します。データはシリアル・クロックの立ち下がりエッジでシフトアウトされます。

Vcc とグランド(GND) ピンに加えて、SPI インターフェイスは以下の 2 つの機能をサポートします:

#### 1. HOLD

アクティブに選択されている間、デバイスをポーズします。複数のデバイスが同じ SPI 信号を共有しているとき、この機能は有用です。

2. WP;ライト・プロテクト

ステータス・レジスタの Block Protect ビットに不注意な書き込みを防ぐのに使用されます。

ほとんどの標準8ピンSPIフラッシュ・メモリのピン配置を以下に示します。

# SPI フラッシュ対従来のブートメモリ

SPI フラッシュ・メモリで FPGA を構成する能力は、今日のブートメモリ・オプションよりも顕著な利点を提供します。

\*SPI フラッシュ用の広いサード・パーティ・ベンダ

ベンダ間の競争は価格の低減と、より短期間での入手性を促進する

\*低い部品コスト

「Total FPGA」コストのコンフィグレーション・メモリ部分を減少させる

\*より小さいパッケージと PCB 実装面積

8ピン対(ブートメモリの)20、44、或いは48ピン・パッケージ

\*より広いメモリ・サイズ品の入手性

SPI フラッシュは 32M と 64M が今日入手できる

\*メモリ・サイズのマイグレーション対応性が優れている

SPI フラッシュは全て同じ8ピンのパッケージで入手できる

# SPI フラッシュの広範なサード・パーティ・ベンダ

SPI フラッシュ・メモリは市場においては比較的新しく、ほとんどのベンダが、2003年の後半に SPI フラッシュ製品ラインを投入しました。既に市場には多くの SPI フラッシュ・サプライヤがありますが、さらに幾らかのメモリ・サプライヤが今後数四半期の間にこの人気のあるマーケット・セグメントに参入すると予想されています。一般に、512Kから 16Mのメモリ・サイズは複数のベンダから入手可能で、そのほとんどが 32Mと 64Mのオプションを今後数四半期内に提供する計画を発表しています。現在の SPI フラッシュ・メモリ・サプライヤ、およびそれらのいくつかの製品が以下に記載されています。

| ベンダ                                 | ファミリ      | 512K | 1M | 2M | 4M | 8M | 16M | 32M | 64M |

|-------------------------------------|-----------|------|----|----|----|----|-----|-----|-----|

| STMicroelctronics                   | M25Pxx    | Х    | Х  | Χ  | Х  | Х  | Х   | Р   | Р   |

| NexFLASH                            | NX25Pxx   |      | Х  | Х  | Х  | Р  | Р   | Р   | Р   |

| Silicon Storage<br>Technology (SST) | SST25VFxx | Х    | X  | Х  | Х  | X  | Х   |     |     |

| Saifun                              | SA25Fxx   | Х    | Х  | Х  | Р  | Р  | Р   | Р   | Р   |

| Atmel                               | AT45DBxx  |      | Х  | Х  | Х  | Х  | Х   | Х   | Х   |

X=現時点で入手可能; P=計画中(2004年6月の時点でベンダのウェブサイトに基づいた入手情報)

| ベンダ    | ファミリ                            | 機能                                            | 512K | 1M | 2M | 4M | 8M | 16M | 32M | 64M |

|--------|---------------------------------|-----------------------------------------------|------|----|----|----|----|-----|-----|-----|

| Atmel  | AT17LVxx                        | EEProm                                        | Х    | Χ  | Х  | Х  |    | Р   |     |     |

|        | Legacy<br>XC17Vxx               | One-Time<br>Programmable                      |      | Х  | Х  | Х  | Х  | Х   |     |     |

| Xilinx | Legacy<br>XC18Vxx               | Flash                                         |      | Х  | Х  | Х  |    |     |     |     |

|        | Platform Flash<br>XCFxx         | Flash                                         |      | Х  | Х  | Х  | Р  | Р   |     |     |

|        | Config. Devices<br>EPCxx        | One-Time<br>Programmable                      | х    | Х  | Х  |    |    |     |     |     |

| Altera | Enhanced Config. Devices EPCxx  | 2-Chip "Stacked" Package:<br>Flash+Controller |      |    |    | Х  | Х  | Х   |     |     |

|        | Serial Config. Devices<br>EPCSx | Serial Flash                                  |      | Х  |    | Х  |    | Р   |     | Р   |

X=現時点で入手可能; P=計画中(2004年6月の時点でベンダのウェブサイトに基づいた入手情報)

ブートメモリ・サプライヤは数がさらに制限されます。Xilinx 社と Altera 社はそれぞれの FPGA 製品ファミリを対象とした、さまざまなブートメモリ・オプションを提供しています。Atmel 社からは「FPGA コンフィグレーション EE メモリ」デバイスを 2 バージョンで入手可能で、それらは Altera 社と互換性があるもの、および Xilinx 社と互換性があるものです。しかしながら、Atmel 社は現在、4M しかメモリ・サイズをサポートしていません。より大きいメモリ・サイズが必要な場合、設計者は Xilinx 社からのワンタイム・プログラム品のソリューションか、Altera 社からの高価で、2 チップで、そして、スタックト・パッケージ・ソリューションのどちらかを用いなければなりません。

# より安い部品コスト

複数のサプライヤからコモディティとして提供されるチップによりドライブされている、SPI フラッシュ・メモリ市場はかなり競争が激しいので、Atmel 社、Xilinx 社、および Altera 社からの標準品でない、独自のブートメモリよりも、SPI フラッシュ・メモリが積極的に値付けさられるのは驚くべきことではありません。

SPI フラッシュの価格利点を定量化するために、SPI フラッシュ・ベンダとブートメモリ・ベンダのディストリビュータ・ウェブサイトで公にされている価格設定(少量時)で比較をしました(2004年6月1日現在)。それぞれのメモリ・サイズ・レベルで、SPI フラッシュ・ベンダの最低価格が、いずれかのブートメモリ・ベンダの最低価格と比較されました。この価格設定の絶対値が殆どのユーザが支払うだろうより高いのは確かですが、より多量調達時の価格設定では、相対的な価格はおそらく実際に当てはまるでしょう。

| .) w 11    | 公表されている最低価格 |         |    |       |         |  |  |  |  |  |

|------------|-------------|---------|----|-------|---------|--|--|--|--|--|

| メモリ        |             | (全ベンダ中) |    |       |         |  |  |  |  |  |

| サイズ        | 5           | SPI     | フ  | ート    | SPI との差 |  |  |  |  |  |

|            | フラ          | ッシュ     | Р  | ROM   | (%)     |  |  |  |  |  |

| 512K       | \$          | 1.10    | \$ | 3.50  | 69%     |  |  |  |  |  |

| 1 <b>M</b> | \$          | 1.25    | \$ | 3.30  | 62%     |  |  |  |  |  |

| 2M         | \$          | 1.70    | \$ | 5.70  | 70%     |  |  |  |  |  |

| 4M         | \$          | 2.15    | \$ | 8.40  | 74%     |  |  |  |  |  |

| 8M         | \$          | 3.00    | \$ | 15.85 | 81%     |  |  |  |  |  |

| 16M        | \$          | 6.70    | \$ | 20.95 | 68%     |  |  |  |  |  |

|            |             |         | 7  | 平均:   | 71%     |  |  |  |  |  |

従来のブートメモリに対して、業界基準、サード・パーティの SPI フラッシュ・メモリを用いることによって平均 71%のコスト節約できることを示しています。言い換えれば、SPI フラッシュ・メモリ価格が同等サイズのブートメモリの 29%にすぎないということになります。

SPI フラッシュのコスト優位性を見る別の方法は、従来のブートメモリが FPGA/ブートメモリ・サイズによって「総 FPGA ソリューション・コスト」の 5%から 30%を占めているのを理解することです。より小さサイズでは、ブートメモリは全 FPGA ソリューション・コストのより顕著な割合を占めます。SPI フラッシュでは、その割合は 1%以下ないしは 10%以下の範囲に下がります。以下の表は、Xilinx 社の Spartan III と関連する「プラットホーム・フラッシュ」ブート PROM の 100 個以上オーダ時のユニット単価を示します。

| FPGA+ ブ   | ートメモリ             | 100+ ユニ   | ット価格              | トータル     | PROM の |  |

|-----------|-------------------|-----------|-------------------|----------|--------|--|

| Spartan-3 | Platform<br>Flash | Spartan-3 | Platform<br>Flash | コスト      | 占める%   |  |

| XC3S50    | XCF01S            | \$8.15    | \$3.30            | \$11.45  | 29%    |  |

| XC3S200   | XCF01S            | \$14.35   | \$3.30            | \$17.65  | 19%    |  |

| XC3S400   | XCF02S            | \$25.15   | \$5.70            | \$30.85  | 18%    |  |

| XC3S1000  | XCF04S            | \$55.60   | \$8.40            | \$64.00  | 13%    |  |

| XC3S1500  | XCF08S            | \$98.25   | \$15.85           | \$114.10 | 14%    |  |

| XC3S2000  | XCF08S            | \$176.50  | \$15.85           | \$192.35 | 8%     |  |

| XC3S4000  | XCF16S            | \$324.35  | \$20.95           | \$345.30 | 6%     |  |

| XC3S5000  | XCF16S            | \$409.55  | \$20.95           | \$430.50 | 5%     |  |

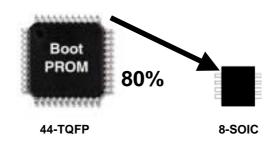

# より小さいパッケージ/PCB 実装面積

SPI フラッシュ・メモリを用いる主要な利点の1つは、すべてのメモリ・サイズ・オプションが8ピンMLP(マイクロ・リードフレーム・パッケージ)で入手可能であるということです。このパッケージは6x5mmのボディーサイズと小さいPCB実装面積を特徴とします。16Mのサイズ以下では、SPI フラッシュ・メモリはより低価格で従来の8ピンSOICパッケージでも入手できます。このパッケージは、端子を含めてMLPと同じPCB実装面積(6x5mm)です。

他方ブートメモリは、あるメモリ・サイズをとると、ベンダによって異なるさまざまなパッケージ・スタイルで出ています。共通パッケージは、メモリ・サイズで異なっており、以下を含んでいます:

- ▶ 8ピンの DIP

- ➤ 20ピンのPLCC、SOIC、およびTSSOP

- ▶ 32 ピンの TQFP

- ➤ 44 ピンの TQFP と PLCC

- ➤ 48 ピンの TSOP

- ➤ 48 ボールの csBGA

- > 88 ボールの BGA

- ➤ 100 ピンの PQFP

SPI フラッシュ・メモリの使用に関連する顕著なボード面積節減について、例として 4M、8M、或いは 16M のメモリを必要とする FPGA をコンフィグレーションするケースを考えてください。44 ピンの TQFP パッケージは PCB 領域の 144mm2 (12x12mm) を必要としますが、これに比べて SPI フラッシュ・パッケージは 30mm2 (6x5mm) になります。SPI フラッシュは同等なブートメモリより約 80%も小さく済みます。

注: すべての寸法はパッケージ端子を含んでいます。サイズは実寸ではありませんが、等倍率です。

#### より広いメモリ・サイズが入手可能

ベンダ/メモリ・サイズ製品の提供を示した 4 ページの表から、SPI フラッシュ・メモリが広く 512K からに 16M のレベルで複数の業者から入手できるのがわかります。32Mと 64M のメモリは、4 つの異なるベンダにより今日入手できるか、あるいは現在計画されています。

従来のブートメモリでは、Atmel 社(唯一の独立サプライヤ)が最大 4M(16M のデバイスも計画されている)をサポートします。Xilinx 社は、最大 16M までの古い、ワンタイム・プログラム品をサポートし、Altera 社は高価で、デュアル・スタックのチップ・ソリューションを最大 16M までサポートします。これらのベンダのいづれも 32M をサポートする計画はなく、Xilinx 社だけが 2個の FPGA 製品ファミリだけをサポートする 64M デバイスの計画を発表しました。

コンフィグレーション・メモリ・サイズの完全なポートフォリオを望む設計者は、 確実に SPI フラッシュ・メモリ・アプローチを好むでしょう。

# 優れたメモリ・サイズのマイグレーション性

SPI フラッシュ・メモリ・アプローチの別の主要な利点は「メモリ・サイズのマイグレーション性」です。SPI フラッシュでは、512Kから 64Mの任意なメモリ・サイズが、同一8ピン MLPパッケージで入手できます。設計者は、異なったメモリ・サイズのためにボードを変更しなければいけないという心配なしに、このただ一種類のパッケージ実装だけ考慮してプロトタイプ・ボードをレイアウトできます。

この機能は LatticeECP/EC FPGA ファミリには特に役に立ちます。というのは共にコンフィグレーション・データ・ストリームのデータ圧縮をサポートするためです。まず設計者は、メモリ・サイズの大きい SPI フラッシュを用いてシステム・デバッグを完了します。次にデザインが完成して、最終的な圧縮データ・ストリームのファイル・サイズが確定した後の量産用ビルドでは、設計者はダウンサイジングしたコンフィグレーション・メモリにストアすることが可能になります。PCB は何ら触る必要がありません。

# LatticeECP/EC 製品とコンフィグレーション概要

## <u>LatticeECP/EC</u> 概要

LatticeECP-DSP ファミリは効率的な FPGA ファブリックに結びつけられた高度な DSP ブロックを提供します。これによって、より高い DSP 性能と改良されたロジック使 用効率をもたらします。さらに低コスト・ソリューションのために、LatticeECTM ファミリは専用の DSP リソースを除いた LatticeECP-DSP ファミリのすべての機能をサポートします。

LatticeECP/ECファミリはともに、入出力性能、分散メモリ、組み込みメモリ(EBR)、ロジック、および配線が多量生産機器マーケットに最適化されたシリコン効率の良い FPGAファブリックを活用しています。

費用対効果に優れた DSP 機能の必要なアプリケーションでの使用に、LatticeECP-DSP は理想的です。そのようなアプリケーションにはソフトウェア無線機、無線通信、軍事用途、およびビデオ処理装置などが含まれます。LatticeEC™ デバイスは、低コスト・ネットワーク、ブレード・サーバ、ネットワーク・アクセス機器、家電、産業、医療、そして自動車などのアプリケーションの、一般的な非 DSP 用途に理想的です。

#### 主要な特色と利点

- ▶ 低コスト FPGA

- o 主流のアプリケーションのために最適化された機能

- o バランスのとれているロジック/メモリ/ I/0 リソース

- ▶ 高性能 sysDSP™ブロック (LatticeECP-DSP)

- o 乗算、アキュミュレート、加算と減算

- o 入力、中間、および出力パイプライン・レジスタ

- o 1 デバイスあたり 4~10 個の sysDSP™ブロック

- ・各ブロックは複数の 9×9、18×18 または 36×36 乗算器をサポート

- ▶ 大きなロジック規模とパッケージ・オプション

- o 1.5K から 41K の LUT4、67~576 I/0

- o ロジック規模のマイグレーションをサポート

- o パッケージ・オプションは TQFP、PQFP、および fpBGA

- ▶ 組み込みメモリと分散メモリ

- o 645k ビットから 18k ビットの sysMEM™ を組み込み

- o ブロック RAM(EBR)

- o 164k ビットまでの分散 RAM

- ▶ フレキシブルな入出力バッファ

- o ホット・ソケッティング(活線挿抜)

- o プログラマブル sysI0™バッファは広範囲のインターフェイスをサポート

- > LVCMOS3. 3/2. 5/1. 8/1. 5/1. 2

- > LVTTL

- ➤ SSTL3/2 クラス I、II、SSTL18 クラス I

- ▶ HSTL18 クラス I、II、III、HSTL15 クラス I、III

- ➤ PCI

- ▶ LVDS、バス-LVDS、LVPECL、RSDS

- ▶ 専用の DDR メモリ・サポート

- o インターフェイスは DDR333 まで実装(166MHz)

- ➤ sysCLOCK<sup>TM</sup> PLL

- o 1 デバイスあたり最大 4 個のアナログ PLL

- o クロックてい倍、分周と位相シフト

- ▶ システムレベル・サポート

- o 標準 IEEE1149.1 バウンダリ・スキャン、および ispTRACY™による内部ロジックアナライザ能力

- o 業界基準、サード・パーティ SPI ブート・フラッシュ・インターフェイス

- o 1.2 V 電源

## LatticeECP-DSP と LatticeEC FPGA ファミリ

| Parameter                   | EC1 | EC3 | ECP6/<br>EC6 | ECP10 /<br>EC10 | ECP15/<br>EC15 | ECP20/<br>EC20 | ECP40 /<br>EC40 |

|-----------------------------|-----|-----|--------------|-----------------|----------------|----------------|-----------------|

| PFU/PFF Rows                | 12  | 16  | 24           | 32              | 40             | 44             | 64              |

| PFU/PFF Columns             | 16  | 24  | 32           | 40              | 48             | 56             | 80              |

| Number of PFUs/PFFs         | 192 | 384 | 768          | 1280            | 1920           | 2464           | 5120            |

| sysDSP Blocks (ECP only)    | _   | _   | 4            | 5               | 6              | 7              | 10              |

| 18x18 Embedded Multipliers  | _   | _   | 16           | 20              | 24             | 28             | 40              |

| LUTs (K)                    | 1.5 | 3.1 | 6.1          | 10.2            | 15.4           | 19.7           | 41              |

| Distributed RAM (K bits)    | 6   | 12  | 25           | 41              | 61             | 79             | 164             |

| EBR Block SRAM (K bits)     | 18  | 55  | 92           | 277             | 350            | 424            | 645             |

| Number of EBR SRAM Blocks   | 2   | 6   | 10           | 30              | 38             | 46             | 70              |

| V <sub>cc</sub> Voltage (V) | 1.2 | 1.2 | 1.2          | 1.2             | 1.2            | 1.2            | 1.2             |

| Number of PLLs              | 2   | 2   | 2            | 4               | 4              | 4              | 4               |

| Packages & I/O Combinations |     |     |              |                 |                |                |                 |

| 100-pin TQFP (14 x 14 mm)   | 67  | 67  |              |                 |                |                |                 |

| 144-pin TQFP (20 x 20 mm)   | 97  | 97  | 97           |                 |                |                |                 |

| 208-pin TQFP (28 x 28 mm)   | 112 | 145 | 147          | 147             |                |                |                 |

| 256-ball fpBGA (17 x 17 mm) |     | 160 | 195          | 195             | 195            |                |                 |

| 484-ball fpBGA (23 x 23 mm) |     |     | 224          | 288             | 352            | 360            |                 |

| 672-ball fpBGA (27 x 27 mm) |     |     |              |                 |                | 400            | 496             |

| 900-ball fpBGA (31 x 31 mm) |     |     |              |                 |                |                | 576             |

# 所要コンフィグレーション・メモリ

ECP/EC FPGA ファミリはともにコンフィグレーション・データ・ストリームの圧縮をサポートします。ほとんどのデータ・ストリームで、最大 25%のファイル・サイズの低減を期待することができます。元のデバイス・コンフィグレーション用データ・ストリームはラティス ispLEVER®開発ツールによって圧縮されます。ECP/EC デバイスは、それぞれデバイス内に伸張エンジンを含んでおり、SPI フラッシュから入力されるコンフィグレーション・データ・ストリームを伸張します。多くの場合、この圧縮機能で、より小さい容量の SPI メモリ・デバイスを用いることができるようになります。例えば、5.3M のコンフィグレーション・ビットを含む EC20 デバイスは、通常 8M の SPI メモリを必要とします。25%のデータ・ストリーム圧縮で、4M の SPI メモリによって EC20 デバイスを構成することができるようになるため、総システム・コストをさらに減少させます。

以下の表に ECP/EC FPGA ファミリの所要 SPI メモリ・サイズをまとめます。色付きのセルは、ECP/EC ファミリのデータ・ストリーム圧縮能力によって、より小さい SPI メモリ・デバイスの使用が可能になる場合を強調しています。2 つのケース以外のすべてにおいて、必要なブートメモリは半分になりました。

| ファミリ       | デバイス | LUTs<br>(K) | 最大構成 ビット | 所要メモリ |      |  |

|------------|------|-------------|----------|-------|------|--|

|            |      | (14)        | サイズ(M)   | 圧縮なし  | 圧縮あり |  |

| EC         | 1    | 1.5         | 0.6      | 1     | 512K |  |

|            | 3    | 3.1         | 1.1      | 2     | 1    |  |

|            | 6    | 6.1         | 1.8      | 2     | 2    |  |

|            | 10   | 10.2        | 3.1      | 4     | 4    |  |

| EC/<br>ECP | 15   | 15.4        | 4.3      | 8     | 4    |  |

| 201        | 20   | 19.7        | 5.3      | 8     | 4    |  |

|            | 40   | 41.0        | 9.7      | 16    | 8    |  |

## ラティス ECP/EC への SPI フラッシュ・インターフェイス

LatticeECP/EC デバイスはどうしたらすべてのサード・パーティ SPI シリアル・フラッシュ・メモリにインターフェイスすることができるでしょうか?ラティスは、SPI シリアル・フラッシュ・ベンダのかなりの大部分がオペ・コード (OP Codes) の同じ組み合わせを利用するという事実を活用しています。特に「データ読み出し」コマンドの一般的なオペ・コードは、 $^{\prime\prime}$ 03H "(H=hex) です。ECP/EC デバイスは、03H オペ・コードをデバイス・シリコンの中に固定配線しました。ECP/EC デバイスがパワーアップされるとき、チップ・セレクト (CS) ピンを通して SPI フラッシュ・メモリを自動的にイネーブルして、オペ・コード $^{\prime\prime}$ 03H $^{\prime\prime}$ をメモリアドレス $^{\prime\prime}$ 0 と組み合わせてアクセスします。そして SPI メモリ・デバイスは、ECP/EC デバイスにコンフィグレーション・データ・ストリームを出力します。読み出しオペ・コード $^{\prime\prime}$ 03H $^{\prime\prime}$ を参照して、この簡単な  $^{\prime\prime}$ 4線(データ  $^{\prime\prime}$ 1本、制御  $^{\prime\prime}$ 3本)のコンフィグレーション・モードは $^{\prime\prime}$ 5PI3 $^{\prime\prime}$ 2と呼ばれます。

さらに"SPIx"モードにより、ECP/EC デバイスは"03H"以外の読み出しオペ・コードによる SPI フラッシュ・メモリとの容易なインターフェイスが可能です。このモードのサポートは、例えば現在入手できる"高速読み出しオペ・コード Fast Read Op Code; 0BH"による SPI メモリには有用で、事実約 20MHz から約 40MHz までデータ出力レートを倍にできます。この 11 線(データ 8 本、制御 3 本)のインターフェイスは、ECP/EC デバイスの sysCONFIG™ プログラミング・ポート (D[7:0])の 8 データ I/O を使用して必要なオペ・コードを設定します。このモードを用いるためには、D7:O ピンに弱い抵抗(4.7K)

で、8 ビットのオペ・コードを PCB 上で固定配線(プルアップ、またはプルダウン)します。パワーアップ時に、ECP/EC デバイスは、D[7:0] データ I/0 からオペ・コードを抽出して、SPI フラッシュ・メモリにそれを渡します。

## SPI フラッシュ・プログラミング・サポート

ラティス ispVM®システムは、ラティスの ispDOWNLOAD®ケーブル(フライ・ワイヤ) と組み合わせて、次の2モードのどちらかで SPI シリアル・フラッシュ・メモリのプログラミングをサポートします:

- 1. SPI フラッシュに接続されている専用の SPI インターフェイス/ヘッダーを通して (現在)

- 2. ECP/EC デバイスと SPI フラッシュに接続されている JTAG インターフェイス/ ヘッダーを通して(3Q04)

## まとめ

業界基準で、サード・パーティの SPI シリアル・フラッシュ・メモリによるコンフィグレーションをサポートすることによって、ラティスの ECP/EC FPGA ファミリは、競合他社の FPGA ソリューション用に提供されているよりも、かなり費用対効果に優れたコンフィグレーション・オプションをシステム設計者に提供します。

従来のブートメモリ・ソリューションよりかなり安価に値付けられることに加えて、SPIフラッシュは広範囲のメモリ・サイズにわたって入手でき、かつ実装スペースに優れた8ピン・パッケージで入手できます。ECP/ECデバイスのデータ圧縮機能を利用して、SPIフラッシュのメモリ・サイズ・マイグレーション機能を活用することができます。最後に、ラティス開発ツールは、設計者による開発努力を促進するためにSPIフラッシュ・コンフィグレーション・ソリューションの包括的なポートフォリオを提供します。

低コスト、業界基準、サード・パーティの SPI シリアル・フラッシュの利用をサポートすることにより、ラティスは真に費用対効果に優れた FPGA ソリューションを提供します。現在入手できる他の FPGA と比べて、LatticeECP/EC の「トータル FPGA ソリューション」は 30%から 50%のコスト節減をユーザにお届けします。

###