July 2, 2010

Subject: PCN# 10A-10, 90-Day Notification of Intent to Utilize an Alternate Foundry Process for the ispLSI 1032 and ispLSI 1048 Devices

**Dear Lattice Customers:**

In accordance with our Product Change Notification (PCN) policy, Lattice is providing this 90-day notification of our intent to utilize an alternate foundry process for the ispLSI<sup>®</sup> 1032 and ispLSI 1048 devices.

Lattice issued PCN#10D-08 (Notification of Intent to Utilize an Alternate Foundry Process for Select Mature Products) in July 2008 for an enhanced passivation process affecting select mature devices, including the ispLSI 1016, GAL®18V10B, and GAL20V8B products. We are now implementing the same passivation enhancement for the ispLSI 1032 and ispLSI 1048 devices. These are the last two device families that will need this process enhancement. Lattice will be able to provide seamless supply of these mature products by upgrading the fabrication process. This foundry process change has no impact on the device's electrical performance.

#### AFFECTED DEVICES

The affected devices are listed below. This PCN affects all speed and temperature grades for the device families listed below. Please refer to the device data sheets on the Lattice website at <a href="http://www.latticesemi.com">http://www.latticesemi.com</a> for complete list of Ordering Part Numbers (OPNs). This PCN also affects any custom devices (i.e. factory programmed, special test, tape and reel, non-standard speed grade, etc), which are derived from any of the devices listed.

| Product Line | Package Code | Package Type |

|--------------|--------------|--------------|

| ispLSI 1032  | J            | 84-PLCC      |

|              | Т            | 100-TQFP     |

| ispLSI 1048  | Q            | 120-PQFP     |

## **DEVICE IDENTIFICATION (EXAMPLE)**

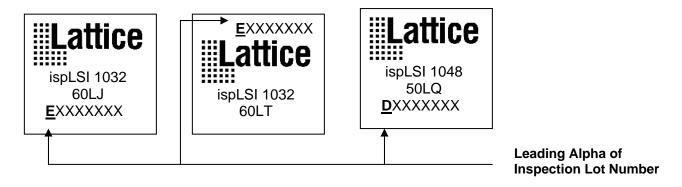

Devices with this new process can be identified by the first alpha character of the Inspection Lot Number, which is marked on the topside of the device. Inspection lot numbers are also marked on the label ("Mark Code" field) on the outside of the inventory box as well as on the anti-static, moisture barrier bag within. See device topside marking examples on the next page.

The products built on the new process can be identified by the leading alpha characters of the inspection lot number listed in the table below.

| Product Line | Leading Alpha of<br>Inspection Lot Number |

|--------------|-------------------------------------------|

| ispLSI 1032  | E/F                                       |

| ispLSI 1048  | D                                         |

#### **DATA SHEET SPECIFICATIONS**

This PCN has no impact on any data sheet specifications.

#### **QUALIFICATION DATA**

Reliability testing for the qualification of this fabrication process is complete. A summary of the qualification data is available <a href="here">here</a>.

#### **CONVERSION TIMING**

Conversion timing for this PCN is 90 days from the date of this Notice. Should samples be required to complete evaluation of this PCN, such sample requests must be received no later than August 2, 2010 (30 days after the date of this Notice).

# **CONVERSION TIMING - SUMMARY**

Sample Request Cut-off Date: August 2, 2010

PCN Expiration Date: October 1, 2010

## **RESPONSE**

In accordance with JESD46-C, this change is deemed accepted by the customer if no acknowledgement is received within 30 days from this Notice.

Note: Be sure to sign up for PCN "Web Alerts" (See PCN#13A-09 for details) and receive all future Lattice PCNs via e-mail!

# **CONTACT**

If you have any questions or require additional information, please contact pcn@latticesemi.com.

Sincerely,

Lattice Semiconductor PCN Administration