# A new breed of programmable logic. Not a CPLD, Not an FPGA.

## Introducing the ispGDXV

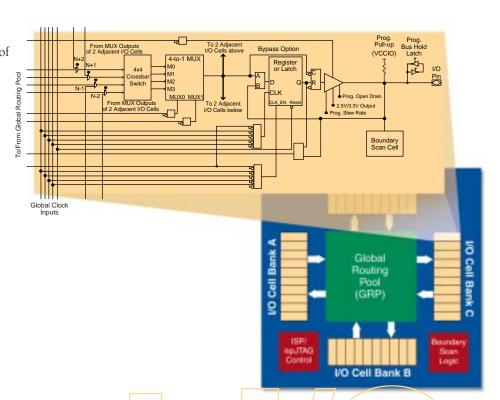

The 3.3-volt ispGDXV is a new class of high-density programmable component distinct from complex programmable logic devices (CPLDs) and field programmable gate arrays (FPGAs). This family of devices has been optimized for fast, cost-effective integration of complex interface logic and signal routing applications. With blazing fast 3ns input to output speeds, 250MHz pipelined operating frequencies, and programmable 3.3V or 2.5V output levels, the ispGDXV family supports the most demanding next-generation system designs. The ispGDXV family consists of devices with 80, 160 and 240 I/Os. The original 5V ispGDX® Family is available in 80, 120 and 160 I/O versions.

#### ispGDX/V Devices Support Applications CPLDs and FPGAs Don't Address

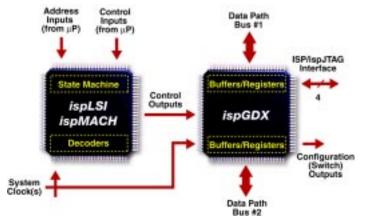

ispGDXV devices are the perfect complement to Lattice ispLSI® and ispMACH™ devices. Use ispLSI and ispMACH devices for fast control logic and ispGDXV devices for fast datapath logic.

#### **Key Features**

- In-System Programmable

- High Speed for Leading-Edge µP Clock Rates and Interfacing – 3ns t<sub>PD</sub>, 250MHz f<sub>MAX</sub>

- High I/O Integrates Dozens of Standard Bus Interface Devices

- Any Pin to Any Pin Routing

- Individually Programmable 3.3V or 2.5V Output Levels

- High Drive (24mA) I<sub>OL</sub>

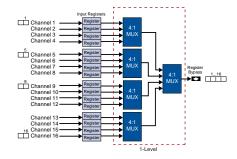

- Programmable Wide MUX, Supports from 4:1 to 16:1

High Speed MUX

- Programmable I/O Cells (Combinatorial/Register/Latch)

- Boundary Scan Test

## ispGDX/V Family

|                            | ispGDX80VA | ispGDX120A           | ispGDX160/VA                     | ispGDX240VA |

|----------------------------|------------|----------------------|----------------------------------|-------------|

| Supply Voltage             | 5V/3.3V    | 5V                   | 5V/3.3V                          | 3.3V        |

| I/O Pins                   | 80         | 120                  | 160                              | 240         |

| Speed — f <sub>MAX</sub> * | 250MHz     | 143MHz               | 250MHz                           | 200MHz      |

| Speed — t <sub>PD</sub>    | 3ns        | 5ns                  | 3.5ns                            | 4.5ns       |

| Speed — t <sub>GCO</sub>   | 3ns        | 5ns                  | 3.5ns                            | 4ns         |

| Registers                  | 80         | 120                  | 160                              | 240         |

| Boundary Scan Test         | Yes        | Yes                  | Yes                              | Yes         |

| Pins/Package               | 100-TQFP   | 176-TQFP<br>160-PQFP | 208-PQFP<br>208-fpBGA<br>272-BGA | 388-fpBGA   |

<sup>\*</sup>  $f_{MAX} = 1/(t_{WH} + t_{WL})$

#### ispGDX/V Applications

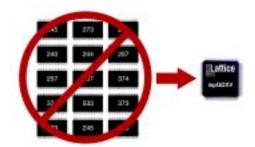

The ispGDXV replaces dozens of discrete interface devices, reducing PCB area and switching noise.

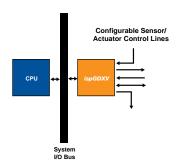

The ispGDXV provides an in-system programmable signal routing device for industrial control and instrumentation applications.

Multiplex 16 slow-speed channels into a single highspeed channel.

# ispGDX/V Development System

The ispLEVER Development System supports ispGDXV and ispGDX design entry, timing analysis, programming and timing simulation interfaces using a simple language syntax and an easy-to-use graphical user interface. The software runs under Windows® XP, Windows 2000, Windows 98 and Windows NT®. A command line driven version is also available to run on Sun Solaris and HP-Unix workstations.

# **For More Information**

www.latticesemi.com

#### **Applications Support**

1-800-LATTICE (528-8423) (408) 826-6002 techsupport@latticesemi.com