## Introducing the ispGDXV

The 3.3-volt ispGDXV is a new class of high-density programmable component distinct from complex programmable logic devices (CPLDs) and field programmable gate arrays (FPGAs). This family of devices has been optimized for fast, cost-effective integration of complex interface logic and signal routing applications. With blazing fast 3.5ns input to output speeds, 250MHz pipelined operating frequencies, and programmable 3.3V or 2.5V output levels, the ispGDXV family supports the most demanding future-generation system designs.

Lattice's ispGDXV family offers the ultimate interface solution for design engineers.

# Solutions

# Lattice ispGDXV Devices Simplify PCB Layout

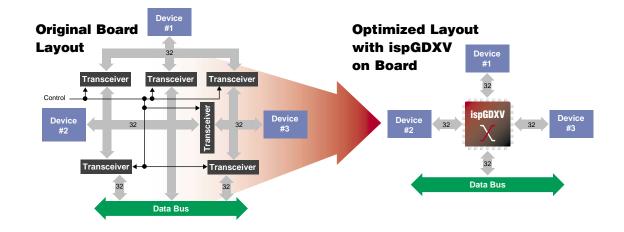

In this design, three peripheral devices must interface with each other and a data bus backplane. The original design required several transceivers and significant board routing resources to perform the data bus switching.

### with ispGDXV ...

- All transceivers are replaced by a single ispGDXV

- Traces and vias are dramatically reduced

- Significant reduction in EMI/RFI

- Boundary Scan Test added

#### **OC192 Bi-directional Access Port**

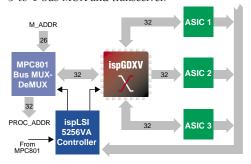

In this OC192 bi-directional access port, the ispGDXV performs a 3-to-1 bus MUX and transceiver.

#### **OC192 Product-Fiber Output Port**

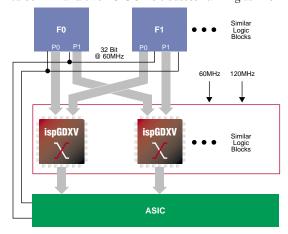

This OC192 application implements several 32-bit busses running at 60MHz and two ASIC 32-bit busses running at 120MHz.

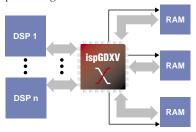

#### **BTS Transcoder Unit**

In this transcoder application, multiple DSPs interface with three RAMs. The transcoder performs voice compression and voice processing and each DSP can read and write each of the RAMs.

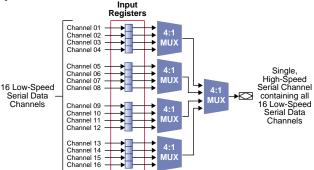

#### **Parallel to Serial Conversion**

In this time division multiplex application, 16 channels of lower line data are being multiplexed by a synchronous clock to a high speed serial line.

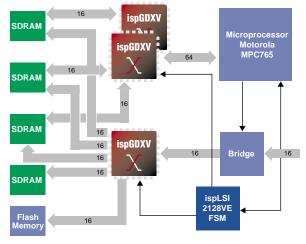

#### **Data Bus and Address Bus Transceivers**

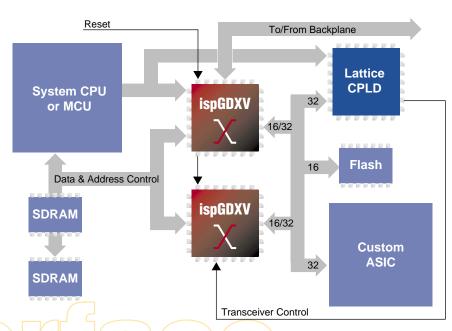

In this processor board application, the ispGDXV device performs muxing and demuxing from the SDRAMs and Flash to the PowerPC.

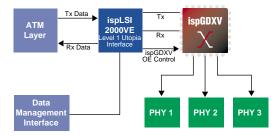

#### **ATM Utopia Interface**

In this Utopia 2 bus configuration, the ispGDXV device allows the Utopia 2 ATM frame to be steered to multiple physical layers.

#### **Switch Controller**

The ispGDXV is ideal for integrating a shared bus. In this application, the ispGDXV multiplexes the address and data path. CPU, ASIC and Bus share the same memory.

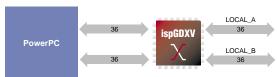

#### **PowerPC Interface**

The ispGDXV multiplexes a 72 bit data (with parity) bus to either of two local 36 bit busses. Plus, the ispGDXV provides voltage translation from the PowerPC at 2.5V to the other busses which are 3.3V.

#### **Applications Support**

1-800-LATTICE (528-8423) (408) 826-6002 techsupport@latticesemi.com

www.latticesemi.com