# LatticeECP/ECファミリ データシート

### 機能

- □ 幅広いロジック規模とパッケージのオプション

- 1.5Kから32.8KのLUT4

- 65~496 I/O

- ロジック規模のマイグレーションをサポート

- □ sysDSPブロック(LatticeECPバージョン)

- 高性能の積和演算機能

- 4~8ブロック

- 4~8個の36×36乗算器、または

- 16~32個の18×18乗算器、または

- 32~64個の9×9乗算器

- □ 組み込みメモリ(EBR)と分散メモリ

- 18Kbits~535Kbits sysMEM 組み込みブロックRAM(EBR)

- 最大131Kbitの分散メモリ(RAM)

- 自由度の高いメモリ・リゾース:

- 分散メモリとブロック・メモリ

- □ 専用のDDRメモリ・サポート

- DDR333(166MHz)までのインターフェイス実装に対応

- □ 自由度の高い入出力バッファ

- プログラマブルなsyslOバッファは広範囲の インターフェイスをサポート

- LVCMOS 3.3/2.5/1.8/1.5/1.2

- LVTTL

- SSTL 3/2クラスI, II, SSTL18クラスI

- HSTL 18クラスI, II, III, HSTL15クラスI, III

- PCI

- LVDS, Bus-LVDS, LVPECL

### ☐ sysCLOCK PLL

- 1デバイスあたり最大4個のアナログPLL

- クロックのてい倍、分周、および位相シフト

- □ システムレベル・サポート

- IEEE標準1149.1バウンダリ・スキャン、およびispTRACY (内部組み込みのロジックアナライザ機能)

- SPIブート・フラッシュ・インターフェイス

- 1.2V電源

### □ 低コストFPGA

- 主流のアプリケーションのために最適化された機能

- 低コストのTQFPとPQFPパッケージ

### 表 1-1 LatticeECP/ECファミリ・セレクション・ガイド

| デバイス                        | LFEC1 | LFEC3 | LFEC6 /<br>LFECP6 | LFEC10/<br>LFECP10 | LFEC15/<br>LFECP15 | LFEC20/<br>LFECP20 | LFEC33/<br>LFECP33 |

|-----------------------------|-------|-------|-------------------|--------------------|--------------------|--------------------|--------------------|

| PFU/PFF Row数                | 12    | 16    | 24                | 32                 | 40                 | 44                 | 64                 |

| PFU/PFF Column数             | 16    | 24    | 32                | 40                 | 48                 | 56                 | 64                 |

| PFU/PFF 総数                  | 192   | 384   | 768               | 1280               | 1920               | 2464               | 5120               |

| LUT サイズ (K)                 | 1.5   | 3.1   | 6.1               | 10.2               | 15.4               | 19.7               | 32.8               |

| 分散 RAM (Kbits)              | 6     | 12    | 25                | 41                 | 61                 | 79                 | 131                |

| EBR SRAM (Kbits)            | 18    | 55    | 92                | 277                | 350                | 424                | 535                |

| EBR SRAMブロック数               | 2     | 6     | 10                | 30                 | 38                 | 46                 | 58                 |

| SysDSP ブロック*1               | _     | _     | 4                 | 5                  | 6                  | 7                  | 8                  |

| 18x18 乗算器*1                 | _     | _     | 16                | 20                 | 24                 | 28                 | 32                 |

| V <sub>CC</sub> 電圧 (V)      | 1.2   | 1.2   | 1.2               | 1.2                | 1.2                | 1.2                | 1.2                |

| PLL 数                       | 2     | 2     | 2                 | 4                  | 4                  | 4                  | 4                  |

| パッケージとI/O                   |       |       |                   |                    |                    |                    |                    |

| 100-pin TQFP (14 x 14 mm)   | 67    | 67    |                   |                    |                    |                    |                    |

| 144-pin TQFP (20 x 20 mm)   | 97    | 97    | 97                |                    |                    |                    |                    |

| 208-pin PQFP (28 x 28 mm)   | 112   | 145   | 147               | 147                |                    |                    |                    |

| 256-ball fpBGA (17 x 17 mm) |       | 160   | 195               | 195                | 195                |                    |                    |

| 484-ball fpBGA (23 x 23 mm) |       |       | 224               | 288                | 352                | 360                | 360                |

| 672-ball fpBGA (27 x 27 mm) |       |       |                   |                    |                    | 400                | 400                |

<sup>1.</sup> LatticeECPデバイス(LFECPxx)のみ

### イントロダクション

FPGAデバイスのLatticeECP/ECファミリは、低コストで主流のFPGA機能を提供するために最適化されました。最大性能と価値のために、LatticeECP(EConomy Plus)FPGAのコンセプトは、効率的なFPGAファブリックを高速の専用機能を組み合わせるものです。このアプローチを実装するラティスの最初のファミリは、専用の高性能DSPブロックをオンチップで提供するLatticeECP-DSP(EConomy Plus DSP)ファミリです。

LatticeEC(EConomy)ファミリは、低コスト・ソリューションを達成するために、LatticeECPデバイスの専用機能ブロックを除いた汎用機能を全てサポートします。LatticeECP/EC FPGAファブリックは、低コストを念頭に設計着手されながら、すべての重要なFPGA要素を持っています。LUTベースのロジック、組み込み/分散メモリ、PLL、および主要なI/Oのサポート、専用のDDRメモリ・インターフェイス・ロジックも内蔵されており、ますますコスト重視のアプリケーションで一般的になっているこのメモリをサポートします。ラティスからのispLEVER設計ツールにより、大きい複雑なデザインも、LatticeECP/ECファミリを用いることで効率的に実装できます。標準的な論理合成ツール用に、LatticeECP/EC用ライブラリをサポートします。

ispLEVER®ツールはLatticeECP/ECデバイスにデザインを配置配線するために、論理合成ツール出力をフロア・プランニング・ツールからの制約と共に用います。ispLEVERツールは、タイミング検証のために、配線からタイミング情報を抽出して、デザインにバック・アノテートします。

ラティスは予め設計された多くのIP(Intellectual Property) ispLeverCOREモジュールをLatticeECP/ECファミリのために提供します。標準化されたブロックとしてこれらのIPを用いることによって、設計者は自らの設計独自な部分に集中することができ、生産性を上げることができます。

# LatticeECP/ECファミリデータシート アーキテクチャ

### アーキテクチャ概要

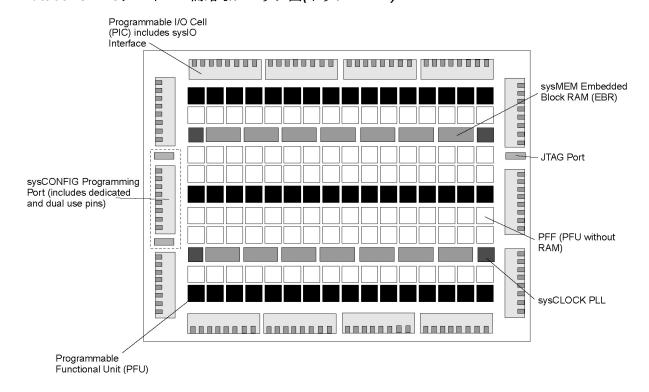

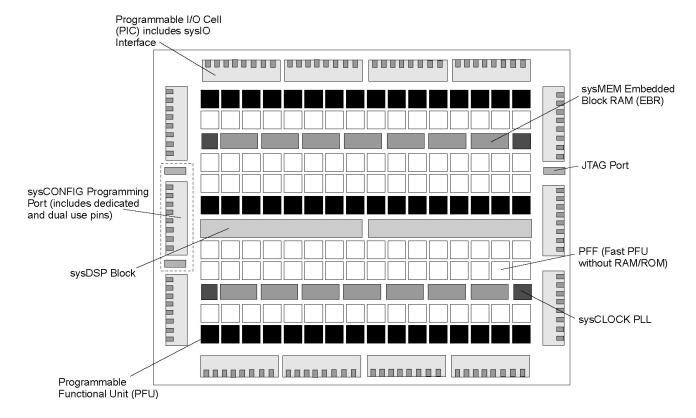

LatticeECP-DSPとLatticeECアーキテクチャはプログラマブルI/Oセル(PIC)によって囲まれた論理ブロックのアレイを含んでいます。論理ブロックの列の間に点在するのは、図2-1と図2-2で示されるsysMEM組み込みブロックRAM(EBR)の列です。さらに、LatticeECP-DSPは図2-2で示されるように追加のDSPブロック列をサポートします。

2種類の論理ブロック、プログラマブル・ファンクション・ユニット(PFU)、およびRAM/ROMなしのPFUユニット(PFF)があります。PFUはロジック、演算、RAM、ROM、およびレジスタ機能のためのビルディング・ブロックを含みます。PFFブロックはロジック、演算、およびROM機能のためのビルディング・ブロックを含んでいます。PFUとPFFブロックは共に、複雑なデザインを迅速にかつ効率的に実装できるように柔軟性が最適化されています。論理ブロックは2次元配列でアレンジされており、1つのタイプのブロックだけが列単位で用いられます。PFUブロックは外側の列で用いられています。コアの残りはPFUブロックの列が点在するPFFブロックの列から成ります。3列のPFFブロックごとにPFUブロックが一列あります。

各PICブロックはそれぞれのsysIOインターフェイスで2PIO(PIOペア)を取り囲みます。デバイスの左右のエッジにあるPIOペアは送受信LVDSペアとして構成することができます。sysMEM EBRは大きく、専用の高速メモリ・ブロックです。RAMかROMとしてそれらを構成することができます。

PFU、PFF、PIC、およびEBRブロックは図2-1で示されるように二次元格子の列とコラムで配置されます。 ブロックは多くの縦方向と横方向の配線チャネルリソースに接続されます。配置配線ソフトウェア・ツール は自動的にこれらの配線リソースを割り当てます。

### 図2-1 LatticeECP/ECデバイスの簡略なブロック図(トップレベル)

sysMEMブロックを含む列の終わりに、sysCLOCK位相ロック・ループ(PLL)ブロックがあります。これらのPLLにはてい倍、分周、および位相シフトの能力があります。それらは、クロックの位相関係を管理するのに用いられます。LatticeECP/ECアーキテクチャは1デバイスあたり最大4個のPLLを提供します。

ファミリの全デバイスにはJTAGポートがあり、組み込むことができるロジック・アナライザ(ispTRACY)機能のアクセスにも用いられます。sysCONFIGポートはシリアルまたはパラレルのデバイス・コンフィグレーションを可能にします。LatticeECP/ECデバイスはそのコア電圧として1.2Vを用います。

### 図2-2 LatticeECP-DSPデバイスの簡略なブロック図(トップレベル)

# PFU / PFFブロック

LatticeECP/ECデバイスのコアはPFUとPFFブロックから成ります。PFUはロジック、演算、分散RAM、および分散ROM機能を実行するようにプログラムすることができます。PFFブロックはロジック、演算、およびROM機能を実行するようにプログラムすることができます。特に明記する場合を除いて、データシートの残りでは、PFUとPFFブロックの両方を示すのに用語PFUを用います。

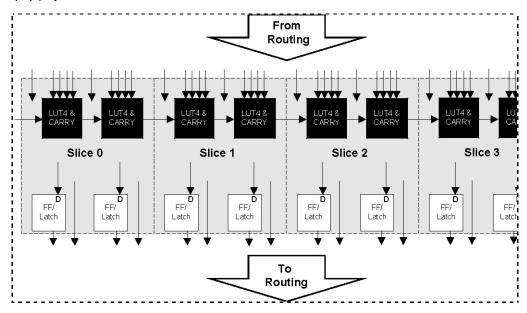

それぞれのPFUブロックは、図2-3で示されるように0~3と番号付けられた4つの相互接続されたスライスから成ります。PFUブロックに出入りするすべての相互接続は配線(領域)から来ています。それぞれのPFUブロックに関連する53本の入力と25本の出力があります。

### 図2-3 PFUダイヤグラム

### スライス

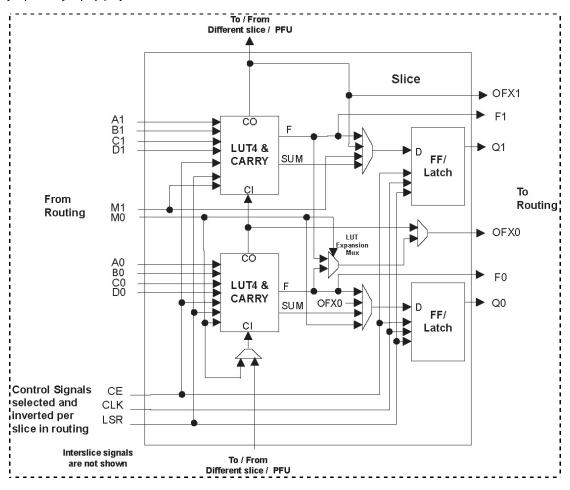

各スライスは、2つのレジスタ(FFかLatchモードでプログラムされる)に接続する2個のLUT4ルックアップ・テーブルよりなり、さらにLUTがLUT5や、LUT6、LUT7およびLUT8などの機能を実行するために組み合わせられるようにする関連ロジックを含んでいます。セット/リセット機能(同期か非同期でプログラムできる)、クロック選択、チップセレクト、そしてより広いRAM/ROM機能を実行するための制御ロジックがあります。図2-4はスライスの内部ロジックの概観を示します。正/負の、そしてエッジ/レベル・クロック用にスライス内のレジスタを構成することができます。

スライスには14の入力信号があります。配線からの13本の信号と、キャリ・チェーンからの1本(隣接しているスライスかPFUから)です。7本の出力があります。配線への6本と(隣接しているPFUへの)キャリ・チェーンの1本です。表2-1は各スライスに関連している信号をリストアップします。

表2-1 スライス信号記述

| 機能 | タイプ    | 信号名            | 記述                                           |

|----|--------|----------------|----------------------------------------------|

| 入力 | データ信号  | A0, B0, C0, D0 | LUT4入力                                       |

| 入力 | データ信号  | A1, B1, C1, D1 | LUT4入力                                       |

| 入力 | 複数用途   | MO             | 複数用途入力                                       |

| 入力 | 複数用途   | M1             | 複数用途入力                                       |

| 入力 | 制御信号   | CE             | クロック・イネーブル                                   |

| 入力 | 制御信号   | LSR            | ローカル・セット/リセット                                |

| 入力 | 制御信号   | CLK            | システム・クロック                                    |

| 入力 | PFU間信号 | FCIN           | 高速キャリ入力1                                     |

| 出力 | データ信号  | F0, F1         | LUT4出力レジスタ・バイパス信号                            |

| 出力 | データ信号  | Q0, Q1         | レジスタ出力                                       |

| 出力 | データ信号  | OFX0           | LUT5 MUX出力                                   |

| 出力 | データ信号  | OFX1           | LUT6, LUT7, LUT8 <sup>2</sup> MUX 出力、スライスに依存 |

| 出力 | PFU間信号 | FCO            | 最右PFU用の高速キャリ・チェイン出力 <sup>1</sup>             |

- 1. 接続の詳細については図2-3を参照.

- 2. 2 PFUが必要.

図2-4 スライス・ダイヤグラム

#### 動作モード

それぞれのスライスには4動作モードがあり、それはロジック、リップル、RAM、およびROMです。PFFのスライスはRAM以外の全モードができます。表2-2はモードとスライス・ブロックの機能をリストします。

表2-2 スライス・モード

|          | ロジック               | リップル         | RAM     | ROM         |

|----------|--------------------|--------------|---------|-------------|

| PFU スライス | LUT 4x2 or LUT 5x1 | 2-bit 演算ユニット | SPR16x2 | ROM16x1 x 2 |

| PFF スライス | LUT 4x2 or LUT 5x1 | 2-bit 演算ユニット | N/A     | ROM16x1 x 2 |

**ロジック・モード**: このモードで、各スライスにおけるLUTは、4入力の組み合わせルックアップ・テーブルとして構成されます。LUT4は16の可能な入力組み合わせを持つことができます。このルックアップ・テーブルをプログラムすることによって、4入力があるどんなロジック機能も生成することができます。1スライスあたり2個のLUT4があるので、1スライスでLUT5を組み立てることができます。他のスライスを連結することによって、LUT6や、LUT7、LUT8などのより大きいルックアップ・テーブルを構成することができます。

**リップル・モード**: リップル・モードは小さな演算機能の効率的な実装ができます。リップル・モードでは、各スライスは以下の機能を実装することができます。

- 2ビット加算

- 2ビット減算

- ・動的な制御での2ビット加算・減算

- 2ビット・アップカウンタ

- 2ビット・ダウンカウンタ

- リップル・モード乗算器ビルディング・ブロック

- AとB入力のコンパレータ機能

- AはBより等しいか大きい

- AはBに等しくない

- AはBより等しいか小さい

**2**つの追加信号。Carry Generate(キャリ生成)とCarry Propagate(キャリ伝播)はこのモードでスライス単位で生成され、スライスを連結することによって高速演算機能が構成できます。

**RAMモード**; このモードでは、16×1ビットのメモリとしてそれぞれのLUTブロックを用いることで,分散メモリ(RAM)を構成することができます。LUTとスライスの組み合わせで、さまざまな異なったメモリを構成することができます。

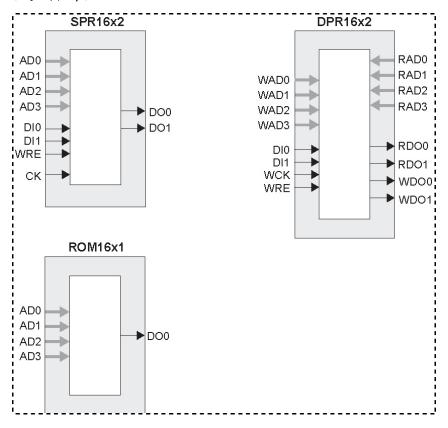

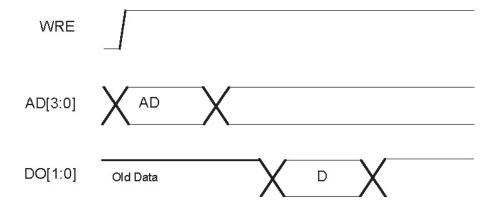

ラティス・デザインツールは種々異なるサイズのメモリ作成をサポートします。適切な場合、PFUの能力を示す分散メモリ・プリミティブを用いることで、ソフトウェアはこれらを構成します。表2-3は異なる分散メモリ(RAM)プリミティブを実装するのに必要なスライスの数を示します。図2-5は分散メモリ・プリミティブ・ブロック図を示します。デュアルポート・メモリは2つのスライスの組み合わせにかかわっており、一方のスライスはリード・ライト・ポートとして機能します。もう片方のスライスは、リードオンリ・ポートをサポートします。LatticeECP/ECデバイスでRAMを用いる詳しい情報に関しては、テクニカル・ドキュメンテーション(TN1051)を参照してください。

### 図2-5 分散メモリ・プリミティブ

#### 表2-3 分散RAMの実装に必要なスライスの数

|       | SPR16x2 | DPR16x2 |

|-------|---------|---------|

| スライス数 | 1       | 2       |

注: SPR = Single Port RAM, DPR = Dual Port RAM

**ROMモード:**ROMモードはライト・ポートを除いてRAMモードと同じ原則を用います。プリロードはコンフィグレーションの間、プログラミング・インターフェイスを通して達成されます。

#### PFU動作モード

より大きい機能を形成するためにPFU内でスライスを組み合わせることができます。表**2-4**はこれらのモードを表にしており、PFUレベルで可能な機能を記述します。

#### 表2-4 PFU動作モード

| ロジック                       | リップル              | RAM <sup>1</sup>           | ROM         |

|----------------------------|-------------------|----------------------------|-------------|

| LUT 4x8 or<br>MUX 2x1 x 8  | 2-bit Add x 4     | SPR16x2 x 4<br>DPR16x2 x 2 | ROM16x1 x 8 |

| LUT 5x4 or<br>MUX 4x1 x 4  | 2-bit Sub x 4     | SPR16x4 x 2<br>DPR16x4 x 1 | ROM16x2 x 4 |

| LUT 6x 2 or<br>MUX 8x1 x 2 | 2-bit Counter x 4 | SPR16x8 x 1                | ROM16x4 x 2 |

| LUT 7x1 or<br>MUX 16x1 x 1 | 2-bit Comp x 4    |                            | ROM16x8 x 1 |

<sup>1.</sup> このモードはPFFブロックにはない

### 配線

単独信号かバス信号として関連する制御信号と共に配線するための多くのリソースがLatticeECP/ECデバイスに用意されています。配線リソースはスイッチング回路、バッファ、およびメタル・インターコネクト(配線)セグメントから成ります。

PFU相互の接続は(2PFUにまたがる)x1ライン、(3PFUにまたがる)x2ライン、および(7PFUにまたがる)x6ラインで行われます。x1とx2接続は速くて効率の良い接続を横方向と縦方向に提供します。x2とx6リソースはバッファリングされ、PFU間に短い接続と長い接続配線を可能にします。

ispLEVERデザイン・ツールは、論理合成ツールの出力を取り込んで、デザインを配置配線します。デザインを最適化するために対話的な配線エディタが利用できますが、一般に配置配線ツールは完全に自動です。

### クロック分配ネットワーク

クロック入力は外部I/O、sysCLOCK PLLまたは配線から選択されます。これらのクロック入力はクロック分配システムを介してチップ全体に与えられます。

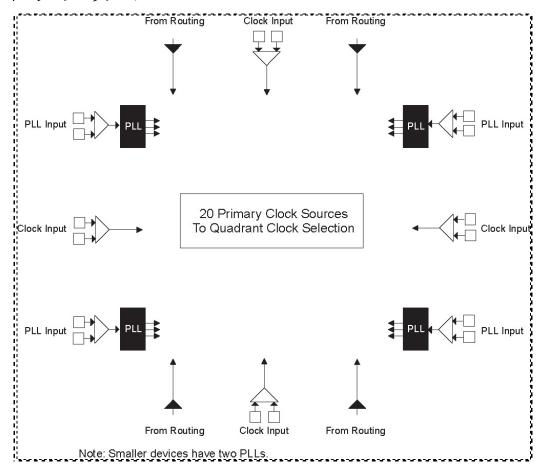

#### プライマリ・クロック・ソース

LatticeECP/ECデバイスは3プライマリ・ソースからクロックを得ます。それらはPLL出力、専用のクロック入力、および配線です。LatticeECP/ECデバイスは左右の側に位置する2~4個のsysCLOCK PLLを持っています。デバイスには計4本の専用クロック入力があり、それぞれの辺に一本あります。図2-6は20本のプライマリ・クロック・ソースを示します。

### 図2-6 プライマリ・クロック・ソース

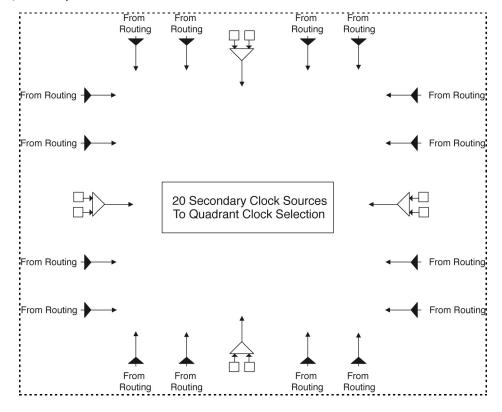

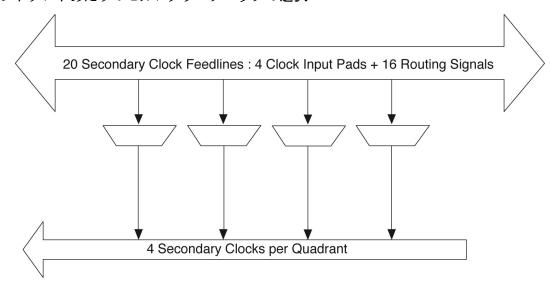

### セカンダリ・クロック・ソース

LatticeECP/ECデバイスはクワドラント(チップ内を4分割した領域)毎に4本のセカンダリ・クロック・ソースがあります。セカンダリ・クロックは全てのPFUに分岐タップがあります。これらセカンダリ・クロック・ネットワークは制御信号や高ファンアウトのデータ線にも使用することができます。セカンダリ・クロックは、4本のクロック入力パッドと16本の配線領域からの信号より得られ、図2-7に示されています。

図2-7 セカンダリ・クロック・ソース

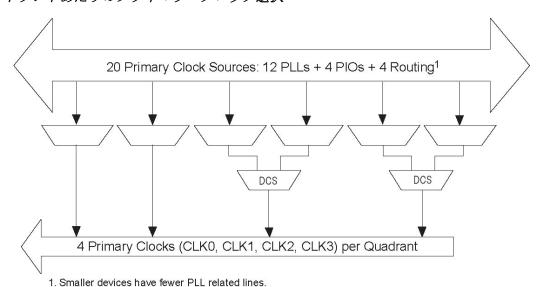

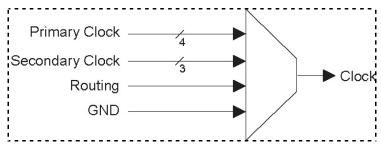

### クロック配線

LatticeECP/ECデバイスにおけるクロック配線構造は、クワドラントごとに4本のプライマリ・クロック線と、1本のセカンダリ・クロック・ネットワークから成ります。プライマリ・クロックはそれぞれクワドラントに位置するマルチプレクサから生成されます。図2-8はこのクロック配線を示します。

### 図2-8 クワドラントあたりのプライマリ・クロック選択

2-8

LatticeECP/EC

**4**本のセカンダリ・クロックは図**2-9**に示されるように、各クワドラントにあるマルチプレクサから生成されます。各スライスは図**2-10**で示されるように、プライマリ・クロック・ライン、セカンダリ・クロック・ライン、および配線からクロックをもらいます。

### 図2-9 クワドラントあたりのセカンダリ・クロックの選択

図2-10 スライスのクロック選択

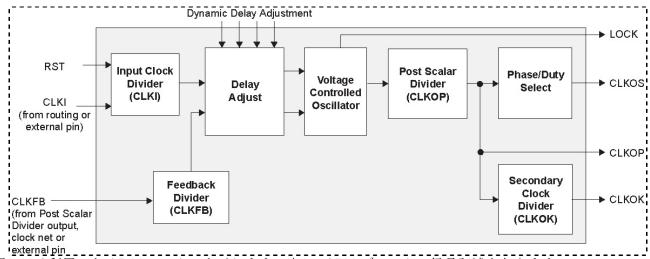

### sysCLOCK位相ロック・ループ(PLL)

PLLへのクロック入力は、ピンか配線から入力クロック分周器に与えられます。フィードバック分周器へのフィードバック信号としては4つのソースがあります。これらはクロック・ネット、後段の分周器出力、配線、そして外部ピンです。VCOが入力クロック信号にロックしたことを示すために、PLL\_LOCK信号があります。図2-11はsysCLOCK PLLダイヤグラムを示します。

PLLのフィードバックか入力経路に遅延をプログラムすることによって、デバイスのセットアップとホールド時間を改良することができますが、これによって入力クロックに対し出力クロックを進めるかまたは遅らせるためです。この遅延は、コンフィグレーションの間プログラムするか、またはダイナミックに調整することができます。ダイナミックなモードでは、PLLは調整の後にロックを失い、t<sub>Lock</sub>パラメータが満たされるまで再ロックしないかもしれません。さらに、位相とデューティサイクル・ブロックで、ユーザはCLKOS出力の位相とデューティ比を調整できます。

sysCLOCK PLLはクロック周波数を合成する機能があります。各PLLには、それに関連する4つの分周器があり、それらは入力クロック分周器、フィードバック分周器、スカラの分周器とセカンダリ・クロック分周器です。入力クロック分周器は入力クロック信号を分周し、他方フィードバック分周器はてい倍することに等価です。ポスト・スカラ分周器によりVCOがクロック出力より高い周波数で動作することを可能にし、その結果周波数範囲を増大させます。セカンダリ分周器は、より低い周波数出力を引き出すのに用いられます。

#### 図2-11 PLLダイヤグラム

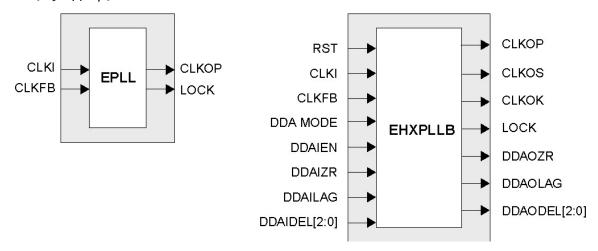

図2-12は利用できるPLLのマクロを示します。表2-5はPLLブロックの信号記述を与えます。

#### **図2-12 PLL** プリミティブ

表2-5 PLL信号記述

| 信号           | I/O | 記述                                            |

|--------------|-----|-----------------------------------------------|

| CLKI         | 1   | クロック入力。外部ピンもしくは配線から                           |

| CLKFB        | 1   | PLLフィードバック入力。PLL出力、クロックネット、配線、または外部ピンから       |

| RST          | - 1 | "1" でクロック・ドライバをリセット                           |

| CLKOS        | 0   | PLL出力クロック。クロックツリーへ(位相シフト、デューティ比可変)            |

| CLKOP        | 0   | PLL出力クロック。クロックツリーへ(位相シフトなし)                   |

| CLKOK        | 0   | PLL出力。セカンダリ・クロック・ドライバを介してクロックツリーへ             |

| LOCK         | 0   | "1" でPLLがCLKIにロック                             |

| DDAMODE      | I   | ダイナミック遅延イネーブル。"1" ピン制御 (動的), "0": フューズ制御 (静的) |

| DDAIZR       |     | ダイナミック遅延ゼロ。"1": 遅延 = 0, "0": 遅延 = on          |

| DDAILAG      | I   | ダイナミック遅延動的遅延。 "1": 遅れ(Lag)、"0": 進み(Lead)      |

| DDAIDEL[2:0] | Ī   | ダイナミック遅延入力                                    |

| DDAOZR       | 0   | ダイナミック遅延ゼロ出力                                  |

| DDAOLAG      | 0 | ダイナミック遅延動的遅延(Lag/Lead)出力 |

|--------------|---|--------------------------|

| DDAODEL[2:0] | 0 | ダイナミック遅延出力               |

PLLの詳しい情報に関しては、テクニカル・ドキュメンテーション(TN1049)を参照してください。

# ダイナミック・クロック・セレクト(DCS)

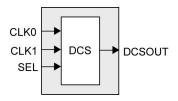

DCSはマルチプレクサ機能のついたグローバル・クロック・バッファです。グリッチや細ったパルスを出す事なしに2クロック入力から1出力を選択します。これはクロック信号がどこでトグルするかに係わらず行われます。デバイス内には8つのDCSブロックがあり、各辺の中央に2つの組で配置されています。図2-13はDCSマクロ・ブロックを示します。

### 図2-13 DCS ブロック・プリミティブ

図2/14はデフォルト・モード時のDCSのタイミング波形を示します。DCSは他の動作モードにも設定できます。DCSの詳しい情報に関しては、テクニカル・ドキュメンテーション(TN1049)を参照してください。

#### 図2-14 DCS波形

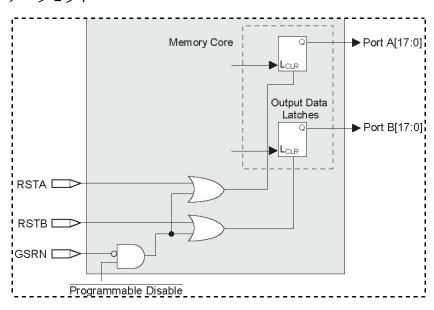

# sysMEMメモリ

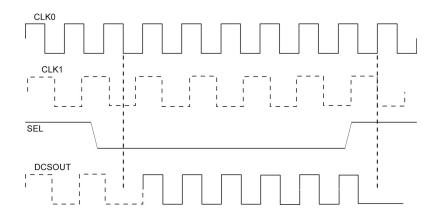

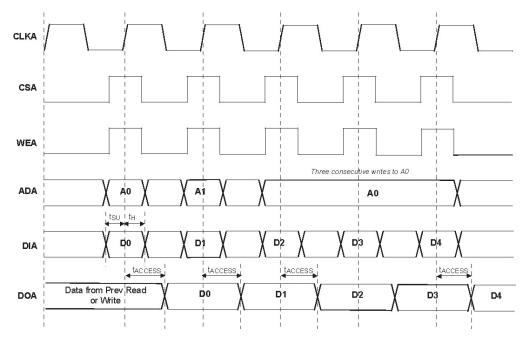

LatticeECP/ECファミリのデバイスは多くのsysMEM組み込みブロックRAM(EBR)を持っています。EBRは専用の入出力レジスタがある9kビットのRAMから成ります。

### sysMEMメモリ・ブロック

sysMEMブロックはシングルポート、デュアルポートまたは疑似デュアルポート・メモリを実装することができます。表2-6に示されるようにさまざまな深さと幅で各ブロックを用いることができます。

#### 表2-6 sysMEMブロック・コンフィグレーション

| メモリ・モード   | 構成                                                                       |

|-----------|--------------------------------------------------------------------------|

| シングルポート   | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |

| 真のデュアルポート | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18             |

| 擬似デュアルポート | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |

### バス・サイズ・マッチング

多ポート・メモリ・モードのすべてがそれぞれの異なるポート幅をサポートします。RAMビットはWord0のLSBからMSBへ、Word1のLSBからMSBへというように配置されます。ワード長とワード数はポートごとに異なりますが、このマッピング体系は各ポートに適用されます。

### RAMの初期化とROM動作

望む場合、デバイス・コンフィグレーションの際に、RAMの内容をプリロードすることができます。チップ・コンフィグレーション・サイクルの間、RAMブロックをプリロードし、書き込み制御をディセーブル(不許可)することで、sysMEMブロックはまた、ROMとして利用することができます。

#### メモリの連結

EBR sysMEMブロックを用いることで、より大きくて、より深いRAMブロックを作成することができます。通常、ラティス・デザインツールは特定の設計への入力に基づいて透過的に(暗黙に)メモリを連結します。

### シングル/デュアル/擬似デュアルポート・モード

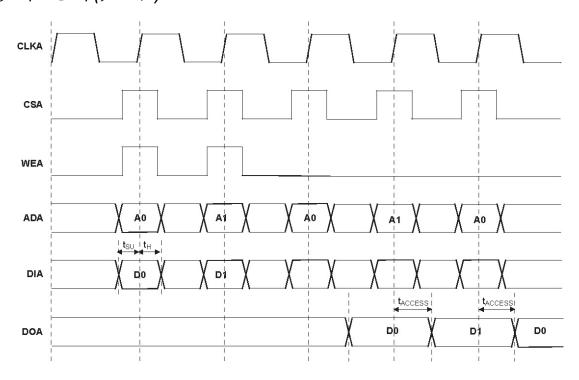

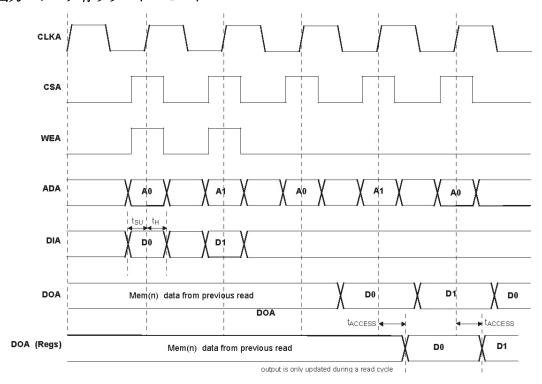

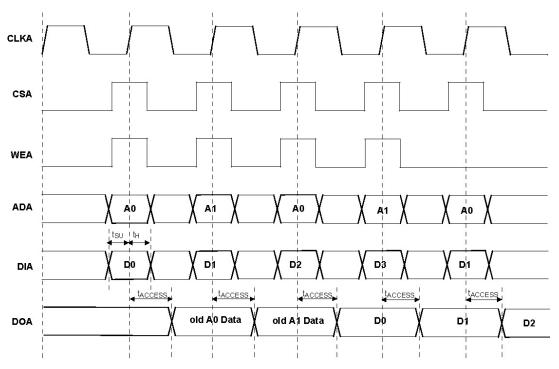

図2-15は4つの基本的なメモリ・コンフィグレーションとそれらの入力/出力名を示します。全てのsysMEM RAMモードで、ポートへの入力データとアドレスにはメモリ・アレイの入力にレジスタがあります。メモリの出力データへのレジスタはオプションです。

EBRメモリはシングルポートかデュアルポート動作のための書き込みの振舞いとして3つの形態をサポートします。

- **1. 標準**;出力データはリード・サイクルの間だけ現れます。ライト・サイクルの間、現在のアドレスのデータは出力に現れません。

- 2. ライトスルー; ライト・サイクルの間、入力データのコピーが同じポートの出力に現れます。

- 3. **リード・ビフォー・ライト**;新しいデータが書かれときに、アドレスの古い内容が出力に現れます。

### 図2-15 sysMEM EBRプリミティブ

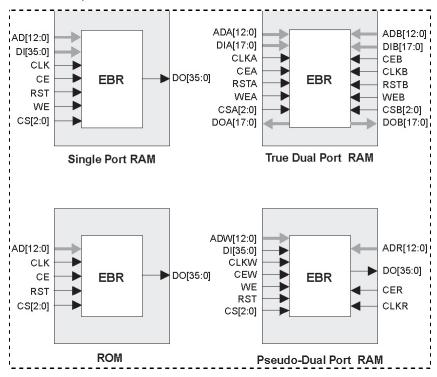

### メモリコア・リセット

EBRのメモリ・アレイはA出力とB出力ポートのラッチを利用します。これらのラッチを非同期か同期でリセットすることができます。RSTAとRSTBはローカルの信号で、出力ラッチをリセットし、それぞれPort AとPort Bに関連します。Global Reset(GSRN)信号は両ポートをリセットします。両ポートのための出力データ・ラッチと関連するリセットが図2-16で示されます。

#### 図2-16 メモリコア・リセット

sysMEM EBRブロックの詳しい情報に関しては、テクニカル・ドキュメンテーション (TN1051) を参照してください。

# sysDSPブロック

LatticeECP-DSPファミリはsysDSPブロックを提供し、これにより低コストで高性能のデジタル信号処理 (DSP)アプリケーションに理想的に適しています。これらのアプリケーションで用いられる典型的な機能は 有限インパルス応答 (FIR)フィルタです。高速フーリエ変換(FFT)機能、相関器、リード・ソロモン/ターボ/たたみ込み符号器、および復号器。これらの複雑な信号処理機能は、加算器と乗算器やアキュムレータと乗算器のように類似のビルディング・ブロックを用います。

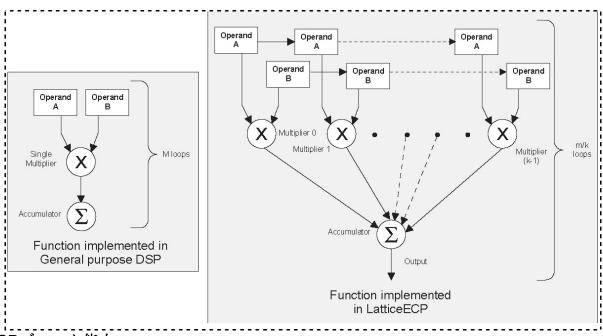

### sysDSPブロック・アプローチと汎用DSPとの比較

従来の汎用DSPチップは固定データ幅のMAC(乗算とアキュミュレート)ユニットを通常1~4個含んでいます。これは限られた並列度と限られたスループットに通じます。それらのスループットは、より高いクロックスピードによって増加されます。他方LatticeECPには、異なったデータ幅をサポートする多くのDSPブロックがあります。これで、設計者はDSP機能の非常に並列度のある実装ができます。設計者は、適切なレベルの並列度を選ぶことによって、エリアに対するDSP性能を最適化することができます。図2-17はシリアル実装と並列実装を比較します。

### 図2-17 汎用DSPとLatticeECP-DSPアプローチの比較

### sysDSPブロック能力

LatticeECP-DSPファミリにおけるsysDSPブロックは、4個の機能要素を9、18と36の3種のデータパス幅でサポートします。ユーザは機能要素をDSPブロック用に選択して、次にオペランドの幅とタイプ(符号あり/なし)を選びます。LatticeECP-DSPファミリsysDSPブロックにおけるオペランドは、符号ありか符号なしですが、機能要素の中で混在できません。同様に、オペランド幅もブロックの中で混在できません。

各sysDSPブロックにおけるリソースは以下の4つの要素をサポートするために構成することができます。

• MULT 乗算

MAC 積和(乗算とアキュミュレート(累積))

• MULTADD 乗算、加算/減算

MULTADDSUM 乗算、加算/減算、アキュミュレート

各ブロックで利用できる要素の数は、x9、x18、およびx36の3つのオプションに依存します。これらの多くの要素はDSP機能の並列度の高い実装のために連結できます。表2-1はブロックの機能を示します。

表2-7 ブロックにおける最大の要素数

| 乗算器幅 (>)   | х9 | x18 | x36 |

|------------|----|-----|-----|

| MULT       | 8  | 4   | 1   |

| MAC        | 4  | 2   | _   |

| MULTADD    | 4  | 2   | _   |

| MULTADDSUM | 2  | 1   | _   |

4つの要素ではいくつかのオプションが利用できます。すべての要素の入力レジスタには、直接ロードするか、または直前のオペランドのシフト・レジスタからロードできます。符号あり/なしオプションでの"ダイナミック動作"を選択することに加えて、オペランドを各サイクルごとに符号あり・符号なしを切り換えることができます。同様に、"Add/Sub"オプションでダイナミック動作を選択することによって、アキュミュレータを各サイクルごとに加算と減算で切り換えることができます。

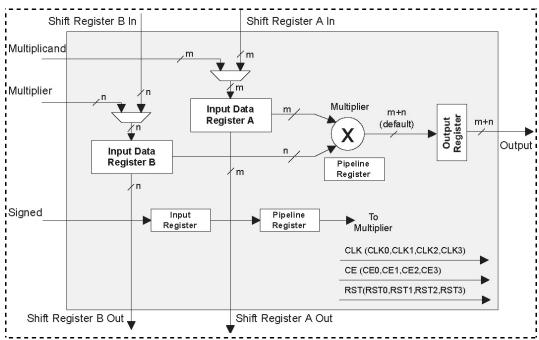

### MULT sysDSP要素

この乗算器要素は加算/アキュムレータ・ノードなしで乗算します。二つのオペランド(AとB)は、乗算され、そして、結果が出力に出てきます。ユーザは入力/出力/パイプライン各レジスタをイネーブルすることができます。図2-18はMULT sysDSP要素を示します。

### 図2-18. MULT sysDSP要素

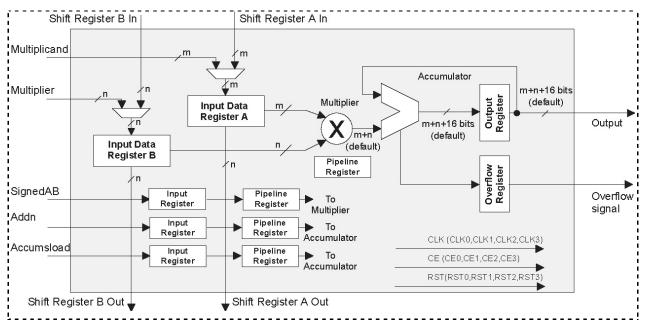

### MAC sysDSP 要素

この場合、二つのオペランド(AとB)は乗算されて、結果はアキュミュレート(累積)された直前の値に加えられます(積和動作)。このアキュミュレート値は出力で利用できます。ユーザは入力とパイプライン・レジスタをイネーブルすることができますが、出力レジスタは常にイネーブルされます。出力レジスタは、アキュミュレートされた値を保持するために用いられます。また、レジスタのあるオーバフロー信号も利用できます。本ドキュメントの後ではオーバフロー条件を示します。図2-19はMAC sysDSP要素を示します。

### 図2-19. MAC sysDSP要素

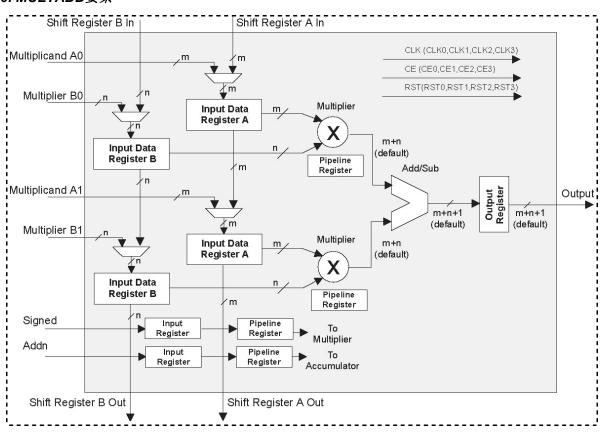

### MULTADD sysDSP要素

オペランドのA0とB0は乗算されて、その結果は、オペランドA1とA2の乗算の結果に加えられるか、または引き算されます。ユーザは入力/出力/パイプライン各レジスタをイネーブルすることができます。図2-20は MULTADD sysDSP要素を示します。

### 図2-20. MULTADD要素

LatticeECP/EC

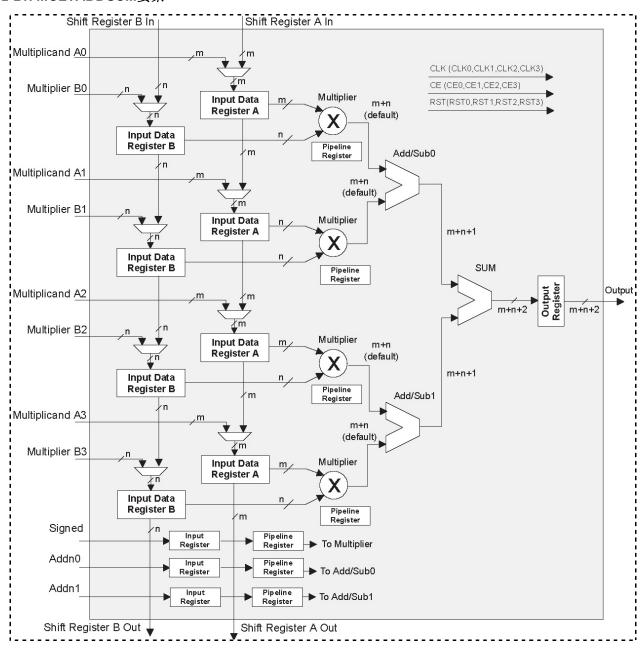

### MULTADDSUM sysDSP要素

オペランドのA0とB0は乗算されて、その結果は、オペランドA1とB1の乗算の結果に加えられるか、または引き算されます。オペランドのA2とB2は乗算されて、その結果は、オペランドのA3とB3の乗算の結果にさらに加えられるか、または引き算されます。加算/減算の結果は共に総和(加算)ブロックで加えられます。ユーザは入力/出力/パイプライン各レジスタをイネーブルすることができます。図2-21はMULTADDSUM sysDSP要素を示します。

図2-21. MULTADDSUM要素

### クロック、クロック・イネーブル、およびリセット・リソース

配線からのグローバル・クロック、クロック・イネーブルとリセット信号は全てのDSPブロックで使用できます。各4本のクロック、リセット、およびクロック・イネーブル信号はsysDSPブロックのために選択されます。4つのクロック・ソース(CLK0、CLK1、CLK2、CLK3)から、1つのクロックがそれぞれの入力レジスタ、パイプライン・レジスタ、および出力レジスタのために選択されます。同様に、クロック・イネーブル(CE)とリセット(RST)は各4つのソース(CE0、CE1、CE2、CE3とRST0、RST1、RST2、RST3)から入力/パイプライン/出力レジスタでそれぞれ選択されます。

### 異なる幅での符号あり・符号なし

DSPブロックはx9、x18、およびx36ビット幅以外に、符号あり・符号なしで乗算器の異なる幅をサポートします。符号なしオペランドにおいて、未使用の上位データ・ビットは、有効なx9、x18またはx36オペランドを作成するために拡張されなければなりません。符号あり2の補数オペランドにおいて、x9、x18またはx36幅に達するまで、最上位ビット(MSB)の符号拡張は実行されるべきです。表2-8はこの例を示します。

表2-8 符号拡張に関する例

| 値  | 符号なし | 符号なし<br>9-bit | 符号なし<br><b>18-bit</b> | 符号あり | 2の補数<br>符号あり <b>9-bit</b> | 2の補数<br>符号あり 18-bit |

|----|------|---------------|-----------------------|------|---------------------------|---------------------|

| +5 | 0101 | 000000101     | 00000000000000101     | 0101 | 00000101                  | 00000000000000101   |

| -6 | 0110 | 000000110     | 00000000000000110     | 1010 | 111111010                 | 111111111111111010  |

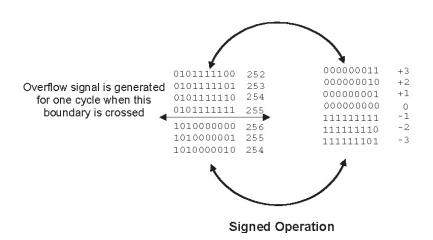

### 図2-22 アキュミュレータ・オーバフロー/アンダフロー条件

### MACからのOVERFLOWフラグ

sysDSPブロックは、アキュムレータがオーバフローしたことを示すための出力を提供します。2つの符号なし数が加えられて、結果がそれらより小さい数になった時、アキュムレータ・ロールオーバが起こったと言い、オーバフロー信号が示されます。2つの正数が加算されその和が負であるとき、または2つの負数が加算され和が正数の場合、アキュムレータ・ロールオーバが起こったと言い、そしてオーバフロー信号が示されます。オーバフロー・フラグは1サイクルだけの間存在していますので、オーバフローがいつ起こるかに注意する必要があります。FPGAロジックでこれらのオーバフロー・パルスを数えることによって、より大きいアキュムレータを構成することができます。符号ありおよび符号なしオペランドでのオーバフロー状態は図2-22でリストアップされています。

### ispLEVERモジュール・マネージャ(Module Manager)

ユーザは、それぞれのDSPモジュール(または、モジュールのグループ)を構成するオプションを持っている ispLEVERモジュール・マネージャか、或いは直接HDLインスタンス化を通してsysDSPブロックにアクセス することができます。さらにラティスは、グラフィカルなシミュレーション環境であるSimulinkツール内の インスタンス化をサポートするMathwork社とパートナになっています。SimulinkはispLEVERと共に動作して、ラティスFPGAでのDSP設計サイクルを劇的に短くします。

### 最適化されたDSP機能

ラティスは最適化されたDSP IP機能のライブラリを提供します。LatticeECP DSP用に計画されているIPのいくつかは以下の通りです。ビット相関器、高速フーリエ変換、有限インパルス応答 (FIR)フィルタ、リード・ソロモン符号器/復号器、ターボ符号器/復号器、および畳み込み符号器/復号器。利用できるDSP IPの最新のリストについてはラティスまで連絡してください。

### LatticeECPファミリで利用できるリソース

表2-9はLatticeECPファミリの各メンバーの最大乗算器数を示します。表2-10はそれぞれのLatticeECPファミリにおける利用できる最大EBR RAMブロックを示します。EBRブロックは、分散RAMと共に、高速DSP動作のために変数を局所的に格納するために用いることができます。

| 表2-9 LatticeFCPファミリにおけるDSPブロック数 | 表2-0 | LatticeFCD 7 | ファミリに | おけるDCD. | ブロック粉 |

|---------------------------------|------|--------------|-------|---------|-------|

|---------------------------------|------|--------------|-------|---------|-------|

| デバイス    | DSP ブロック | 9x9 乗算器 | 18x18乗算器 | 36x36乗算器 |

|---------|----------|---------|----------|----------|

| LFECP6  | 4        | 32      | 16       | 4        |

| LFECP10 | 5        | 40      | 20       | 5        |

| LFECP15 | 6        | 48      | 24       | 6        |

| LFECP20 | 7        | 56      | 28       | 7        |

| LFECP33 | 8        | 64      | 32       | 8        |

### 表2-10LatticeECPファミリにおけるエンベデッドSRAM

| デバイス    | EBR SRAM ブロック | 総 EBR SRAM<br>(Kbits) |

|---------|---------------|-----------------------|

| LFECP6  | 10            | 92                    |

| LFECP10 | 30            | 276                   |

| LFECP15 | 38            | 350                   |

| LFECP20 | 46            | 424                   |

| LFECP33 | 58            | 535                   |

### LatticeECPファミリのDSPの性能

表2-11はLatticeECPファミリ各メンバーの最大性能を、百万MAC毎秒(MMAC)の単位でリストしています。

表2-11 LatticeECPファミリのDSPブロック性能

| デバイス    | DSP ブロック | DSP 性能MMAC |

|---------|----------|------------|

| LFECP6  | 4        | 3680       |

| LFECP10 | 5        | 4600       |

| LFECP15 | 6        | 5520       |

| LFECP20 | 7        | 6440       |

| LFECP33 | 8        | 7360       |

sysDSPの詳しい情報に関しては、テクニカル・ドキュメンテーション(TN1050)を参照してください。

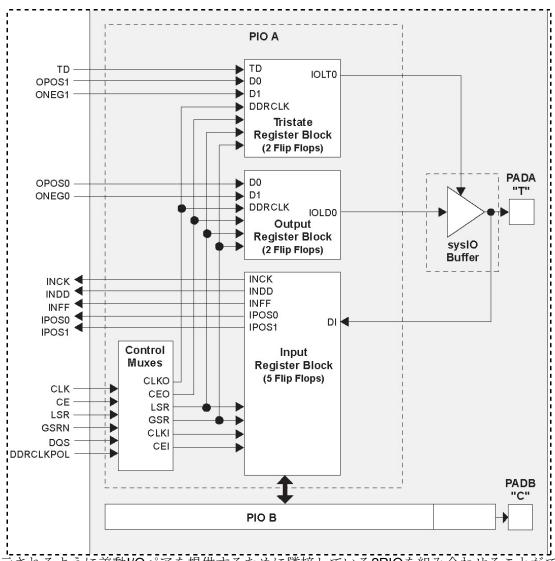

# プログラマブルI/Oセル(PIC)

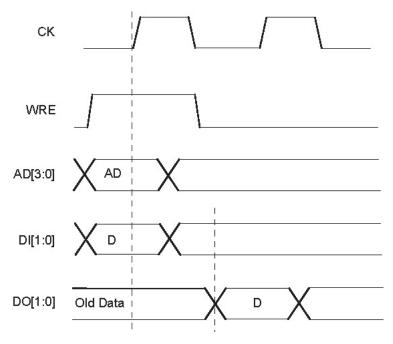

各PICは図2-23に示されるように2PIOを含んでおり、これはそれぞれのsysIOバッファにそしてパッドに接続されています。PIOブロックは出力データ(DO)とトライステート制御信号(TO)をsysIOバッファに提供し、バッファから入力を受け取ります。

#### 図2-23 PICダイヤグラム

図2-24に示されるように差動I/Oペアを提供するために隣接している2PIOを組み合わせることができます。 パッドは2PIOを区別するために"T"と"C"にラベルされます。デバイスの左・右辺のPIOペアしか送受信を LVDSに構成することができません。

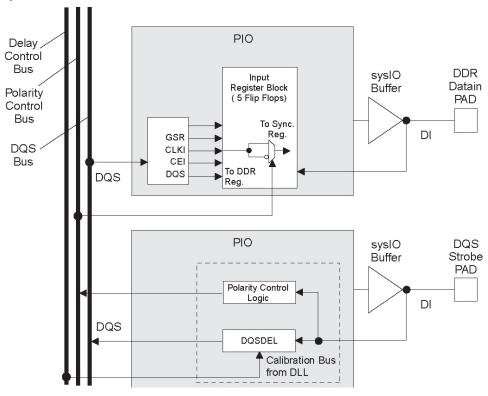

16PIO毎の1つはDQS信号の生成を容易にする遅延素子を含んでいます。DQS信号は複数の16PIOの組にまたがるDQSバスを与えます。バスからのDQS信号は、メモリからのDDRデータを入力レジスタ・ブロックにストローブするために用いられます。このインターフェイスは、8ビットのデータあたり1つのDQSストローブをサポートするメモリ用に設計されています。

LatticeECP/EC

表2-12 PIO信号リスト

| 名称           | タイプ            | 記述                                |

|--------------|----------------|-----------------------------------|

| CE0, CE1     | コアからの制御        | クロックイネーブル。入出力ブロックのFF用             |

| CLK0, CLK1   | コアからの制御        | システムクロック。入出力ブロック用                 |

| LSR          | コアからの制御        | ローカル・セット/リセット                     |

| GSRN         | 配線からの制御        | グローバル・セット/リセットt (lowアクティブ).       |

| INCK         | コアへの入力         | プライマリ・クロック・ネットへの入力、またはPLL基準入力     |

| DQS          | PIO〜の入力        | DQS信号。ロジック(配線)からPIOへ.             |

| INDD         | コアへの入力         | レジスタされないデータ入力。コアへ                 |

| INFF         | コアへの入力         | レジスタされる入力。クロック(CLKO)の立ち上がりで       |

| IPOS0, IPOS1 | コアへの入力         | DDRXレジスタされる入力。コアへ                 |

| ONEG0        | コアからの制御        | 出力信号。コアから、SDRとDDR動作用.             |

| OPOS0,       | コアからの制御        | 出力信号。コアから、DDR動作用.                 |

| OPOS1 ONEG1  | コアからのトライステート制御 | トライステート・レジスタブロックへ、DDR動作用          |

| TD           | コアからのトライステート制御 | トライステート信号。コアから、SDR動作用.            |

| DDRCLKPOL    | クロック極性バスからの制御  | DDR入力ブロックに与えられるクロック (CLK0)の極性を制御。 |

#### **図2-24 DQS配線**

#### PIO

PIOは4ブロックを含んでいます。入力レジスタ・ブロック、出力レジスタ・ブロック、トライステート・レジスタ・ブロック、および制御論理ブロックです。これらのブロックは、必要なクロックと選択ロジックと共に、シングル・データレート(SDR)とダブル・データレート(DDR)動作の両方のためのレジスタを含んで

います。入ってくるクロックとデータ信号をシフトするプログラマブル遅延線がこれらのブロックに含まれています。

#### 入力レジスタ・ブロック

入力レジスタ・ブロックはそれらがデバイス・コアに渡される前に信号を整えるために用いることができる遅延素子とレジスタを含んでいます。図**2-25**は入力レジスタ・ブロックのダイヤグラムを示します。

入力信号は(信号DIとして)sysIOバッファから入力レジスタ・ブロックに加えられます。望まれる場合、入力信号はレジスタと遅延素子をバイパスして、直接組み合わせ信号(INDD)として用いることができます。バイパス・オプションの1つが選ばれない場合、信号は最初にオプションの遅延ブロックを通り抜けます。この遅延が選択されてグローバル・クロックが用いられるとき、入力レジスタのホールド時間要件を減らします。

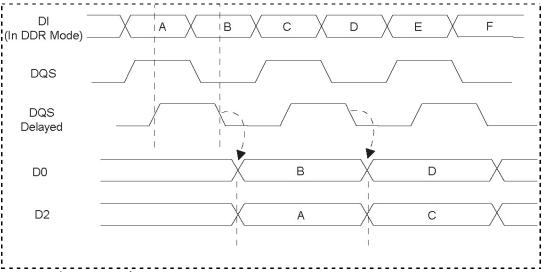

入力ブロックは2動作モードを許容します。シングル・データレート(SDR)では、データはSDR同期レジスタ・ブロック内のレジスタの1つによってシステム・クロックでサンプルされます。DDRモードでは、2つのレジスタが用いられ、DQS信号の正と負のエッジでデータをサンプルして、2本のデータ・ストリーム、D0およびD2を作ります。これらの2つのデータ・ストリームはコアに入る前にシステムクロックと同期化されます。このトピックについてのさらなる議論はこのデータシートのDDRメモリ・セクションにあります。

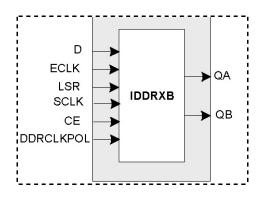

図2-26は、DDR動作の入力レジスタ波形を示し、また図2-27がデザインツール・プリミティブを示します。 SDR/SYNCレジスタには、リセットとクロック・イネーブルがあります。

信号DDRCLKPOLは同期レジスタで用いられるクロックの極性を制御します。これでDQSからシステム・クロック・ドメインまでデータを転送するとき、適切なタイミングを確実にします。このトピックについてのさらなる議論に関しては、このデータシートのDDRメモリ・セクションを参照してください。

#### (From sysIO INCK Buffer) INDD Delay Block Fixed Delay SDR & Sync **DDR Registers** Registers D0 To Routing Q D D IPOS0 D-Type D-Type /LATCH D2 IPOS1 D1 D D Q D Q D-Type D-Type D-Type /LATCH DQS Delayed (From DQS Bus) CLK<sub>0</sub> (From Routing) **DDRCLKPOL** (From DDR Polarity Control Bus

図2-25 入力レジスタ・ダイヤグラム

図2-26 入力レジスタDDR波形

図2-27 INDDRXBプリミティブ

#### 出力レジスタ・ブロック

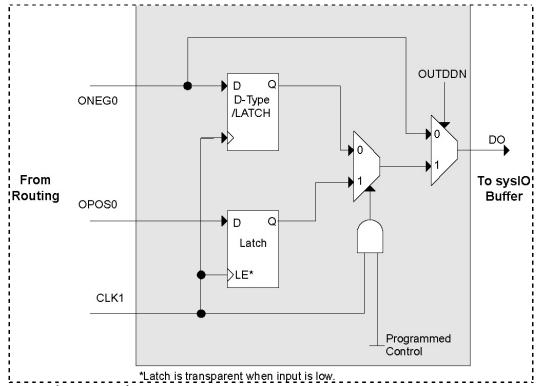

出力レジスタ・ブロックでは、信号がデバイスのコアからsyslOバッファに渡される前にサンプルすることができます。このブロックはSDR動作のためのレジスタを含んでおり、DDR動作のための追加ラッチと組み合わせられます。図2-28は出力レジスタ・ブロックのダイヤグラムを示します。

SDRモードでは、ONEG0はフリップフロップの1つに与えられ、それが出力につながります。フリップフロップは、D-タイプかラッチとして構成されます。DDRモードで、ONEG0をクロックの正のエッジで一方のレジスタに与えられ、そして、OPOS0がラッチされます。同じクロックで動作するマルチプレクサが、出力(D0)に信号を与える正しいレジスタを選択します。

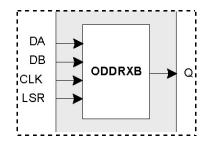

図2-29はデザインツールDDRプリミティブを示します。SDR出力レジスタにはリセットとクロック・イネーブルがあります。DDR動作のための追加レジスタにはリセットやクロック・イネーブルは利用できません。

図2-28 出力レジスタ・ブロック

図2-29 ODDRXBプリミティブ

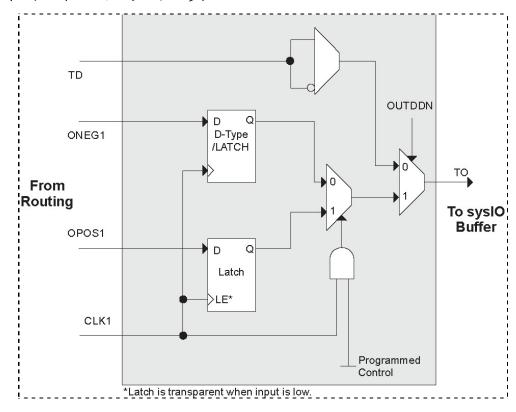

#### トライステート・レジスタ・ブロック

トライステート・レジスタ・ブロックでは、信号がデバイスのコアからsysIOバッファに渡される前にサンプルすることができます。このブロックはSDR動作のためのレジスタとDDR動作のための追加ラッチを含んでいます。図2-30はトライステート・レジスタ・ブロックのダイヤグラムを示します。

SDRモードでは、ONEG1はフリップフロップの1つに与えられ、それが出力につながります。フリップフロップは、D-タイプかラッチとして構成されます。DDRモードで、ONEG1をクロックの正のエッジで一方のレジスタに与えられ、そして、OPOS1がラッチされます。同じクロックで動作するマルチプレクサが、出力(D0)に信号を与える正しいレジスタを選択します。

### 制御ロジック・ブロック

制御ロジック・ブロックは、PIOブロック内で使用される制御信号の選択と変更を可能にします。クロックは、汎用の配線から提供されたクロック信号か、プログラマブルDQSピンから提供されたDQS信号の1つから選択されます。クロックは任意に(optionally)反転することができます。

2-25

LatticeECP/EC

図2-30 トライステート・レジスタ・ブロック

クロック・イネーブルとローカルのリセット信号は、配線から選択されて、任意に反転します。グローバルなトライステート信号はこのブロックを通り抜けます。

# DDRメモリ・サポート

高性能DDRメモリ・インターフェイスを実装することは、入力(読み出し動作のため)と出力(書き込み動作のため)で専用のDDRレジスタ構造を必要とします。PIOロジック・セクションにみられるように、ECデバイスはこの機能を提供します。これらのレジスタに加えて、ECデバイスは読み出し動作のために入力構造の設計を簡素化するために2つの要素を含んでいます。それはDQS遅延ブロックと極性制御ロジックです。

#### DLLにより較正されるDQS遅延ブロック

一般に、ソース・シンクロナス・インターフェイスは、入力レジスタで正しくデータをキャプチャするために入力クロックが調整されることを必要とします。殆んどのインターフェイスにおいてはPLLがこの調整に用いられますが、DDRメモリではクロック(DQSと呼ばれる)は、フリーランしていませんので、このアプローチを用いることができません。DQS遅延ブロックは必要なクロック・アライメントをDDRメモリ・インターフェイスに提供します。

DQS信号(特定のPIOのみ)はパッドから専用のDQS配線リソースを通してDQS遅延素子に入れられます。 DQS信号はまた、クロック極性制御ロジックにも与えられ、これは入力レジスタ・ブロック内の同期化レジスタへのクロックの極性を制御します。図2-31と図2-32 DQS転送信号がどうPIOに配線されるかを示します。

DQS遅延ブロックの温度、電圧、およびプロセス変動は、デバイスの反対側に位置する2個のDLLから与えられる1組の較正信号(6ビットのバス)によって補償されます。各DLLは図2-32に示されるようにデバイスの半分でDQS遅延を補償します。DLLループは、システム・クロックとフィードバック・ループによって温度、電圧、およびプロセス変動が補償されます。

LatticeECP/EC

### 図2-31 DQS ローカル・バス

図2-32 DLL較正(Calibration)バスとDQS/DQS転送分配

### 極性制御ロジック

典型的なDDRメモリ・インターフェイスの設計では、入力される遅れたDQSストローブと内部のシステム・クロック(リードサイクルの間)との位相関係は未知です。

LatticeECP/ECファミリはこれらドメイン間のデータ転送に専用回路を含んでいます。ドメイン転送のときにセットアップ/ホールド時間違反を防ぐため、クロック極性セレクタが使用されます。これはデータが入力レジスタ・ブロック内の同期レジスタでサンプルされるエッジを変えます。これは正しいクロック極性のためにそれぞれのリード・サイクルの始めでの評価を必要とします。

DDRメモリの読み出し動作の前に、DQSは(終端抵抗で引っ張られる)トライステート状態にあります。DDRメモリ・デバイスはプリアンブル・ステートの始めでDQSをLowにドライブします。専用回路がこの遷移を検出し、検出信号は同期レジスタへのクロック極性制御に用いられます。

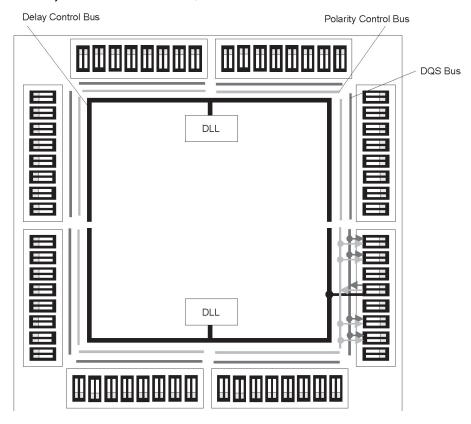

### syslOバッファ

それぞれのI/OはsysIOバッファと呼ばれるフレキシブルなバッファに関連しています。これらのバッファは、デバイスの周囲にバンクと呼ばれる8つのグループで配置されます。sysIOバッファは、ユーザはLVCMOS、SSTL、HSTL、LVDS、およびLVPECLを含む、今日のシステムで見られる広範な標準の実装を可能にします。

### syslOバッファ・バンク

LatticeECP/ECデバイスには、8つのsysIOバッファ・バンクがあります。それぞれが、複数のI/O標準をサポートすることができます。各sysIOバンクには、それ自身のI/O電源電圧( $V_{CCIO}$ )、2本の参照電圧 $V_{REF1}$ 、 $V_{REF2}$ のリソースがあり、それぞれのバンクを互いに完全に独立させることができます。図2-33は8つのバンクとそれらに関連する電源電圧を示します。

LatticeECP/ECデバイスでは、シングルエンド出力バッファとレシオ入力バッファ(LVTTL、LVCMOS、PCI、およびPCI-X)は、 $V_{CCIO}$ を用いて電源が与えられます。また、 $V_{CCIO}$ の如何にかかわらず、LVTTL、LVCMOS33、LVCMOS25、およびLVCMOS12入力には固定スレッショルドを設定することができます。バンク $V_{CCIO}$ 電源に加えて、LatticeECP/ECデバイスには $V_{CC}$ コア・ロジック電源があり、また $V_{CCAUX}$ は全ての差動バッファと参照電圧ありのバッファに電力を供給します。

各バンクは基準電圧を参照する入力バッファにスレッショルドを設定する $V_{REF}$ 電圧を最大2つ、 $V_{REF1}$ および  $V_{REF2}$ 、を別々にサポートすることができます。LatticeECP/ECデバイスでは、いくつかの専用I/Oピンをバンクにおける参照電圧ピンになるように構成することができます。それぞれのI/Oはバンクへの電源電圧と参照電圧に基づいて個別に構成可能です。

#### 図2-33 LatticeECP/ECバンク

#### 1. 上・下辺のsysIOバッファ・ペア(シングルエンド出力のみ)

デバイスの上下辺バンクにおけるsysIOバッファ・ペアは、2シングルエンド出力ドライバと2組のシング ルエンド入力バッファ(レシオ型と参照電圧使用型共に)から成ります。参照電圧ありの入力バッファは差 動入力として構成することもできます。

ペアとなる2個のパッドは"True"と"Comp"として記述されます。Trueパッドが差動入力バッファの正 側(信号)に関連していて、Comp(コンプリメンタリ)パッドが差動の入力バッファの反転側(信号)に 関連しています。

上下辺バンクのI/OにのみPCIクランプがあります。

#### 2. 左・右辺の**syslO**バッファ・ペア(差動およびシングルエンド出力)

デバイスの左右辺バンクにおけるsysIOバッファ・ペアは、2シングルエンド出力ドライバと2組のシング ルエンド入力バッファ(レシオ型と参照電圧使用型共に)、および差動出力ドライバから成ります。参照電 圧ありの入力バッファは差動入力として構成することもできます。ペアとなる2個のパッドは"True"と "Comp"として記述されます。Trueパッドが差動I/Oの正側(信号)に関連していて、Comp(コンプリメン タリ)パッドが差動のI/Oの反転側(信号)に関連しています。

左右辺のバンクにのみ、(真の) LVDSの差動出力ドライバがあります。電源投入時のI/Oリーク電流に ついては、I<sub>DK</sub>仕様値を参照して下さい(page 3-1)。

### サポートされる標準

LatticeECP/EC sysIOバッファは、シングルエンドと差動の標準を共にサポートします。シングルエンド標準はさらにLVCMOS、LVTTL、および他の標準に細分することができます。バッファはLVTTL、LVCMOS1.2/1.5/1.8/2.5/3.3V標準をサポートします。LVCMOSとLVTTLモードでは、バッファには、ドライブ強度、バス・メンテナンス(弱いプルアップ、弱いプルダウン、またはバスキーパ・ラッチ)、およびオープン・ドレインとして個別に構成可能なオプションがあります。サポートされる他のシングルエンド標準にはSSTLとHSTLを含みます。サポートされる差動の標準にはLVDS、BLVDS、LVPECL、差動SSTL、および差動HSTLが含まれます。表2-13と表2-14は、LatticeECP/ECデバイスでサポートされるI/O標準を、それらの電源電圧と参照電圧と共に示します。sysIOバッファを利用する種々標準のサポートの詳細については、テクニカル・インフォメーション(TN1056)を参照してください。

表2-13 サポートされる入力標準

| 入力標準                               | V <sub>REF</sub> (公称值) | V <sub>ccio</sub> <sup>1</sup> (公称值) |

|------------------------------------|------------------------|--------------------------------------|

| シングルエンド・インターフェイス                   |                        |                                      |

| LVTTL                              | _                      | _                                    |

| LVCMOS33 <sup>2</sup>              | _                      | _                                    |

| LVCMOS25 <sup>2</sup>              | _                      | _                                    |

| LVCMOS18                           |                        | 1.8                                  |

| LVCMOS15                           |                        | 1.5                                  |

| LVCMOS12 <sup>2</sup>              | _                      | _                                    |

| PCI                                | _                      | 3.3                                  |

| HSTL18 クラス I, II                   | 0.9                    | _                                    |

| HSTL18 クラス III                     | 1.08                   | _                                    |

| HSTL15 クラス I                       | 0.75                   | _                                    |

| HSTL15 クラス III                     | 0.9                    | _                                    |

| SSTL3 クラス I, II                    | 1.5                    | _                                    |

| SSTL2 クラス I, II                    | 1.25                   | _                                    |

| SSTL18 クラス I                       | 0.9                    | _                                    |

| 差動・インターフェイス                        |                        |                                      |

| Differential SSTL18 クラス I          |                        | _                                    |

| Differential SSTL2 クラス I, II       | _                      | _                                    |

| Differential SSTL3 クラス I, II       | _                      | _                                    |

| Differential HSTL15 クラス I, III     | _                      | _                                    |

| Differential HSTL18 クラス I, II, III | _                      | _                                    |

| LVDS, LVPECL, BLVDS, RSDS          | _                      | _                                    |

- 1. 特に明記されない場合  $V_{ccio}$  は有効な動作範囲内のどの値にも設定可能

- 2. JTAG入力は固定スレッショルド・オプションがなく、常に $V_{ccl}$ に従う

表2-14 サポートされる出力標準

| 出力標準             | ドライブ                       | V <sub>ccio</sub> (公称值) |

|------------------|----------------------------|-------------------------|

| シングルエンド・インターフェイス |                            |                         |

| LVTTL            | 4mA, 8mA, 12mA, 16mA, 20mA | 3.3                     |

| LVCMOS33         | 4mA, 8mA, 12mA 16mA, 20mA  | 3.3                     |

| LVCMOS25         | 4mA, 8mA, 12mA, 16mA, 20mA | 2.5                     |

| LVCMOS18         | 4mA, 8mA, 12mA, 16mA       | 1.8                     |

| LVCMOS15         | 4mA, 8mA                   | 1.5                     |

| LVCMOS12                  | 2mA, 6mA                  | 1.2 |

|---------------------------|---------------------------|-----|

| LVCMOS33, オープンドレイン        | 4mA, 8mA, 12mA 16mA, 20mA | _   |

| LVCMOS25, オープンドレイン        | 4mA, 8mA, 12mA 16mA, 20mA | _   |

| LVCMOS18, オープンドレイン        | 4mA, 8mA, 12mA 16mA       | _   |

| LVCMOS15, オープンドレイン        | 4mA, 8mA                  | _   |

| LVCMOS12, オープンドレイン        | 2mA, 6mA                  | _   |

| PCI33                     | N/A                       | 3.3 |

| HSTL18 クラス I, II, III     | N/A                       | 1.8 |

| HSTL15 クラス I, III         | N/A                       | 1.5 |

| SSTL3 クラス I, II           | N/A                       | 3.3 |

| SSTL2 クラス I, II           | N/A                       | 2.5 |

| SSTL18 クラス I              | N/A                       | 1.8 |

| 差動インターフェイス                |                           |     |

| 差動 SSTL3, クラス I, II       | N/A                       | 3.3 |

| 差動 SSTL2, クラス I, II       | N/A                       | 2.5 |

| 差動 SSTL18, クラス I          | N/A                       | 1.8 |

| 差動 HSTL18, クラス I, II, III | N/A                       | 1.8 |

| 差動 HSTL15, クラス I, III     | N/A                       | 1.5 |

| LVDS                      | N/A                       | 2.5 |

| BLVDS <sup>1</sup>        | N/A                       | 2.5 |

| LVPECL <sup>1</sup>       | N/A                       | 3.3 |

| RSDS <sup>1</sup>         | N/A                       | 2.5 |

<sup>1.</sup> 外部抵抗でエミュレート

# ホット・ソケッティング(活線挿抜)

パワーアップやパワーダウンの間、予測できる振舞いを確実にするようにLatticeECP/ECデバイスは入念に設計されました。電源投入は順不同にすることができます。パワーアップとパワーダウン・シーケンスの間、電源電圧が信頼できる動作を確実にすることができるくらい高くなるまで、I/Oはトライステートのままです。さらに、I/Oピンへのリークは仕様範囲内に制御されますので、これによりシステムの他部分とのインテグレーションが容易にできます。この機能でLatticeECP/ECを多くの複数電源やホットスワップのアプリケーションに理想的です。

推奨電源投入シーケンス;前のパラグラフで述べたように、供給電源の順序は任意です。しかしながら、いったん内部電源の動作状態が満たされる( $V_{CC}$ ,  $V_{CCAUX}$ , バンク3の $V_{CCIO}$ で決まる)と、その後デバイスはI/Oをトライステート状態から開放するため、I/Oの管理は設計者の責任で行う必要があります。したがってシステム設計を簡易化するためには、 $V_{CCIO}$ 、 $V_{CC}$ 、 $V_{CCAUX}$ の順序で供給することを推奨します。もし $V_{CCIO}$ が $V_{CCAUX}$ に接続されている場合、他の電源よりも $V_{CCIO}$ と関連する電源を先に供給することを推奨します。

### コンフィグレーションとテスト

以下のセクションはLatticeECP/ECファミリデバイスのコンフィグレーションとテスト機能について説明します。

### IEEEの1149.1準拠のバウンダリ・スキャン・テスタビリティ

すべてのLatticeECP/ECデバイスには、IEEE1149.1準拠のテスト・アクセス・ポート(TAP)を通してアクセスされるバウンダリ・スキャン・セルがあります。これは、すべての重要なロジック・ノードにアクセスすることができるシリアル・スキャン・パスを通して、デバイスが搭載される回路基板の機能的なテストを可能にします。内部レジスタはリンクされており、テストデータがシフトインされて直接テスト・ノードにロードされるか、または検証のためにテストデータをキャプチャしてシフトアウトすることができます。テスト・アクセス・ポートはTDI、TDO、TCK、およびTMSの専用I/Oから成ります。テスト・アクセス・ポートは、それ自身の電源電圧V<sub>CCI</sub>を持っていて、LVCMOS3.3/2.5/1.8/1.5/1.2の標準で動作することができます。

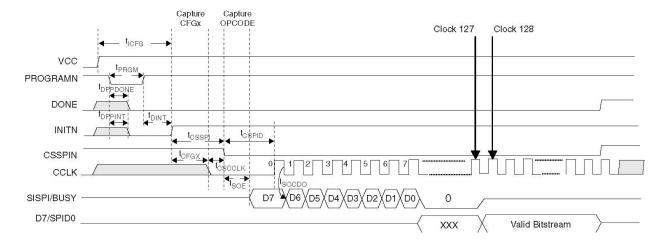

### デバイス・コンフィグレーション

すべてのLatticeECP/ECデバイスがデバイス・コンフィグレーションに用いることができる2つのポートを含んでいます。TAPはビット幅のコンフィグレーション、およびsysCONFIGポートはバイト幅かシリアル・コンフィグレーションをサポートします。

TAPは、IEEE標準1149.1バウンダリ・スキャン仕様とIEEE標準1532のインシステム・コンフィグレーション 仕様の両方をサポートします。sysCONFIGポートは20ピンのインターフェイスで、6ピンの専用I/Oと、複数 用途の残りのピンよりなります。sysCONFIGモードが使用されないとき、これらの複数用途のピンは汎用I/O として利用できます。LatticeECP/ECデバイスには4つのコンフィグレーション・オプションがあります。

- 1. 業界基準SPIメモリ

- 2. 業界基準のバイト幅フラッシュと制御・アドレシング用のispMACH4000

- 3. コンフィグレーション・バスかTAPを通してシステムのマイクロプロセッサから

- 4. 業界基準のFPGAボード・メモリ

パワーアップするとき、sysCONFIGポートがアクティブな状態でFPGA SRAMは構成される準備ができています。IEEE1149.1シリアル・モードは、パワーアップ後にTAPポートを通して適切なコマンドを送ることによっていつでも活性化することができます。コンフィグレーション・ポートがいったん選択されると、そのポートはロックされ、次のパワーアップ・シーケンスまで別のコンフィグレーション・ポートは動作させることはできません。

デバイス・コンフィグレーションの詳しい情報に関しては、テクニカル・ドキュメンテーション (TN1053) を参照してください。

### ロジック・アナライザ機能(ispTRACY)

すべてのLatticeECP/ECデバイスにロジック・アナライザ診断機能を組み込むことができます。診断機能は プログラマブル・イベント/トリガ条件や深いトレースメモリのような、外部に接続するロジック・アナライ ザと同様の機能を提供します。この機能はラティスのispTRACYによってイネーブルされ、ispTRACYユーティリティはコンパイル時にユーザの設計に加えられます。

ispTRACYの詳しい情報に関しては、テクニカル・ドキュメンテーション(TN1054)を参照してください。

#### 外部抵抗

LatticeECP/ECデバイスはXRESピンとグランド間に $10K\Omega+/-1\%$ の抵抗一本を必要とします。この抵抗がないと、デバイス・コンフィグレーションは終了しません。外部抵抗パッドにはバウンダリ・スキャン・レジスタはありません。

### オシレータ

全LatticeECP/ECデバイスが、コンフィグレーション用のマスタシリアル・クロックを得るために用いられる内部CMOSオシレータを持っています。オシレータとマスタシリアル・クロックは連続して動作します。マスタシリアル・クロックのデフォルト値は2.5MHzです。表2-15は利用できるすべてのマスタシリアル・クロック周波数を記載します。デザインの過程で異なるマスタシリアル・クロックが選択されるとき、以下のシーケンスが行われます。

- 1. ユーザは異なるマスタシリアル・クロック周波数を選択します。

- 2. コンフィグレーションの間、デバイスはデフォルト(2.5MHz)マスタシリアル・クロック周波数から始まります。

- 3. クロック・コンフィグレーション設定はコンフィグレーション・ビット・ストリームの初めに含まれています。

- **4.** クロック・コンフィグレーション・ビットがいったん受け取られると、マスタシリアル・クロック周波数は選択された周波数に変化します。

コンフィグレーション用オシレータの詳しい情報に関しては、テクニカル・ドキュメンテーション (TN1053) を参照してください。

表2-15 コンフィグレーションの間の選択可能なマスタシリアル・クロック(CCLK)周波数

| CCLK (MHz) | CCLK (MHz) | CCLK (MHz) |

|------------|------------|------------|

| 2.5(デフォルト) | 13         | 45         |

| 4.3        | 15         | 51         |

| 5.4        | 20         | 55         |

| 6.9        | 26         | 60         |

| 8.1        | 30         | 130        |

| 9.2        | 34         | _          |

| 10.0       | 41         | _          |

# ロジック集積度の移行(マイグレーション)

同じパッケージで異なるロジック集積度のデバイスが同じピン配置であることを保証するようにLatticeECP/ECファミリは設計されてあります。さらにアーキテクチャは、小さいロジック集積度のデバイスからより大きいロジック集積度のデバイスに設計のマイグレーションを行うときに、高い成功率を確実にします。また多くの場合、高密度デバイスの低い使用効率の設計を、小さいロジック集積度のデバイスにターゲットを移行させることも可能です。しかしながら、最終的なリソース使用効率の正確な詳細は、それぞれのケースで成功の確からしさに影響を与えるでしょう。

# LatticeECP/ECファミリデータシート DCおよびスイッチング特性

# 絶対最大定格123

| 電源電圧 V <sub>CC</sub>                    | 0.5 $\sim$ 1.32V |

|-----------------------------------------|------------------|

| 電源電圧 V <sub>CCAUX</sub>                 | 0.5 ~ 3.75V      |

| 電源電圧 V <sub>CCJ</sub>                   | 0.5 ~ 3.75V      |

| 出力電源電圧 <b>V</b> <sub>CCIO</sub>         | 0.5 ~ 3.75V      |

| 加えられる入力電圧1                              | 0.5 ~ 4.25V      |

| 加えられる <b>I/O</b> トライステート電圧 <sup>4</sup> | 0.5 ~ 3.75V      |

| 保存温度(周囲)                                | 65 ∼ 150°C       |

| ジャンクション温度 <b>(Tj)</b>                   | +125°C           |

<sup>1 &</sup>quot;絶対最大定格"で記載された以上のストレスはデバイスに永久的な損傷を引き起こすかもしれません。これら条件下で、或 いはこれら仕様項目の推奨動作条件セクションで示される以外のいかなる他の条件下で、デバイスの機能的な動作を暗示する ものではありません。

- 2 ラティス"Thermal Management" (熱管理) ドキュメントに従うことが必要です。

- 3 全ての電圧はGND基準です

- 4-2V~(V<sub>THMAX</sub> + 2)Vまでのオーバシュートとアンダシュートは <20nsの期間は許容されます。

## 推奨動作条件

| シンボル                              | パラメータ                      | Min.  | Max.  | 単位                      |

|-----------------------------------|----------------------------|-------|-------|-------------------------|

| V <sub>CC</sub>                   | コア電源電圧                     | 1.14  | 1.26  | V                       |

| $V_{CCAUX}$                       | 補助(Auxiliary)電源電圧          | 3.135 | 3.465 | V                       |

| V <sub>CCIO</sub> <sup>1, 2</sup> | I/Oドライバ電源電圧                | 1.140 | 3.465 | V                       |

| V <sub>CCJ</sub> <sup>1</sup>     | IEEE1149.1テスト・アクセス・ポート電源電圧 | 1.140 | 3.465 | V                       |

| t <sub>JCOM</sub>                 | ジャンクション温度、コマーシャル動作         | 0     | +85   | $^{\circ}\! \mathbb{C}$ |

| $t_{JIND}$                        | ジャンクション温度、インダストリアル動作       | -40   | 100   | $^{\circ}\!\mathbb{C}$  |

- 1. VccioかVcc」が1.2Vに設定される場合、それらはVccと同じ電源に接続のこと。 VccioかVcciが3.3Vに設定される場合、それらはVccauxと同じ電源に接続のこと。

- 2. 後の表におけるI/O標準毎の推奨電圧を参照のこと。

# ホット・ソケッティング(活線挿抜)仕様1234

| シンボル               | パラメータ                            | 条件                              | Min. | Тур. | Max     | 単位 |  |  |

|--------------------|----------------------------------|---------------------------------|------|------|---------|----|--|--|

| I <sub>DK</sub>    | 入力、I/Oのリーク電流                     | $0 \le V_{IN} \le V_{IH} (MAX)$ | _    | _    | +/-1000 | uA |  |  |

| 左右辺I/Oバン           | 左右辺I/Oバンクの汎用sysIOポート(バンク2、3、6、7) |                                 |      |      |         |    |  |  |

|                    | 入力、 <b>I/O</b> のリーク電流            | $V_{IN} \leq V_{IH} (MAX)$      | _    | _    | +/-1000 | uA |  |  |

| I <sub>DK_LR</sub> | 八月、1/0のサーク電流                     | $V_{IN} \ge V_{IH} (MAX)$       | _    | 35   | _       | mA |  |  |

$<sup>1\,</sup>V_{CC}$ 、 $V_{CCAUX}$  及び  $V_{CCIO}$  のシーケンスは順不同。ただし、いずれも単調増加・降下レートであることが必要

$<sup>2.0 \</sup>le V_{CC} \le V_{CC}$  (MAX)、 $0 \le V_{CCIO} \le V_{CCIO}$  (MAX)、または  $0 \le V_{CCAUX} \le V_{CCAUX}$  (MAX)  $3~I_{DK}$  は  $I_{PU}$  、 $I_{PW}$  、または  $I_{BH}$  に加算される

<sup>4</sup> LVCMOSとLVTTLにて測定した値に基づく

# DC電気的特性

| シンボル                                          | パラメータ                            | 条件                                                                                         | Min.                  | Тур. | Max.                  | 単位 |

|-----------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|----|

| I <sub>IL,</sub> I <sub>IH</sub> <sup>1</sup> | <br> 入力、 <b>I/O</b> のリーク電流       | $0 \le V_{IN} \le (V_{CCIO} - 0.2V)$                                                       | _                     |      | 10                    | uA |

| IIL, IIH                                      |                                  | $(V_{CCIO} - 0.2V) \leq V_{IN} \leq 3.6V$                                                  | _                     |      | 40                    | uA |

| I <sub>PU</sub>                               | I/Oアクティブ・プルアップ電流                 | $0 \le V_{IN} \le 0.7 V_{CCIO}$                                                            | 30                    |      | 150                   | uA |

| $I_{PD}$                                      | I/Oアクティブ・プルダウン電流                 | $V_{IL}$ (MAX) $\leq V_{IN} \leq V_{IH}$ (MAX)                                             | -30                   |      | -150                  | uA |

| I <sub>BHLS</sub>                             | バスホールドLow維持電流                    | $V_{IN} = V_{IL} (MAX)$                                                                    | 30                    |      |                       | uA |

| I <sub>BHHS</sub>                             | バスホールドHigh維持電流                   | $V_{IN} = 0.7V_{CCIO}$                                                                     | -30                   |      | _                     | uA |

| I <sub>BHLO</sub>                             | バスホールドLowオーバドライブ<br>電流           | $0 \le V_{IN} \le V_{IH} (MAX)$                                                            | _                     | _    | 150                   | uA |

| I <sub>BHLH</sub>                             | バスホールド <b>High</b> オーバドライブ<br>電流 | $0 \le V_{IN} \le V_{IH} (MAX)$                                                            | _                     | _    | -150                  | uA |

| V <sub>BHT</sub>                              | バスホールド・トリップ・ポイン<br>ト             | $0 \le V_{IN} \le V_{IH} (MAX)$                                                            | V <sub>IL</sub> (MAX) | _    | V <sub>IH</sub> (MIN) | ٧  |

| C1                                            | I/O容量 <sup>2</sup>               | $V_{CCIO}$ = 3.3V, 2.5V, 1.8V, 1.5V, 1.2V, $V_{CC}$ = 1.2V, $V_{IO}$ = 0 to $V_{IH}$ (MAX) | _                     | 8    | _                     | pf |

| C2                                            | 専用入力の容量 <sup>2</sup>             | $V_{CCIO}$ = 3.3V, 2.5V, 1.8V, 1.5V, 1.2V, $V_{CC}$ = 1.2V, $V_{IO}$ = 0 to $V_{IH}$ (MAX) | _                     | 6    | _                     | pf |

<sup>1.</sup> 入力やI/Oのリーク電流は、出力ドライバをトライステートにし、ピンは入力として、またはI/Oとして構成して測定される。出力ドライバがアクティブな状態では測定されない。バスメンテナンス回路はディセーブルされる。

<sup>2.</sup>  $T_A 25^{\circ}C$ , f = 1.0MHz

# 供給電流(スタンバイ時)<sup>1234</sup>

| シンボル               | パラメータ                 | 条件                                                                                               | Typ. <sup>5</sup> | Max. | 単位 |

|--------------------|-----------------------|--------------------------------------------------------------------------------------------------|-------------------|------|----|

|                    |                       | LFEC1                                                                                            |                   |      | mA |

|                    |                       | LFEC3                                                                                            |                   |      | mA |

|                    |                       | LFEC6/LFECP6                                                                                     | 14                |      | mA |

| I <sub>CC</sub>    | コア電源電流                | LFEC10/LFECP10                                                                                   |                   |      | mA |

|                    |                       | LFEC15/LFECP15                                                                                   |                   |      | mA |

|                    |                       | LFEC20/LFECP20                                                                                   | 60                | mA   |    |

|                    |                       | LFEC33/LFECP33                                                                                   |                   |      | mA |

|                    |                       | LFEC1                                                                                            |                   |      | mA |

|                    |                       | LFEC3                                                                                            |                   |      | mA |

|                    |                       | LFEC6/LFECP6                                                                                     | 15                |      | mA |

| I <sub>CCAUX</sub> | 補助(Auxiliary)電源電流     | LFEC10/LFECP10                                                                                   |                   |      | mA |

|                    |                       | LFEC15/LFECP15                                                                                   |                   |      | mA |

|                    |                       | LFEC20/LFECP20                                                                                   | 15                |      | mA |

|                    |                       | LFEC33/LFECP33                                                                                   |                   |      | mA |

| I <sub>CCPLL</sub> | PLL電源電流               | LFEC1, LFEC3, LFEC6/LFECP6,<br>LFEC10/LFECP10, LFEC15/LFECP15,<br>LFEC20/LFECP20, LFEC33/LFECP33 | 5                 |      | mA |

| I <sub>CCIO</sub>  | バンク電源電流               |                                                                                                  | 2                 |      | mA |

| I <sub>CCJ</sub>   | V <sub>CCJ</sub> 電源電流 |                                                                                                  | 5                 |      | mA |

- 1 供給電流についてのさらなる情報については、このデータシートの後ろの付加的技術情報の詳細を参照のこと。 2 全出力はトライステート、全入力はLVCMOSに構成されてV<sub>CCIO</sub>またはGNDに固定されていると仮定。

- 3 周波数 0MHz.

- 4 パターンは標準的な設計例をとり、ロジックが65%、EBRが55%、配線が10%使用されたものとする。5 Tj=25%、電源電圧は標準値

- 6 バンク当り

# 初期化供給電流123456

| シンボル               | パラメータ                 | 条件                                                                                               | Typ. <sup>6</sup> | Max. | 単位 |

|--------------------|-----------------------|--------------------------------------------------------------------------------------------------|-------------------|------|----|

|                    |                       | LFEC1                                                                                            |                   |      | mA |

|                    |                       | LFEC3                                                                                            |                   |      | mA |

|                    |                       | LFEC6/LFECP6                                                                                     | 25                |      | mA |

| Icc                | コア電源電流                | LFEC10/LFECP10                                                                                   |                   |      | mA |

|                    |                       | LFEC15/LFECP15                                                                                   |                   |      | mA |

|                    |                       | LFEC20/LFECP20                                                                                   | 150               |      | mA |

|                    |                       | LFEC33/LFECP33                                                                                   |                   |      | mA |

|                    |                       | LFEC1                                                                                            |                   |      | mA |

|                    |                       | LFEC3                                                                                            |                   |      | mA |

|                    |                       | LFEC6/LFECP6                                                                                     | 15                |      | mA |

| I <sub>CCAUX</sub> | 補助(Auxiliary)電源電流     | LFEC10/LFECP10                                                                                   |                   |      | mA |

|                    |                       | LFEC15/LFECP15                                                                                   |                   |      | mA |

|                    |                       | LFEC20/LFECP20                                                                                   | 25                |      | mA |

|                    |                       | LFEC33/LFECP33                                                                                   |                   |      | mA |

| I <sub>CCPLL</sub> | PLL電源電流               | LFEC1, LFEC3, LFEC6/LFECP6,<br>LFEC10/LFECP10, LFEC15/LFECP15,<br>LFEC20/LFECP20, LFEC33/LFECP33 | 12                |      | mA |

| Iccio              | バンク電源電流 <sup>7</sup>  |                                                                                                  | 10                |      | mA |

| I <sub>CCJ</sub>   | V <sub>CCJ</sub> 電源電流 |                                                                                                  | 10                |      | mA |

- 1 DONE信号がアクティブになるまで

- 2 供給電流についてのさらなる情報については、このデータシートの後ろの付加的技術情報の詳細を参照のこと。 3 全出力はトライステート、全入力はLVCMOSに構成されて $V_{CCIO}$ またはGNDに固定されていると仮定。

- 5 パターンは標準的な設計例をとり、ロジックが65%、EBRが55%、配線が10%使用されたものとする。

- 6 Tj=25℃、電源電圧は標準値

- 7 バンク当り

# sysIO推奨動作条件

| +## 'X##            |       | V <sub>CCIO</sub> |       |      | V <sub>REF</sub> (V) |      |

|---------------------|-------|-------------------|-------|------|----------------------|------|

| 標準                  | Min.  | Тур.              | Max.  | Min. | Тур.                 | Max. |

| LVCMOS 3.3          | 3.135 | 3.3               | 3.465 | _    | _                    | _    |

| LVCMOS 2.5          | 2.375 | 2.5               | 2.625 | _    | _                    | _    |

| LVCMOS 1.8          | 1.71  | 1.8               | 1.89  | _    | _                    | _    |

| LVCMOS 1.5          | 1.425 | 1.5               | 1.575 | _    | _                    | _    |

| LVCMOS 1.2          | 1.14  | 1.2               | 1.26  | _    | _                    | _    |

| LVTTL               | 3.135 | 3.3               | 3.465 | _    | _                    | _    |

| PCI                 | 3.135 | 3.3               | 3.465 | _    | _                    | _    |

| SSTL18 クラス I        | 1.71  | 2.5               | 1.89  | 1.15 | 1.25                 | 1.35 |

| SSTL2 クラス I, II     | 2.375 | 2.5               | 2.625 | 1.15 | 1.25                 | 1.35 |

| SSTL3 クラス I, II     | 3.135 | 3.3               | 3.465 | 1.3  | 1.5                  | 1.7  |

| HSTL15 クラス I        | 1.425 | 1.5               | 1.575 | 0.68 | 0.75                 | 0.9  |

| HSTL15 クラス III      | 1.425 | 1.5               | 1.575 | _    | 0.9                  | _    |

| HSTL 18 クラス I, II   | 1.71  | 1.8               | 1.89  | _    | 0.9                  | _    |

| HSTL 18 クラス III     | 1.71  | 1.8               | 1.89  | _    | 1.08                 | _    |

| LVDS                | 2.375 | 2.5               | 3.625 |      |                      |      |

| LVPECL <sup>1</sup> | 3.135 | 3.3               | 3.465 | _    | _                    |      |

| BLVDS <sup>1</sup>  | 2.375 | 2.5               | 2.625 |      |                      |      |

<sup>1.</sup> チップに対する入力。出力は外部抵抗を加えて実装する

# シングルエンドsysIO DC電気的特性

| 入出力標準         | V <sub>IL</sub> |                          | V <sub>IH</sub>          |          | V <sub>OL</sub> Max. | V <sub>OH</sub> Min.     | I <sub>OL</sub> <sup>1</sup> | I <sub>OH</sub> <sup>1</sup> |

|---------------|-----------------|--------------------------|--------------------------|----------|----------------------|--------------------------|------------------------------|------------------------------|

| 八山刀保华         | Min. (V)        | Max. (V)                 | Min. (V)                 | Max. (V) | (V)                  | (V)                      | (mA)                         | (mA)                         |

| LVCMOS 3.3    | -0.3            | 0.8                      | 2.0                      | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 20, 16, 12,<br>8, 4          | -20, -16, -12,<br>-8, -4     |

|               |                 |                          |                          |          | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                          | -0.1                         |

| LVTTL         | -0.3            | 0.8                      | 2.0                      | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 20, 16, 12,<br>8, 4          | -20, -16, -12,<br>-8, -4     |

|               |                 |                          |                          |          | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                          | -0.1                         |

| LVCMOS 2.5    | -0.3            | 0.7                      | 1.7                      | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 20, 16, 12,<br>8, 4          | -20, -16, -12,<br>-8, -4     |

|               |                 |                          |                          |          | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                          | -0.1                         |

| LVCMOS 1.8    | -0.3            | 0.25\/                   | 0.65V <sub>CCIO</sub>    | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 16, 12, 8, 4                 | -16, -12, -8, -4             |

| LVCIVIOS 1.6  | -0.3            | 0.35V <sub>CCIO</sub>    | 0.63 V CCIO              | 3.0      | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                          | -0.1                         |

| LVCMOS 1.5    | -0.3            | 0.35V <sub>CCIO</sub>    | 0.65V <sub>CCIO</sub>    | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 8, 4                         | -8, -4                       |

| LVCIVIOS 1.5  | -0.3            | 0.33 V CCIO              | 0.03 A CCIO              | 3.0      | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                          | -0.1                         |

| LVCMOS 1.2    | -0.3            | 0.35V <sub>CC</sub>      | 0.65V <sub>CC</sub>      | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 6, 2                         | -6, -2                       |

| LVCIVIOS 1.2  | -0.3            | 0.33VCC                  | 0.03 V CC                | 3.0      | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                          | -0.1                         |

| PCI           | -0.3            | $0.3V_{\text{CCIO}}$     | 0.5V <sub>CCIO</sub>     | 3.6      | 0.1V <sub>CCIO</sub> | 0.9V <sub>CCIO</sub>     | 1.5                          | -0.5                         |

| SSTL3 クラス I   | -0.3            | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 3.6      | 0.7                  | V <sub>CCIO</sub> - 1.1  | 8                            | -8                           |

| SSTL3 クラス II  | -0.3            | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 3.6      | 0.5                  | V <sub>CCIO</sub> - 0.9  | 16                           | -16                          |

| SSTL2 クラス I   | -0.3            | V <sub>REF</sub> - 0.18  | V <sub>REF</sub> + 0.18  | 3.6      | 0.54                 | V <sub>CCIO</sub> - 0.62 | 7.6                          | -7.6                         |

| SSTL2 クラス II  | -0.3            | V <sub>REF</sub> - 0.18  | V <sub>REF</sub> + 0.18  | 3.6      | 0.35                 | V <sub>CCIO</sub> - 0.43 | 15.2                         | -15.2                        |

| SSTL18 クラス I  | -0.3            | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 6.7                          | -6.7                         |

| HSTL15 クラス I  | -0.3            | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 8                            | -8                           |

| HSTL15クラス III | -0.3            | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 24                           | -8                           |

| HSTL18クラス I   | -0.3            | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 9.6                          | -9.6                         |

| HSTL18クラス II  | -0.3            | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 16                           | -16                          |

| HSTL18 クラスⅢ   | -0.3            | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 24                           | -8                           |

<sup>1.</sup> ロジック信号接続表で示されるように、I/OによってGND接続の間、あるいはのI/Oバンクの端の最後のGNDとI/Oバンク間を流れる平均DC電流は、n\*8mAを超えないものとします。ここでnはバンクGND接続か、バンクの最後のGNDとバンク端の間のI/O数です。

(The average DC current drawn by I/Os between GND connections, or between the last GND in an I/O bank and the end of an I/O bank, as shown in the logic signal connections table shall not exceed n \* 8mA. Where n is the number of I/Os between bank GND connections or between the last GND in a bank and the end of a bank.)

# 差動syslO電気的特性

# LVDS

| パラメータ<br>シンボル                       | パラメータ記述                                    | テスト条件                                                          | Min.                | Тур. | Max.  | 単位 |

|-------------------------------------|--------------------------------------------|----------------------------------------------------------------|---------------------|------|-------|----|

| V <sub>INP</sub> , V <sub>INM</sub> | 入力電圧                                       |                                                                | 0                   | _    | 2.4   | V  |

| $V_{THD}$                           | 差動の入力スレッショルド                               |                                                                | +/-100              | _    | _     | mV |

|                                     |                                            | $100 \text{mV} \leq V_{THD}$                                   | V <sub>THD</sub> /2 | 1.2  | 1.8   | V  |

| $V_{CM}$                            | 入力コモンモード電圧                                 | $200 \text{mV} \leq V_{THD}$                                   | V <sub>THD</sub> /2 | 1.2  | 1.9   | V  |

|                                     |                                            | $350 \text{mV} \leq V_{THD}$                                   | V <sub>THD</sub> /2 | 1.2  | 2.0   | V  |

| I <sub>IN</sub>                     | 入力電流                                       | パワーオン、またはオフ                                                    | _                   | _    | +/-10 | uA |

| V <sub>OH</sub>                     | V <sub>OP</sub> かV <sub>OM</sub> の出力High電圧 | R <sub>T</sub> = 100 Ohm                                       | _                   | 1.38 | 1.60  | V  |

| V <sub>OL</sub>                     | V <sub>OP</sub> かV <sub>OM</sub> の出力Low電圧  | R <sub>T</sub> = 100 Ohm                                       | 0.9V                | 1.03 | _     | V  |

| V <sub>OD</sub>                     | 出力差動電圧                                     | (V <sub>OP</sub> - V <sub>OM</sub> ), R <sub>T</sub> = 100 Ohm | 250                 | 350  | 450   | mV |

| $\Delta V_{OD}$                     | HighとLow間のV <sub>OD</sub> の変化              |                                                                | _                   | _    | 50    | mV |

| Vos                                 | 出力電圧オフセット                                  | $(V_{OP} - V_{OM})/2$ , $R_T = 100 \text{ Ohm}$                | 1.125               | 1.25 | 1.375 | V  |

| $\Delta V_{OS}$                     | HとLの間のVos VOSの変化                           |                                                                | _                   | _    | 50    | mV |

| I <sub>OSD</sub>                    | 出力短絡電流                                     | $V_{OD} = 0V$ 、ドライバ出力をショート                                     | _                   | _    | 6     | mA |

## 差動のHSTLとSSTL

差動のHSTLとSSTL出力は1組のコンプリメンタリなシングルエンド出力として実装されます。すべての許容できるシングルエンド出力クラス(クラスIとクラスII)がこのモードでサポートされます。

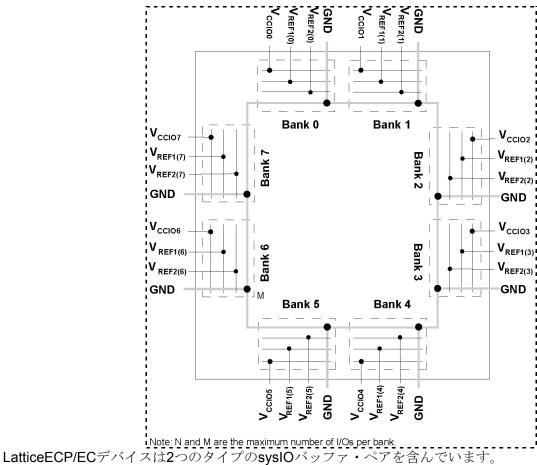

### LVDS25E

LatticeECP/ECデバイスの上下辺I/Oバンクは、コンプリメンタリなLVCMOS出力を外部抵抗とともに用いることで、LVDSをサポートします。図3-1で示すのはポイント・ツー・ポイント接続時の一つの構成例です。

## 図3-1 LVDS25E出力終端の例

### 表3-1 LVDS25EのDC条件

| パラメータ             | 記述          | 標準値  | 単位 |

|-------------------|-------------|------|----|

| V <sub>OH</sub>   | 出力High電圧    | 1.42 | V  |

| V <sub>OL</sub>   | 出力Low電圧     | 1.08 | V  |

| V <sub>OD</sub>   | 出力差動電圧      | 0.35 | V  |

| V <sub>CM</sub>   | 出力コモンモード電圧  | 1.25 | V  |

| Z <sub>BACK</sub> | バック・インピーダンス | 100  | Ω  |

## **BLVDS**

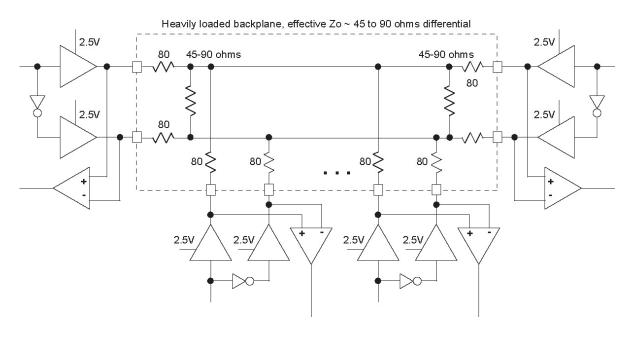

LatticeECP/ECデバイスは、BLVDS標準をサポートします。この標準は、ドライバ出力間のパラレル外部抵抗と共にコンプリメンタリなLVCMOS出力を用いることでエミュレートされます。BLVDSはマルチドロップで双方向のマルチポイント差動シグナリングが必要な時に用いられることを意図しています。図3-2で示されるスキームは、双方向のマルチポイント差動信号のための1つの可能なソリューションです。

### 図3-2 BLVDSマルチポイント出力の例

### 表3-1 BLVDS直流条件

推奨動作条件にわたって

| パラメータ               | 記述                | Тур     | 単位      |          |

|---------------------|-------------------|---------|---------|----------|

|                     | 記处                | Zo = 45 | Zo = 90 | 中亚       |

| Z <sub>OUT</sub>    | 出力インピーダンス         | 100     | 100     | ohm      |

| R <sub>TLEFT</sub>  | 左端の終端             | 45      | 90      | ohm      |

| R <sub>TRIGHT</sub> | 右端の終端             | 45      | 90      | ohm      |

| $V_{OH}$            | 出力 <b>High</b> 電圧 | 1.375   | 1.48    | V        |

| $V_{OL}$            | 出力Low電圧           | 1.125   | 1.02    | <b>V</b> |

| $V_{OD}$            | 出力差動電圧            | 0.25    | 0.46    | V        |

| V <sub>CM</sub>     | 出力コモンモード電圧        | 1.25    | 1.25    | V        |

| I <sub>DC</sub>     | DC出力電流            | 11.2    | 10.2    | mA       |

<sup>1.</sup> 入力バッファに関しては、LVDS表を参照してください

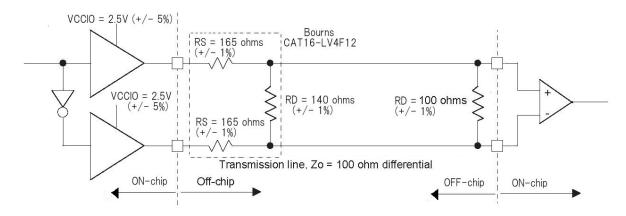

## **LVPECL**

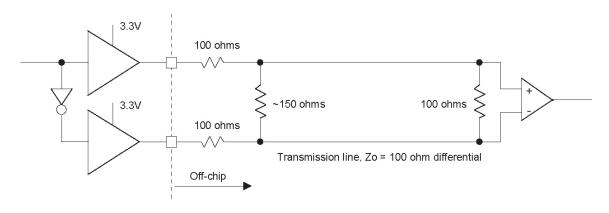

LatticeECP/ECデバイスは、差動LVPECL標準をサポートします。この標準は、ドライバ出力間のパラレル外部抵抗と共にコンプリメンタリなLVCMOS出力を用いることでエミュレートされます。図3-3で示されるスキームは、ポイント・ツー・ポイント信号のための1つの可能なソリューションです。

## 図3-3 差動LVPECL

### 表3-2 LVPECL直流条件1

### 推奨動作条件にわたって

| パラメータ             | 記述          | Typical | 単位  |

|-------------------|-------------|---------|-----|

| Z <sub>OUT</sub>  | 出力インピーダンス   | 100     | ohm |

| R <sub>P</sub>    | ドライバのパラレル抵抗 | 150     | ohm |

| R <sub>T</sub>    | レシーバ終端      | 100     | ohm |

| V <sub>OH</sub>   | 出力High電圧    | 2.03    | V   |

| V <sub>OL</sub>   | 出力Low電圧     | 1.27    | V   |

| V <sub>OD</sub>   | 出力差動電圧      | 0.76    | V   |

| V <sub>CM</sub>   | 出力コモンモード電圧  | 1.65    | V   |

| Z <sub>BACK</sub> | バック・インピーダンス | 85.7    | ohm |

| I <sub>DC</sub>   | DC出力電流      | 12.7    | mA  |

<sup>1.</sup> 入力バッファに関しては、LVDS表を参照してください。

LVPECL、BLVDS、および他の差動のインターフェイスの詳細に関しては、テクニカルドキュメンテーション (TN1056) を参照してください。

3-10

LatticeECP/EC

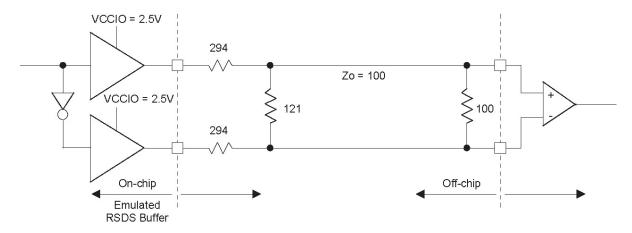

## **RSDS**

LatticeECP/ECデバイスは、差動RSDS標準をサポートします。この標準は、ドライバ出力間のパラレル外部抵抗と共にコンプリメンタリなLVCMOS出力を用いることでエミュレートされます。図3-4に示されたスキームはRSDS標準の実装のための1つの可能なソリューションです。RSDS動作には推奨抵抗値でLVDS25Eモードを用いてください。図3-3における抵抗値は1%偏差の業界標準値です。

## **⊠**3-4 RSDS (Reduced Swing Differential Standard)

## 表3-3 RSDS DC条件

| パラメータ             | 記述          | Typical | 単位  |

|-------------------|-------------|---------|-----|

| Z <sub>OUT</sub>  | 出力インピーダンス   | 20      | ohm |

| Rs                | ドライバ・シリーズ抵抗 | 294     | ohm |

| $R_P$             | ドライバ・パラレル抵抗 | 121     | ohm |

| $R_T$             | レシーバ終端      | 100     | ohm |

| $V_{OH}$          | 出力 High 電圧  | 1.35    | V   |

| $V_{OL}$          | 出力 Low 電圧   | 1.15    | V   |

| $V_{OD}$          | 出力差動電圧      | 0.20    | V   |

| $V_{CM}$          | 出力コモンモード電圧  | 1.25    | V   |

| Z <sub>BACK</sub> | バック・インピーダンス | 101.5   | ohm |

| I <sub>DC</sub>   | DC 出力電流     | 3.66    | mA  |

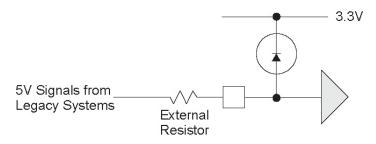

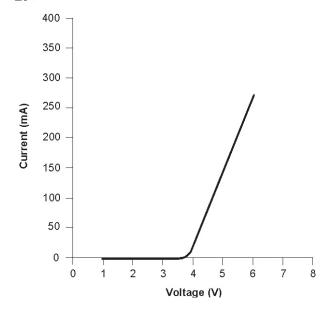

# 5V許容の入力バッファ

デバイスのLatticeECP/ECファミリの入力バッファは、図3-5で示されるようにPCIクランプと外部のシリーズ抵抗を用いて5V信号をサポートすることができます。図3-6で示されるようなPCIクランプ特性を用いることによって、適切な抵抗を選択することができます。

## 図3-5 5V許容の入力バッファ

## 図3-6 典型的なPCIクランプ電流

# 典型的なビルディング・ブロック機能パフォーマンス

# ピン・ピン間のパフォーマンス(LVCMOS25 12mAドライブ)

| 機能                      | -5 タイミング | 単位 |

|-------------------------|----------|----|

| 基本機能                    |          |    |

| 16ビット・デコーダ              | 6.2      | ns |

| 32ビット・デコーダ              | 7.2      | ns |

| 64ビット・デコーダ              | 7.7      | ns |

| 4:1 MUX                 | 4.8      | ns |

| 8:1 MUX                 | 5.1      | ns |

| 16:1 MUX                | 6.1      | ns |

| 32:1 MUX                | 6.5      | ns |

| 組み合わせ(ピンから LUT、そしてピンへ)。 | 5.3      | ns |

# レジスタ・レジスタ間パフォーマンス

| 機能                                  | -5 タイミング | 単位  |

|-------------------------------------|----------|-----|

| 基本機能                                | •        |     |

| 16ビット・デコーダ                          | 331      | MHz |

| 32ビット・デコーダ                          | 277      | MHz |

| 64ビット・デコーダ                          | 240      | MHz |

| 4:1 MUX                             | 727      | MHz |

| 8:1 MUX                             | 482      | MHz |

| 16:1 MUX                            | 439      | MHz |

| 32:1 MUX                            | 382      | MHz |

| 8 ビット加算器                            | 391      | MHz |

| 16 ビット加算器                           | 337      | MHz |

| 64 ビット加算器                           | 190      | MHz |

| 16 ビット・カウンタ                         | 410      | MHz |

| 32 ビット・カウンタ                         | 315      | MHz |

| 64 ビット・カウンタ                         | 215      | MHz |

| 64 ビット・アキュムレータ                      | 155      | MHz |

| エンベデッド・メモリ機能                        |          |     |

| 256×36 シングルポート RAM                  | 280      | MHz |

| 512×18 真のデュアルポート RAM                | 280      | MHz |

| 分散メモリ機能                             |          |     |

| 16×2 シングルポート RAM                    | 549      | MHz |

| 64×2 シングルポート RAM                    | 259      | MHz |

| 128×4シングルポート RAM                    | 205      | MHz |

| 32×2 擬似デュアルポート RAM                  | 360      | MHz |

| 64×4 擬似デュアルポート RAM                  | 301      | MHz |

| DSP機能                               | •        |     |

| 9×9 パイプライン化乗算/アキュミュレート <sup>1</sup> | 250      | MHz |

| 18×18 パイプライン化乗算/アキュミュレート1           | 230      | MHz |

### PreliminaryDS Apr. 2005

| 36×36 パイプライン化乗算1 | 210 | MHz |

|------------------|-----|-----|

#### . LatticeECPデバイスだけに適用

本数値はispLEVER開発ツールを用いて算出されたもので、設計とツールのバージョンにより正確な値は異なることがある。ツールが用いる内部パラメータはキャラクタライズされたものであるが、全てのデバイスについてテストされたものではない。

## ディレーティング・タイミング表

データシートの以下のセクションとispLEVERデザインツールに提供されるロジック・タイミングは、動作範囲の最悪値です。ベストケース・プロセスの公称温度と電圧における実際の遅延は、表で与えられた値よりはるかに良い場合があります。特定の温度と電圧でロジック・タイミング値について計算するには、示された値に以下に示すディレーティング係数を乗算してください。

FPGAのジャンクション温度はデバイスの電力消費、パッケージの熱特性( $\Theta_{JA}$ )、および周囲温度により、以下の等式で計算されます。

$$T_{\text{JMAX}} = T_{\text{AMAX}} + (電力 * \Theta_{\text{JA}})$$

ユーザは、以下の $T_{J}$   $\mathbb{C}$ ディレーティング表に基づくディレーティング係数を決定するためにこの温度を決定して、次にそれを用いなければなりません。

表3-4 内部ブロックのための遅延ディレーティング表

| TJ ℃   | T¹ ℃     | 電源電圧  |      |       |  |  |  |

|--------|----------|-------|------|-------|--|--|--|

| コマーシャル | インダストリアル | 1.14V | 1.2V | 1.26V |  |  |  |

| _      | -40      | 0.82  | 0.77 | 0.71  |  |  |  |

| _      | -25      | 0.82  | 0.76 | 0.71  |  |  |  |

| 0      | 15       | 0.89  | 0.83 | 0.81  |  |  |  |

| 25     | 40       | 0.93  | 0.87 | 0.89  |  |  |  |

| 85     | 100      | 1.00  | 0.94 | 0.90  |  |  |  |

| 100    | 115      | 1.00  | 0.95 | 0.90  |  |  |  |

| 110    | 125      | 1.00  | 0.95 | 0.90  |  |  |  |

| 125    | _        | 1.02  | 0.96 | 0.91  |  |  |  |

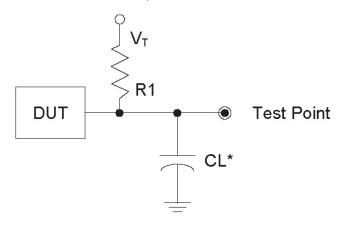

# LatticeECP/EC 外部スイッチング特性

## 推奨動作条件にわたって

| パラメー                  | 記述                                         | デバイス                                              | -5    |       | -4    | ļ     | -     | 3     | 単位  |

|-----------------------|--------------------------------------------|---------------------------------------------------|-------|-------|-------|-------|-------|-------|-----|

| タ                     |                                            |                                                   | Min.  | Max.  | Min.  | Max.  | Min.  | Max.  |     |

| 汎用 <b>I/O</b> ピン      | ノ・パラメータ(PLLなしでプライマリ・クロック                   | を用いる <b>)</b> 1                                   |       |       |       |       |       |       |     |

| tco                   | クロック対出力 - PIO 出力レジスタ                       | LFECP6/EC6,<br>LFECP20/EC20                       |       | 5.71  | -     | 6.85  | _     | 7.99  | ns  |

| t <sub>SU</sub>       | クロック対データ・セットアップ - PIO 入<br>カレジスタ           | LFECP6/EC6,<br>LFECP20/EC20                       | 0.00  | _     | 0.00  | _     | 0.00  | _     | ns  |

| t <sub>H</sub>        | クロック対データ・ホールド - PIO 入力レ<br>ジスタ             | LFECP6/EC6,<br>LFECP20/EC20                       | 3.41  | _     | 4.09  | _     | 4.77  | _     | ns  |

| t <sub>SU_DEL</sub>   | クロック対データ・セットアップ - データ<br>入力遅延あり PIO 入力レジスタ | LFECP6/EC6,<br>LFECP20/EC20                       | 3.84  | _     | 4.62  | _     | 5.38  | _     | ns  |

| t <sub>H_DEL</sub>    | クロック対データ・ホールド - 入力データ<br>遅延あり PIO 入力レジスタ   | LFECP6/EC6,<br>LFECP20/EC20                       | 0     | _     | 0     | _     | 0     | _     | ns  |

| f <sub>MAX_IO</sub>   | I/OとPFUレジスタのクロック周波数                        | LFECP6/EC6,<br>LFECP20/EC20                       | _     | 420   | _     | 378   | _     | 340   | Mhz |

| DDR I/O ಟಿ            | ン・パラメータ <sup>2,3</sup>                     |                                                   |       |       |       |       |       |       |     |

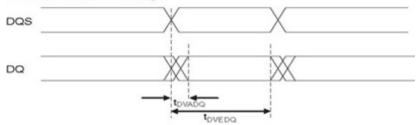

| t <sub>DVADQ</sub> 4  | DQS後の有効データ(DDRリード)                         | LFECP6/EC6,<br>LFECP20/EC20                       | _     | 0.192 | _     | 0.192 | _     | 0.192 | UI  |

| t <sub>DVEDQ</sub> 4  | DQS後のデータホールド(DDRリード)                       | LFECP6/EC6,<br>LFECP20/EC20                       | 0.668 | _     | 0.668 | _     | 0.668 | _     | UI  |

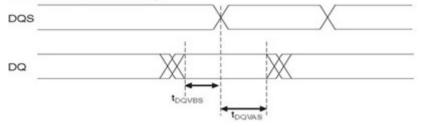

| t <sub>DQVBS</sub>    | DQS前の有効データ                                 | LFECP6/EC6,<br>LFECP20/EC20                       | 0.2   | _     | 0.2   | _     | 0.2   |       | UI  |

| t <sub>DQVAS</sub>    | DQS前の有効データ                                 | LFECP6/EC6,<br>LFECP20/EC20                       | 0.2   | _     | 0.2   | _     | 0.2   |       | UI  |

| £                     | DDRクロック周波数                                 | LFECP6/EC6<br>(fpBGA),<br>LFECP20/EC20<br>(fpBGA) | 95    | 200   | 95    | 166   | 95    | 133   | MHz |

| f <sub>MAX_DDR</sub>  | DDRクロツク同仮数                                 | LFECP6/EC6<br>(TQFP),<br>LFECP20/EC20<br>(TQFP)   | 95    | 166   | 95    | 133   | 95    | 133   | MHz |

| プライマリ                 | とセカンダリ・クロック                                |                                                   |       |       |       |       |       |       |     |

| f <sub>MAX_PRI</sub>  | プライマリ・クロックツリー周波数                           | LFECP6/EC6,<br>LFECP20/EC20                       | _     | 420   | _     | 378   |       | 340   | MHz |

| t <sub>W_PRI</sub>    | プライマリ・クロックパルス幅                             | LFECP6/EC6,<br>LFECP20/EC20                       | 1.19  | _     | 1.19  | _     | 1.19  | _     | ns  |

| t <sub>SKEW_PRI</sub> | I/Oバンク内のプライマリ・クロックスキュ<br>ー                 | LFECP6/EC6,<br>LFECP20/EC20                       | _     | 250   |       | 300   |       | 350   | ps  |

- 1. 一般のタイミング値はLVCMOS2.5V、12mAに基づく

- 2. DDRタイミング値はSSTL I/Oに基づく

- 3. DR仕様値はキャラクタライズされているが、テストはされていない

- 4. UIはビットあたりの平均

## 図3.7 DDRタイミング

## DQ and DQS Write Timings

# LatticeECP/EC内部タイミング・パラメータ<sup>1</sup>

## 推奨動作条件にわたって

| 0= , 2-                 | <i>4.</i> 7.€                          |       | 5     |       | 4     | -3    |       | 环 1수 |

|-------------------------|----------------------------------------|-------|-------|-------|-------|-------|-------|------|

| パラメータ                   | 記述                                     | Min.  | Max.  | Min.  | Max.  | Min.  | Max.  | 単位   |

| PFU/PFFロジッ              | ク・モード・タイミング                            |       |       | •     |       |       | •     |      |

| t <sub>LUT4_PFU</sub>   | LUT4 遅延(A~D 入力から F 出力)                 | _     | 0.25  | _     | 0.31  |       | 0.36  | ns   |

| t <sub>LUT6 PFU</sub>   | LUT6 遅延(A~D 入力から OFX 出力)               | _     | 0.55  | _     | 0.66  | _     | 0.77  | ns   |

| t <sub>LSR PFU</sub>    | セット/リセット対 PFU 出力                       | _     | 0.81  | _     | 0.98  | _     | 1.14  | ns   |

| t <sub>SUM_PFU</sub>    | 入力セットアップ時間、クロック対 Mux (MO、M1)           | 0.08  | _     | 0.10  | _     | 0.11  | _     | ns   |

| t <sub>HM_PFU</sub>     | 入力ホールド時間、クロック対 Mux (MO、M1)             | -0.06 | _     | -0.07 | _     | -0.08 | _     | ns   |

| t <sub>SUD_PFU</sub>    | 入力セットアップ時間、クロック対 D 入力                  | 0.11  | _     | 0.14  | _     | 0.16  | _     | ns   |

| t <sub>HD_PFU</sub>     | ホールド時間、クロック対 D 入力                      | -0.04 | _     | -0.04 | -     | -0.05 | _     | ns   |

| t <sub>CK2Q_PFU</sub>   | クロック対 $Q$ 遅延、 $D$ -タイプ・レジスタ・コンフィグレーション | _     | 0.43  | _     | 0.51  | _     | 0.60  | ns   |