# LatticeXP sysCONFIG 使用ガイド

# はじめに

パワーアップ時やユーザがデバイスを更新したい時はいつでも、コンフィグレーション・メモリに自動的にロードすることができるように、SRAMセルに伴って、LatticeXP TM FPGAにおいてはフラッシュ・セルを用いてメモリが構築されています。 "インスタントオン"機能に加えて、オンチップ・フラッシュメモリはコンフィグレーション・ビットストリームが外部に出ないことによって、設計のセキュリティが増大します。一方で、SRAMベースFPGAの使いやすさと再プログラム性を維持します。

外部デバイスは不要ですが、LatticeXPは複数の外部コンフィグレーション・モードをサポートします。利用できる外部コンフィグレーション・モードは以下の通りです。ンフィグレーション・モードは以下の通りです。

- ・スレーブシリアル

- ・マスタシリアル

- ・スレーブパラレル

- ・ ispJTAG TM (1149.1インターフェイス)

このガイドはLatticeXPで利用できるすべてのコンフィグレーション・オプションをカバーします。

# プログラミング概要

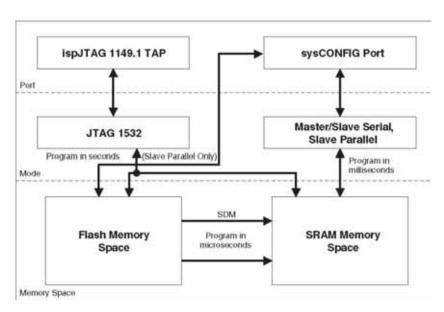

LatticeXPは2種類のメモリ、SRAMおよびフラッシュを含んでいます(図12-1を参照してください)。SRAMは、本質的には回路の接続を定義する"ヒューズ"FPGAコンフィグレーションを保持します。フラッシュはコンフィギュレーション・データ用に不揮発性の内部記憶スペースを提供します。

SRAMは、外部コンフィグレーション・モードの1つであるJTAGを用いるか、またはオンチップ・フラッシュにデータを格納することによって、コンフィグレーションできます。コンフィギュレーション・プロセスはSRAM初期化(RAMとアドレス・ポインタのクリア)、コンフィギュレーション・データのSRAMへのロード、そしてユーザモードにFPGAを設定(FPGAをウェイクアップ)することから成ります。

JTAGを用いるか、または外部スレーブパラレル・ポートを用いることによって、オンチップ・フラッシュをプログラムすることができます。デバイスがパワーアップされている時はいつでもJTAGフラッシュ・プログラミングを実行することができます。スレーブパラレルは、直接またはバックグランドでsysCONFIG <sup>™</sup>ピンを用いてフラッシュをプログラムすることができます。ダイレクト・プログラミングはコンフィグ・モード時、バックグランド・プログラミングはユーザモード時に行われます。FPGAはパワーアップ時にPROGRAMNピンがLowにされるか、またはJTAGを通してリフレッシュ・コマンドが発行される時、コンフィグ・モードに入ります。ウェイクアップすると、すなわちデバイスがユーザ回路の動作を始める時に、ユーザモードに入ります。ダイレクトとバックグランドのこれら2モードは、このドキュメントでは"フラッシュダイレクト(直接)"と"フラッシュ・バックグランド"と呼ぶことにします。

## 図12-1 プログラミング・ブロック図

# コンフィグレーション・ピン

LatticeXPデバイスは2つのタイプ(専用と複数目的)のsysCONFIGピンをサポートします。それらがコンフィグレーションに用いられない場合、デュアル・ファンクションのピンはI/Oピンとして利用できます。

プログラマブル・オプションと共に、2本のコンフィグレーション・モード・ピンがデュアル・ファンクションのコンフィグレーション・ピンを制御します。コンフィグレーション・モード・ピン(CFG)は、通常PCBに固定配線され、どのコンフィグレーション・モードが用いられるかを決定します。ラティスispLEVER Rデザイン・ソフトウェアか、HDLソースファイル・アトリビュートによるプリファレンスでプログラマブル・オプションを指定します。これにより、ユーザや配置配線ソフトウェアがコンフィグレーション・ピンを使用してしまうことから保護することができます。また、LatticeXPデバイスはispJTAGによるコンフィグレーションをサポートしますが、JTAGポートはトランスペアレント・リードバックやJTAGテストにも用いられます。以下のセクションはsysCONFIGとJTAGピンの機能について説明します。JTAGとispJTAGは本書では同じ意味で用いていることに注意してください。表12-1を参考として示します。

# 専用ピン

以下はLatticeXPデバイスの専用sysCONFIGピンの記述です。これらのピンは、コンフィギュレーション・プロセスを制御するか、またはモニタするために用いられます。これらのピンは非JTAGプログラミング・シーケンスだけに用いられます。JTAGピンはこのドキュメントの "ispJTAG ピン "セクションで説明されています。

#### CFG[1:0]

コンフィグレーション・モード・ピンは弱いプルアップがある専用入力です。CFGピンは、LatticeXPのコンフィグレーション・モード、すなわちどのタイプのデバイスからコンフィグレーションされるかを選択するために用いられます。パワーオン・リセット(POR)時や、PROGRAMNピンがLowにドライブされると、選択されたコンフィグレーション・モードによって、デュアル・ファンクション・ピンの異なるグループがデバイス・コンフィグレーションに用いられます。

表12-1 LatticeXPデバイスのコンフィグレーション・ピン

| ピン        | 記述               | デフォルト・ピン機能 | 用いられるモード  |

|-----------|------------------|------------|-----------|

| CFG[1:0]  | 弱いプルアップがある入力     | 専用         | All       |

| PROGRAMN  | 弱いプルアップがある入力     | 専用         | All       |

| INITN     | 弱いプルアップがある双方向オープ | 専用         | All       |

|           | ン・ドレイン、またはドライブ出力 |            |           |

| DONE      | 弱いプルアップがある双方向オープ | 専用         | All       |

|           | ン・ドレイン           |            |           |

| CCLK      | 入力、または出力         | 専用         | All       |

| DIN       | 弱いプルアップがある入力     | デュアル用途     | シリアル      |

| DOUT/CSON | 出力               | デュアル用途     | シリアル、パラレル |

| CSN       | 弱いプルアップがある入力     | デュアル用途     | パラレル      |

| CS1N      | 弱いプルアップがある入力     | デュアル用途     | パラレル      |

| WRITEN    | 弱いプルアップがある入力     | デュアル用途     | パラレル      |

| BUSY      | 出力、トライステート、弱いプルア | デュアル用途     | パラレル      |

|           | ップ               |            |           |

| D[0:7]    | 入力、または出力         | デュアル用途     | パラレル      |

| TDI       | 弱いプルアップがある入力     | JTAG       |           |

| TDO       | 弱いプルアップがある出力     | JTAG       |           |

| TCK       | ヒステリシスあり入力、プルアップ | JTAG       |           |

| TCK       | なし               | JIAG       |           |

| TMS       | 弱いプルアップがある入力     | JTAG       |           |

注:弱いプルアップは30uAから150uAの電流源から成ります。CFGとPROGRAMNのプルアップは $V_{CC}$ (コア)をトラッキングし、TDI、TDO、およびTMSのプルアップは $V_{CCJ}$ をトラッキングします。他のすべてのプルアップは、そのピンの $V_{CCIO}$ をトラッキングします。

両CFGピンがHighのときには、デバイスはオンチップ・フラッシュに格納されたデータを読むことによって、自分を構成します。これはSDM、またはセルフ・ダウンロード・モード(Self Download Mode)と呼ばれます。SDMに関する詳しい情報は、このドキュメントのセルフ・ダウンロードモード・セクションを参照して下さい。

表12-2 LatticeXPのコンフィグレーション・モード

| コンフィグレーション・モード   | CFG[1] | CFG[0] |

|------------------|--------|--------|

| スレーブシリアル         | 0      | 0      |

| マスタシリアル          | 0      | 1      |

| スレーブパラレル         | 1      | 0      |

| セルフ・ダウンロード (SDM) | 1      | 1      |

#### **PROGRAMN**

PROGRAMNは弱いプルアップがある入力専用ピンです。このピンは、非JTAG SRAMコンフィグレーション・シーケンスを開始するのに用いられます。PROGRAMNピンがHighからLowにされると、デバイスはコンフィグレーション・モードに入ります。PROGRAMNピンを用いることで、いつでもコンフィグレーションのトリガとすることができます。

デバイスがJTAGを用いている場合、デバイスがJTAGモードからリリースされるまで、PROGRAMNは無視されます。CFGピンがともにHighでない(SDMでない)場合、コンフィグレーション・シーケンスは、選択されたコンフィグレーション・ポートを用いて続けられます。両方のCFGピンがHigh(SDM)で、フラッシュをプログラムしてあると、コンフィグレーション・シーケンスは、オンチップ・フラッシュのデータを用いて続けられます。

両方のCFGピンがHigh(SDM)で、フラッシュがプログラムされていないと、コンフィグレーション・シーケンスは一時的に止まり、プログラムが完了してFlash Doneビットがセットされるのを待ちます。フラッシュがプログラムされ、PROGRAMNがHighにされるとコンフィグレーション・シーケンスが続けられます。

#### INITN

INITNピンは弱いプルアップがある専用の双方向オープン・ドレイン・ピンです。INITNは外部からドライブされるLowパルスを検出すると共に、外部をLowパルスでドライブすることができます。

外部デバイスからSRAMをコンフィグレーションする際にINITNがLowになるのは、SRAMが初期化されていることを示します。次にINITNがHighになると、FPGAはコンフィギュレーション・データを受け入れる準備ができていることを示します。コンフィグレーションを遅らせるために、外部的にINITNピンをLowに保持することができます。INITNピンがLowである限り、デバイスはコンフィグレーション・モードに入りません。コンフィグレーションが始まった後に、INITNはビットストリームの誤りを示すために用いられます。計算したCRCとコンフィギュレーション・データのCRCが一致しないと、INITNピンはLowにドライブされます。この場合DONEピンはLowのままで、LatticeXPは起動しません。

オンチップ・フラッシュをプログラムするとき、INITNピンのみが消去、あるいはプログラミング時の誤りを示すために用いられます。誤りが発生すると、INITNはLowにドライブされます。フラッシュ直接プログラミングの間の誤りは、フラッシュからFPGAを構成することを妨げます。フラッシュ・バックグランド・プログラミングの間の誤りは、既に動作しているSRAMでの構成には影響しません。

#### **DONE**

DONEピンは弱いプルアップがある専用の双方向オープン・ドレイン(デフォルト)で、あるいはアクティブ・ドライブできるピンです。デバイスがコンフィグレーション・モードにあり、内部DONEビットがプログラムされていない際に、DONEはLowにドライブされます。INITNとPROGRAMNピンがHigh (SDMの場合はPROGRAMNピンのみがHigh)になり、内部DONEビットがプログラムされると、DONEピンは解除(或いは、アクティブ・ドライブであるならHighに)されます。外部からDONEピンをLowに保持することができ、選択されたウェイクアップ・シーケンスによっては、DONEピンが外部的にHighにされるまで、デバイスは動作を開始しません。

DONEビットを読み出すことは、FPGAが構成されたかどうかを外部デバイスが知る良い方法です。

SRAMを構成するためにJTAGを用いるとき、DONEピンはバウンダリ・スキャン・セルによってドライブされるため、DONEピンのステートは意味がありません。

#### CCLK

CCLKは専用の双方向ピンで、方向はマスタ・モードかスレーブ・モードのどちらが選択されるかに依存します。マスタモードがCFGピンによって選択されると、CCLKピンは出力になりますが、そうででなければ、CCLKは入力ピンです。

CCLKピンが出力になると、内部プログラマブル・オシレータはCCLKに接続され、外部スレーブ・デバイスをドライブします。CCLKは、DONEピンがHighにされ、デバイスのウェイクアップ・シーケンスが完了した後に100~500クロック周期で止まります。付加的なクロック周期により、チェインにある他のデバイスがウェイクアップするのに十分なクロックが提供されることを確実にします。止まると、CCLKは入力(トラ

イステート出力)になります。CCLKは次のコンフィグレーション初期化シーケンスで再開し(出力になり)ます。

MCCLK\_FREQパラメータはCCLKマスタ周波数を制御します(表12-3を参照)。CCLKはコンフィグレーション時に変えられるまでは2.5MHzです。コンフィグレーション時、最初にロードされるものの1つはMCCLK\_FREQパラメータです。一度このパラメータがロードされると、グリッチのないスイッチを用いて、選択された周波数へ変化します。スレーブ・デバイスの周波数仕様や、PCBレイアウトの信号インテグリティ機能を超えないように注意するべきです。

## 表12-3 マスタクロック周波数の選択

| CCLK (MHz) | CCLK (MHz) | CCLK (MHz) |

|------------|------------|------------|

| 2.5*       | 13         | 45         |

| 4.3        | 15         | 51         |

| 5.4        | 20         | 55         |

| 6.9        | 26         | 60         |

| 8.1        | 30         | 130        |

| 9.2        | 34         | _          |

| 10.0       | 41         | _          |

注:デフォルトは最も低い周波数の2.5MHz

## 表12-4 最大コンフィグレーション・ビットサイズ

| デバイス   | ピットストリームサイズ (Mb) |

|--------|------------------|

| LFXP3  | 1.0              |

| LFXP6  | 1.6              |

| LFXP10 | 2.8              |

| LFXP15 | 4.0              |

| LFXP20 | 4.9              |

## 表12-5 SDM ピンの用い方

| コンフィグレーション・<br>モード    | SDM(セルフ・ダウンロード・モード)                                      |                         |       |         |  |  |  |

|-----------------------|----------------------------------------------------------|-------------------------|-------|---------|--|--|--|

| CFG[1:0]              |                                                          | [1, 1]                  |       |         |  |  |  |

| フラッシュ・プログラミ<br>ング・モード | ダイレクト(Direct)                                            | バックグランド<br>(Background) | ダイレクト | バックグランド |  |  |  |

| ポート                   | sysCONFIG ispJTAG <sup>1</sup>                           |                         |       |         |  |  |  |

| ピン                    | CCLK, CSN, CSN1, WRITEN, D[0:7] TAP                      |                         |       |         |  |  |  |

| ユーザI/Oステータス           | トライステート                                                  | ユーザ                     | BSCAN | ユーザ     |  |  |  |

| PROGRAMN              | Highを保持 Highを保持 <sup>2</sup>                             |                         |       |         |  |  |  |

| BUSY                  | ステータス ステータス 未使用                                          |                         |       |         |  |  |  |

| INITN                 | 成功(pass)/失敗(fail) 成功(pass)/失敗(fail) Highを保持 <sup>3</sup> |                         |       |         |  |  |  |

| DONE                  | Done 未使用 Highを保持⁴                                        |                         |       |         |  |  |  |

| Persistent ビット        | 無視                                                       | ON                      | 無     | Ħ視      |  |  |  |

<sup>1</sup> CFGピンのステートにかかわらずフラッシュをプログラムするのにispJTAGを用いることができます。デバイスがSDMにある場合にだけSRAMを構成するためにフラッシュを用いることができます。

<sup>2</sup> JTAGフラッシュ・プログラミングの間、PROGRAMNピンのステートをデバイスは無視しますが、フラッシュからSRAMへのデータ転送を防ぐために、ピンはHighに保持されるべきです。

- 3 JTAGフラッシュ・プログラミングの間、INITピンのステートをデバイスは無視しますが、ピンは内部プルアップを用いてHighにフロートすることを許可するべきです。

- 4 JTAGフラッシュ・プログラミングの間、DONEピンのステートはデバイスが無視しますが、デバイスの起動を妨ぐため、ピンは内部プルアップを用いてHighにフローティングすることを許可するべきです。

#### 表12-6 メモリアクセスに使用されるピンの詳細

| CF  | G   | コンフィグ        | オンチップ<br>フラッシュ          | SRAM           |                      |

|-----|-----|--------------|-------------------------|----------------|----------------------|

| 1   | 0   | モート          | Write/Read <sup>2</sup> | 書き込みソース        | リードバック <sup>23</sup> |

| x 1 | x 1 | JTAG         | TAP                     | TAP            | TAP                  |

| 1   | 1   | SDM          | sysCONFIG               | オンチップ<br>フラッシュ | sysCONFIG            |

| 1   | 0   | スレーブ<br>パラレル | N/A <sup>4</sup>        | sysCONFIG      | sysCONFIG            |

| 0   | 1   | マスタ<br>シリアル  | N/A <sup>4</sup>        | sysCONFIG      | N/A <sup>5</sup>     |

| 0   | 0   | スレーブ<br>シリアル | N/A <sup>4</sup>        | sysCONFIG      | N/A <sup>5</sup>     |

- 1 CFG設定の如何にかかわらず、ispJTAGポートは常に利用できます。

- 2 セキュリティ・ビットをプログラムすることによってのみ、リードバックを禁止することができます。

- 3 バックグラウンド・リードバックのためにsysCONFIGポートを確保するためには、PERSISTENTビットをONにセットします。

- 4 フラッシュへのアクセスは本モードでは禁止されます

- 5 SRAMリードバックは本モードでは禁止されます

## プログラミング・シーケンス

3つのタイプのプログラミング、SRAM、フラッシュ直接、およびフラッシュ・バックグランドがあります。 このセクションは、専用ピンがどう使用されるかを、それぞれのプロセスについて見ていきます。

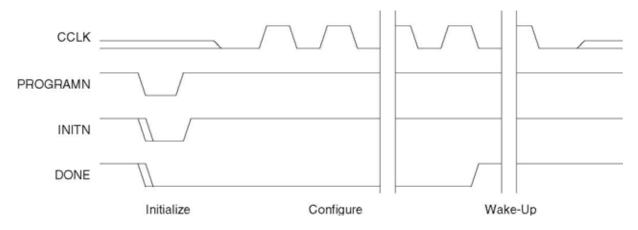

#### **SRAM**

SRAMのコンフィグにSDMを使用しない場合、内部パワーオン・リセット(POR)がリリースされるか、またはPROGRAMNピンがLowにドライブされるとシーケンスが始まります(図12-2を参照)。LatticeXPはINITNをLowにドライブし、I/Oをトライステートにし、内部のSRAMと制御ロジックを初期化します。これが完了すると、PROGRAMNがHighであれば、INITNはリリースされます。INITNが外部的にLowに保持されていると、LatticeXPはHighになるまで待ち、その後LatticeXPはCFGピンで決定される選択されたコンフィグレーション・ポート上でコンフィギュレーション・データ・プリアンブルを探し始めます。

コンフィグレーションがいったん完了すると、内部DONEビットはセットされ、DONEピンはHighになり、FPGAは起動し(ユーザモードに入り)ます。ビットストリームを読むときにCRC誤りが検出されると、INITNはLowになり、内部DONEビットはセットされないで、DONEピンはLowのままで、LatticeXPはウェイクアップしません。

SRAMのコンフィグレーションにSDMを使用する場合、INITが使用されない(モニタされない)以外は、シーケンスは同様です。内部パワーオン・リセット(POR)がリリースされるか、またはPROGRAMNピンがLowにドライブされるとシーケンスが始まります(図12-2)。LatticeXPはI/Oをトライステートにし、内部のSRAMと制御ロジックを初期化します。これが完了するとLatticeXPはオンチップ・フラッシュからコンフィグレーション・データのロードを開始します。

SDMモードでない場合と同様に、コンフィグレーションが完了するとDONEビットがセットされ、DONEピンがHighになり、そしてFPGAがウェイクアップしユーザモードに入ります。

#### 図12-2 SRAMコンフィグレーション・タイミング図

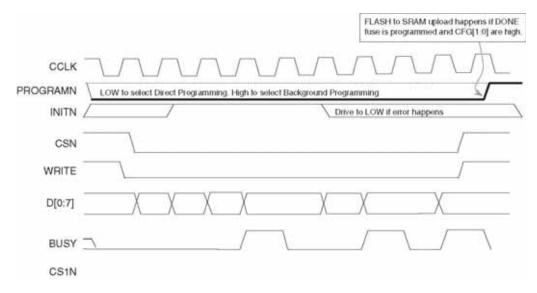

## フラッシュ・ダイレクト

フラッシュ・ダイレクト・プログラミングは、CFGピンが共にHighの場合(SDM)、スレーブパラレル・ポートを用いることで可能です。シリアルポートは、フラッシュをプログラムするのには用いられないかもしれません。フラッシュ・ダイレクトは、DONEピンがLow(SRAMがブランク)の場合のみ有効です。

PROGRAMNピンがLowにドライブされたとき、シーケンスが始まります。LatticeXPはI/Oをトライステートにし、内部のSRAMと制御ロジックを初期化します。LatticeXPはWRITEN、CSNとCS1Nピンが共にLowとなるのを待ち、プログラミング・プリアンブルを探し、その後消去、プログラム、ベリファイ各コマンドが続きます。データはD[0:7]ピン上でリード・ライトされます。

フラッシュがいったんプログラムされると、フラッシュからSRAMへの転送を始めるためにPROGRAMNピンはHighにすることができます。

#### フラッシュ・バックグランド

フラッシュ・バックグランド・プログラミングは、CFGピンが共にHighなら(SDM)、スレーブパラレル・ポートを用いることで可能です。シリアルポートは、フラッシュをプログラムするのに用いられないかもしれません。フラッシュ・バックグランドはFPGAの現在のコンフィグレーションを妨げません。

フラッシュ・バックグランド・プログラミングはコンフィグ・モードとユーザモードの両方(DONEビットは 0か1)で用いられるかもしれません。ユーザモードでフラッシュ・バックグランド・プログラミングをサポートするためには、PERSISTENTビットをONに設定しなければなりません。

WRITENがLowになり、CSNとCS1Nも共にLowだと、FPGAはプリアンブルを待ち、適切なコマンドを探します。INITNがLowになるのは、フラッシュの消去かプログラムの誤りを示します。データはD[0:7]ピンでリード・ライトされます。

フラッシュをプログラムした後に、ユーザはフラッシュ・データをSRAMに転送するためにPROGRAMNピンをトグルすることができます。

## 図12-3 フラッシュ・プログラミング・タイミング図

# デュアル・ファンクションのsysCONFIGピン

以下は、デュアル・ファンクションのsysCONFIGピンのリストです。これらのピンはコンフィグレーション後に汎用I/Oとして利用できます。デュアル・ファンクションのコンフィグレーション・ピンを汎用I/Oとしても用いる場合、ユーザは以下の事項を守らなければなりません。

- ・GPIOはコンフィグレーション時の方向と同じでなければなりません。即ち、コンフィグレーション時に ピンが入力であるなら、GPIOとしても入力でなければなりません。コンフィグレーション時に出力である なら、GPIOとしても出力でなければなりません。また双方向であるなら、それはGPIOとしても双方向で なければなりません。

- ・I/Oタイプは同じでなければなりません。即ち、コンフィグレーション時に、ピンが3.3V CMOSピン (LVCMOS33)であるなら、GPIOとしてもCMOS33でなければなりません。

- ・パーシスタンス (Persistent)オプションをOFFに設定しなければなりません。ispLEVERのプリファレンス・エディタを用いることによって、パーシスタンス・オプションにアクセスできます。

- ・ユーザはどんな内部、または外部論理もデバイス・コンフィグレーションを妨げないことを保証する責任があります。

また、スレーブパラレル・コンフィグレーションモードが使われない場合、パラレルポート・チップセレクト(CSN、CS1N)の一方または両方は、コンフィグレーション中にHigh或いはトライステートである必要があります。

コンフィグレーション後、GPIOとして用いられない場合、これらのピンはトライステートになり、弱くプルアップされます。

#### DIN

DIN(データ入力)は弱いプルアップがあるデュアル・ファンクションの入力ピンですDINはシリアル・ビットストリームのコンフィグレーションに用いられます。

## DOUT/CSON

DOUT/CSONはチェイン・モード(デイジー・チェイン)で用いられるデュアル・ファンクションの出力です。 このピンは、シリアルかパラレルモードで用いることができ、2つの用途を持っています。 バイパス・チェイン・モードが選択されると、シリアルやパラレルのコンフィグレーション・モード用に、このピンはDOUTになります。デバイスが完全に構成されると、シリアル・コンフィグレーション・モードでは、バイパス命令が実行され、そして、DINピンのデータはバイパス・レジスタを通してDOUTピン上に出されます。このようにしてシリアル・データは次のデバイスに渡されます。パラレル・コンフィグレーション・モードでは、データはシリアルにされてその後DOUTに出されます。D[0](MSb)が最初にシフトアウトされ、その後D[1]、D[2]と続きD[7](LSb)が出力されます。

フロースルー・チェイン・モードが選択されているとき、パラレル・コンフィグレーション・モード用に、このピンはチップセレクト出力(CSON)になります。デバイスが完全に構成されると(内部DONEビットがHigh)、フロースルー・チェイン・モードでは、フロースルー命令が実行されます。そして、CSONピンは、次のデバイスのチップセレクト・ピンをイネーブルするためにLowにドライブされます。

DOUT/CSONバイパス・レジスタはパワーアップ時にHighを出力し?、ビットストリーム内のバイパス命令かフロースルー命令を実行するまでそのままです。

内部のフラッシュから構成する(SDM)とき、チェイン・モードはサポートされません。

#### CSN & CS1N

CSNとCS1Nは共に弱いプルアップがあるLowアクティブの入力ピンで、パラレルモードのみで用いられます。これらの入力は論理ORされ、バイト・データをD[0:7]データピンでの入出力をイネーブルするのに用いられます。

非SDMでCSNまたはCS1NがHighのときには、D[0:7]、INITN、およびBUSYピンはトライステートになります。CSNとCS1Nの両方がHighにドライブされると、バイパス/フロースルー・レジスタはリセットされます。D[0:7]、INITN、およびBUSYピンを制御しているとき、CSNとCS1Nは互換です。

SDMが選択されて、CSNかCS1NがHighのとき、D[0:7]、INITN、およびBUSYピンはトライステートになります。フラッシュがプログラムされていないで、CSNとCS1Nが両方Highであると、LatticeXPは内部のFPGAコンフィグレーション回路をリセットするために、INITNピンをLowにドライブします。そしてLatticeXPは、D[0:7]をモニタしコンフィグレーション・プリアンブルを待ちます。D[0:7]、INITN、およびBUSYピンを制御しているとき、CSNとCS1Nは互換です。D[0]は最上位ビット(MSb)で D[7]が最下位ビット(LSb)です。

デバイスがユーザモードの間(DONEピンがHigh)SRAMかフラッシュがアクセスされる必要があるなら、CSNとCS1Nとしてこれらのピンを確保するためにPERSISTENTプリファレンスをONに設定しなければなりません。

#### WRITEN

WRITENピンはパラレルモードのみで用いられる弱くプルアップされたLowアクティブの入力です。 WRITENピンはデータピンD[0:7]の方向を決定するのに用いられます。WRITENピンは、バイトデータがデバイスに入力されるときはLowにドライブされ、デバイスからデータが読まれるときにはHighにされる必要があります。

デバイスがユーザモードの間(DONEピンがHigh)、SRAMかフラッシュがアクセスされる必要があるなら、WRITENとしてこのピンを確保するために、PERSISTENTプリファレンスをONに設定しなければなりません。

#### **BUSY**

パラレルモードでは、BUSYピンは弱いプルアップがあるトライステート出力です。D[0:7]ピンからバイト・データを入力する準備ができているとき、またはバイト・データを読み出す準備ができているときにのみ、LatticeXPデバイスはBUSYピンをLowにドライブします。非同期ペリフェラル・モード(ハンドシェイク)を

サポートするためにBUSYピンを用いることができます。このピンは、LatticeXPがコマンドを実行するために余分に時間が必要なことを示すのに用いられます。

デバイスがユーザモードの間、SRAMかフラッシュがアクセスされる必要があるとき、BUSYとしてこのピンを確保するために、PERSISTENTプリファレンスをONに設定しなければなりません。

#### D[0:71

D[0:7]ピンはスレーブパラレル・モードのみをサポートします。D[0:7]ピンはデータのリード・ライトに用いられ、トライステートにできる双方向I/Oピンです。WRITEN信号がLowで、CSNとCS1NピンもLowのとき、D[0:7]ピンはデータ入力になります。WRITEN信号がHighで、CSNとCS1NピンがLowのとき、D[0:7]ピンはデータ出力になります。CSNかCS1NのどちらかがHighであると、D[0:7]はトライステートになります。

デバイスがユーザモードの間、SRAMかフラッシュがアクセスされる必要があるとき、D[0;7]としてこのピンを確保するために、PERSISTENTプリファレンスをONに設定しなければなりません。

EBRかPFUメモリのリードバックの際は、注意しなければなりません。これらのRAMを読むことでデータが確実にこわれないようにすることは、ユーザに委ねられています。すなわち、これらのRAMはユーザ・コードによってアクセスされている間、読まれないかもしれません。

#### ispJTAGピン

ispJTAGピンは標準のIEEE1149.1 TAP(テスト・アクセス・ポート)ピンです。LatticeXPデバイスがパワーアップされているとき、ispJTAGピンは専用ピンであり、いつでもアクセスできます。ispJTAGを通してSRAMをプログラムするとき、DONEなどのように、プログラミングの進捗を決定する専用プログラミング・ピンを用いることはできません。これはJTAG1149.1に従って、通常の内部ロジックではなくバウンダリ・スキャン・セルのステートがピンをドライブするためです。

#### **TDO**

テストデータ出力ピンTDOは、シリアルのテスト命令とデータをシフトアウトするために用いられます。 TDOが内部回路によってドライブされていないとき、ピンはハイ・インピーダンス・ステートにあります。

#### TDI

テストデータ入力ピンは、シリアルのテスト命令とデータをシフト入力するのに用いられます。TDIピンには内部プルアップ抵抗があり、Vcc」にプルアップされています。

#### **TMS**

テスト・モード選択ピンはTAPコントローラのテスト動作を制御します。TCKの立ち下がリエッジで、TMSのステートによって、TAPコントローラ・ステート・マシンは状態遷移します。TMSピンには内部プルアップ抵抗があり、Vcc」にプルアップされています。

#### **TCK**

テスト・クロック・ピン(TCK)は、データ及び命令レジスタをロード、アンロードするTAPコントローラを動作させるためのクロックを提供します。TCKはHighかLowの状態で止めることができ、デバイス・データシートで示された周波数まで上げることができます。TCKピンはヒステリシスをサポートしており、値はデータシートのDCパラメータ・テーブルに示されます。TCKピンには、プルアップがありません。 $V_{cc}$ が立ち上がる際にTAPコントローラが不注意にクロッキングされるのを避けるため、PCB上に4.7Kプルダウン抵抗を置くことを推奨します。

#### オプションのTRST

LatticeXPデバイスではテストリセット、TRSTはサポートされません。

## **VCCJ**

JTAG VCC( $V_{CCJ}$ )は独立した電圧をJTAGポートに供給し、共通の電圧の他デバイスとJTAGチェインを作ることを可能にします。JTAGが使用されていなくても、 $V_{CCJ}$ を接続しなければなりません。また、この電圧はJTAGダウンロード・ケーブルにも供給されます。有効な電圧レベルは、3.3Vと、2.5V、1.8V、1.5V、そして1.2Vです。

さらなるJTAGチェイン情報は、www.latticesemi.comのラティス・ウェブサイトより入手できる、ispJTAGデバイス用の"インシステム・プログラミング・デザイン・ガイドライン"を参照してください。

## コンフィグレーションとJTAG電圧レベル

制御ピンとプログラミング・ピンのすべてがLVCMOSをデフォルトとします。CFGとPROGRAMNは $V_{cc}$ (core)に接続されます。TCK、TDI、TDO、およびTMSは $V_{cc}$ 」をトラッキングします。他のすべてのピンがそのピン用の $V_{cc}$ 」をトラッキングします。

# コンフィグレーション・モードとオプション

LatticeXPデバイスはセルフ・コンフィグレーションを含み、シリアルまたはパラレルデータ入力を利用する、幾つかのコンフィグレーション・モードをサポートします。パワーアップ時、またはPROGRAMNピンがLowにドライブされると、LatticeXPデバイスの構成に用いられるモードを決定するためにCFG[1:0]ピンがサンプルされます。CFGピンは、通常PCB上で固定配線されており、デバイスがコンフィギュレーション・データを得るのにどのポートを用いるかを決定します。CONFIG\_MODEは、ラティスispLEVERデザイン・ソフトウェアか、HDLソースファイル・アトリビュートとして、プリファレンスとしてアクセスできるプログラマブル・オプションです。そして、コンフィグレーション・ピンをユーザや配置配線ソフトウェアが期せずして使用してしまうことがないように、ユーザは保護できます。

表12-7はモード、CFG[1:0]、およびソフトウェアCONFIG\_MODEパラメータを示します。以下はそれぞれのコンフィグレーション・モードを詳述します。

| 表12-7 LatticeXPのコンフィグレーシ | ィョン・ | $\mathcal{F}-$ | ĸ |

|--------------------------|------|----------------|---|

|--------------------------|------|----------------|---|

| コンフィグレーション・モード           | CFG[1] | CFG[0] | CONFIG_MODE 1         | チェインモード <sup>2</sup> |

|--------------------------|--------|--------|-----------------------|----------------------|

| スレーブシリアル (オーバフロー・オプション   | 0      | 0      | Slave_Serial          | Disable              |

| なし)                      |        |        |                       |                      |

| スレーブシリアル(バイバスON)         | 0      | 0      | Slave_Serial          | Bypass               |

| マスタシリアル (オーバーロード・オプション   | 0      | 1      | Master_Serial         | Disable              |

| なし)                      |        |        |                       |                      |

| マスタシリアル (バイバスON)         | 0      | 1      | Slave_Serial          | Bypass               |

| スレーブパラレル (オーバーロード・オプショ   | 1      | 0      | Slave_Parallel        | Disable              |

| ンなし)                     |        |        |                       |                      |

| スレーブパラレル(バイバスON)         | 1      | 0      | Slave_Parallel        | Bypass               |

| スレーブパラレル(フロースルーON)       | 1      | 0      | Slave_Parallel        | Flowthrough          |

| SDM                      | 1      | 1      | None/Slave_Parallel 4 | Disable              |

| ispJTAG(1149.1 インターフェイス) | X 3    | Χ³     | None <sup>5</sup>     |                      |

- 1 CONFIG MODEはispLEVERプリファレンス・エディタ内にあります。

- 2 CHAIN\_MODEはispLEVER bitgenオプションにあります("Generate Bitstream Data"で右クリックし、そして "Properties"をクリックします)。

- 3 ispJTAGインターフェイスは常時オンです。

- 4 ispJTAGがオンチップ・フラッシュとSRAMにアクセスするのに排他的に用いられる場合、Noneを選択します。フ

ラッシュとSRAM、あるいはその一方にアクセスするのにスレーブパラレルが用いられる場合、Slave\_Parallelを選択してください。

5 Noneの選択は、デュアル・ファンクションのピンがコンフィグレーションのためには予約されないことを示します。これはデフォルトです。

## コンフィグレーション・オプション

各CONFIG MODEには複数のコンフィグレーション・オプションがあります。

・ 複数のFPGAデバイスをデイジー・チェインにするときのため、コンフィグレーション・オーバフロー・オプションがあります。最初のFPGAがいったんダウンロードを完了すると、コンフィギュレーションデータ・オーバフローが起こります。そして、残りのコンフィグレーション・データは、最初のFPGAを介してその後のFPGAへ出力されます。

SDMを用いるとき、コンフィギュレーションデータ・オーバフローはサポートされません。

- マスタクロックを用いるとき、その周波数を設定することができます。

- SRAMやフラッシュのリードバックを防ぐためにセキュリティ・ビットがあります。

ラティスispLEVERデザイン・ソフトウェアで適切なパラメータを設定することにより、選択されたコンフィグレーション・オプションが生成されるビットストリームに設定されます。ビットストリームがデバイスにロードされる際に、選択されたコンフィグレーション・オプションは有効になります。これらのオプションは以下のセクションで説明されます。

#### オーバフロー・オプションのバイパス

シリアル、あるいはパラレルのデバイス・デイジーチェインでバイパス・オーバフローオプションを用いることができます。最初のデバイスがコンフィギュレーション・データのダウンロードを完了し、バイパス・オプション・プリファレンスが選択されている場合、sysCONFIGピンのデバイス・コンフィグレーション・ポートに入力されるデータはDOUTの外へシリアルにオーバフローし、そして次のスレーブシリアル・デバイスのDINピンに入ります。バイパス・オプションは、ispLEVERで"Generate Bitstream Data"で右クリックし、"Properties"をクリックすることによって選択されます。

シリアル・コンフィグレーション・モードでは、コンフィギュレーション・データのすべてがいったん最初のデバイスにロードされると、バイパス・オプションはバイパス・レジスタによってDINピンをDOUTピンに接続します。バイパス・レジスタはコンフィグレーションの始めに'1'で初期化されます。

パラレル・コンフィグレーション・モードでは、一度コンフィギュレーション・データのすべてが最初のデバイスにロードされて、バイパス・オプションはD[0:7]から入力されるデータをシリアルにDOUTにシフトアウトします。シリアル化されたデータはバイパス・レジスタを通してDOUTに出力されます。バイト幅データのD[0]が最初にシフトアウトされ、以下D[1]、D[2]と続きます。

一度バイパス・オプションが始まると、デバイスはウェイクアップ・シーケンスが完了するまでそのままです。CSNとCS1Nの両方をHighにすることによって、バイパス・オプションを中止することができます。

#### フロースルー・オーバフロー・オプション

フロースルー・オーバフロー・オプションはパラレルモードのみで用いられます。FPGAにコンフィギュレーション・データがすべて入力されたとき、フロースルー・オプションはCSONピンをLowにし、デイジー・チェインの次デバイスのチップセレクトをドライブすることで、D[0:7]からコンフィギュレーション・データを読み始めることができるようにします。いったんコンフィギュレーション・データのすべてを受け取ると、フロースルー・オプションはまた、デイジー・チェインで他のデバイスの干渉を防ぐために、D[0:7]、INITN、

およびBUSYピンをトライステートにします。

一度フロースルー・オプションが始まると、ウェイクアップ・シーケンスが完了するまでデバイスはフロースルーのままです。CSNとCS1Nの両方をHighにすることによって、フロースルー・オプションを中止することができます。

## マスタクロック

CFGピンによりマスタデバイスになると、CCLKピンはユーザによって設定された周波数の出力になります。 デフォルトのマスタクロック周波数は2.5MHzです。

ユーザは、ラティスispLEVERデザイン・ソフトウェアでMCCLK\_FREQプリファレンスを設定することによって、マスタクロック周波数を指定することができます。コンフィグレーション時に最初にロードされるものの一つはMCCLK\_FREQパラメータです。一度このパラメータがロードされると、周波数はグリッチのないスイッチを用いて選択された値へ変えられます。スレーブ・デバイスの周波数仕様や、PCBレイアウトの信号インテグリティ機能を超えないように注意します。利用できるオプションについては表12-3を参照してください。

#### セキュリティ・ピット

セキュリティ・ビットを設定すると、JTAGやsysCONFIGピンからSRAMとフラッシュのリードバックすることを防ぎます。セキュリティ・ビットが設定されるとき、利用できる動作は消去と書き込みだけです。セキュリティ・ビットは、SRAMコンフィグレーションかフラッシュ・プログラミングの最後の動作としてアップデートされます。

オンチップ・フラッシュを用い、かつセキュリティ・ビットを設定することによって、ユーザは非常に安全なデバイスを作成することができます。

セキュリティ・ビットはispLEVERデザイン・ソフトウェアによりプリファレンス・エディタ ( Preference Editor ) を通してアクセスされます。

ラティスセミコンダクターのウェブサイトwww.latticesemi.comより入手できるドキュメント"FPGA Design Security Issues: Using the ispXPGA Family of FPGAs to Achieve Design Security (FPGA設計におけるセキュリティの課題:ispXPGA FPGAファミリを用いた高いデザイン・セキュリティの達成)"でデバイス・セキュリティに関する詳しい情報があります。

#### スレープシリアル・モード

| モード                           | CFG[1] | CFG[0] | CONFIG_MODEパラメータ | チェインモード |

|-------------------------------|--------|--------|------------------|---------|

| Slave Serial (オーバフロー・オプションなし) | 0      | 0      | SLAVE_SERIAL     | 禁止      |

| Slave Serial (バイパス On)        | 0      | 0      | SLAVE_SERIAL     | バイパス    |

CCLKピンは入力になり、DIのデータはCCLKの立ち上がりエッジで取り込まれます。バイパス・オプションが設定されていると、デバイスが完全に構成された後に、DIに送られたデータは図12-4で示されるようにDOUTピンを通して次のデバイスに送られます。

## マスタシリアル・モード

| モード                                | CFG[1] | CFG[0] | CONFIG_MODEパラメータ | チェインモード |

|------------------------------------|--------|--------|------------------|---------|

| Master Serial (オーバフロー・オプ<br>ションなし) | 0      | 1      | MASTER_SERIAL    | 禁止      |

| Master Serial (バイパス ON)            | 0      | 1      | MASTER_SERIAL    | バイパス    |

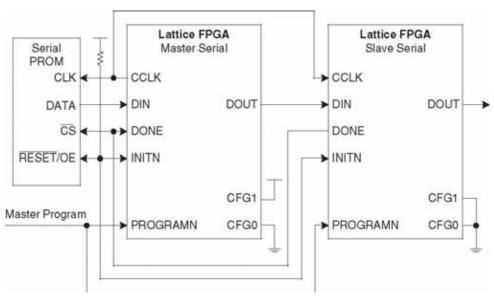

マスタシリアル・モードでは、デバイスはチェインのスレーブシリアル・デバイスと、ビットストリームを

提供するシリアルPROMのためにCCLKをドライブします。マスタデバイスはCCLKの立ち上がりエッジでDINのデータを受け入れます。マスタシリアル・デバイスは、コンフィグレーションの開始から、外部のDONEピンがHighにドライブされ、その後さらに100~500クロック周期の間、CCLKをドライブし続けます。パワーアップ時のCCLK周波数は2.5MHzをデフォルトとします。新しいクロック周波数がビットストリームからロードされるまで、マスタクロック周波数はデフォルトのままです。

マスタシリアル・デバイスがスレーブシリアル・デバイスとデイジー・チェインされる場合、オーバフロー・コンフィギュレーション・データがDOUTピンに向けられるように、バイパス・オプションが用いられるべきです。

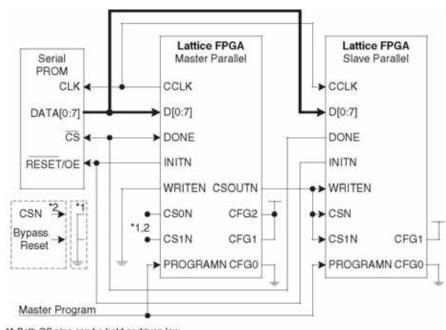

図12-4はシリアル・デイジーチェインを示します。デイジー・チェインは、コンフィグレーション・データ記憶デバイス一つで複数のラティスFPGAデバイスを構成することができます。中央のデバイスはバイパス・オプションをセットしてマスタシリアルで動作し、一方デイジー・チェインにある他のラティスFPGAデバイスはスレーブシリアル・モードで動作します。チップセレクト・ピンはデバイスのDONEピンによってドライブされますが、PROMのRESET/OEピンはINITNによってドライブされます。

図12-4 マスタ、およびスレープのシリアル・デイジーチェイン

## スレーブパラレル・モード

| モード                             | CFG[1] | CFG[0] | CONFIG_MODEパラメータ | チェインモード |

|---------------------------------|--------|--------|------------------|---------|

| Slave Parallel (オーバフロー・オプションなし) | 1      | 1      | SLAVE_PARALLEL   | 禁止      |

| Slave Parallel (バイパス ON)        | 1      | 1      | SLAVE_PARALLEL   | バイパス    |

| Slave Parallel (フロースルー<br>ON)   | 1      | 1      | SLAVE_PARALLEL   | フロースルー  |

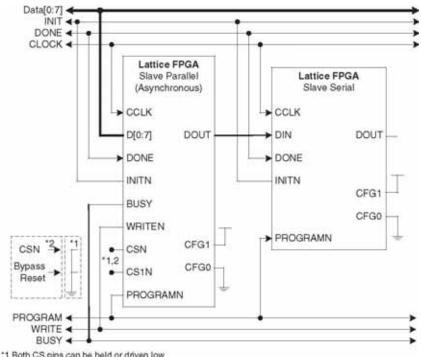

スレーブパラレル・モードでは、ホストシステムはバイト幅のストリームでコンフィギュレーション・データをデバイスに送ります。CCLK、CSN、CS1N、およびWRITENピンはホストシステムによってドライブされます。スレーブパラレル・コンフィグレーション・モードは、図12-5で示されるように複数のデバイスが並列にチェインを作ります。デバイスに書くためにはWRITEN、CSN、およびCS1NをLowに保持しなければなりません。データはD[0:7]から入力されます。また、内部コンフィグレーションのリードバックにスレ

ーブパラレル・モードを用いることができます。

WRITENピン、CSNとCS1NをLowにドライブすることによって、デバイスはD[0:7]ピンの上にリードバック命令を入力します。次に、WRITENはHighにドライブされ、データはD[0:7]で読み込まれます。リードバックをサポートするためには、ispLEVER内プリファレンス・エディタでPERSISTENTビットをONに設定しなければなりません。

スレーブパラレル・モードは2つのタイプのオーバフロー、バイパスおよびフロースルー、をサポートすることができます。バイパス・オプションが設定されていると、最初のデバイスがコンフィギュレーション・データのすべてを受け入れた後に、D[0:7]ピンのデータはシリアルにされ、DOUTピンにバイパスされます。フロースルー・オプションが設定されると、最初のデバイスがコンフィギュレーション・データのすべてを受け入れた後に、図12-5で示されるようにCSON信号は後ろにあるパラレルモード・デバイスのチップセレクトをLowにします。

非同期コンフィグレーションをサポートするために、FPGAが受け入れることができるより速くホストがデータを提供するかもしれない場合のために、スレーブパラレル・モードではBUSY信号を用いることができます。BUSY信号をHighにドライブすることによって、スレーブパラレル・デバイスは、データ送出を止めるようにホストに通知します。図12-6を参照してください。

## 図12-5 マスタ、及びスレープのパラレル・デイジーチェイン

<sup>&</sup>quot;1 Both CS pins can be held or driven low

<sup>\*2</sup> An option that allows the Bypass and Flow-Through option to be reset

<sup>\*1、</sup>両方のCSピンはLowに保持されるか、またはドライブされることができます。

<sup>\*2</sup> バイパスとフロースルー・オプションをリセットすることができるオプション

図12-6 スレーブパラレル・コンフィグレーション・モードの非同期な用法

\*1、両方のCSピンはLowに保持されるか、またはドライブされることができます。 \*2 バイパスとフロースルー・オプションをリセットすることができるオプション

図12-6は、バイパス・オプションを用いることによる非同期ペリフェラルの書き込みシーケンスを示します。 コンフィギュレーション・データをデバイスに送るために、WRITEN信号がアサートされなければなりませ ん。ライト・サイクルの間、BUSY信号はホストシステムとLatticeXPデバイスの間のハンドシェイクを提供 します。BUSYがLowのとき、CCLKの次の立ち上がりエッジで、デバイスはバイト・データを読む準備がで きています。デバイスがデータを読み、かつデータを処理するために付加的なクロック周期を必要とする場 合、BUSY信号がHighにされます。

ホストシステムがビジィである場合、一時的にライト・プロセスを止めるためにCSNかCS1N信号をHighス テートにすることができます。CSNとCS1Nが共に再びLowにされると、LatticeXPデバイスはコンフィグレ ーションを再開します。

いずれかのオーバフロー・オプションが選択されている場合、CSNとCS1Nピンの両方をHighに設定するこ とで、このオプションからスレーブパラレル・デバイスをリセットすることができます。

セルフ・ダウンロード・モード

| <b>モード</b> | CFG[1] | CFG[0] | CONFIG_MODEパラメータ    | チェインモード |

|------------|--------|--------|---------------------|---------|

| SDM        | 1      | 1      | None/Slave_Parallel | 禁止      |

セルフ・ダウンロード・モード(SDM)は、いかなる外部デバイスも用いないでFPGA自体を構成します。ま た、これはビットストリームが露出されないので、非常に安全なコンフィグレーション・モードです。ispJTAG かsysCONFIGピン上のスレーブパラレル・ポートを用いることで、ユーザはオンチップ・フラッシュにアク セスすることができます。

デバイスがパワーアップされている間はいつでも、デバイス動作を妨げることなくJTAGを介してオンチッ

<sup>&</sup>quot;1 Both CS pins can be held or driven low

<sup>\*2</sup> An option that allows the Bypass and Flow-Through option to be reset

プ・フラッシュにアクセスできます。また、JTAGはコンフィグレーションSRAMを読み書きもできます。オンチップのフラッシュとSRAMへのアクセスがJTAGのみに制限される場合、デュアル・ファンクションのピンを解放して汎用I/Oとして使用できるように、CONFIG\_MODEはNoneに設定されるべきです。

オンチップ・フラッシュにアクセスするためにスレーブパラレル・ポートも用いることができます。スレーブパラレル・ポートが使用される場合、CONFIG\_MODEはスレーブパラレル(Slave\_Parallel)設定されるべきです。オンチップ・フラッシュに書き込むためにはEN、CSN、およびCS1NをLowに保持しなければなりません。データはD[0:7]から入力されます。また、フラッシュとSRAMの両方のリードバックにスレーブパラレル・ポートを用いることができます。WRITENピンをLowにし、CSNとCS1NもLowにすることによって、デバイスはD[0:7]ピンにリードバック命令を入力するでしょう。リード・コマンド内のあるビットが、読み出しをフラッシュかSRAMかどうか決定します。デバイスがユーザ・モードである間(DONEピンはHigh)、リードバックをサポートするために、プリファレンス・エディタのPERSISTENTビットをONに設定しなければなりません。

SDMはオーバフローをサポートしません。

## ispJTAGモード

| モード                       | CFG[1] | CFG[0] | CONFIG_MODEパラメータ | チェインモード |

|---------------------------|--------|--------|------------------|---------|

| ispJTAG (1149.1 インターフェイス) | X      | Х      | None             |         |

ispJTAGポートを通してLatticeXPデバイスを構成することができます。選択されたコンフィグレーション・モードに係わらず、ispJTAGポートは常にオンであり、利用できます。JTAGポートが排他的に用いられること、すなわち、シリアルとパラレル・ポートは用いられないことを配置配線ツールに通知するために、ラティス ispLEVER デザイン・ソフトウェアで CONFIG\_MODE の None を選択することができます。CONFIG\_MODEをNoneに設定することで、デュアル・ファンクションのピンすべてが汎用I/Oとして用いられるのを許容します。

#### ISC 1532

ispJTAGポートによるコンフィグレーションはIEEE 1532標準に準拠します。いかなる1532モード命令の間も、バウンダリ・スキャン・セルがI/Oを制御します。JTAG1532モードを用いるときはいつでも、予め決められた値にバウンダリ・スキャン・セルを設定することができます。このため、有効なコンフィグレーション・ステータスのためのDONEなどの専用ピンに頼ることはできません。

## トランスペアレント・リードバック

ispJTAGのトランスペアレント・リードバック・モードで、ユーザはデバイスが通常動作状態にあっても SRAMやフラッシュのデータを読み出すことが可能です。EBRと分散メモリ(RAM)を読み出すときは、注意 しなければなりません。ユーザ・デザインからのアクセスとの衝突を引き起こす(データがこわれる)可能性 があるためです。

I/Oと非JTAGコンフィグレーション・ピンはトランスペアレント・リードバックの間、アクティブなままです。デバイスはJTAG命令によってトランスペアレント・リードバック・モードに入ります。

#### バウンダリ・スキャンとBSDLファイル

ラティス・ウェブサイトwww.latticesemi.comにデバイスのBSDLファイルがあります。バウンダリ・スキャン・リングはI/Oピンのすべてと、専用およびのデュアル・ファンクションのsysCONFIGピンをカバーしています。

#### 省電力モード

I/O省電力モード・オプションがLatticeXPデバイスにはあり、I/Oセル・ドライバの部分を非活性にします。

HSTL、SSTLなどのようなコンパレータ・タイプ(VREF用いる)入力ピンを用いるときだけ有効です。

省電力モードはバウンダリ・スキャンの機能のいくつかを制限します。バウンダリ・スキャン・テストにおいて、I/Oのすべてがフルに機能するようにI/O省電力モードをOFFに設定することを勧めます。

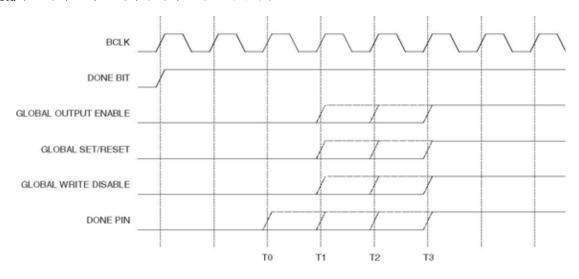

## ウェイクアップ(起動)オプション

コンフィグレーション(SRAMへのロード)が完了した後に、デバイスは予測できる形式でウェイクアップ(起動)するべきです。2つの同期ウェイクアップ・プロセスがあり、その選択でデバイスがどのように起動するかを決定します。1つは、DONEピンが外部的にLowに保持されるかどうかにかかわらず、内部Doneビットが設定されると自動的にデバイスを起動します。他方は、ウェイクアップ・プロセスを始める前にDONEピンがHighにドライブされるのを待ちます。DONE\_EXプリファレンスは、外部DONEピンが同期ウェイクアップを制御するかどうかを決定します。

## ウェイクアップ・シーケンス

表12-8はLatticeXPによってサポートされるウェイクアップ・シーケンスのリストを提供します。

## 内部Doneビットに同期

LatticeXPデバイスがチェインにおける唯一のデバイスである場合、またはチェインで最後のデバイスである場合、ウェイクアップ・プロセスはコンフィグレーションの完了で開始されるべきです。コンフィグレーションが完了すると、内部Doneビットがセットされ、次に、ウェイクアップ・プロセスが始まります。

表12-8 LatticeXPによってサポートされるウェイクアップ・シーケンス

| シーケンス     | フェーズT0 | フェーズT1          | フェーズT2          | フェーズT3          |

|-----------|--------|-----------------|-----------------|-----------------|

| 1         | DONE   | GOE, GWDIS, GSR |                 |                 |

| 2         | DONE   |                 | GOE, GWDIS, GSR |                 |

| 3         | DONE   |                 |                 | GOE, GWDIS, GSR |

| 4         | DONE   | GOE             | GWDIS, GSR      |                 |

| 5         | DONE   | GOE             |                 | GWDIS, GSR      |

| 6         | DONE   | GOE             | GWDIS           | GSR             |

| 7         | DONE   | GOE             | GSR             | GWDIS           |

| 8         |        | DONE            | GOE, GWDIS, GSR |                 |

| 9         |        | DONE            |                 | GOE, GWDIS, GSR |

| 10        |        | DONE            | GWDIS, GSR      | GOE             |

| 11        |        | DONE            | GOE             | GWDIS, GSR      |

| 12        |        |                 | DONE            | GOE, GWDIS, GSR |

| 13        |        | GOE, GWDIS, GSR | DONE            |                 |

| 14        |        | GOE             | DONE            | GWDIS, GSR      |

| 15        |        | GOE, GWDIS      | DONE            | GSR             |

| 16        |        | GWDIS           | DONE            | GOE, GSR        |

| 17        |        | GWDIS, GSR      | DONE            | GOE             |

| 18        |        | GOE, GSR        | DONE            | GWDIS           |

| 19        |        |                 | GOE, GWDIS, GSR | DONE            |

| 20        |        | GOE, GWDIS, GSR |                 | DONE            |

| 21(デフォルト) |        | GOE             | GWDIS, GSR      | DONE            |

| 22        |        | GOE, GWDIS      | GSR             | DONE            |

| 23        |        | GWDIS           | GOE, GSR        | DONE            |

|   | 24 | GWDIS, GSR | GOE   | DONE |

|---|----|------------|-------|------|

| ĺ | 25 | GOE, GSR   | GWDIS | DONE |

## 図12-7内部クロックとウェイクアップ・シーケンス

## 外部DONE信号に同期

ウェイクアップを遅らせるためにDONEピンを選択することができます。DONE\_EXが真であると、DONE ピンがHighになるまでウェイクアップ・シーケンスは遅れます。そして、デバイスは選択されたWAKE\_UP シーケンスに従います。

#### ウェイクアップ・クロックの選択

WAKE\_UPシーケンスはクロックソースと同期します。ユーザはウェイクアップのクロックソースを選択します。クロックソースは、CCLKと、TCK、そしてUser Clockです。選択したプログラミング/コンフィグレーション方法によって、デフォルトはTCKかCCLKのどちらかです。ispJTAGを用いる場合デフォルト・クロックはTCKで、sysCONFIGを用いる場合CCLKです。User Clockはユーザのデザインで選ばれます。ユーザはUser ClockソースとしてデバイスのCLKピン、またはネット(配線ノード)のいずれかを選択することができます。図12-7はUser ClockとしてBCLKを用いています。WAKEUP\_CLKはTCKかCCLKをデフォルトとします。

## ソフトウェアで選択可能なオプション

デフォルト設定を超えてLatticeXPデバイスのコンフィグレーションを制御するために、ソフトウェア・プリファレンスが使用されます。表12-9はプリファレンスのリストをデフォルト設定と共に示します。

表12-9 LatticeXP ソフトウェア・プリファレンス・リスト

| プリファレンス(プリファレンス) | デフォルト設定 [すべての設定]                    |

|------------------|-------------------------------------|

| PERSISTENT       | OFF [off, on]                       |

| CONFIG MODE      | NONE [SLAVE_PARALLEL, SLAVE_SERIAL, |

| CONFIG_MODE      | MASTER_SERIAL, MASTER_PARALLEL]     |

| DONE_OD          | ON [on, off]                        |

| DONE_EX          | OFF [off, on]                       |

| MCCLK_FREQ       | 最低周波数(表12-3 参照)                     |

| CONFIG_SECURE    | OFF [off, on]                       |

| IWAKE UP   | 21 (DONE_EX = Off) [1:25]<br>4 (DONE_EX = On) [1:7] |  |

|------------|-----------------------------------------------------|--|

| WAKEUP_CLK | EXTERNAL [external, user]                           |  |

| PWRSAVE    | OFF [off, on]                                       |  |

## パーシスタント (Persistent)

ユーザモードでSRAMやフラッシュ・メモリを読むためにsysCONFIGポートを用いる際は、PERSISTENT プリファレンスをONに設定しなければなりません。PERSISTENT=ONは、いつでも外部デバイスからFPGA にアクセスできるようにsysCONFIGピンのすべてを確保します。PERSISTENT=ONはソフトウェアにデュアル・ファンクションのコンフィグレーション・ピンのすべてが予約されており、フィッタでユーザが使用できるというわけではないことを知らせます。PERSISTENT=ONはCONFIG\_MODEに係わらずデュアル・ファンクションのsysCONFIGピンすべてを予約します。

#### コンフィグレーション・モード

デバイスは、CFG[1:0]のステートを読み込むことで物理的なsysCONFIGポートが用いられることがわかっていますが、フィッタ・ソフトウェアはどのポートが用いられるかも知る必要があります。フィッタはコンフィグレーション・ピンをサンプルすることができないので、ユーザは適切なCONFIG\_MODEを選択することによって、フィッタに伝えなければなりません。CONFIG\_MODEは、どのsysCONFIGピンがユーザI/Oとして利用できるかどうかをフィッタに伝えます。

ソフトウェアによって設定される他のコンフィグレーション・オプションとしてはオーバフローなどいくつかがあります。これらのオプションは、ispLEVERで"Generate Bitstream Data"プロセスを右クリックし "Properties"を選択することによって設定できます。オーバフロー・オプションが選択されると、DONE\_EXとWAKE\_UP選択がこれに相当するように設定されます(表12-10を参照)。詳細についてはドキュメントの "コンフィグレーション・モードとオプション"のセクションを参照してください。

表12-10 オーバフロー・オプションのデフォルト

| オーパフロー・オプション<br>(パイパス、フロースルー) | DONE_EX プリファレンス   | WAKE_UP プリファレンス             |

|-------------------------------|-------------------|-----------------------------|

| Off                           | Off (デフォルト)       | Default 21 (ユーザ選択可、1 から 25) |

| Off                           | On                | Default 21 (ユーザ選択可、1 から 25) |

| On (いずれか)                     | ON (ソフトウェアが自動で設定) | Default 4 (ユーザ選択可、1 から 7)   |

## DONE オープン・ドレイン

"DONE\_OD"プリファレンスで、ユーザはオープン・ドレインとしてDONEピンを構成します。"DONE\_OD" プリファレンスはDONEピンのみに用いられます。DONEピンが内部的か外部的にLowにドライブされるとき、これはコンフィグレーションが完了していないことを示し、デバイスはウェイクアップ・シーケンスの準備ができていません。デバイスがいったんコンフィグレーションが誤りなしで完了し、ウェイクアップの準備ができるようになると、DONEピンはHighにされます。他のデバイスがウェイクアップ・プロセスを制御することができるように、DONEピンのコンテンションを避けるためオープン・ドレインにコンフィグレーションされる必要があります。DONEピンのための"DONE\_OD"プリファレンスはデフォルトがONです。DONE\_EXプリファレンスがONに設定されると、DONE\_ODプリファレンスは自動的にONに設定されます。DONE\_ODとDONE\_EXとの関係の詳しい情報に関しては表12-11を参照してください。

#### **DONE External**

Done ビットがセットされるか、またはDONE ピンが外部的にHighにドライブされるのを待ったあと、LatticeXPデバイスはそれ自身でウェイクアップすることができます。

DONE\_EX=ONにすることで、クロックと同期する外部信号によってDONEピンがHighにドライブされるまでウェイクアップを遅らせることができます。OFFを選択すると、内部Doneビットがセットされたときに同期してウェイクアップし、DONEピンの外部状態がどのようにドライブされているかは無視します。デフォルトはDONE\_EX=OFFです。DONE\_EXがONに設定されると、DONE\_ODもONに設定されます。外部信号がDONEピンをドライブしているなら、それはまたオープン・ドレインとするべきです(外部にプルアップ抵抗を加える必要性があるかもしれません)。DONE\_ODとDONE\_EXとの関係の詳しい情報に関して表12-11を参照してください。

## 表12-11 DONEピン・プリファレンスに関するまとめ

| DONE_EX | ウェイクアップ・プロセス  | DONE_OD      |

|---------|---------------|--------------|

| OFF     | 外部DONEは無視     | ユーザ選択        |

| ON      | 外部DONEのLowで遅れ | デフォルトに設定(ON) |

#### マスタクロックの選択

ユーザが、LatticeXPをマスタ・コンフィグレーション・デバイスにすると決めると(適切にCFG[1:0]ピンを設定することによる)、これは同時にコンフィグレーションのためのクロックソースとなることを意味します。CCLKピンはMCCLK\_FREQに値によって設定された周波数の出力になります。コンフィグレーションの始めでは、デバイスは2.5MHzのデフォルトのマスタクロック周波数で動作します。コンフィグレーション・ビットストリームにおける幾つかの先頭ビットの一つはMCCLK\_FREQです。これらがいったんデバイスに読み込まれると、クロックはすぐにユーザ定義の周波数で動作し始めます。グリッチのないスイッチを用いることでクロック周波数を切り変えます。

## セキュリティ

CONFIG\_SECUREがONに設定されるとき、sysCONFIGかispJTAGポートを通してのリードバック動作はサポートされません。ただしispJTAG DeviceID領域のみは読み出し可能で、これはセキュリティの対象とは考えらないためです。デフォルトはOFFです。

#### ウェイクアップ・シーケンス

WAKE\_UPシーケンスは3つの内部信号とDONEピンを制御します。DONEピンはコンフィグレーションの後でかつユーザモードの前にドライブされます。位相コントロール例とウェイクアップ選択に関する情報に関しては、このドキュメントのウェイクアップ・シーケンス・セクションを参照してください。WAKE\_UPプリファレンスのデフォルト設定はDONE\_EXの設定で決定されます。

## DONE\_EX = Off でのウェイクアップ(デフォルト設定)

DONE\_EX = OFF(デフォルト)のためのWAKE\_UPプリファレンスは、表12-8で示されるようにユーザの選択可能なオプション1~25をサポートします。 ユーザがウェイクアップ・シーケンスを選択しないと、 DONE\_EX=OFFでは、デフォルトはウェイクアップ・シーケンス21になります。

## DONE\_EX = On でのウェイクアップ

DONE\_EX=ONのWAKE\_UPプリファレンスは、表12-8で示されるようにユーザの選択可能なオプション1  $\sim$  7をサポートします。ユーザがウェイクアップ・シーケンスを選択しないと、デフォルトはウェイクアップ・シーケンス4になります。

## ウェイクアップ・クロックの選択

WAKE\_UPシーケンスはクロックソースと同期します。ユーザは、ウェイクアップのクロックソースを選択することができます。クロックソースは、外部(CCLKまたはTCK)かユーザクロックのいずれかです。デフォルトは外部(External)で、選択したプログラミング/コンフィグレーションによって、TCKかCCLKのどちらか

になります。デフォルト・クロックはispJTAG用いる場合TCKで、sysCONFIGを用いる場合はCCLKになります。ユーザクロック(User Clock)はユーザの設計で選ばれます。ユーザはソースとしてデバイスのCLKピン、またはネット(配線ノード)のどれかを選択することができます。WAKEUP\_CLKはTCKかCCLKをデフォルトとします。

## **INBUF**

I/O INBUFオプションはI未使用の入力バッファを全て非活性化します。INBUFモードはバウンダリ・スキャン機能の一部を制限します。バウンダリ・スキャン・テストのためには、I/Oのすべてがフルに機能するように本モードをONに設定することをお勧めします。

# テクニカル・サポート支援

ホットライン: 1-800-LATTICE (North America)

+1-503-268-8001 (Outside North America)

e-mail: techsupport@latticesemi.com

インターネット: www.latticesemi.com